#### Overview:

The RS9113 module family is based on Redpine Signals' RS9113 ultra-low-power Convergence SoC. These modules offer dual-band 1x1 802.11n, dual-mode Bluetooth 4.0 and ZigBee® 802.15.4 in a single device. They are high performance, long range and ultra-low power modules and include a proprietary multi-threaded MAC processor called ThreadArch®, digital and analog peripheral interfaces, baseband digital signal processor, calibration OTP memory, dual-band RF transceiver, dual-band high-power amplifiers, baluns, diplexers, diversity switch and Quad-SPI flash.

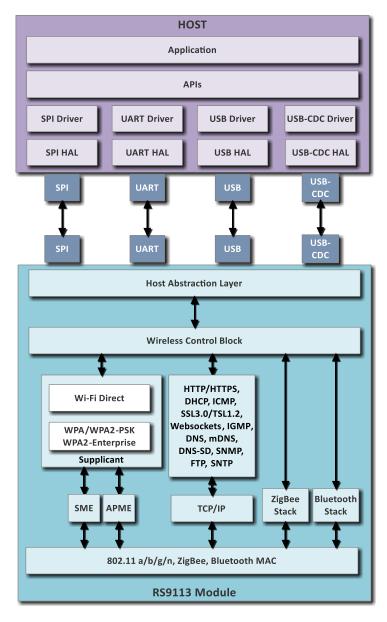

The modules are offered with two software architectures - hosted and embedded. The hosted variant (n-Link®) realizes a host-based architecture where the necessary MAC and PHY layers are implemented in the device to support highperformance, long range WLAN, Bluetooth and ZigBee applications in a 32-bit host processor over SDIO or USB interfaces. The embedded variants (WiSeConnect® and Connect-io-n®) realize WLAN, Bluetooth and ZigBee protocols along with Wi-Fi Direct™(1), WPA/WPA2-PSK, WPA/WPA2-Enterprise (EAP-TLS, EAP-FAST, EAP-TTLS, EAP-PEAP, EAP-LEAP)(1) and a feature-rich networking stack thus providing a fully-integrated solution for embedded low-end wireless applications. These modules can be connected to 8/16/32-bit host processors through SPI, UART, USB and USB-CDC interfaces.

The modules are available in two hardware footprints. One footprint type comes with an integrated antenna and an u.FL connector and the other footprint comes without an integrated antenna.

### **Applications:**

- Smartphones, Tablets and e-Readers

- VoWi-Fi phones

- Smart meters and in-home displays

- Industrial automation and telemetry

- Medical devices

- Industrial monitoring and control

- Home and building automation

- Wireless Headset

### **Module Features:**

#### WLAN:

- Compliant to single-spatial stream IEEE 802.11

a/b/g/n with dual band (2.4 and 5 GHz) support.

- Support for 20MHz and 40MHz (n-Link™ only) channel bandwidths.

- Transmit power up to +17dBm with integrated PA.

- Receive sensitivity of -97dBm.

### Bluetooth:

- Compliant to dual-mode Bluetooth 4.0

- Transmit power up to 15dBm (class-1) with integrated PA.

- Receive sensitivity of -94 dBm.

### ZigBee:

- Compliant to IEEE 802.15.4

- Transmit power up to 15 dBm with integrated PA.

- Receive sensitivity of -102 dBm.

- ZigBee Pro stack embedded.

#### n-Link®:

- Seamless integration with 32-bit processors over SDIO and USB.

- Host Drivers for Linux, Android and Windows<sup>2</sup>

### WiSeConnect® and Connect-io-n®:

- WLAN, Bluetooth and ZigBee stacks embedded in the device.

- Supports Wi-Fi Direct™(1), Access point mode, WPA/WPA2-PSK, WPA/WPA2-Enterprise (EAP-TLS, EAP-FAST, EAP-TTLS, EAP-PEAP, EAP-LEAP)1

- Bluetooth profiles embedded.<sup>3</sup>

- ZigBee Pro stack embedded.

- TCP/IP stack (IPv4/IPv6), HTTP/HTTPS, DHCP, ICMP, SSL 3.0/TLS1.2, Websockets, IGMP, FTP Client, SNTP, DNS, mDNS, DNS-SD, SNMP<sup>4</sup> embedded in the device.

- SPI, UART, USB, USB-CDC host interfaces.

### General:

- FCC, IC, ETSI/CE, TELEC Certified

- U.FL connector for external antenna connection.

- Dual external antenna for antenna diversity (n-Link™ only.

- Wireless firmware upgrade (for WiSeConnect™ and Connect-io-n™ only)

- Options for single supply of 3.0 to 3.6 V operation or multiple supplies for power saving<sup>5</sup>.

<sup>&</sup>lt;sup>1</sup>This feature is specific to WiSeConnect® Modules and not available in Connect-io-n® Modules.

<sup>&</sup>lt;sup>2</sup>Drivers for Linux and Android available now. Contact Redpine Signals Sales (<u>sales@redpinesignals.com</u>) for availability of drivers Windows.

<sup>&</sup>lt;sup>3</sup>Refer to the Features section for list of profiles supported.

<sup>&</sup>lt;sup>4</sup>mDNS and DNS-SD supported in future software releases.

<sup>&</sup>lt;sup>5</sup>USB Interface needs VBUS level of 5V for detection and enumeration.

• Operating temperature range: -40°C to +85°C

### **About this Document**

This document describes the RS9113 module family specifications. The document covers the modules' hardware and software features, package descriptions, pin descriptions, interface specifications, electrical characteristics, performance specifications, reliability and certification information and ordering information.

### Disclaimer:

The information in this document pertains to information related to Redpine Signals, Inc. products. This information is provided as a service to our customers, and may be used for information purposes only. Redpine assumes no liabilities or responsibilities for errors or omissions in this document. This document may be changed at any time at Redpine's sole discretion without any prior notice to anyone. Copyright © 2017 Redpine Signals, Inc. All rights reserved.

## Table of Contents

| 1 | Ove         | erview                                                       | 8  |

|---|-------------|--------------------------------------------------------------|----|

|   | 1.1         | Block Diagram                                                | 8  |

|   | 1.2         | Product Naming and Variants                                  | 9  |

| 2 | Fea         | tures                                                        | 11 |

| 3 | Pac         | kage Description                                             | 19 |

|   | 3.1         | Package Description of Module without Antenna (Package # P6) |    |

|   | 3.1.1       |                                                              |    |

|   | 3.1.2       |                                                              |    |

|   | 3.1.3       | 3 PCB Landing Pattern                                        | 21 |

|   | 3.2         | Package Description of Module with Antenna (Package # P7)    | 21 |

|   | 3.2.1       |                                                              |    |

|   | 3.2.2       |                                                              |    |

|   | 3.2.3       |                                                              |    |

|   | 3.1         | Recommended Reflow Profile                                   |    |

|   | 3.2         | Baking Instructions                                          |    |

| 4 | Pine        | out and Pin Description                                      |    |

|   | 4.1         | Pinout of Module without Antenna                             | 26 |

|   | 4.2         | Pinout of Module with Integrated Antenna                     |    |

|   | 4.3         | Pin Description                                              | 27 |

| 5 | Spe         | ecifications                                                 | 38 |

|   | 5.1         | Absolute Maximum Ratings                                     | 38 |

|   | 5.2         | Recommended Operating Conditions                             | 39 |

|   | 5.3         | Reliability Qualification                                    | 39 |

|   | 5.4         | DC Characteristics – Digital I/O Signals                     | 40 |

|   | 5.5         | AC Characteristics                                           | 41 |

|   | 5.5.1       | 1 SDIO Interface                                             | 41 |

|   | 5.          | .5.1.1 Full Speed Mode                                       |    |

|   | _           | .5.1.2 High Speed Mode                                       |    |

|   | 5.5.2       | ,                                                            |    |

|   | _           | .5.2.1 Low Speed Mode                                        |    |

|   | 5.<br>5.5.3 | .5.2.2 High Speed Mode                                       |    |

|   |             | .5.3.1 Fast Speed Mode                                       |    |

|   | _           | .5.3.2 High Speed Mode                                       |    |

|   | 5.5.4       |                                                              |    |

|   | 5.5.5       |                                                              |    |

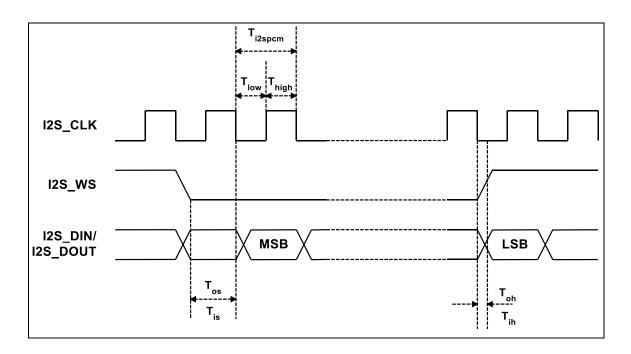

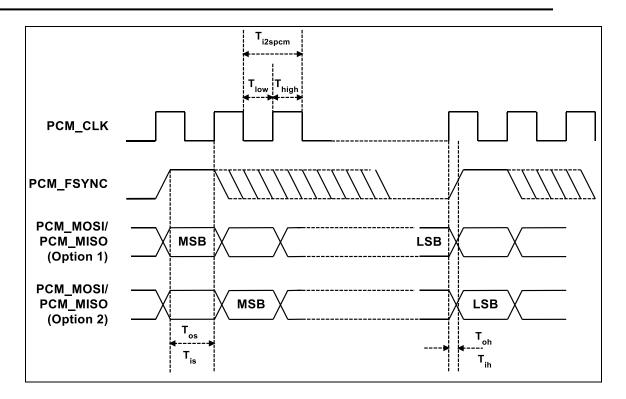

|   | 5.          | .5.5.1 Timing Characteristics                                | 48 |

|   | 5.          | .5.5.2 Electrical Characteristics                            | 49 |

|   | 5.          | .5.5.3 Voltage Thresholds                                    | 49 |

|   | 5.5.6       |                                                              |    |

|   | 5.6         | Regulatory Specifications and Certifications                 |    |

|   | 5.6.1       | -0                                                           |    |

| _ | 5.6.2       |                                                              |    |

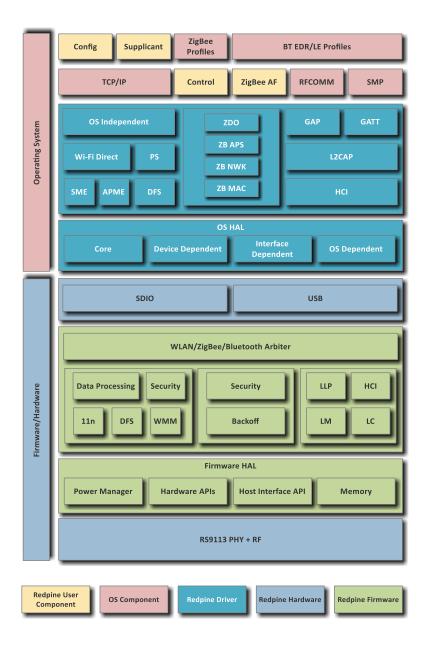

| 6 |             | tware Architecture                                           |    |

|   | 6.1         | n-Link® Software Architecture                                |    |

|   | 6.1.1       | 1 Operating System Support                                   | 52 |

| 6.2 WiSeConnect®/Connect-io-n® Software Architecture                           | .52  |

|--------------------------------------------------------------------------------|------|

| 7 Module Marking and Ordering Information                                      | .54  |

| 7.1 Module Marking Information                                                 |      |

| 7.2 Ordering Information                                                       |      |

| 7.3 Collateral                                                                 |      |

| 7.3.1 Collateral for n-Link® Modules                                           |      |

| 7.3.2 Collateral for WiSeConnect®/Connect-io-n® Modules                        |      |

| ·                                                                              |      |

| 7.4 Packing Information                                                        |      |

| 7.5 Contact Information                                                        | .58  |

|                                                                                |      |

| <u>Table of Figures</u>                                                        |      |

| Figure 1: Block Diagram of RS9113 Module without Integrated Antenna            | 8    |

| Figure 2: Block Diagram of RS9113 Module with Integrated Antenna               | 9    |

| Figure 3: RS9113 Modules' Naming Convention                                    | 9    |

| Figure 4: Package Dimensions of Module without Antenna                         |      |

| Figure 5: PCB Landing Pattern of Module without Antenna                        |      |

| Figure 6: Package Dimensions of Module with Antenna                            |      |

| Figure 7: PCB Landing Pattern of Module with Antenna                           |      |

| Figure 8: Mounting View of Module with Antenna                                 |      |

| Figure 9: Reflow Diagram                                                       |      |

| Figure 10: Pinout Diagram of Module without Antenna                            |      |

| Figure 11: Pinout Diagram of Module with Antenna                               |      |

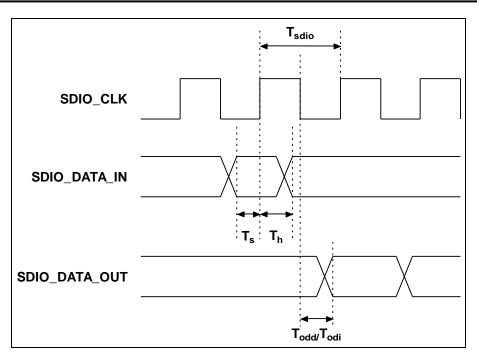

| Figure 12: SDIO Interface Timings – Full Speed Mode                            |      |

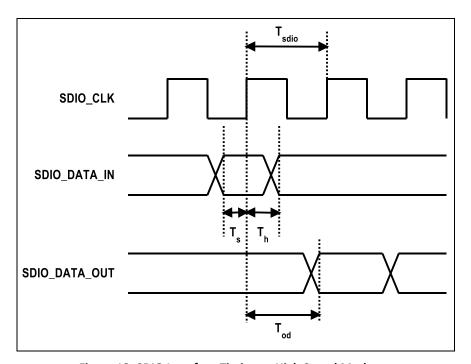

| Figure 13: SDIO Interface Timings – High Speed Mode                            |      |

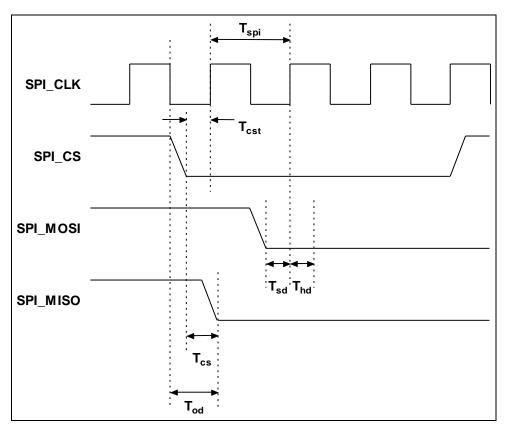

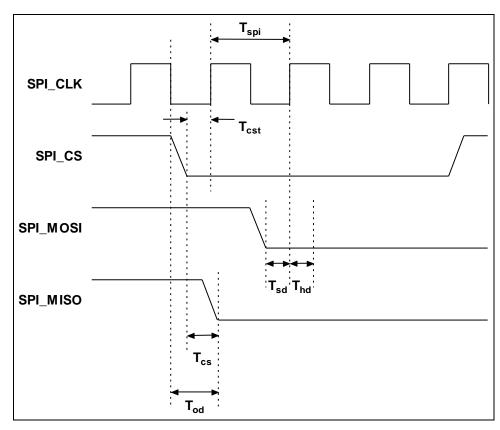

| Figure 14: Slave SPI Interface Timings – Low Speed Mode                        |      |

| Figure 15: Slave SPI Interface Timings – High Speed Mode                       |      |

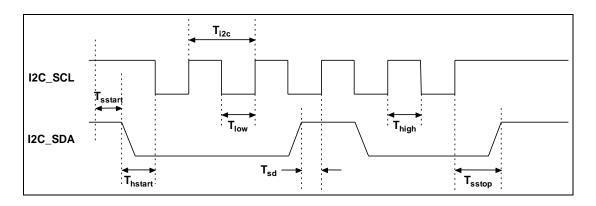

| Figure 16: Interface Timings – I <sup>2</sup> C Fast Speed Mode                |      |

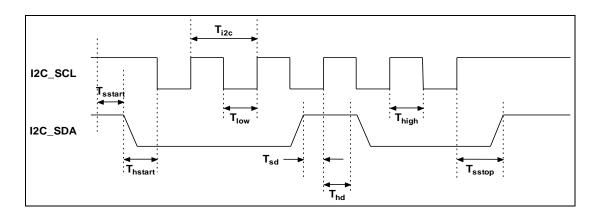

| Figure 17: Interface Timings – 1°C Fast Speed Mode                             |      |

| Figure 18: Interface Timings – I C High Speed Mode                             |      |

| Figure 19: Interface Timings – PCM                                             |      |

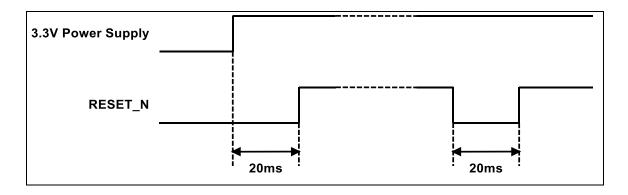

| Figure 20: Reset Timings – PCWI                                                |      |

| Figure 29: n-Link®Software Architecture                                        |      |

|                                                                                |      |

| Figure 30: WiSe Connect® / Connect-io-n® Software Architecture                 |      |

| Figure 31: Module Marking Information                                          |      |

| Figure 32: Mechanical Details of Tray for P6 Package                           |      |

| Figure 33: Mechanical Details of Tray for P7 Package                           | . 58 |

| <u>Table of Tables</u>                                                         |      |

|                                                                                | _    |

| Table 1: RS9113 Module Family Features                                         |      |

| Table 2: Mechanical Dimensions of Module without Antenna                       |      |

| Table 3: Mechanical Dimensions of Module with Antenna                          |      |

| Table 4: Pin Descriptions                                                      |      |

| Table 5: Absolute Maximum Ratings                                              |      |

| Table 6: Recommended Operating Conditions                                      |      |

| Table 7: HTOL Based Stress Testing                                             |      |

| Table 8: Input/Output DC Characteristics                                       |      |

| Table 9: AC Characteristics – SDIO Full Speed Mode (as per SDIO v2.0 Protocol) |      |

| Table 10: AC Characteristics – SDIO Full Speed Mode (on Silicon)               | . 41 |

|                                                                                |      |

| 42 |

|----|

| 43 |

| 43 |

| 44 |

| 45 |

| 46 |

| 47 |

| 48 |

| 49 |

| 49 |

| 50 |

| 50 |

| 55 |

|    |

### 1 Overview

The RS9113 n-Link®, WiSeConnect® and Connect-io-n® modules are M2M Combo modules based on Redpine Signals' RS9113 ultra-low-power Convergence SoC.

They differ in terms of the features embedded in the module's firmware and their performance. The n-Link® modules are high-performance modules which realize a zero-host architecture for the data path. The necessary MAC and PHY layers are implemented in the device to support WLAN, Bluetooth and ZigBee applications and they interface with 32-bit host processors over SDIO or USB interfaces. The WiSeConnect® and Connect-io-n® modules offer WLAN, ZigBee and Bluetooth protocols along with Wi-Fi Direct™(6), WPA/WPA2-PSK,WPA/WPA2-Enterprise (EAP-TLS, EAP-FAST, EAP-TTLS, EAP-PEAP, EAP-LEAP) (6) and a feature-rich networking stack embedded in the device, thus providing a fully-integrated solution for embedded wireless applications. These modules can be interfaced to 8/16/32-bit host processors through SPI, UART, USB and USB-CDC interfaces.

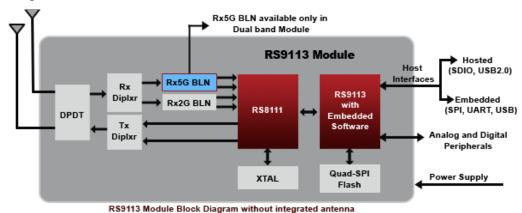

All three modules are offered with and without an integrated antenna. The module with the integrated antenna also offers a u.FL connector for connecting an external antenna with an option to select either one of them.

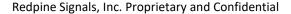

### 1.1 Block Diagram

The following figures are the block diagrams for the modules with and without the integrated antenna.

Figure 1: Block Diagram of RS9113 Module without Integrated Antenna

<sup>&</sup>lt;sup>6</sup>This feature is specific to WiSeConnect® Modules.

Figure 2: Block Diagram of RS9113 Module with Integrated Antenna

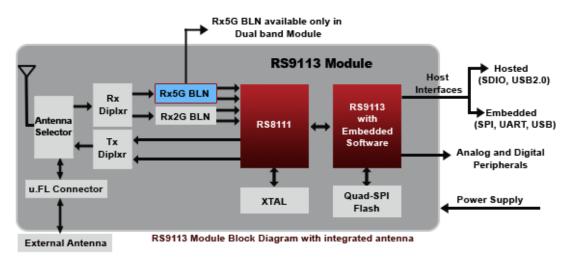

### 1.2 Product Naming and Variants

The figure below shows the naming convention of the RS9113 Family Modules.

Figure 3: RS9113 Modules' Naming Convention

### NOTE:

- 1) The possible combinations of 'XYZ' are 'N00', 'NB0', 'N0Z' and 'NBZ'.

- 2) The modules and the accompanying software/firmware support a maximum of two wireless protocols simultaneously.

For the full list of available module variants, please see the section on Ordering Information.

## 2 Features

The table below lists the features supported by the n-Link $^{\scriptsize @}$ , WiSeConnect $^{\scriptsize @}$  and Connect-ion $^{\scriptsize @}$  modules.

| S.No. | Feature                                  | n-Link®                                                   | WiSeConnect®                                                                    | Connect-io-n®                                     |

|-------|------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------|

| 1.    | Wireless Protocols                       | IEEE 802.11a, 802.11                                      | b, 802.11g, 802.11n                                                             |                                                   |

|       |                                          | Bluetooth 4.0 (2.1+E                                      | DR, LE)                                                                         |                                                   |

|       |                                          | ZigBee 802.15.4                                           |                                                                                 |                                                   |

| 2.    | Operational Modes Supported <sup>7</sup> | Wi-Fi Access Point<br>with support for<br>upto 32 clients | Wi-Fi Access Point with support for upto 8 clients and limited packet buffering |                                                   |

|       |                                          | Wi-Fi Client                                              |                                                                                 |                                                   |

|       |                                          | Wi-Fi Access Point<br>+ Client                            | NA                                                                              |                                                   |

|       |                                          | Wi-Fi Direct™                                             |                                                                                 | NA                                                |

|       |                                          | Wi-Fi Client +<br>Bluetooth Classic<br>(EDR v2.1)         | Wi-Fi Client +<br>ZigBee End Device                                             | Wi-Fi Client +<br>Bluetooth Classic<br>(EDR v2.1) |

|       |                                          | Wi-Fi Client +<br>Bluetooth Low<br>Energy                 |                                                                                 | Wi-Fi Client +<br>Bluetooth Low<br>Energy         |

|       |                                          | Wi-Fi Client +<br>ZigBee End Device                       |                                                                                 | Wi-Fi Client +<br>ZigBee End Device               |

|       |                                          | ZigBee Router <sup>8</sup>                                |                                                                                 |                                                   |

|       |                                          | ZigBee Coordinator8                                       |                                                                                 |                                                   |

| 3.    | WLAN Bandwidth                           | 20 and 40 MHz                                             | 20 MHz                                                                          |                                                   |

| 4.    | WLAN Data Rates                          | 802.11b: 1, 2, 5.5, 11                                    | Mbps                                                                            |                                                   |

|       |                                          | 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps                |                                                                                 |                                                   |

|       |                                          | 802.11n: MCS0 to MCS7 with and without Short GI           |                                                                                 |                                                   |

| 5.    | WLAN Operating Frequency                 | 2412 MHz – 2484 MHz                                       |                                                                                 |                                                   |

|       | Range                                    | 4910 MHz – 5825 MHz                                       |                                                                                 |                                                   |

| 6.    | WLAN Modulation                          | OFDM with BPSK, QF                                        | PSK, 16-QAM, and 64-0                                                           | QAM                                               |

<sup>&</sup>lt;sup>7</sup>For other co-existence modes not listed here, contact Redpine Signals Sales (<u>sales@redpinesignals.com</u>) for custom offerings.

<sup>&</sup>lt;sup>8</sup>Supported in future software releases.

| S.No. | Feature                                | n-Link®                                                                            | WiSeConnect®                 | Connect-io-n® |

|-------|----------------------------------------|------------------------------------------------------------------------------------|------------------------------|---------------|

|       |                                        | 802.11b with CCK an                                                                | d DSSS                       |               |

| 7.    | WLAN Transmit Power                    | 17 dBm                                                                             |                              |               |

| 8.    | WLAN Receive Sensitivity               | -97 dBm                                                                            |                              |               |

| 9.    | Bluetooth Data Rates                   | 1, 2, 3 Mbps                                                                       |                              |               |

| 10.   | Bluetooth Operating Frequency<br>Range | 2402 MHz - 2480 MH                                                                 | lz                           |               |

| 11.   | Bluetooth Channel Spacing              | BR, EDR – 1 MHz<br>LE – 2 MHz                                                      |                              |               |

| 12.   | Bluetooth Modulation                   | GFSK, DQPSK, 8DPSK                                                                 |                              |               |

| 13.   | Bluetooth Transmit Power               | 15 dBm (Class-1)                                                                   |                              |               |

| 14.   | Bluetooth Receive Sensitivity          | -94 dBm                                                                            |                              |               |

| 15.   | ZigBee Data Rate                       | 250 kbps                                                                           |                              |               |

| 16.   | ZigBee Operating Frequency<br>Range    | 2405MHz - 2480 MHz                                                                 |                              |               |

| 17.   | ZigBee Modulation                      | DSSS                                                                               |                              |               |

| 18.   | ZigBee Transmit Power                  | 15 dBm                                                                             |                              |               |

| 19.   | ZigBee Receive Sensitivity             | -102 dBm                                                                           |                              |               |

| 20.   | Deep Sleep Current<br>Consumption      | < 10 μA in disconnec                                                               |                              |               |

| 21.   | Host Interfaces                        | SDIO 2.0<br>USB 2.0/1.1                                                            | SPI UART USB 2.0/1.1 USB-CDC |               |

| 22.   | SDIO Host Interface                    | Compatible with<br>SDIO standard<br>version 2.0<br>Maximum clock<br>speed of 50MHz | NA                           |               |

| 23.   | USB Host Interface                     | Supports 480 Mbps High Speed (HS) mode and 12 Mbps Full Speed (FS) modes.          |                              |               |

| 24.   | SPI Host Interface                     | NA                                                                                 | Maximum clock spee           | d of 80MHz    |

| S.No. | Feature                                  | n-Link®                                             | WiSeConnect®                                                                                                                                                                                                                                         | Connect-io-n®         |

|-------|------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|       |                                          |                                                     | Support for SPI Mode<br>CPHA=0) and 3 (CPO                                                                                                                                                                                                           | · ·                   |

| 25.   | UART Host Interface                      | NA                                                  | Supported Baud Rates (bps): 9600,<br>19200, 38400, 57600, 115200, 230400,<br>460800, 921600                                                                                                                                                          |                       |

|       |                                          |                                                     | Support for AT and B<br>Configuration and Da                                                                                                                                                                                                         | =                     |

|       |                                          |                                                     | Support for 8 bits en                                                                                                                                                                                                                                | coding                |

|       |                                          |                                                     | Support for 1stop bit                                                                                                                                                                                                                                | :                     |

|       |                                          |                                                     | Support for Auto Flo                                                                                                                                                                                                                                 | w Control             |

|       |                                          |                                                     | Support for Transpar                                                                                                                                                                                                                                 | ent Mode              |

| 26.   | Software Architecture                    | Architecture for<br>Zero Host Load for<br>Data path | Embedded Architecture which includes all network related features, including WLAN, Bluetooth, ZigBee stacks and a feature-rich TCP/IP stack embedded in the module. Option to bypass the TCP/IP stack and include only the Wireless protocol stacks. |                       |

| 27.   | Wireless Security Features               | WPA/WPA2<br>Personal                                | WPA/WPA2-<br>Personal                                                                                                                                                                                                                                | WPA/WPA2-<br>Personal |

|       |                                          | WPA/WPA2                                            | WPA/WPA2                                                                                                                                                                                                                                             | WPS                   |

|       |                                          | Enterprise Security                                 | Enterprise <sup>9</sup> :                                                                                                                                                                                                                            | (embedded in the      |

|       |                                          | WPS                                                 | EAP-TLS                                                                                                                                                                                                                                              | device)               |

|       |                                          | (in the Host)                                       | EAP-FAST                                                                                                                                                                                                                                             |                       |

|       |                                          |                                                     | EAP-TTLS                                                                                                                                                                                                                                             |                       |

|       |                                          |                                                     | EAP-PEAP                                                                                                                                                                                                                                             |                       |

|       |                                          |                                                     | EAP-LEAP<br>WPS                                                                                                                                                                                                                                      |                       |

|       |                                          |                                                     | (embedded in the                                                                                                                                                                                                                                     |                       |

|       |                                          |                                                     | device)                                                                                                                                                                                                                                              |                       |

| 28.   | Advanced Security Features <sup>10</sup> | PUF Based Security                                  |                                                                                                                                                                                                                                                      |                       |

|       |                                          | AES 128/256-bit                                     |                                                                                                                                                                                                                                                      |                       |

<sup>&</sup>lt;sup>9</sup>Supported only in Wi-Fi Client mode. For Enterprise Security methods not listed here, contact Redpine Signals Sales (<u>sales@redpinesignals.com</u>) for custom offerings.

<sup>&</sup>lt;sup>10</sup>These features are not part of the standard firmware. Contact Redpine Signals Sales (sales@redpinesignals.com) for details.

| S.No. | Feature                                   | n-Link®                                                                               | WiSeConnect®                                 | Connect-io-n®       |

|-------|-------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------|---------------------|

|       |                                           | RSA                                                                                   |                                              |                     |

|       |                                           | SHA, SHA256                                                                           |                                              |                     |

|       |                                           | ECDH                                                                                  |                                              |                     |

| 29.   | Application throughputs <sup>11</sup>     | Upto 90 Mbps UDP                                                                      | With embedded TCP                            | /IP Stack:          |

|       |                                           | Upto 70 Mbps TCP                                                                      | Upto 25 Mbps UDP                             |                     |

|       |                                           |                                                                                       | Upto 20 Mbps TCP                             |                     |

|       |                                           |                                                                                       | With TCP/IP Stack in                         | Host:               |

|       |                                           |                                                                                       | Upto 40 Mbps UDP                             |                     |

|       |                                           |                                                                                       | Upto 25 Mbps TCP                             |                     |

| 30.   | Operating Temperature Range               | -40°C to +85°C                                                                        |                                              |                     |

| 31.   | Supply Voltages and Options <sup>12</sup> | Option 1: Single 3.0 to 3.6V Supply                                                   |                                              |                     |

|       |                                           | Option $2^{13}$ : A 3.0 to 3.6V Supply, a 1.8 to 3.6V Supply and a 1.9 to 3.6V Supply |                                              |                     |

| 32.   | WLAN Features                             | Dynamic selection of data rate depending on the channel statistics.                   |                                              |                     |

|       |                                           | Hardware accelerato                                                                   | ors for WEP 64/128-bit                       | , TKIP, AES and WPS |

|       |                                           | Support for WMM                                                                       |                                              |                     |

|       |                                           | Support for AMPDU and De-aggregation                                                  | Aggregation/De-aggre                         | gation and AMSDU    |

|       |                                           | Support for IEEE 802.11d/e/I, 802.11j <sup>14</sup> , 802.11w/k/v/r/h <sup>14</sup>   |                                              |                     |

| 33.   | TCP/IP Features                           | NA                                                                                    | TCP/IP Stack with IPv                        | /4, IPv6            |

|       |                                           |                                                                                       | HTTP Server/Client                           |                     |

|       |                                           |                                                                                       | Static and Dynamic V<br>Objects (for HTML Se | . •                 |

|       |                                           |                                                                                       | DHCP Server/Client f                         | or IPv4 and IPv6    |

<sup>&</sup>lt;sup>11</sup>The throughputs mentioned here have been recorded in an ideal environment on an x86 platform over USB. Throughputs observed in other environments might differ based on the host interface speeds (e.g., SPI/SDIO clock frequency, UART Baud Rate, etc.), host processor capabilities (CPU frequency, RAM, etc.), wireless medium, physical obstacles, distance, etc.

<sup>&</sup>lt;sup>12</sup>USB Interface needs VBUS level of 5V for detection and enumeration.

$<sup>^{13}</sup>$ This option results in lower power consumption overall. Refer to the Module Integration Guide for details on the circuit.

<sup>&</sup>lt;sup>14</sup>Except 802.11h, all other features to be supported in future software releases. 802.11h is supported in n-Link™ only. Contact Redpine Signals Sales (<u>sales@redpinesignals.com</u>) for DFS certification for different regulatory domains.

| S.No. | Feature                                    | n-Link®                                                                                                                                                                                                                                                                                                                        | WiSeConnect®                                                 | Connect-io-n®                 |

|-------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|

|       |                                            |                                                                                                                                                                                                                                                                                                                                | HTTPS Server/Client                                          |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | ICMP                                                         |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | SSL 3.0/TLS 1.2                                              |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | Websockets                                                   |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | DNS Client                                                   |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | IGMP                                                         |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | FTP Client                                                   |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | SNTP                                                         |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | mDNS Client <sup>15</sup>                                    |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | DNS-SD Client <sup>15</sup>                                  |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                | SNMP <sup>15</sup>                                           |                               |

| 34.   | Bluetooth Features                         | Supports Classic mod                                                                                                                                                                                                                                                                                                           | le piconet with seven a                                      | active slaves <sup>16</sup> . |

|       |                                            | Supports Low Energy                                                                                                                                                                                                                                                                                                            | mode with upto eight                                         | active slaves <sup>17</sup> . |

|       |                                            | Supports scatternet one slave role while l                                                                                                                                                                                                                                                                                     | with two slave roles or<br>being visible <sup>18</sup> .     | one master role and           |

|       |                                            | Proprietary Mode to<br>"reserved" bit <sup>18</sup> .                                                                                                                                                                                                                                                                          | support 15 active slav                                       | es by using the               |

|       |                                            | Bluetooth security fe<br>Encryption.                                                                                                                                                                                                                                                                                           | atures: Authentication                                       | n, Pairing and                |

|       |                                            | Supports low power modes with selectab                                                                                                                                                                                                                                                                                         | connection states such<br>le sniff intervals <sup>19</sup> . | as hold and sniff             |

|       |                                            | Adaptive Frequency Hopping (AFH), Interlaced scanning, Quality of Service, Channel Quality Driven Data Rate <sup>18</sup> .  Channel assessment algorithm provides fast and accurate determination of occupied channels for use in adaptive frequency hopping mode <sup>18</sup> .  Proprietary FEC for DQPSK and 8-PSK modes. |                                                              |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                |                                                              |                               |

|       |                                            |                                                                                                                                                                                                                                                                                                                                |                                                              |                               |

|       |                                            | Provides finer granularity of range vs. throughput contro                                                                                                                                                                                                                                                                      |                                                              | ighput control.               |

| 35.   | Bluetooth Profiles/Protocols <sup>20</sup> | All profiles are to                                                                                                                                                                                                                                                                                                            | GAP                                                          |                               |

<sup>&</sup>lt;sup>15</sup>mDNS, DNS-SD and SNMP supported in future software releases.

<sup>&</sup>lt;sup>16</sup>Current software releases support one slave.

<sup>&</sup>lt;sup>17</sup>WiSeConnect<sup>™</sup> release v1.6.1 onwards supports upto 8 active slaves and n-Link<sup>™</sup> release v1.2.0 onwards supports upto 3 active slaves. Support for upto eight slaves for n-Link<sup>™</sup> to be added in future releases.

<sup>&</sup>lt;sup>18</sup>Supported in future software releases. Two slave roles can be supported only when LE mode is not enabled.

<sup>&</sup>lt;sup>19</sup>Hold supported in future software releases.

| S.No. | Feature         | n-Link®                                                                                                                     | WiSeConnect®                      | Connect-io-n®            |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

|       |                 | be implemented in                                                                                                           | GATT                              |                          |

|       |                 | the Host.                                                                                                                   | SPP                               |                          |

|       |                 |                                                                                                                             | SDP                               |                          |

|       |                 |                                                                                                                             | SMP                               |                          |

|       |                 |                                                                                                                             | L2CAP                             |                          |

|       |                 |                                                                                                                             | RFCOMM                            |                          |

|       |                 |                                                                                                                             | iAP1                              |                          |

| 36.   | ZigBee Features | MAC:                                                                                                                        |                                   |                          |

|       | · ·             | <del>'</del>                                                                                                                | gBee Coordinator, Rou             | uter <sup>21</sup> , End |

|       |                 | PHY features: Beacon<br>Promiscuous mode.                                                                                   | n <sup>18</sup> , Non-Beacon, CCM | Security,                |

|       |                 | Power saving using End Device Sleep, network periodic sleep.                                                                |                                   |                          |

|       |                 | Supports CCM* Secu                                                                                                          | rity levels 1-7.                  |                          |

|       |                 | Supports Active scan, channel selection, Association and Disassociation, Orphan scanning, and coordinator realignment.      |                                   |                          |

|       |                 | Network Layer:                                                                                                              |                                   |                          |

|       |                 | Network Discovery                                                                                                           |                                   |                          |

|       |                 | Energy Detection Sca                                                                                                        | ın                                |                          |

|       |                 | Network Formation                                                                                                           |                                   |                          |

|       |                 | Permit Joining                                                                                                              |                                   |                          |

|       |                 | Network Join                                                                                                                |                                   |                          |

|       |                 | Network Rejoin                                                                                                              |                                   |                          |

|       |                 | Stochastic Addressin                                                                                                        | g                                 |                          |

|       |                 | Network Leave Network Reset Routing (Symmetric) Address Conflict PANID Conflict Network Status Updates Link Status Commands |                                   |                          |

|       |                 |                                                                                                                             |                                   |                          |

|       |                 |                                                                                                                             |                                   |                          |

|       |                 |                                                                                                                             |                                   |                          |

|       |                 |                                                                                                                             |                                   |                          |

|       |                 |                                                                                                                             |                                   |                          |

|       |                 |                                                                                                                             | Jnicast and Broadcast)            |                          |

<sup>&</sup>lt;sup>20</sup>Profiles not listed here can be offered as part of custom firmware. Contact Redpine Signals Sales (<u>sales@redpinesignals.com</u>) for details.

<sup>&</sup>lt;sup>21</sup>Coordinator and Router modes supported in future software releases.

| S.No. | Feature                        | n-Link®                                                                                                                                                                                                                                                                                                | WiSeConnect®                                                                                         | Connect-io-n® |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------|

|       |                                | NIB Management                                                                                                                                                                                                                                                                                         |                                                                                                      |               |

|       |                                | Many-to-one and so                                                                                                                                                                                                                                                                                     | urce routing                                                                                         |               |

|       |                                | Multicast relaying an                                                                                                                                                                                                                                                                                  | d route discovery                                                                                    |               |

|       |                                |                                                                                                                                                                                                                                                                                                        |                                                                                                      |               |

|       |                                | APS Layer:                                                                                                                                                                                                                                                                                             |                                                                                                      |               |

|       |                                | APSDE Data primitive                                                                                                                                                                                                                                                                                   | es                                                                                                   |               |

|       |                                | APSME Group Service                                                                                                                                                                                                                                                                                    |                                                                                                      |               |

|       |                                | APSME Binding Servi                                                                                                                                                                                                                                                                                    |                                                                                                      |               |

|       |                                | APSME Fragmentation                                                                                                                                                                                                                                                                                    | on Service                                                                                           |               |

|       |                                | Reliable Transport                                                                                                                                                                                                                                                                                     |                                                                                                      |               |

|       |                                | Duplicate Rejection                                                                                                                                                                                                                                                                                    |                                                                                                      |               |

|       |                                | APS Layer Security                                                                                                                                                                                                                                                                                     |                                                                                                      |               |

|       |                                | ZDO/ZDP Layer:                                                                                                                                                                                                                                                                                         |                                                                                                      |               |

|       |                                | Device Discovery                                                                                                                                                                                                                                                                                       |                                                                                                      |               |

|       |                                | Service Discovery                                                                                                                                                                                                                                                                                      |                                                                                                      |               |

|       |                                | Security Manager                                                                                                                                                                                                                                                                                       |                                                                                                      |               |

|       |                                | Node Manager                                                                                                                                                                                                                                                                                           |                                                                                                      |               |

|       |                                | Network Manager                                                                                                                                                                                                                                                                                        |                                                                                                      |               |

|       |                                | Binding Manager                                                                                                                                                                                                                                                                                        |                                                                                                      |               |

|       |                                | Group Manager                                                                                                                                                                                                                                                                                          |                                                                                                      |               |

|       |                                | Startup Attributes Se                                                                                                                                                                                                                                                                                  | t                                                                                                    |               |

| 37.   | Power Save Modes <sup>22</sup> | Dynamic Clock Gatin                                                                                                                                                                                                                                                                                    | g                                                                                                    |               |

|       |                                | , ,                                                                                                                                                                                                                                                                                                    | Low Power (LP) Mode – Modem and RF Transceiver Powered off. Host Interface is active. Supported with |               |

|       |                                | Ultra-Low Power (ULP) Mode – Most of the module powered off except for a small portion running a timer. Host interface is inactive. Entry and exit of sleep mode can be through packet or GPIO based handshake. Supported only in SPI, UART (WiSeConnect® and Connect-io-n®) and SDIO (n-Link®) modes. |                                                                                                      |               |

| 38.   | Miscellaneous Features         | Automatic<br>Firmware<br>Checksum<br>validation and                                                                                                                                                                                                                                                    | Wireless Firmware U<br>Wireless Configuration                                                        | . •           |

<sup>&</sup>lt;sup>22</sup>Refer to Technical Reference Manual of n-Link® Modules and Programmer Reference Manual/API User Guide of WiSeConnect® and Connect-io-n® Modules for more details on how to use these modes. Refer to the GPIO section of the Pin Description table to understand the signal requirements for these modes.

| S.No. | Feature | n-Link®                 | WiSeConnect® | Connect-io-n® |

|-------|---------|-------------------------|--------------|---------------|

|       |         | upgrade at power-<br>up |              |               |

Table 1: RS9113 Module Family Features

## 3 Package Description

The RS9113 Modules are offered in two package variants – one with an integrated antenna (and U.FL connector) and the other without an antenna.

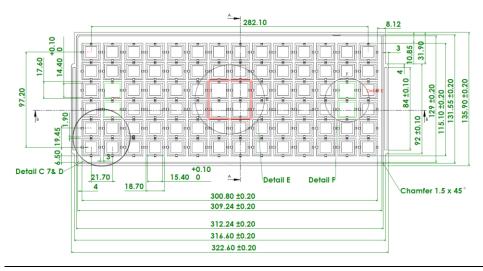

## 3.1 Package Description of Module without Antenna (Package # P6)

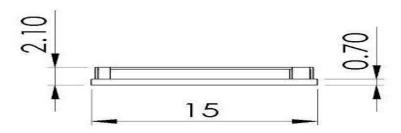

### 3.1.1 Mechanical Characteristics

| Parameter         | Value (L X W X H) | Units |

|-------------------|-------------------|-------|

| Module Dimensions | 14 x 15 x 2.1     | mm    |

| Tolerance         | ±0.2              | mm    |

Table 2: Mechanical Dimensions of Module without Antenna

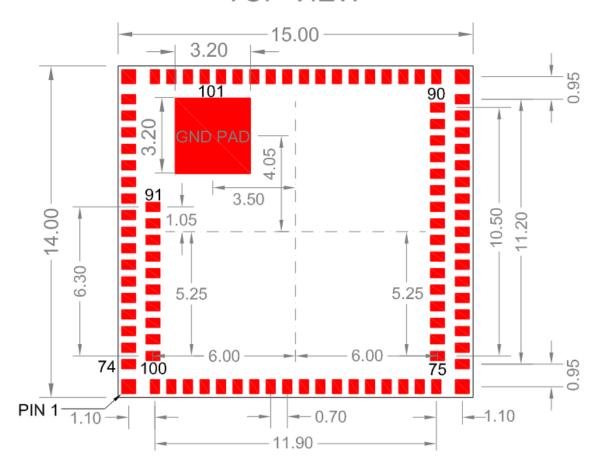

### 3.1.2 Package Dimensions

# **TOP VIEW**

PAD SIZE 0.40mm x 0.60mm CORNERPAD SIZE 0.60mm x 0.60mm PAD PITCH:0.70mm

ALL DIMENSIONS ARE IN MM

Figure 4: Package Dimensions of Module without Antenna

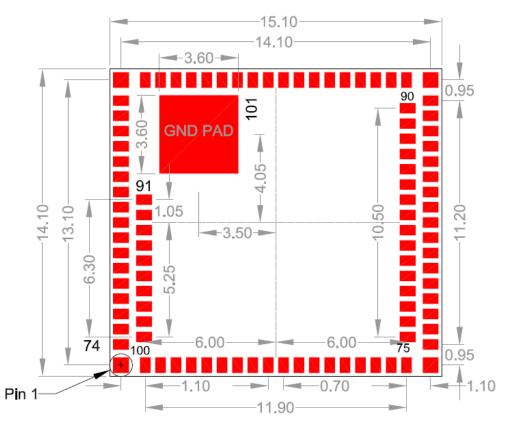

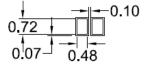

### 3.1.3 PCB Landing Pattern

All Dimensions are in mm

Pad size 0.48 mm x 0.72 mm

Corner Pad size 0.72 mm x 0.72 mm

Pad pitch 0.70 mm

Figure 5: PCB Landing Pattern of Module without Antenna

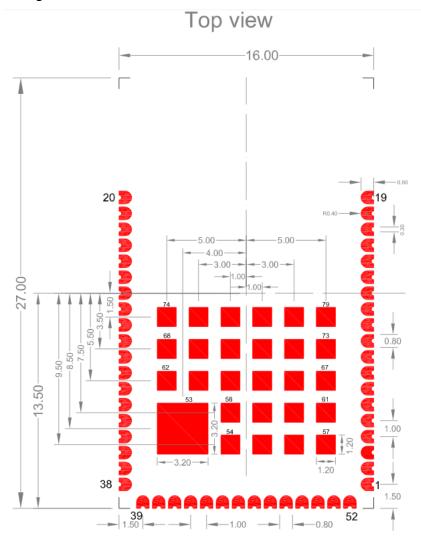

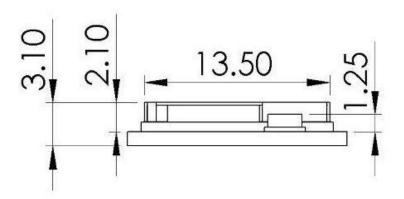

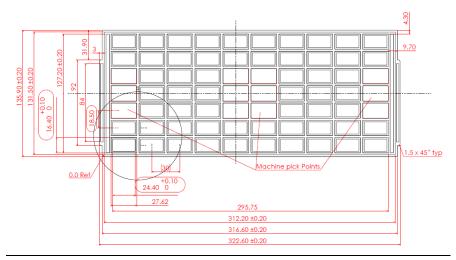

## 3.2 Package Description of Module with Antenna (Package # P7)

## 3.2.1 Mechanical Characteristics

| Parameter         | Value (L X W X H) | Units |

|-------------------|-------------------|-------|

| Module Dimensions | 27 x 16 x 3.1     | mm    |

| Tolerance         | ±0.2              | mm    |

Table 3: Mechanical Dimensions of Module with Antenna

### 3.2.2 Package Dimensions

All Dimensions are in mm

Figure 6: Package Dimensions of Module with Antenna

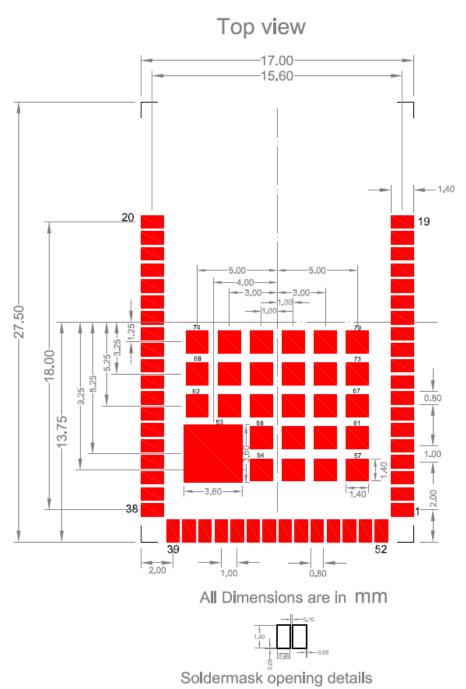

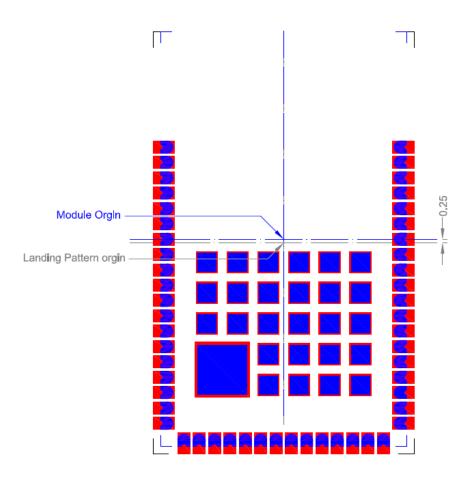

### 3.2.3 PCB Landing Pattern

Figure 7: PCB Landing Pattern of Module with Antenna

Figure 8: Mounting View of Module with Antenna

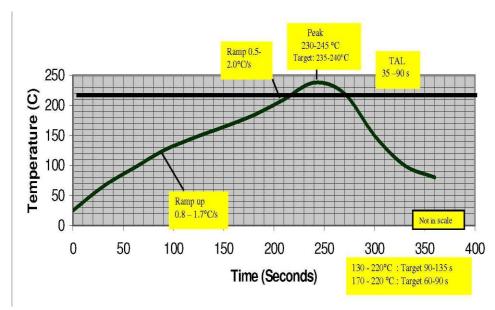

### 3.1 Recommended Reflow Profile

Figure 9: Reflow Diagram

Note: The profile shown is based on SAC 305 solder (3% silver, 0.5% copper). We recommend the ALPHA OM-338 lead-free solder paste. This profile is provided mainly for guidance. The total dwell time depends on the thermal mass of the assembled board and the sensitivity of the components on it. The recommended belt speed is 50-60 Cm/Min. A finished module can go through two more reflow processes

### 3.2 Baking Instructions

The RS9113 module packages are moisture sensitive and devices must be handled appropriately. After the devices are removed from their vacuum-sealed packs, they should be taken through reflow for board assembly within 168 hours at room conditions, or stored at under 10% relative humidity. If these conditions are not met, the devices must be baked before reflow. The recommended baking time is nine hours at 125°C.

## 4 Pinout and Pin Description

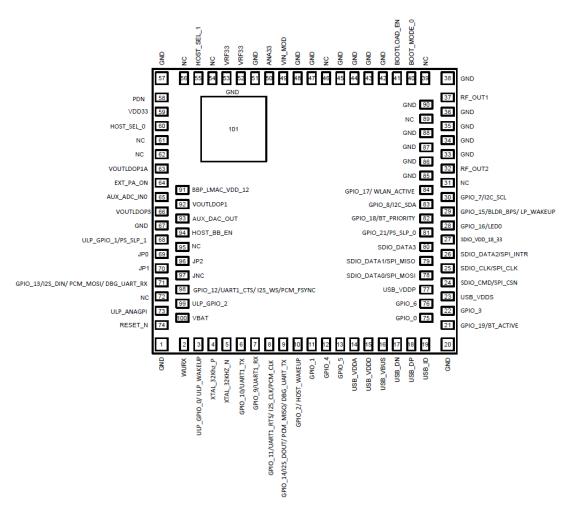

### 4.1 Pinout of Module without Antenna

Figure 10: Pinout Diagram of Module without Antenna

**Pinout of Module with Integrated Antenna**

#### 800TM006\_0 20 19 10.0\_100\_18\_33 21 SDIO\_CLK/SPI\_CLK 18 US8\_V00P 17 SDIO\_CMD/SPI\_CSN 22 U\$8\_V006 23 GRO\_7/2C\_50, SDIO\_DATA2/ SPI\_INTR 16 GPO\_15/6LDR\_BPS/LP\_WAKEUP SDIO\_DATAS 15 25 GRO\_16/LEDO SDIO\_DATAS/ SPI\_MSD 14 GPIO\_2/ HOST\_WAKEUP 26 13 SOI O\_DATAO/ SPI\_MOSI SOOTLOAD\_EN USB\_ID 12 74 75 78 79 76 77 GPIO\_17/ WLAN\_ACTIVE 28 11 USS\_DP GND USB\_DN 29 10 GPIO\_8/20\_50A 71 72 73 70 68 69 GRO\_18/ST\_PRIORITY 9 USB\_VBUs GND GND GND GND QPIO\_21/PS\_SUP\_0 31 8 GPIO\_S4/25\_DOUT/ PCM\_MISO/ DBG\_UART\_TX 62 67 64 65 66 63 7 GRO\_11/UART1\_RT5/125\_QX/PCM\_QX GRO\_19/8T\_ACTIVE 32 GRO\_9/UARTI\_RX VIN\_MOD 6 61 58 59 60 GRO\_10/UART1\_TX ANASS 34 5 53 GND GND GND HOST\_SEL\_1 XTAL\_32KHZ\_N 35 4 57 56 54 55 XTAL\_\$20%\_P HOST\_SEL\_O 36 3 ULP\_GRO\_Q'ULP\_WAKEUP VOUTLDOP1 37 2 38 1 AUX\_DAC\_DUT USB VOOR DIRLYPCIA MOSVIDES UART 8X WOUTLOOPS NUX ADC.

Figure 11: Pinout Diagram of Module with Antenna

## 4.3 Pin Description

4.2

This section describes the pins of the two packages of the RS9113 Module family. The information contained here should be used along with the information in the Module Integration Guide.

| S.No                     | Pin Name                           | Pin # in P6 | Pin # in P7 | Direction       | Description                                                                                                                                                                                                  |  |  |

|--------------------------|------------------------------------|-------------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Control and RF Interface |                                    |             |             |                 |                                                                                                                                                                                                              |  |  |

| 1.                       | RESET_N                            | 74          | 51          | Input           | Active-low asynchronous reset signal. The minimum reset assertion time is 20 ms.                                                                                                                             |  |  |

| 2.                       | RF_OUT_2                           | 32          |             | RF In/RF<br>Out | Default Antenna port. Connect to Antenna with a $50~\Omega$ impedance. Refer to Module Integration Guide for details.                                                                                        |  |  |

| 3.                       | RF_OUT_1                           | 37          |             | RF In/RF<br>Out | Used in the case of Antenna Diversity $^{23}$ . If used, connect to Antenna with a 50 $\Omega$ impedance and follow same guidelines as RF_OUT_2 from Module Integration Guide. If unused, leave unconnected. |  |  |

| Power                    | and Ground Interface <sup>24</sup> |             |             |                 |                                                                                                                                                                                                              |  |  |

| 4.                       | VIN_MOD                            | 49          | 33          | Input           | 3.3V Digital Power Supply                                                                                                                                                                                    |  |  |