#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                         | Operating Temperature Range40°C to +85°C Storage Temperature Range65°C to +150°C Maximum Junction Temperature+150°C Lead Temperature (soldering, 10s)+300°C |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-Pin SO123 (derate 8./mW/°C above +/0°C)696mW |                                                                                                                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7 \text{V to } +3.6 \text{V (MAX5363)}, V_{DD} = +4.5 \text{V to } +5.5 \text{V (MAX5364)}, V_{DD} = +2.7 \text{V to } +5.5 \text{V (MAX5365)}, R_L = 10 \text{k}\Omega, C_L = 50 \text{pF}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are  $T_A = +25 ^{\circ}\text{C}$ .)

| PARAMETER                         | SYMBOL          | COND                                                   | ITIONS            | MIN                       | TYP                 | MAX                  | UNITS      |  |

|-----------------------------------|-----------------|--------------------------------------------------------|-------------------|---------------------------|---------------------|----------------------|------------|--|

| STATIC ACCURACY                   |                 |                                                        |                   |                           |                     |                      |            |  |

| Resolution                        |                 |                                                        |                   | 6                         |                     |                      | Bits       |  |

| Integral Linearity Error          | INL             | (Note 1)                                               |                   |                           |                     | ±1                   | LSB        |  |

| Differential Linearity Error      | DNL             | Guaranteed monotoni                                    | С                 |                           |                     | ±1                   | LSB        |  |

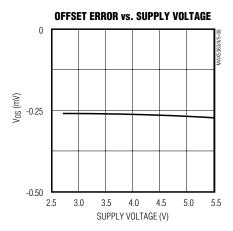

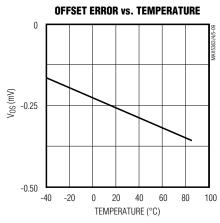

| Offset Error                      | Vos             | (Note 2)                                               |                   |                           | ±1                  | ±25                  | mV         |  |

| Offset Error Supply Rejection     |                 | MAX5365 (Notes 2, 3)                                   |                   |                           |                     | 60                   | dB         |  |

| Offset Error                      |                 | MAX5363/MAX5364                                        |                   |                           | 3                   |                      | ppm/°C     |  |

| Temperature Coefficient           |                 | MAX5365                                                |                   |                           | 1                   |                      | ррпі/ С    |  |

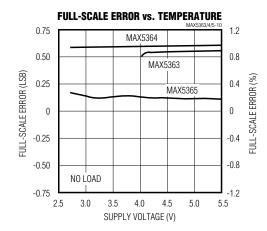

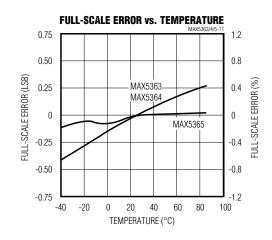

| Full-Scale Error                  |                 | Code = 63, no load                                     | MAX5363/MAX5364   |                           |                     | 10                   | % of ideal |  |

| Full-Scale EITOI                  |                 | Code = 65, 110 10au                                    | MAX5365           |                           |                     | 5                    | FS         |  |

| Full-Scale Error Supply           |                 | Code = 63 (Note 4)                                     | MAX5363/MAX5364   |                           |                     | 50                   | dB         |  |

| Full-Scale Error Temperature      |                 | Code = 63                                              | MAX5363/MAX5364   |                           | ±40                 |                      | nnm/°C     |  |

| Coefficient                       |                 | Code = 63                                              | MAX5365           |                           | ±10                 |                      | ppm/°C     |  |

| DAC OUTPUT                        |                 |                                                        |                   |                           |                     |                      |            |  |

|                                   |                 | MAX5363<br>MAX5364<br>MAX5365                          |                   | 1.8                       | 2                   | 2.2                  | -<br>- V   |  |

| Internal Reference Voltage        | R <sub>EF</sub> |                                                        |                   | 3.6                       | 4                   | 4.4                  |            |  |

| (Note 5)                          | NEF             |                                                        |                   | 0.85 ×<br>V <sub>DD</sub> | $0.9 \times V_{DD}$ | $0.95 \times V_{DD}$ |            |  |

| Output Load Regulation            |                 | Code = 63, 0 to $100\mu$                               | 4                 |                           | 0.5                 |                      | LSB        |  |

| Output Load Regulation            |                 | Code = 0, 0 to $100\mu$ A                              |                   |                           | 0.5                 |                      | LOD        |  |

|                                   |                 |                                                        | [D13, D12] = 0, 1 |                           | 1k                  |                      |            |  |

| Shutdown Output Resistance to GND |                 | $V_{OUT} = 0$ to $V_{DD}$                              | [D13, D12] = 1, 0 |                           | 100k                |                      | Ω          |  |

| G G G                             |                 | [D13, D12] = 1, 1                                      |                   |                           | 1M                  |                      |            |  |

| DYNAMIC PERFORMANCE               |                 |                                                        |                   |                           |                     |                      |            |  |

| Voltage Output Slew Rate          |                 | Positive and negative                                  |                   |                           | 0.4                 |                      | V/µs       |  |

| Output Settling Time              |                 | To 1/2 LSB, 50kΩ and 50pF load (Note 6)                |                   |                           | 20                  |                      | μs         |  |

| Digital Feedthrough               |                 | Code = 0, all digital inputs from 0 to V <sub>DD</sub> |                   |                           | 2                   |                      | nVs        |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=+2.7V \text{ to } +3.6V \text{ (MAX5363)}, V_{DD}=+4.5V \text{ to } +5.5V \text{ (MAX5364)}, V_{DD}=+2.7V \text{ to } +5.5V \text{ (MAX5365)}, R_L=10k\Omega, C_L=50pF, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$

| PARAMETER                     | SYMBOL          | CONDITIONS                                                      |                          | TYP                       | MAX                      | UNITS |  |

|-------------------------------|-----------------|-----------------------------------------------------------------|--------------------------|---------------------------|--------------------------|-------|--|

| Digital-Analog Glitch Impulse |                 | Code 31 to code 32                                              |                          | 40                        |                          | nVs   |  |

| Wake-Up Time                  |                 | From software shutdown                                          |                          | 50                        |                          | μs    |  |

| POWER REQUIREMENTS            |                 |                                                                 |                          |                           |                          |       |  |

|                               |                 | MAX5363                                                         | 2.7                      |                           | 3.6                      |       |  |

| Supply Voltage                | $V_{DD}$        | MAX5364                                                         | 4.5                      |                           | 5.5                      | V     |  |

|                               |                 | MAX5365                                                         | 2.7                      |                           | 5.5                      | ]     |  |

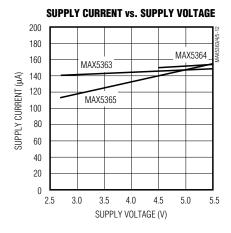

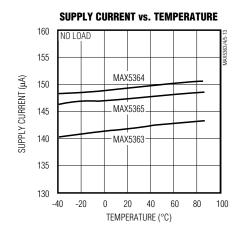

| Supply Current                | I <sub>DD</sub> | No load, all digital inputs at 0 or V <sub>DD</sub> , code = 63 |                          | 150                       | 230                      | μА    |  |

|                               |                 | Shutdown mode                                                   |                          |                           | 1                        | 1     |  |

| DIGITAL INPUTS                |                 |                                                                 |                          |                           |                          |       |  |

| Input Low Voltage             | VIL             |                                                                 |                          |                           | 0.3 ×<br>V <sub>DD</sub> | V     |  |

| Input High Voltage            | VIH             |                                                                 | 0.7 ×<br>V <sub>DD</sub> |                           |                          | V     |  |

| Input Hysteresis              | V <sub>H</sub>  |                                                                 |                          | 0.05 ×<br>V <sub>DD</sub> |                          | V     |  |

| Input Capacitance             | CIN             | (Note 7)                                                        |                          | 10                        |                          | рF    |  |

| Input Leakage Current         | IIN             |                                                                 |                          |                           | ±1                       | μΑ    |  |

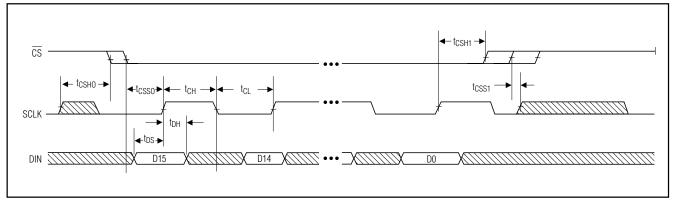

## **TIMING CHARACTERISTICS**

(Figures 3 and 4,  $V_{DD}$  = +2.7V to +3.6V (MAX5363),  $V_{DD}$  = +4.5V to +5.5V (MAX5364),  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = 10k $\Omega$

| PARAMETER                                          | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|-----------------|------------|-----|-----|-----|-------|

| SCLK Period                                        | tCP             |            | 100 |     |     | ns    |

| SCLK Pulse Width High                              | tсн             |            | 40  |     |     | ns    |

| SCLK Pulse Width Low                               | t <sub>CL</sub> |            | 40  |     |     | ns    |

| CS Fall to SCLK Rise Setup<br>Time                 | tcss            |            | 40  |     |     | ns    |

| SCLK Rise to $\overline{\text{CS}}$ Rise Hold Time | tcsh            |            | 0   |     |     | ns    |

| DIN Setup Time                                     | t <sub>DS</sub> |            | 40  |     |     | ns    |

| DIN Hold Time                                      | tDH             |            | 0   |     |     | ns    |

| SCLK Rise to $\overline{\text{CS}}$ Fall Delay     | tcso            |            | 10  |     |     | ns    |

| CS Rise to SCLK Rise Hold                          | tCS1            |            | 40  |     |     | ns    |

| CS Pulse Width High                                | tcsw            |            | 100 |     |     | ns    |

## **TIMING CHARACTERISTICS (continued)**

(Figures 3 and 4,  $V_{DD}$  = +2.7V to +3.6V (MAX5363),  $V_{DD}$  = +4.5V to +5.5V (MAX5364),  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = +2.7V to +5.5V (MAX5365),  $V_{DD}$  = 10k $\Omega$ ,  $V_{DD}$  = 10k $\Omega$

- Note 1: Guaranteed from code 2 to code 63.

- Note 2: The offset value extrapolated from the range over which the INL is guaranteed.

- Note 3: MAX5365 tested at 5V  $\pm 10\%$ .

- Note 4: MAX5363 tested at 3V  $\pm$ 10%; MAX5364 tested at 5V  $\pm$ 10%.

- **Note 5:** Actual output voltages at full scale are 63/64 × V<sub>REF</sub>.

- Note 6: Output settling time is measured by stepping from code 2 to code 63, and from code 63 to code 2.

- Note 7: Guaranteed by design.

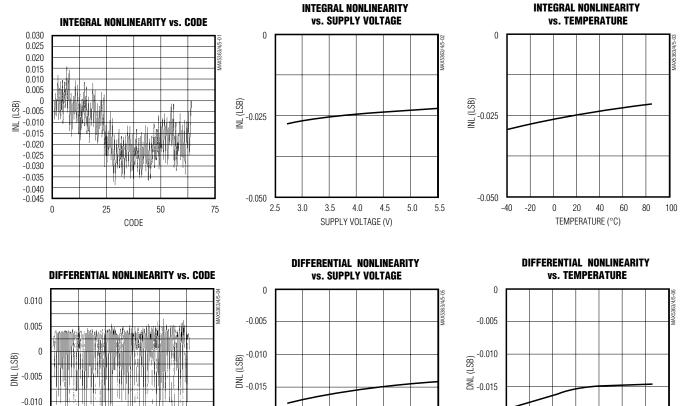

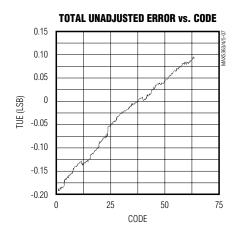

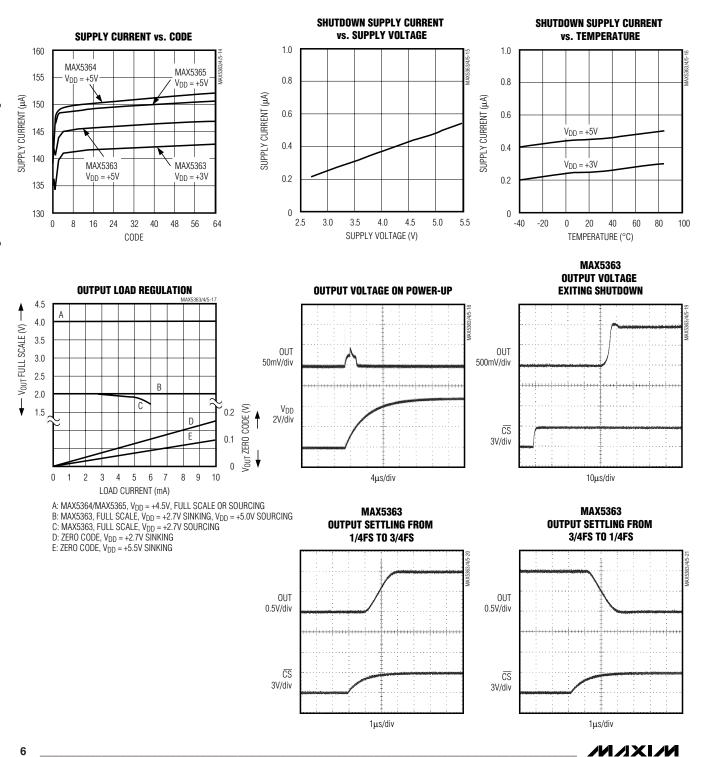

## **Typical Operating Characteristics**

-0.020

-0.025

20

TEMPERATURE (°C)

$(V_{DD} = +3.0V \text{ (MAX5363)}, V_{DD} = +5.0V \text{ (MAX5364/MAX5365)}, T_{A} = +25^{\circ}\text{C}$ , unless otherwise noted.)

-0.020

-0.025

2.5

3.0

4 \_\_\_\_\_\_\_*N*IXI/VI

40

SUPPLY VOLTAGE (V)

5.0

5.5

-0.015 -0.020

0

CODE

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V \text{ (MAX5363)}, V_{DD} = +5.0V \text{ (MAX5364/MAX5365)}, T_{A} = +25^{\circ}\text{C}, unless otherwise noted.)$

MIXIM

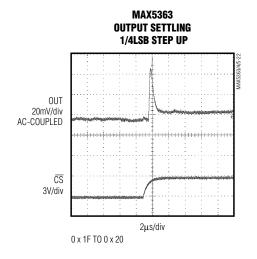

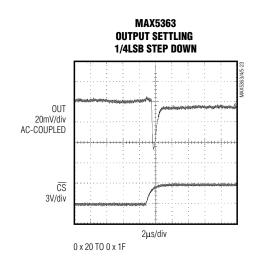

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V \text{ (MAX5363)}, V_{DD} = +5.0V \text{ (MAX5364/MAX5365)}, T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

Downloaded from **Arrow.com**.

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V \text{ (MAX5363)}, V_{DD} = +5.0V \text{ (MAX5364/MAX5365)}, T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

## **Pin Description**

| PIN | NAME     | FUNCTION           |  |

|-----|----------|--------------------|--|

| 1   | OUT      | DAC Voltage Output |  |

| 2   | GND      | Ground             |  |

| 3   | $V_{DD}$ | Power-Supply Input |  |

| 4   | DIN      | Serial Data Input  |  |

| 5   | SCLK     | Serial Clock Input |  |

| 6   | CS       | Chip-Select Input  |  |

## **Detailed Description**

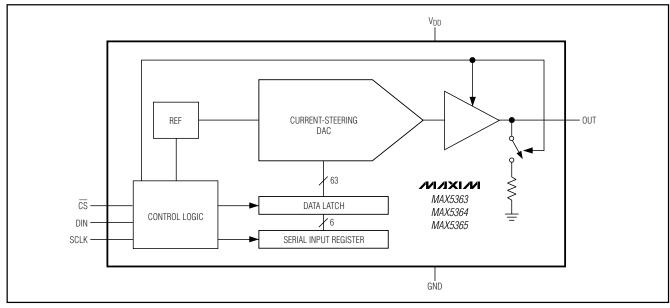

The MAX5363/MAX5364/MAX5365 voltage-output, 6-bit DACs offer full 6-bit performance with less than 1LSB integral nonlinearity error and less than 1LSB differential nonlinearity error, ensuring monotonic performance. The devices use a simple 3-wire, SPI/QSPI/ MICROWIRE-compatible serial interface that operates up to 10MHz. The MAX5363/MAX5364/MAX5365 include an internal reference, an output buffer, and three low-current shutdown modes, making these devices ideal for low-power, highly integrated applications. Figure 1 shows the devices' functional diagram.

#### **Analog Section**

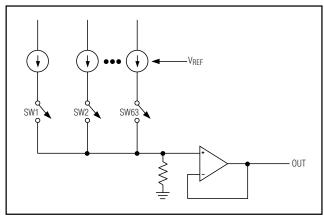

The MAX5363/MAX5364MAX5365 employ a current-steering DAC topology as shown in Figure 2. At the core of the DAC is a reference voltage-to-current converter (V/I) that generates a reference current. This current is mirrored to 63 equally weighted current sources. DAC switches control the outputs of these current mirrors so that only the desired fraction of the total current-mirror currents is steered to the DAC output. The current is then converted to a voltage across a resistor, and this voltage is buffered by the output buffer amplifier.

#### Output Voltage

Table 1 shows the relationship between the DAC code and the analog output voltage. The 6-bit DAC code is binary unipolar with 1LSB = ( $V_{REF}/64$ ). The MAX5363/MAX5364 have a full-scale output voltage of (+2V - 1LSB) and (+4V - 1LSB), respectively, set by the internal references. The MAX5365 has a full-scale output voltage of (0.9 ×  $V_{DD}$  - 1LSB).

#### **Output Buffer**

The DAC voltage output is an internally buffered unity-gain follower that slews up to  $\pm 0.4 \text{V/}\mu\text{s}$ . The output can swing from 0 to full scale. With a 1/4FS to 3/4FS output transition, the amplifier outputs typically settle to 1/2LSB in less than 5 $\mu$ s when loaded with 10k $\Omega$  in parallel with 50pF. The buffer amplifiers are stable with any

Figure 1. Functional Diagram

Figure 2. Current-Steering DAC Topology

#### Table 1. Unipolar Code Output Voltage

| DAC CODE | OUTPUT VOLTAGE  |              |                                 |  |  |  |

|----------|-----------------|--------------|---------------------------------|--|--|--|

| [D11–D6] | MAX5363 MAX5364 |              | MAX5365                         |  |  |  |

| 111 111  | 2V × (63/64)    | 4V × (63/64) | 0.9 × V <sub>DD</sub> × (63/64) |  |  |  |

| 100 000  | 1V              | 2V           | $0.9 \times V_{DD} / 2$         |  |  |  |

| 000 001  | 31mV            | 63mV         | 0.9 × V <sub>DD</sub> / 64      |  |  |  |

| 000 000  | 0               | 0            | 0                               |  |  |  |

combination of resistive loads >10k $\!\Omega$  and capacitive loads <50pF.

#### Power-On Reset

The MAX5363/MAX5364/MAX5365 have a power-on reset circuit to set the DAC's output to 0 when VDD is first applied or when VDD dips below 1.7V (typ). This ensures that unwanted DAC output voltages will not occur immediately following a system startup, such as after a loss of power. The output glitch on startup is typically less than 50mV.

#### Shutdown Mode

The MAX5363/MAX5364/MAX5365 include three software-controlled shutdown modes that reduce the supply current to <1 $\mu$ A. All internal circuitry is disabled, and a known impedance is placed from OUT to GND to ensure 0V while in shutdown. Table 2 details the three shutdown modes of operation.

# **Digital Section**

#### **3-Wire Serial Interface**

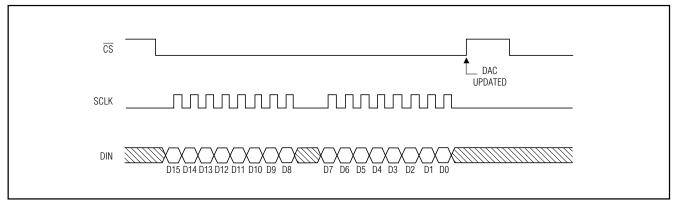

The MAX5363/MAX5364/MAX5365s' digital interface is a standard 3-wire connection compatible with SPI/QSPI/MICROWIRE interfaces. The chip-select input (CS) frames the serial data loading at the data-input pin (DIN). Immediately following CS's high-to-low transition, the data is shifted synchronously and latched into the input register on the rising edge of the serial clock input (SCLK). After 16 bits have been loaded into the serial

input register, it transfers its contents to the DAC latch on CS's low-to-high transition (Figure 3). Note that if CS is not kept low during the entire 16 SCLK cycles, data will be corrupted. In this case, reload the DAC latch with a new 16-bit word. The serial clock (SCLK) can idle either high or low between transitions. Figure 4 shows the complete 3-wire serial interface transmission. Table 3 lists serial interface mapping.

## \_Applications Information

# Device Powered by an External Reference

Since the MAX5365 generates an output voltage proportional to V<sub>DD</sub>, a noisy power supply will affect the accuracy of the on-board reference, thereby affecting the overall accuracy of the DAC. The circuit in Figure 5 rejects this power-supply noise by powering the device directly with a precision voltage reference, improving overall system accuracy. The MAX6103 (+3V, 75ppm) or the MAX6105 (+5V, 75ppm) precision voltage references are ideal choices due to the low power requirements of the MAX5365. This solution is also useful when the required full-scale output voltage is different from the available supply voltages.

#### **Digital Inputs and Interface Logic**

The digital interface for the 6-bit DAC is based on a 3-wire standard that is compatible with SPI, QSPI, and MICROWIRE interfaces. The three digital inputs (CS, DIN, and SCLK) load the digital input serially into the DAC.

All of the digital inputs include Schmitt-trigger buffers to accept slow-transition interfaces. This means that optocouplers can interface directly to the MAX5363/MAX5364/MAX5365 without additional external logic. The digital inputs are compatible with CMOS logic levels and can be driven with voltages up to +5.5V regardless of the supply voltage.

#### **Power-Supply Bypassing and Layout**

Careful PC board layout is important for best system performance. To reduce crosstalk and noise injection, keep analog and digital signals separate. To ensure that the ground return from GND to the supply ground is short and low impedance, a ground plane is recommended. Bypass VDD with a 0.1 $\mu$ F to ground as close as possible to the device. If the supply is excessively noisy, connect a 10 $\Omega$  resistor in series with the supply and VDD and add additional capacitance.

Table 2. Shutdown Modes

| DAC CODE<br>[D13 AND D12] | MODE     | OUTPUT RESISTANCE TO GROUND ( $\Omega$ ) | MAXIMUM SUPPLY<br>CURRENT (μA) |

|---------------------------|----------|------------------------------------------|--------------------------------|

| 01                        | Shutdown | 1k                                       | 1                              |

| 10                        | Shutdown | 100k                                     | 1                              |

| 11                        | Shutdown | 1M                                       | 1                              |

**Table 3. Serial Interface Mapping**

| 16-BIT SERIAL WORD |      |      | ANALOG | FUNCTION                   |                             |  |

|--------------------|------|------|--------|----------------------------|-----------------------------|--|

| MSB                |      | LSB  |        | OUTPUT                     | FUNCTION                    |  |

| XX00               | 0000 | 0000 | XXXX   | OV                         | Normal operation            |  |

| XX00               | 1111 | 11XX | XXXX   | V <sub>REF</sub> × (63/64) | Normal operation            |  |

| XX00               | 0000 | 01XX | XXXX   | V <sub>REF</sub> × (1/64)  | Normal operation            |  |

| XX00               | 1000 | 00XX | XXXX   | V <sub>REF</sub> × (32/64) | Normal operation            |  |

| XX01               | XXXX | XXXX | XXXX   | OV                         | Shutdown,<br>1kΩ to GND     |  |

| XX10               | XXXX | XXXX | XXXX   | OV                         | Shutdown,<br>100kΩ to GND   |  |

| XX11               | XXXX | XXXX | XXXX   | OV                         | Shutdown, $1M\Omega$ to GND |  |

X = Don't care

Figure 3. 3-Wire Serial Interface Timing Diagram

Figure 4. Complete 3-Wire Serial Interface Transmission

# +3.2V TO +12V IN MAX6103 OUT GND WOD TO 10 +2.7V DIN MAX5365 SCLK GND TO 10 +2.7V

Figure 5. Powering the MAX5365 with a Precision Voltage Reference

\_Chip Information

TRANSISTOR COUNT: 2160

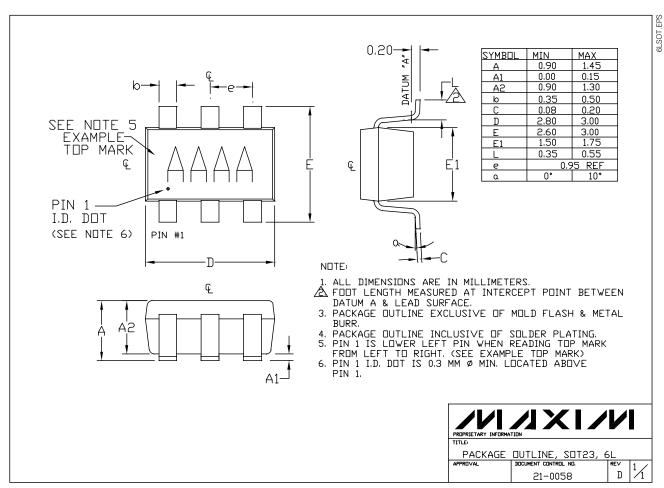

## Package Information

MIXIM

**NOTES**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600