# ABSOLUTE MAXIMUM RATINGS

(Note 1)

| V <sub>IN</sub> to GND                  | 0.3V to 6V    |

|-----------------------------------------|---------------|

| V <sub>OUT</sub> to GND                 | 0.3V to 6V    |

| SHDN to GND                             | 0.3V to 6V    |

| V <sub>OUT</sub> Short-Circuit Duration | Indefinite    |

| Operating Temperature Range             |               |

| Commercial                              | 0°C to 70°C   |

| Industrial                              | 40°C to 85°C  |

| Storage Temperature Range               | 65°C to 150°C |

| Lead Temperature (Soldering, 10 se      | c)300°C       |

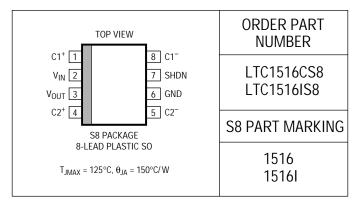

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 2V to 5V, C1 = C2 = 0.22 $\mu$ F,  $C_{IN}$  =  $C_{OUT}$  = 10 $\mu$ F,  $T_{MIN}$  to  $T_{MAX}$  unless otherwise specified (Note 3).

| SYMBOL                     | PARAMETER                     | CONDITIONS                                                             |   | MIN             | TYP   | MAX | UNITS |

|----------------------------|-------------------------------|------------------------------------------------------------------------|---|-----------------|-------|-----|-------|

| $\overline{V_{\text{IN}}}$ | Input Voltage                 |                                                                        | • | 2               |       | 5   | V     |

| $\overline{V_{OUT}}$       | Output Voltage                | $2V \le V_{IN} \le 5V$ , $I_{OUT} \le 20$ mA                           | • | 4.8             |       | 5.2 | V     |

|                            |                               | $3V \le V_{IN} \le 3.6V$ , $I_{OUT} \le 50$ mA                         | • | 4.8             |       | 5.2 | V     |

|                            |                               | $3.6V \le V_{IN} \le 5V$ , $I_{OUT} \le 50$ mA, $T_A = 25$ °C (Note 2) |   | 4.8             |       | 5.2 | V     |

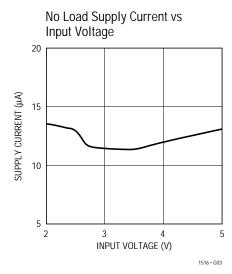

| I <sub>CC</sub>            | Supply Current                | $2V \le V_{IN} \le 5V$ , $I_{OUT} = 0mA$ , $SHDN = 0V$                 | • |                 | 12    | 20  | μΑ    |

|                            |                               | $2V \le V_{IN} \le 5V$ , $I_{OUT} = 0mA$ , $SHDN = V_{IN}$             | • |                 | 0.005 | 1   | μΑ    |

|                            | Output Ripple                 | Full Load                                                              |   |                 | 100   |     | mV    |

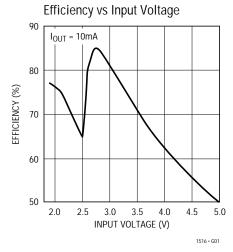

|                            | Efficiency                    | $V_{IN} = 3V$ , $I_{OUT} = 20mA$                                       |   |                 | 82    |     | %     |

| f <sub>OSC</sub>           | Switching Frequency           | Full Load                                                              |   |                 | 600   |     | kHz   |

| $V_{IH}$                   | SHDN Input Threshold          |                                                                        | • | $(0.7)(V_{IN})$ |       |     | V     |

| $\overline{V_{IL}}$        |                               |                                                                        | • |                 |       | 0.4 | V     |

| I <sub>IH</sub>            | SHDN Input Current            | V <sub>SHDN</sub> = V <sub>IN</sub>                                    | • | -1              |       | 1   | μΑ    |

| I <sub>IL</sub>            |                               | V <sub>SHDN</sub> = 0V                                                 | • | -1              |       | 1   | μΑ    |

| t <sub>ON</sub>            | V <sub>OUT</sub> Turn-On Time | $V_{IN} = 3V$ , $I_{OUT} = 0mA$ (Note 3)                               |   |                 | 500   |     | μs    |

The lacktriangle denotes specifications which apply over the full operating temperature range.

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired

Note 2: At input voltages > 3.6V and ambient temperatures >70°C, continuous power dissipation must be derated to maintain junction temperatures below 125°C. Derate 6mW/°C above 70°C in SO-8.

Note 3: The LTC1516 is tested with the capacitors shown in Figure 1.

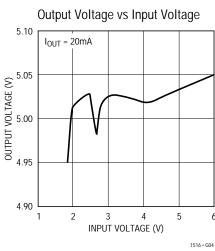

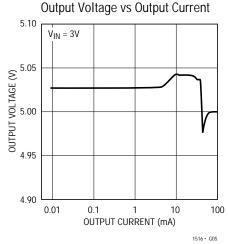

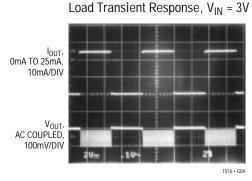

# TYPICAL PERFORMANCE CHARACTERISTICS

# PIN FUNCTIONS

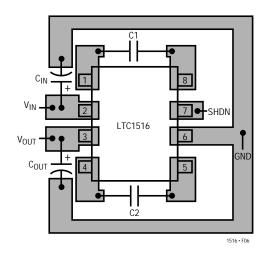

C1+ (Pin 1): Flying Capacitor 1, Positive Terminal.

$V_{\mbox{\scriptsize IN}}$  (Pin 2): Input Supply Voltage.

V<sub>OUT</sub> (Pin 3): 5V Output Voltage (V<sub>OUT</sub> = 0V in Shutdown).

C2+ (Pin 4): Flying Capacitor 2, Positive Terminal.

C2<sup>-</sup> (Pin 5): Flying Capacitor 2, Negative Terminal.

GND (Pin 6): Ground.

SHDN (Pin 7): Active High CMOS Logic-Level Shutdown Input.

C1<sup>-</sup> (Pin 8): Flying Capacitor 1, Negative Terminal.

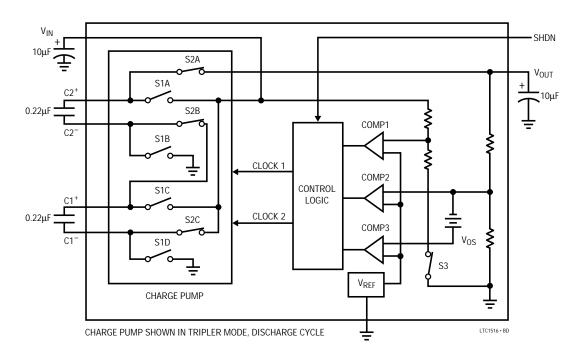

## **BLOCK DIAGRAM**

# APPLICATIONS INFORMATION

### Operation

The LTC1516 uses a switched capacitor charge pump to boost  $V_{IN}$  from 2V to 5V to a regulated 5V  $\pm 4\%$  output voltage. Regulation is achieved by sensing the output voltage through an internal resistor divider and enabling the charge pump when the output voltage droops below the lower trip point of COMP2. When the charge pump is enabled, a 2-phase, nonoverlapping clock controls the charge pump switches. Clock 1 closes the S1 switches which enable the flying capacitors, C1 and C2, to charge up to the V<sub>IN</sub> voltage. Clock 2 closes the S2 switches which stack C1 and C2 in series with V<sub>IN</sub> and connect the top plate of C2 to the output capacitor at V<sub>OUT</sub>. This sequence of charging and discharging continues at a free-running frequency of 600kHz (typ) until the output has risen to the upper trip point of COMP2 and the charge pump is disabled. When the charge pump is disabled, the LTC1516 draws only  $8\mu A$  (typ) from  $V_{IN}$  which provides high efficiency at low load conditions.

To achieve the highest efficiency over the entire  $V_{\text{IN}}$  range, the LTC1516 operates as either a doubler or a tripler

depending on  $V_{IN}$  and output load conditions. COMP1 and COMP2 determine whether the charge pump is in doubler mode or tripler mode. COMP1 forces the part into tripler mode if  $V_{IN}$  is < 2.55V, regardless of output load. When  $V_{IN}$  is > 2.55V, the part will be in doubler mode using only C2 as a flying capacitor. In doubler mode, if the output droops by 50mV under heavy loads, COMP3 will force the charge pump into tripler mode until  $V_{OUT}$  climbs above the upper trip point of COMP3. Under these  $V_{IN}$  and load conditions, the nominal  $V_{OUT}$  will be approximately 50mV lower than the no load nominal  $V_{OUT}$ . This method of sensing  $V_{IN}$  and output load results in efficiency greater than 80% with  $V_{IN}$  between 2.5V and 3V.

In shutdown mode, all circuitry is turned off and the part draws only leakage current (<1 $\mu A$ ) from the  $V_{IN}$  supply.  $V_{OUT}$  is also disconnected from  $V_{IN}$ . The SHDN pin is a CMOS input with a threshold of approximately  $V_{IN}/2$ ; however, the SHDN pin can be driven by logic levels that exceed the  $V_{IN}$  voltage. The part enters shutdown mode when a logic high is applied to the SHDN pin. The SHDN pin cannot float; it must be driven with a logic high or low.

## APPLICATIONS INFORMATION

### Short-Circuit/Thermal Protection

During short-circuit conditions, the LTC1516 will draw between 200mA and 400mA from  $V_{IN}$  causing a rise in the junction temperature. On-chip thermal shutdown circuitry disables the charge pump once the junction temperature exceeds 135°C, and reenables the charge pump once the junction temperature falls back to 115°C. The LTC1516 will cycle in and out of thermal shutdown indefinitely without latchup or damage until the  $V_{OUT}$  short is removed.

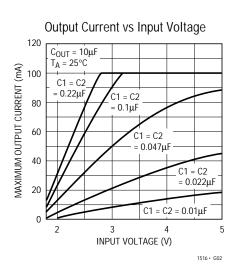

### Capacitor Selection

For best performance, it is recommended that low ESR capacitors be used for both  $C_{IN}$  and  $C_{OUT}$  to reduce noise and ripple. The  $C_{IN}$  and  $C_{OUT}$  capacitors should be either ceramic or tantalum and should be  $10\mu F$  or greater. If the input source impedance is very low,  $C_{IN}$  may not be needed. Increasing the size of  $C_{OUT}$  to  $22\mu F$  or greater will reduce output voltage ripple.

Ceramic or tantalum capacitors are recommended for the flying caps C1 and C2 with values in the range of  $0.1\mu F$  to  $1\mu F$ . Note that large value flying caps (>  $0.22\mu F$ ) will increase output ripple unless  $C_{OUT}$  is also increased. For very low load applications, C1 and C2 may be reduced to  $0.01\mu F$  to  $0.047\mu F$ . This will reduce output ripple at the expense of efficiency and maximum output current.

### **Output Ripple**

Normal LTC1516 operation produces voltage ripple on the  $V_{OUT}$  pin. Output voltage ripple is required for the LTC1516 to regulate. Low frequency ripple exists due to the hysteresis in the sense comparator and propagation delays in the charge pump enable/disable circuits. High frequency ripple is also present mainly due to ESR (Equivalent Series Resistance) in the output capacitor. Typical output ripple under maximum load is  $100 \text{mV}_{P-P}$  with a low ESR  $10 \mu F$  output capacitor.

The magnitude of the ripple voltage depends on several factors. High input voltages ( $V_{IN} > 3.3V$ ) increase the output ripple since more charge is delivered to  $C_{OUT}$  per clock cycle. Large C1 and C2 flying capacitors (>0.22 $\mu$ F) also increase ripple for the same reason. Large output current load and/or a small output capacitor (<10 $\mu$ F) results in

higher ripple due to higher output voltage dV/dt. High ESR capacitors (ESR >  $0.5\Omega$ ) on the output pin cause high frequency voltage spikes on  $V_{OUT}$  with every clock cycle.

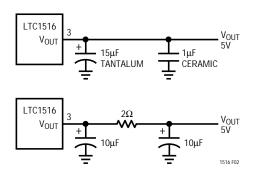

There are several ways to reduce the output voltage ripple. A larger  $C_{OUT}$  capacitor (22 $\mu$ F or greater) will reduce both the low and high frequency ripple due to the lower  $C_{OUT}$  charging and discharging dV/dt and the lower ESR typically found with higher value (larger case size) capacitors. A low ESR ceramic output capacitor will minimize the high frequency ripple, but will not reduce the low frequency ripple unless a high capacitance value is chosen. A reasonable compromise is to use a  $10\mu$ F to  $22\mu$ F tantalum capacitor in parallel with a  $1\mu$ F to  $3.3\mu$ F ceramic capacitor on  $V_{OUT}$  to reduce both the low and high frequency ripple. An RC filter may also be used to reduce high frequency voltage spikes (see Figure 2).

In low load or high  $V_{IN}$  applications, smaller values for C1 and C2 may be used to reduce output ripple. The smaller C1 and C2 flying capacitors (0.022 $\mu F$  to 0.1 $\mu F$ ) deliver less charge per clock cycle to the output capacitor resulting in lower output ripple. However, the smaller value flying caps also reduce the maximum  $I_{OUT}$  capability as well as efficiency.

Figure 2. Output Ripple Reduction Techniques

#### **Inrush Currents**

During normal operation,  $V_{IN}$  will experience current transients in the 100mA to 200mA range whenever the charge pump is enabled. During start-up, these inrush currents may approach 500mA. For this reason, it is important to minimize the source resistance between the input supply and the  $V_{IN}$  pin to prevent start-up problems and large input voltage transients.

### APPLICATIONS INFORMATION

Ultralow Quiescent Current ( $I_Q < 5\mu A$ ) Regulated Supply

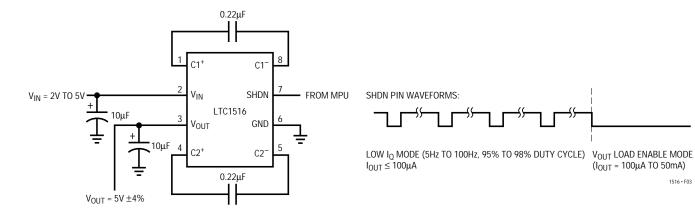

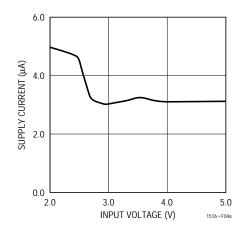

The LTC1516 contains an internal resistor divider (refer to Block Diagram) which draws only 1.5 $\mu$ A (typ) from V<sub>OUT</sub>. During no-load conditions, the internal load causes a droop rate of only 150mV per second on V<sub>OUT</sub> with C<sub>OUT</sub> = 10 $\mu$ F. Applying a 5Hz to 100Hz, 95% to 98% duty cycle signal to the SHDN pin ensures that the circuit of Figure 3 comes out of shutdown frequently enough to maintain regulation during no-load or low-load conditions. Since the part spends nearly all of its time in shutdown, the no-load quiescent current (see Figure 4a) is approximately equal to (V<sub>OUT</sub>)(1.5 $\mu$ A)/(V<sub>IN</sub>)(Efficiency).

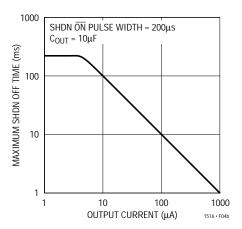

The LTC1516 must be out of shutdown for a minimum duration of 200 $\mu$ s to allow enough time to sense the output and keep it in regulation. As the V<sub>OUT</sub> load current increases, the frequency with which the part is taken out of shutdown must also be increased to prevent V<sub>OUT</sub> from drooping below 4.8V during the OFF phase (see Figure 4b). A 100Hz 98% duty cycle signal on the SHDN pin ensures proper regulation with load currents as high as 100 $\mu$ A. When load current greater than 100 $\mu$ A is needed, the SHDN pin must be forced low as in normal operation. The typical no-load supply current for this circuit with V<sub>IN</sub> = 3V is only 3.2 $\mu$ A.

Figure 3. Ultralow Quiescent Current (<5μA) Regulated Supply

Figure 4a. No Load I<sub>CC</sub> vs Input Voltage for Circuit in Figure 3

Figure 4b. Maximum SHDN OFF Time vs Output Load Current for Ultralow  $I_0$  Operation

### APPLICATIONS INFORMATION

### Paralleling Devices

Two or more LTC1516's may be connected in parallel to provide higher output currents. The  $V_{IN}$ ,  $V_{OUT}$ , GND and SHDN pins may be tied together, but the C1 and C2 pins must be kept separate (see Figure 5). Separate  $C_{IN}$  and  $C_{OUT}$  capacitors may be required to reduce output noise and ripple if the paralleled devices cannot be kept close together. Otherwise, single  $C_{IN}$  and  $C_{OUT}$  capacitors may be used with each being  $2\times$  (or  $3\times$  if three parts are paralleled, etc.) in value.

Figure 5. Paralleling Devices

### **General Layout Considerations**

Due to the high switching frequency and high transient currents produced by the LTC1516, careful board layout is a must. A clean board layout using a ground plane and short connections to all capacitors will improve performance and ensure proper regulation under all conditions (refer to Figure 6).

Figure 6. Suggested Component Placement for LTC1516

## TYPICAL APPLICATIONS

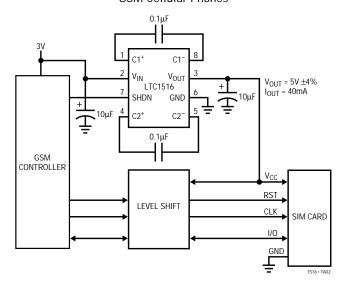

#### Fault-Protected SIM Interface Supply for **GSM Cellular Phones**

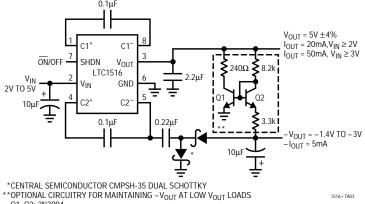

#### Generating 5V and a Negative Supply

Q1, Q2: 2N3904

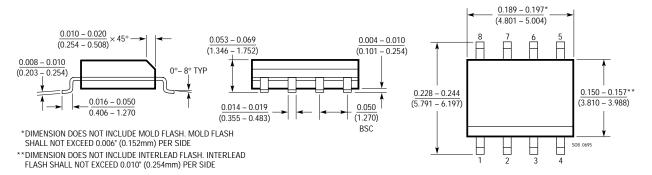

# PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

#### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                 | COMMENTS                                        |  |

|-------------|-------------------------------------------------------------|-------------------------------------------------|--|

| LT®1054     | 100mA Switched Capacitor Converter                          | Includes Reference and Amplifier for Regulation |  |

| LTC1144     | 20mA Switched Capacitor Converter for Up to 20V Inputs      | Includes Micropower Shutdown (8µA)              |  |

| LTC1261     | Positive to Negative Regulated Switched Capacitor Converter | Low Noise (5mV) Output for Up to 10mA Loads     |  |

| LTC1262     | 5V to 12V Regulated Switched Capacitor Converter            | Up to 30mA at Regulated Output                  |  |

| LTC1550/51  | Low Noise Switched Capacitor Regulated Converter            | Provides – 4.1V at 20mA with <1mV Ripple        |  |