Contents L6206Q

# **Contents**

| 1  | Elec  | Electrical data                                        |  |  |  |  |

|----|-------|--------------------------------------------------------|--|--|--|--|

|    | 1.1   | Absolute maximum ratings                               |  |  |  |  |

|    | 1.2   | Recommended operating conditions                       |  |  |  |  |

| 2  | Pin d | connection                                             |  |  |  |  |

| 3  | Elec  | trical characteristics6                                |  |  |  |  |

| 4  | Circ  | uit description                                        |  |  |  |  |

|    | 4.1   | Power stages and charge pump                           |  |  |  |  |

|    | 4.2   | Logic inputs 9                                         |  |  |  |  |

|    | 4.3   | Non-dissipative overcurrent detection and protection11 |  |  |  |  |

|    | 4.4   | Thermal protection                                     |  |  |  |  |

| 5  | Appl  | ication information                                    |  |  |  |  |

| 6  | Para  | Ileled operation                                       |  |  |  |  |

| 7  | Outp  | out current capability and IC power dissipation 21     |  |  |  |  |

| 8  | Ther  | mal management                                         |  |  |  |  |

| 9  | Elec  | trical characteristics curves                          |  |  |  |  |

| 10 | Pack  | age information                                        |  |  |  |  |

|    | 10.1  | VFQFPN48 (7 x 7 x 1.0 mm) package information          |  |  |  |  |

| 11 | Orde  | er codes 26                                            |  |  |  |  |

| 12 | Revi  | sion history                                           |  |  |  |  |

L6206Q Electrical data

## 1 Electrical data

## 1.1 Absolute maximum ratings

**Table 1. Absolute maximum ratings**

| Symbol                                         | Parameter                                                                                                                                                                                        | Test condition                                                                | Value               | Unit |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|------|

| V <sub>S</sub>                                 | Supply voltage                                                                                                                                                                                   | $V_{SA} = V_{SB} = V_{S}$                                                     | 60                  | V    |

| V <sub>OD</sub>                                | Differential voltage between VS <sub>A</sub> ,<br>OUT1 <sub>A</sub> , OUT2 <sub>A</sub> , SENSE <sub>A</sub> and VS <sub>B</sub> ,<br>OUT1 <sub>B</sub> , OUT2 <sub>B</sub> , SENSE <sub>B</sub> | $V_{SA} = V_{SB} = V_S = 60 \text{ V};$<br>$V_{SENSEA} = V_{SENSEB} =$<br>GND | 60                  | V    |

| V <sub>OCDA</sub> ,<br>V <sub>OCDB</sub>       | OCD pins voltage range                                                                                                                                                                           | -                                                                             | -0.3 to +10         | V    |

| V <sub>PROGCLA</sub> ,<br>V <sub>PROGCLB</sub> | PROGCL pins voltage range                                                                                                                                                                        | -                                                                             | -0.3 to +7          | V    |

| V <sub>BOOT</sub>                              | Bootstrap peak voltage                                                                                                                                                                           | $V_{SA} = V_{SB} = V_{S}$                                                     | V <sub>S</sub> + 10 | ٧    |

| $V_{IN}, V_{EN}$                               | Input and enable voltage range                                                                                                                                                                   | -                                                                             | -0.3 to +7          | V    |

| V <sub>SENSEA</sub> ,<br>V <sub>SENSEB</sub>   | Voltage range at pins SENSE <sub>A</sub> and SENSE <sub>B</sub>                                                                                                                                  | -                                                                             | -1 to +4            | V    |

| I <sub>S(peak)</sub>                           | Pulsed supply current (for each VS pin), internally limited by the overcurrent protection                                                                                                        | $V_{SA} = V_{SB} = V_S;$<br>$t_{PULSE} < 1 \text{ ms}$                        | 7.1                 | Α    |

| I <sub>S</sub>                                 | RMS supply current (for each VS pin)                                                                                                                                                             | $V_{SA} = V_{SB} = V_{S}$                                                     | 2.5                 | Α    |

| T <sub>stg</sub> , T <sub>OP</sub>             | Storage and operating temperature range                                                                                                                                                          | -                                                                             | -40 to 150          | °C   |

## 1.2 Recommended operating conditions

Table 2. Recommended operating conditions

| Symbol                | Parameter                                                                                                                                                                                        | Test condition                                                                                    | Min. | Max. | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>S</sub>        | Supply voltage                                                                                                                                                                                   | $V_{SA} = V_{SB} = V_{S}$                                                                         | 8    | 52   | V    |

| V <sub>OD</sub>       | Differential voltage between VS <sub>A</sub> ,<br>OUT1 <sub>A</sub> , OUT2 <sub>A</sub> , SENSE <sub>A</sub> and VS <sub>B</sub> ,<br>OUT1 <sub>B</sub> , OUT2 <sub>B</sub> , SENSE <sub>B</sub> | V <sub>SA</sub> = V <sub>SB</sub> = V <sub>S</sub> ;<br>V <sub>SENSEA</sub> = V <sub>SENSEB</sub> |      | 52   | V    |

| V <sub>SENSEA</sub> , | Voltage range at pins SENSE <sub>A</sub> and                                                                                                                                                     | Pulsed t <sub>W</sub> < t <sub>rr</sub>                                                           | -6   | 6    | V    |

| V <sub>SENSEB</sub>   | SENSE <sub>B</sub>                                                                                                                                                                               | DC                                                                                                | -1   | 1    | V    |

| I <sub>OUT</sub>      | RMS output current                                                                                                                                                                               | -                                                                                                 |      | 2.5  | Α    |

| T <sub>j</sub>        | Operating junction temperature                                                                                                                                                                   | -                                                                                                 | -25  | +125 | °C   |

| f <sub>sw</sub>       | Switching frequency                                                                                                                                                                              | -                                                                                                 |      | 100  | kHz  |

Pin connection L6206Q

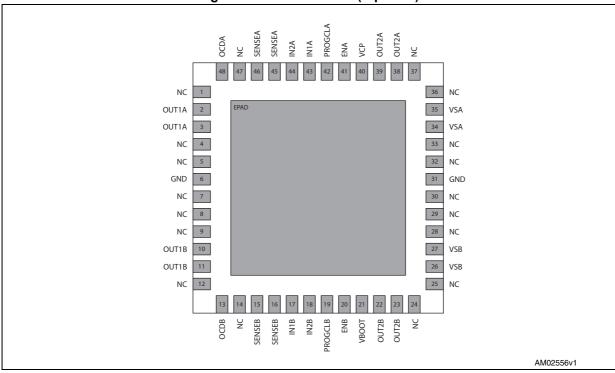

## 2 Pin connection

Figure 2. Pin connection (top view)

1. The exposed PAD must be connected to GND pin.

Table 3. Pin description

| Pin    | Name   | Туре              | Function                                                                                                                                                                             |

|--------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43     | IN1A   | Logic input       | Bridge A logic input 1.                                                                                                                                                              |

| 44     | IN2A   | Logic input       | Bridge A logic input 2.                                                                                                                                                              |

| 45, 46 | SENSEA | Power supply      | Bridge A source pin. This pin must be connected to power ground directly or through a sensing power resistor.                                                                        |

| 48     | OCDA   | Open-drain output | Bridge A overcurrent detection and thermal protection pin. An internal open-drain transistor pulls to GND when overcurrent on bridge A is detected or in case of thermal protection. |

| 2, 3   | OUT1A  | Power output      | Bridge A output 1.                                                                                                                                                                   |

| 6, 31  | GND    | GND               | Signal ground terminals. These pins are also used for heat dissipation toward the PCB.                                                                                               |

| 10, 11 | OUT1B  | Power output      | Bridge B output 1.                                                                                                                                                                   |

| 13     | OCDB   | Open-drain output | Bridge B overcurrent detection and thermal protection pin. An internal open-drain transistor pulls to GND when overcurrent on bridge B is detected or in case of thermal protection. |

| 15, 16 | SENSEB | Power supply      | Bridge B source pin. This pin must be connected to power ground directly or through a sensing power resistor.                                                                        |

| 17     | IN1B   | Logic input       | Bridge B input 1                                                                                                                                                                     |

L6206Q Pin connection

#### Table 3. Pin description (continued)

| Pin    | Name    | Туре           | Function                                                                                                                                                                                                                                               |

|--------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18     | IN2B    | Logic input    | Bridge B input 2                                                                                                                                                                                                                                       |

| 19     | PROGCLB | R pin          | Bridge B overcurrent level programming. A resistor connected between this pin and ground sets the programmable current limiting value for bridge B. By connecting this pin to ground the maximum current is set. This pin cannot be left unconnected.  |

| 20     | ENB     | Logic input    | Bridge B enable. LOW logic level switches OFF all Power MOSFETs of bridge B. If not used, it must be connected to +5 V.                                                                                                                                |

| 21     | VBOOT   | Supply voltage | Bootstrap voltage needed for driving the upper Power MOSFETs of both bridge A and bridge B.                                                                                                                                                            |

| 22, 23 | OUT2B   | Power output   | Bridge B output 2.                                                                                                                                                                                                                                     |

| 26, 27 | VSB     | Power supply   | Bridge B power supply voltage. It must be connected to the supply voltage together with pin VSA.                                                                                                                                                       |

| 34, 35 | VSA     | Power supply   | Bridge A power supply voltage. It must be connected to the supply voltage together with pin VSB.                                                                                                                                                       |

| 38, 39 | OUT2A   | Power output   | Bridge A output 2.                                                                                                                                                                                                                                     |

| 40     | VCP     | Output         | Charge pump oscillator output.                                                                                                                                                                                                                         |

| 41     | ENA     | Logic input    | Bridge A enable. LOW logic level switches OFF all Power MOSFETs of bridge A. If not used, it must be connected to +5 V.                                                                                                                                |

| 42     | PROGCLA | R pin          | Bridge A overcurrent level programming. A resistor connected between this pin and ground sets the programmable current limiting value for bridge A. By connecting this pin to ground, the maximum current is set. This pin cannot be left unconnected. |

Electrical characteristics L6206Q

# 3 Electrical characteristics

$\rm V_S$  = 48 V,  $\rm T_A$  = 25 °C, unless otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                | Parameter                                             | Test condition                                                | Min.  | Тур. | Max. | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------|-------|------|------|------|

| V <sub>Sth(ON)</sub>  | Turn-on threshold                                     | -                                                             | 6.6   | 7    | 7.4  | V    |

| V <sub>Sth(OFF)</sub> | Turn-off threshold                                    | -                                                             | 5.6   | 6    | 6.4  | V    |

| I <sub>S</sub>        | Quiescent supply current                              | All bridges OFF; $T_j = -25$ °C to 125 °C <sup>(1)</sup>      | -     | 5    | 10   | mA   |

| T <sub>j(OFF)</sub>   | Thermal shutdown temperature                          | -                                                             | -     | 165  | -    | °C   |

|                       | Output                                                | DMOS transistors                                              | •     |      | •    |      |

|                       | High side quitab ON resistance                        | T <sub>j</sub> = 25 °C                                        | -     | 0.34 | 0.4  |      |

| Б                     | High-side switch ON resistance                        | T <sub>j</sub> = 125 °C <sup>(1)</sup>                        | -     | 0.53 | 0.59 |      |

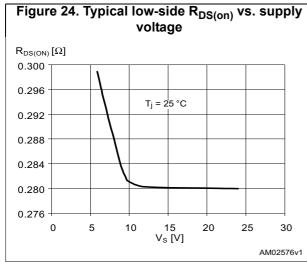

| $R_{DS(ON)}$          | Low side switch ON registeres                         | T <sub>j</sub> = 25 °C                                        | -     | 0.28 | 0.34 | Ω    |

|                       | Low-side switch ON resistance                         | T <sub>j</sub> = 125 °C <sup>(1)</sup>                        | -     | 0.47 | 0.53 |      |

|                       | Lookogo gurrant                                       | EN = low; OUT = V <sub>S</sub>                                | -     | -    | 2    | mA   |

| I <sub>DSS</sub>      | Leakage current                                       | EN = low; OUT = GND                                           | -0.15 | -    | -    | mA   |

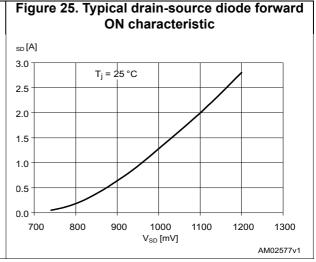

|                       | Soul                                                  | rce drain diodes                                              | •     |      | •    |      |

| V <sub>SD</sub>       | Forward ON voltage                                    | I <sub>SD</sub> = 2.5 A, EN = LOW                             | -     | 1.15 | 1.3  | V    |

| t <sub>rr</sub>       | Reverse recovery time                                 | I <sub>f</sub> = 2.5 A                                        | -     | 300  | -    | ns   |

| t <sub>fr</sub>       | Forward recovery time                                 | -                                                             | -     | 200  | -    | ns   |

|                       |                                                       | Logic input                                                   |       |      |      |      |

| V <sub>IL</sub>       | Low level logic input voltage                         | -                                                             | -0.3  | -    | 8.0  | V    |

| V <sub>IH</sub>       | High level logic input voltage                        | -                                                             | 2     | -    | 7    | V    |

| I <sub>IL</sub>       | Low level logic input current                         | GND logic input voltage                                       | -10   | -    | -    | μΑ   |

| I <sub>IH</sub>       | High level logic input current                        | 7 V logic input voltage                                       | -     | -    | 10   | μA   |

| V <sub>th(ON)</sub>   | Turn-on input threshold                               | -                                                             | -     | 1.8  | 2    | V    |

| V <sub>th(OFF)</sub>  | Turn-off input threshold                              | -                                                             | 0.8   | 1.3  | -    | V    |

| V <sub>th(HYS)</sub>  | Input threshold hysteresis                            | -                                                             | 0.25  | 0.5  | -    | V    |

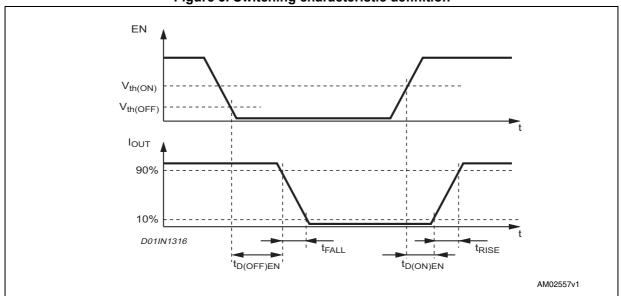

|                       | Switching characteristics                             |                                                               |       |      |      |      |

| t <sub>D(on)EN</sub>  | Enable pin to out, turn ON delay time <sup>(2)</sup>  | I <sub>LOAD</sub> = 2.5 A, resistive load                     | 100   | 250  | 400  | ns   |

| t <sub>D(on)IN</sub>  | Input pin to out, turn ON delay time                  | I <sub>LOAD</sub> = 2.5 A, resistive load (deadtime included) | -     | 1.6  | -    | μs   |

| t <sub>RISE</sub>     | Output rise time <sup>(2)</sup>                       | I <sub>LOAD</sub> = 2.5 A, resistive load                     | 40    | -    | 250  | ns   |

| t <sub>D(off)EN</sub> | Enable pin to out, turn OFF delay time <sup>(2)</sup> | I <sub>LOAD</sub> = 2.5 A, resistive load                     | 300   | 550  | 800  | ns   |

L6206Q Electrical characteristics

Table 4. Electrical characteristics (continued)

| Symbol                | Parameter                                    | Test condition                                                                                                                   | Min. | Тур.                | Max. | Unit        |

|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------------|

| t <sub>D(off)IN</sub> | Input pin to out, turn OFF delay time        | I <sub>LOAD</sub> = 2.5 A, resistive load                                                                                        | -    | 600                 | -    | ns          |

| t <sub>FALL</sub>     | Output fall time <sup>(2)</sup>              | I <sub>LOAD</sub> = 2.5 A, resistive load                                                                                        | 40   | -                   | 250  | ns          |

| t <sub>DT</sub>       | Deadtime protection                          | -                                                                                                                                | 0.5  | 1                   | -    | μs          |

| f <sub>CP</sub>       | Charge pump frequency                        | -25 °C < T <sub>j</sub> < 125 °C                                                                                                 | -    | 0.6                 | 1    | MHz         |

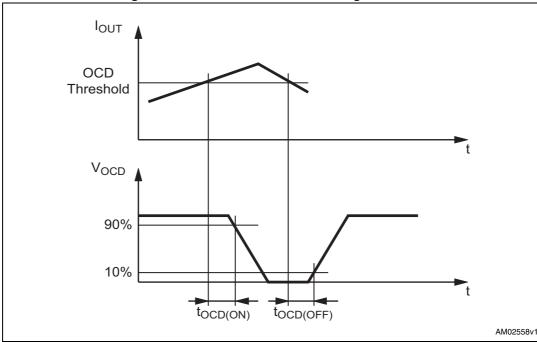

| Overcurre             | Overcurrent detection                        |                                                                                                                                  |      |                     |      |             |

| I <sub>s over</sub>   | Input supply overcurrent detection threshold | -25 °C < $T_j$ < 125 °C; $R_{CL}$ = 39 kΩ<br>-25 °C < $T_j$ < 125 °C; $R_{CL}$ = 5 kΩ<br>-25 °C < $T_j$ < 125 °C; $R_{CL}$ = GND | -    | 0.57<br>4.42<br>5.6 | -    | A<br>A<br>A |

| R <sub>OPDR</sub>     | Open-drain ON resistance                     | I = 4 mA                                                                                                                         | -    | 40                  | 60   | Ω           |

| t <sub>OCD(ON)</sub>  | OCD turn-on delay time <sup>(3)</sup>        | I = 4 mA; C <sub>EN</sub> < 100 pF                                                                                               | -    | 200                 | -    | ns          |

| t <sub>OCD(OFF)</sub> | OCD turn-off delay time <sup>(3)</sup>       | I = 4 mA; C <sub>EN</sub> < 100 pF                                                                                               | -    | 100                 | -    | ns          |

- 1. Tested at 25 °C in a restricted range and guaranteed by characterization.

- 2. See Figure 3.

- 3. See Figure 4.

Figure 3. Switching characteristic definition

Electrical characteristics L6206Q

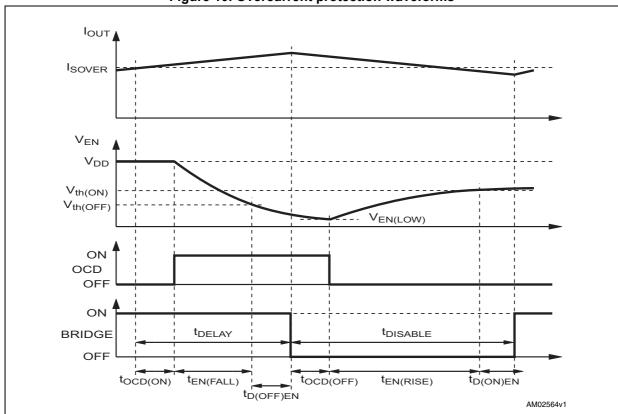

Figure 4. Overcurrent detection timing definition

L6206Q Circuit description

### 4 Circuit description

#### 4.1 Power stages and charge pump

The L6206Q device integrates two independent Power MOS full bridges. Each power MOS has an  $R_{DS(ON)}$  = 0.3  $\Omega$  (typical value at 25 °C) with intrinsic fast freewheeling diode. Cross conduction protection is implemented by using a deadtime (t<sub>DT</sub> = 1  $\mu$ s typical value) set by an internal timing circuit between the turn-off and turn-on of two Power MOSFETs in one leg of a bridge.

Pins VS<sub>A</sub> and VS<sub>B</sub> must be connected together to the supply voltage (V<sub>S</sub>).

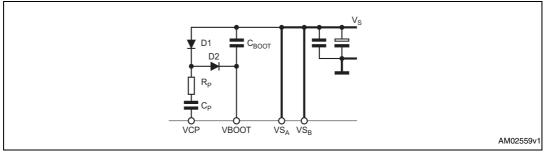

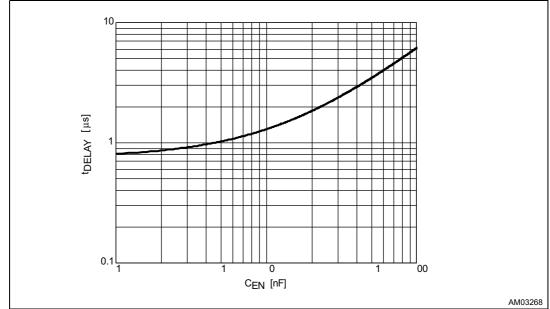

Using an N-channel Power MOSFET for the upper transistors in the bridge requires a gate drive voltage above the power supply voltage. The bootstrapped supply  $(V_{BOOT})$  is obtained through an internal oscillator and few external components to realize a charge pump circuit, as shown in *Figure 5*. The oscillator output (pin VCP) is a square wave at 600 kHz (typically) with 10 V amplitude. Recommended values/part numbers for the charge pump circuit are shown in *Table 5*.

Component

Value

$C_{BOOT}$  220 nF

$C_P$  10 nF

$R_P$  100 Ω

D1

1N4148

D2

1N4148

Table 5. Charge pump external component values

#### 4.2 Logic inputs

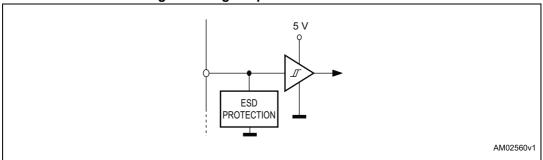

Pins IN1<sub>A</sub>, IN2<sub>A</sub>, IN1<sub>B</sub>, IN2<sub>B</sub>, EN<sub>A</sub>, and EN<sub>B</sub> are TTL/CMOS and  $\mu$ C compatible logic inputs. The internal structure is shown in *Figure 6*. The typical values for turn-on and turn-off thresholds are respectively V<sub>th(ON)</sub> = 1.8 V and V<sub>th(OFF)</sub> = 1.3 V.

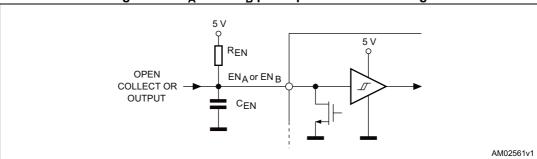

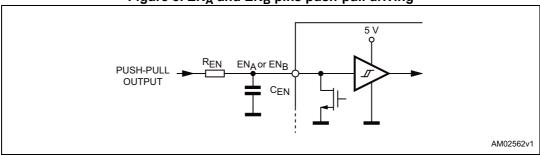

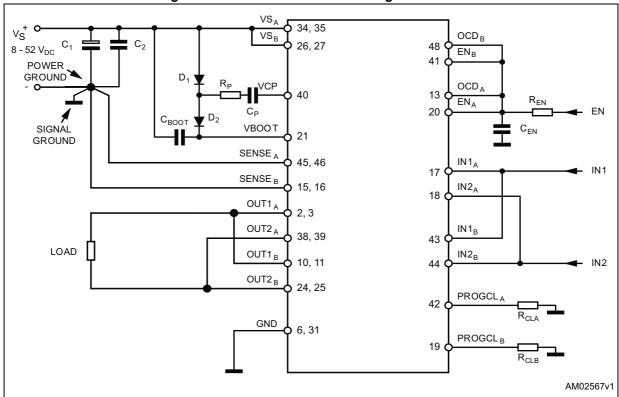

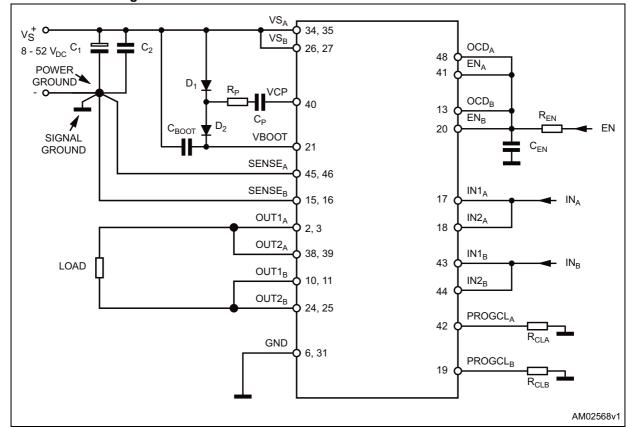

Pins  $EN_A$  and  $EN_B$  are commonly used to implement overcurrent and thermal protection by connecting them respectively to the outputs  $OCD_A$  and  $OCD_B$ , which are open-drain outputs. If this type of connection is chosen, particular care needs to be taken in driving these pins. Two configurations are shown in *Figure 7* and *Figure 8*. If driven by an open-drain (collector) structure, a pull-up resistor  $R_{EN}$  and a capacitor  $C_{EN}$  are connected as

DocID022028 Rev 4

Circuit description L6206Q

shown in Figure 7. If the driver is a standard push-pull structure the resistor  $R_{EN}$  and the capacitor  $C_{EN}$  are connected as shown in Figure 8. The resistor  $R_{EN}$  should be chosen in the range from 2.2 k $\Omega$  to 180 k $\Omega$ . Recommended values for  $R_{EN}$  and  $C_{EN}$  are respectively 100 k $\Omega$  and 5.6 nF. More information on selecting the values can be found in Section 4.3: Non-dissipative overcurrent detection and protection.

Figure 6. Logic inputs internal structure

Figure 7. EN<sub>A</sub> and EN<sub>B</sub> pins open collector driving

Figure 8.  $EN_A$  and  $EN_B$  pins push-pull driving

L6206Q Circuit description

| Inputs |                  |                  | Out                   | puts                  |

|--------|------------------|------------------|-----------------------|-----------------------|

| EN     | IN1              | IN2              | OUT1                  | OUT2                  |

| L      | X <sup>(1)</sup> | X <sup>(1)</sup> | High Z <sup>(2)</sup> | High Z <sup>(2)</sup> |

| Н      | L                | L                | GND                   | GND                   |

| Н      | Н                | L                | V <sub>S</sub>        | GND                   |

| Н      | L                | Н                | GND                   | V <sub>S</sub>        |

| Н      | Н                | Н                | V <sub>S</sub>        | V <sub>S</sub>        |

Table 6. Truth table

#### 4.3 Non-dissipative overcurrent detection and protection

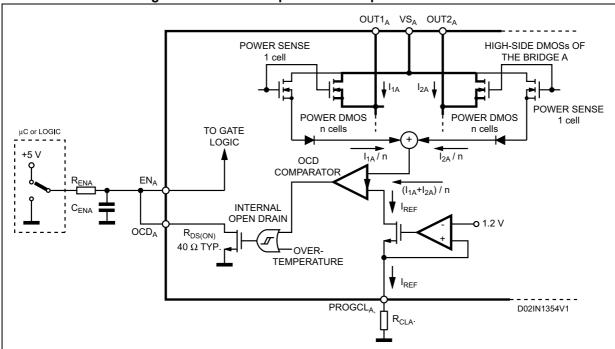

The L6206Q device integrates an overcurrent detection circuit (OCD). With this internal overcurrent detection, the external current sense resistor normally used and its associated power dissipation are eliminated. *Figure 9* shows a simplified schematic of the overcurrent detection circuit for bridge A. Bridge B is provided with an analogous circuit.

To implement the overcurrent detection, a sensing element that delivers a small but precise fraction of the output current is implemented with each high side Power MOSFET. Since this current is a small fraction of the output current there is very little additional power dissipation. This current is compared with an internal reference current  $I_{REF}$ . When the output current reaches the detection threshold  $I_{sover}$ , the OCD comparator signals a fault condition. When a fault condition is detected, an internal open-drain MOSFET with a pull-down capability of 4 mA connected to the OCD pin is turned on. *Figure 10* shows the OCD operation.

This signal can be used to regulate the output current simply by connecting the OCD pin to the EN pin and adding an external R-C, as shown in *Figure 9*. The off-time before recovering normal operation can be easily programmed by means of the accurate thresholds of the logic inputs.

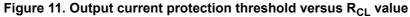

$I_{REF}$  and, therefore, the output current detection threshold, are selectable by the  $R_{CL}$  value, following *Equation 1* and *Equation 2*:

#### **Equation 1**

$I_{sover}$  = 5.6 A ± 30% at -25 °C <  $T_i$  < 125 °C if  $R_{CL}$  = 0  $\Omega$  (PROGCL connected to GND)

#### **Equation 2**

$$I_{sover} = \frac{22100}{R_{CL}} \pm 10\%$$

at -25 °C <  $T_j$  < 125 °C if 5 k $\Omega$  <  $R_{CL}$  < 40 k $\Omega$

Figure 11 shows the output current protection threshold versus  $R_{CL}$  value in the range 5 kΩ to 40 kΩ.

DocID022028 Rev 4

<sup>1.</sup> X = Do not care.

<sup>2.</sup> High Z = high impedance output.

Circuit description L6206Q

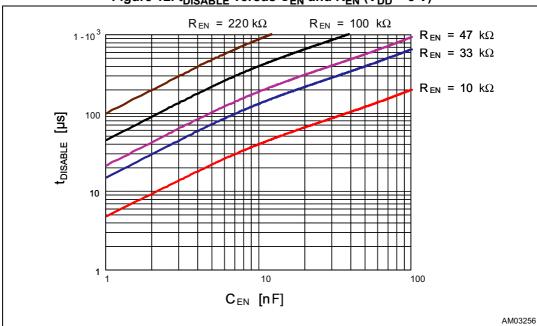

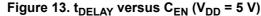

The disable time ( $t_{DISABLE}$ ), before recovering normal operation, can be easily programmed by means of the accurate thresholds of the logic inputs. It is affected either by  $C_{EN}$  or  $R_{EN}$  values and its magnitude is reported in *Figure 12*. The delay time ( $t_{DELAY}$ ), before turning off the bridge when an overcurrent has been detected, depends only on the  $C_{EN}$  value. Its magnitude is reported in *Figure 13*.

$C_{\text{EN}}$  is also used for providing immunity to pin EN against fast transient noises. Therefore the value of  $C_{\text{EN}}$  should be chosen as big as possible according to the maximum tolerable delay time and the  $R_{\text{EN}}$  value should be chosen according to the desired disable time.

The resistor  $R_{EN}$  should be chosen in the range from 2.2 k $\Omega$  to 180 k $\Omega$ . Recommended values for  $R_{EN}$  and  $C_{EN}$  are respectively 100 k $\Omega$  and 5.6 nF which allow a 200  $\mu$ s disable time to be obtained.

Figure 9. Overcurrent protection simplified schematic

L6206Q Circuit description

Figure 10. Overcurrent protection waveforms

Circuit description L6206Q

Figure 12.  $t_{DISABLE}$  versus  $C_{EN}$  and  $R_{EN}$  ( $V_{DD} = 5 V$ )

## 4.4 Thermal protection

In addition to overcurrent detection, the L6206Q device integrates a thermal protection for preventing device destruction in the case of junction overtemperature. It works by sensing the die temperature by means of a sensitive element integrated in the die. The device switches off when the junction temperature reaches 165  $^{\circ}$ C (typ. value) with 15  $^{\circ}$ C hysteresis (typ. value).

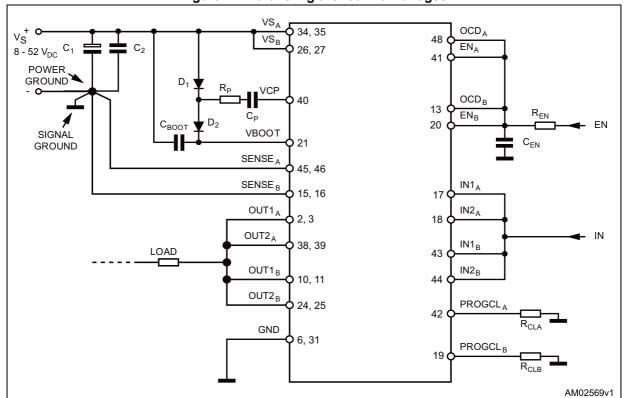

### 5 Application information

A typical application using the L6206Q device is shown in *Figure 14*. Typical component values for the application are shown in *Table 7*. A high quality ceramic capacitor in the range of 100 to 200 nF should be placed between the power pins (VS<sub>A</sub> and VS<sub>B</sub>) and ground near the L6206Q to improve the high frequency filtering on the power supply and reduce high frequency transients generated by the switching. The capacitors connected from the  $EN_A/OCD_A$  and  $EN_B/OCD_B$  nodes to ground set the shutdown time for bridge A and bridge B respectively when an overcurrent is detected (see *Section 4.3: Non-dissipative overcurrent detection and protection*). The two current sources (SENSE<sub>A</sub> and SENSE<sub>B</sub>) should be connected to power ground with a trace length as short as possible in the layout. To increase noise immunity, unused logic pins are best connected to 5 V (high logic level) or GND (low logic level) (see *Table 3.*).

It is recommended to keep power ground and signal ground separated on the PCB.

Table 7. Component values for typical application

| Component         | Value  |

|-------------------|--------|

| C <sub>1</sub>    | 100 μF |

| C <sub>2</sub>    | 100 nF |

| C <sub>BOOT</sub> | 220 nF |

| C <sub>P</sub>    | 10 nF  |

| C <sub>ENA</sub>  | 5.6 nF |

| C <sub>ENB</sub>  | 5.6 nF |

| D <sub>1</sub>    | 1N4148 |

| $D_2$             | 1N4148 |

| R <sub>CLA</sub>  | 5 kΩ   |

| R <sub>CLB</sub>  | 5 kΩ   |

| R <sub>ENA</sub>  | 100 kΩ |

| R <sub>ENB</sub>  | 100 kΩ |

| R <sub>P</sub>    | 100 Ω  |

Figure 14. Typical application

Note: To reduce the IC thermal resistance, and therefore improve the dissipation path, the NC pins can be connected to GND.

57/

L6206Q Paralleled operation

### 6 Paralleled operation

The outputs of the L6206Q device can be paralleled to increase the output current capability or reduce the power dissipation in the device at a given current level. It must be noted, however, that the internal wire bond connections from the die to the power or sense pins of the package must carry current in both of the associated half bridges.

When the two halves of one full bridge (for example  $OUT1_A$  and  $OUT2_A$ ) are connected in parallel, the peak current rating is not increased as the total current must still flow through one bond wire on the power supply or sense pin. In addition, the overcurrent detection senses the sum of the current in the upper devices of each bridge (A or B) so connecting the two halves of one bridge in parallel does not increase the overcurrent detection threshold.

For most applications the recommended configuration is half bridge 1 of bridge A paralleled with the half bridge 1 of bridge B, and the same for the half bridges 2, as shown in *Figure 15*. The current in the two devices connected in parallel share well as the  $R_{DS(ON)}$  of the devices on the same die is well matched. When connected in this configuration the overcurrent detection circuit, which senses the current in each bridge (A and B), senses the current in the upper devices connected in parallel independently and the sense circuit with the lowest threshold trips first. With the enable pins connected in parallel, the first detection of an overcurrent in either upper DMOS device turns off both bridges. Assuming that the two DMOS devices share the current equally, the resulting overcurrent detection threshold is twice the minimum threshold set by the resistors  $R_{CLA}$  or  $R_{CLB}$  in *Figure 15*. It is recommended to use  $R_{CLA} = R_{CLB}$ .

In this configuration the resulting bridge has the following characteristics.

- Equivalent device: full bridge

- R<sub>DS(ON)</sub> 0.15 Ω typ. value at T<sub>i</sub> = 25 °C

- 5 A max. RMS load current

- 11.2 A max. OCD threshold

17/27

Paralleled operation L6206Q

Figure 15. Parallel connection for higher current

To operate the device in parallel and maintain a lower overcurrent threshold, half bridge 1 and the half bridge 2 of bridge A can be connected in parallel and the same is done for bridge B, as shown in *Figure 16*. In this configuration, the peak current for each half bridge is still limited by the bond wires for the supply and sense pins so the dissipation in the device is reduced, but the peak current rating is not increased.

When connected in this configuration the overcurrent detection circuit, senses the sum of the current in upper devices connected in parallel. With the enable pins connected in parallel, an overcurrent turns off both bridges.

Since the circuit senses the total current in the upper devices, the overcurrent threshold is equal to the threshold set by the resistor  $R_{CLA}$  or  $R_{CLB}$  in *Figure 16*.  $R_{CLA}$  sets the threshold when outputs OUT1A and OUT2A are high and resistor  $R_{CLB}$  sets the threshold when outputs OUT1<sub>B</sub> and OUT2<sub>B</sub> are high.

It is recommended to use  $R_{CLA} = R_{CLB}$ .

In this configuration, the resulting bridge has the following characteristics.

- Equivalent device: full bridge

- $R_{DS(ON)}$  0.15  $\Omega$  typ. value at  $T_i$  = 25 °C

- 2.5 A max. RMS load current

- 5.6 A max. OCD threshold

577

L6206Q Paralleled operation

Figure 16. Parallel connection with lower overcurrent threshold

It is also possible to parallel the four half bridges to obtain a simple half bridge as shown in *Figure 17*. In this configuration the overcurrent threshold is equal to twice the minimum threshold set by the resistors  $R_{CLA}$  or  $R_{CLB}$  in *Figure 17*. It is recommended to use  $R_{CLA} = R_{CLB}$ .

The resulting half bridge has the following characteristics.

- Equivalent device: half bridge

- $R_{DS(ON)}$  0.075  $\Omega$  typ. value at  $T_j$  = 25 °C

- 5 A max. RMS load current

- 11.2 A max. OCD threshold

Paralleled operation L6206Q

Figure 17. Paralleling the four half bridges

## 7 Output current capability and IC power dissipation

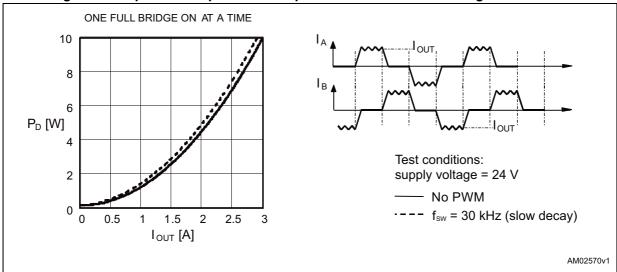

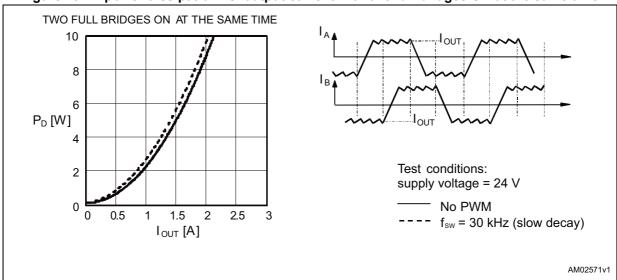

*Figure 18* and *Figure 19* show the approximate relation between the output current and the IC power dissipation using PWM current control driving two loads, for two different driving types:

- One full bridge ON at a time (*Figure 18*) in which only one load at a time is energized.

- Two full bridges ON at the same time (*Figure 19*) in which two loads at the same time are energized.

For a given output current and driving type the power dissipated by the IC can be easily evaluated, in order to establish which package should be used and how large the onboard copper dissipating area must be in order to guarantee a safe operating junction temperature (125 °C maximum).

Figure 18. IC power dissipation vs. output current with one full bridge on at a time

Figure 19. IC power dissipation vs. output current with two full bridges ON at the same time

5

DocID022028 Rev 4

21/27

Thermal management L6206Q

## 8 Thermal management

In most applications the power dissipation in the IC is the main factor that sets the maximum current that can be delivered by the device in a safe operating condition. Therefore, it must be taken into account very carefully. Besides the available space on the PCB, the right package should be chosen considering the power dissipation. Heat sinking can be achieved using copper on the PCB with proper area and thickness.

Table 8. Thermal data

| Symbol            | Parameter                           | Package                 | Тур. | Unit |

|-------------------|-------------------------------------|-------------------------|------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | VFQFPN48 <sup>(1)</sup> | 17   | °C/W |

VFQFPN48 mounted on EVAL6208Q rev. 1.1 board (see EVAL6208Q databrief): four-layer FR4 PCB with a dissipating copper surface of about 45 cm<sup>2</sup> on each layer and 25 via holes below the IC.

4.6

#### 9 Electrical characteristics curves

Figure 20. Typical quiescent current vs. supply voltage

Iq [mA]

5.6

f<sub>sw</sub> = 1 kHz

T<sub>j</sub> = 25 °C

T<sub>j</sub> = 85 °C

T<sub>j</sub> = 125 °C

30

V<sub>s</sub> [V]

40

50

60

AM02572v1

20

10

Figure 21. Typical high-side  $R_{DS(on)}$  vs. supply voltage  $\mathsf{R}_{\mathsf{DS}(\mathsf{ON})}[\Omega]$ 0.380 0.376 0.372 T<sub>i</sub> = 25 °C 0.368 0.364 0.360 0.356 0.352 0.348 0.344 0.340 0.336 0 5 10 15 20 25 30  $V_{S}[V]$ AM02573v1

Figure 22. Normalized typical quiescent current vs. switching frequency

Iq / (Iq at 1 kHz)

1.7

1.6

1.5

1.4

1.3

1.2

1.1

1.0

0.9

0 20 40

f<sub>SW</sub> [kHz]

AM02574v1

57/

DocID022028 Rev 4

23/27

Package information L6206Q

# 10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

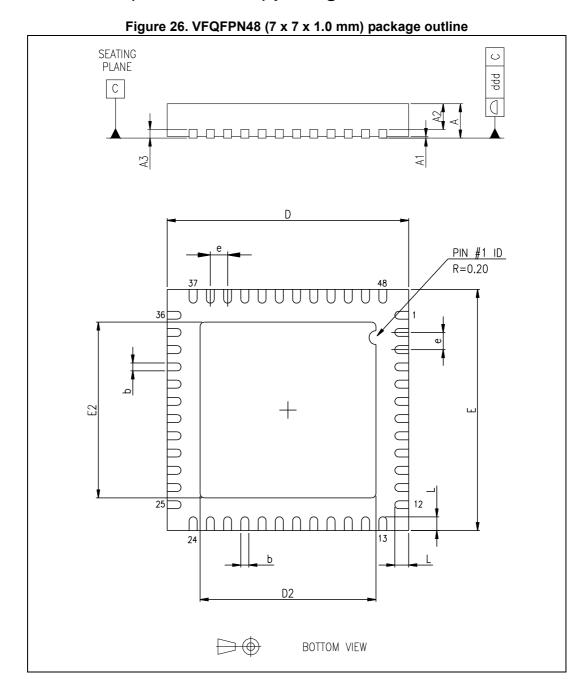

#### 10.1 VFQFPN48 (7 x 7 x 1.0 mm) package information

**577**

L6206Q Package information

Table 9. VFQFPN48 (7 x 7 x 1.0 mm) package mechanical data

| Complete |      | Dimensions (mm) |      |

|----------|------|-----------------|------|

| Symbol   | Min. | Тур.            | Max. |

| А        | 0.80 | 0.90            | 1.00 |

| A1       | -    | 0.02            | 0.05 |

| A2       | -    | 0.65            | 1.00 |

| A3       | -    | 0.25            | -    |

| b        | 0.18 | 0.23            | 0.30 |

| D        | 6.85 | 7.00            | 7.15 |

| D2       | 4.95 | 5.10            | 5.25 |

| E        | 6.85 | 7.00            | 7.15 |

| E2       | 4.95 | 5.10            | 5.25 |

| е        | 0.45 | 0.50            | 0.55 |

| L        | 0.30 | 0.40            | 0.50 |

| ddd      | -    | 0.08            | -    |

Order codes L6206Q

## 11 Order codes

**Table 10. Ordering information**

| Order codes | Package                     | Packaging     |

|-------------|-----------------------------|---------------|

| L6206Q      | VFQFPN48 7 x 7 x 1.0 mm     | Tray          |

| L6206QTR    | VEQEEN40 / X / X 1.0 IIIIII | Tape and reel |

# 12 Revision history

**Table 11. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Nov-2011 | 1        | First release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10-Jun-2013 | 2        | Unified package name to "VFQFPN48" in the whole document. Corrected headings in <i>Table 1</i> and <i>Table 2</i> (replaced "Parameter" by "Test condition").  Updated <i>Table 4</i> (Added subscripts to "I <sub>f</sub> " and "R <sub>OPDR</sub> ").  Added titles to <i>Equation 1</i> and <i>Equation 2</i> and cross-references in <i>Section 4.3: Non-dissipative overcurrent detection and protection</i> . Corrected unit in <i>Table 7</i> (row C <sub>1</sub> ).  Updated <i>Figure 13</i> (added subscripts to "t <sub>DELAY</sub> " and "C <sub>EN</sub> ").  Added <i>Table 8: Thermal data</i> in <i>Section 8: Thermal management</i> .  Updated <i>Section 10: Package information</i> (modified titles, reversed order of <i>Figure 26</i> and <i>Table 9</i> ).  Minor corrections throughout document. |

| 01-Aug-2013 | 3        | Updated <i>Figure 1 on page 1</i> . Corrected note <i>1.</i> below <i>Table 8 on page 22.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10-Mar-2017 | 4        | Updated <i>Table 7 on page 15</i> (removed C <sub>REF</sub> row).  Updated <i>Figure 9 on page 12</i> and <i>Figure 14 on page 16</i> (replaced by new figures).  Minor modifications throughout document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID022028 Rev 4

27/27