# **Table of Contents**

|   | Introd | duction |                                                 |

|---|--------|---------|-------------------------------------------------|

|   | 1.1    | Docun   | nent Overview                                   |

|   | 1.2    | Descri  | iption                                          |

| 2 | Block  | diagra  | m7                                              |

| 3 | Packa  | age pin | outs and signal descriptions                    |

|   | 3.1    | Pad ty  | rpes                                            |

|   | 3.2    | Syster  | m pins                                          |

|   | 3.3    |         | onal ports14                                    |

| 4 |        |         | naracteristics41                                |

|   | 4.1    |         | neter classification                            |

|   | 4.2    |         | RO register                                     |

|   |        |         | NVUSRO [PAD3V5V(0)] field description 42        |

|   |        | 4.2.2   | NVUSRO [PAD3V5V(1)] field description 42        |

|   | 4.3    |         | ute maximum ratings                             |

|   | 4.4    |         | nmended operating conditions44                  |

|   | 4.5    |         | nal characteristics47                           |

|   |        | 4.5.1   | Package thermal characteristics                 |

|   |        | 4.5.2   |                                                 |

|   | 4.6    |         | d electrical characteristics48                  |

|   |        | 4.6.1   | I/O pad types                                   |

|   |        | 4.6.2   | I/O input DC characteristics                    |

|   |        | 4.6.3   | I/O output DC characteristics                   |

|   |        | 4.6.4   | Output pin transition times                     |

|   |        | 4.6.5   | I/O pad current specification                   |

|   | 4.7    |         | T electrical characteristics                    |

|   | 4.8    |         | management electrical characteristics57         |

|   |        | 4.8.1   | Voltage regulator electrical characteristics57  |

|   |        | 4.8.2   | VDD_BV options                                  |

|   | 4.0    | 4.8.3   | Voltage monitor electrical characteristics 60   |

|   | 4.9    |         | oltage domain power consumption                 |

|   | 4.10   |         | memory electrical characteristics               |

|   |        |         | Program/Erase characteristics63                 |

|   |        |         | Flash memory power supply DC characteristics65  |

|   | 4.44   |         | Flash memory start-up/switch-off timings 66     |

|   | 4.11   |         | omagnetic compatibility (EMC) characteristics66 |

|   |        | 4.11.1  | Designing hardened software to avoid noise      |

|   |       | problems                                                  | 0  |

|---|-------|-----------------------------------------------------------|----|

|   |       | 4.11.2 Electromagnetic interference (EMI) 6               | 7  |

|   |       | 4.11.3 Absolute maximum ratings (electrical sensitivity)6 | 37 |

|   | 4.12  | Fast external crystal oscillator (4–40 MHz) electrical    |    |

|   |       | characteristics                                           | 8  |

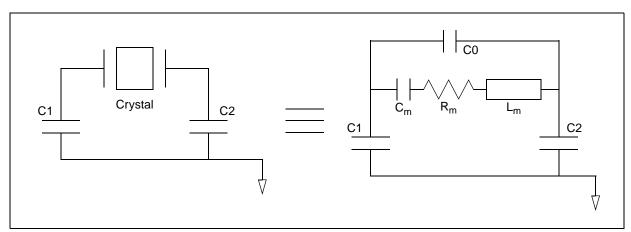

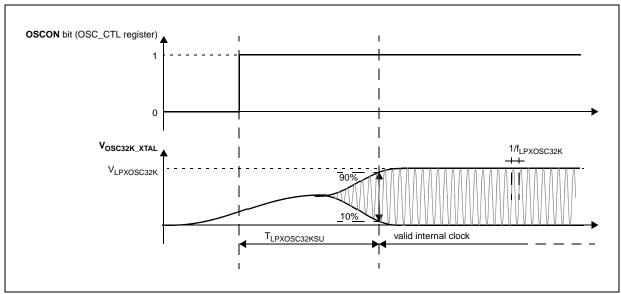

|   | 4.13  | Slow external crystal oscillator (32 kHz) electrical      |    |

|   |       | characteristics                                           | 1  |

|   | 4.14  | FMPLL electrical characteristics                          | 3  |

|   | 4.15  | Fast internal RC oscillator (16 MHz) electrical           |    |

|   |       | characteristics                                           | 4  |

|   | 4.16  | Slow internal RC oscillator (128 kHz) electrical          |    |

|   |       | characteristics                                           | 5  |

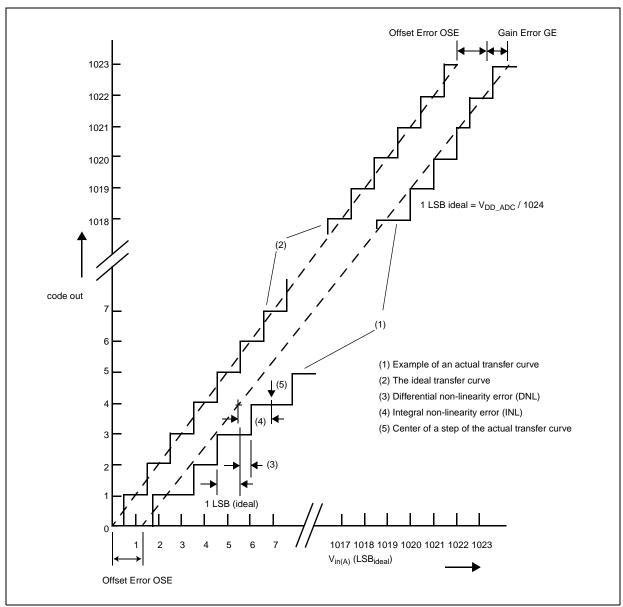

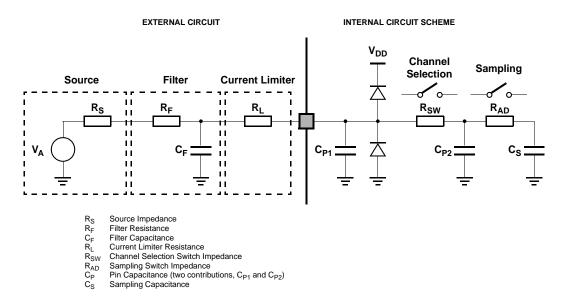

|   | 4.17  | ADC electrical characteristics                            | 6  |

|   |       | 4.17.1 Introduction                                       | 6  |

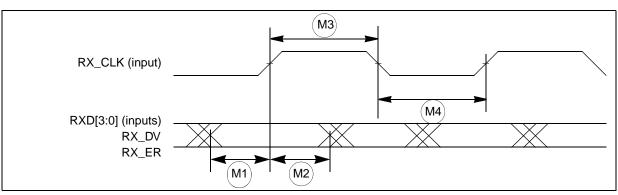

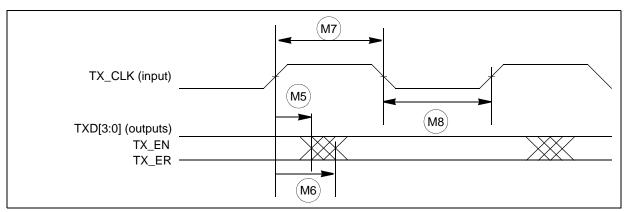

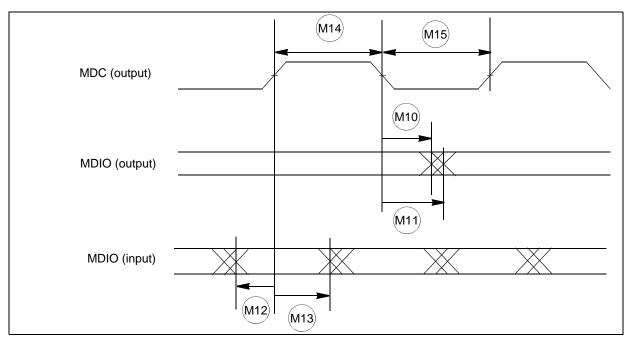

|   | 4.18  | Fast Ethernet Controller                                  | 7  |

|   |       | 4.18.1 MII Receive Signal Timing (RXD[3:0], RX_DV,        |    |

|   |       | RX_ER, and RX_CLK)8                                       | 7  |

|   |       | 4.18.2 MII Transmit Signal Timing (TXD[3:0], TX_EN,       |    |

|   |       | TX_ER, TX_CLK)8                                           | 7  |

|   |       | 4.18.3 MII Async Inputs Signal Timing (CRS and COL)8      | 8  |

|   |       | 4.18.4 MII Serial Management Channel Timing (MDIO ar      | 10 |

|   |       | MDC)89                                                    |    |

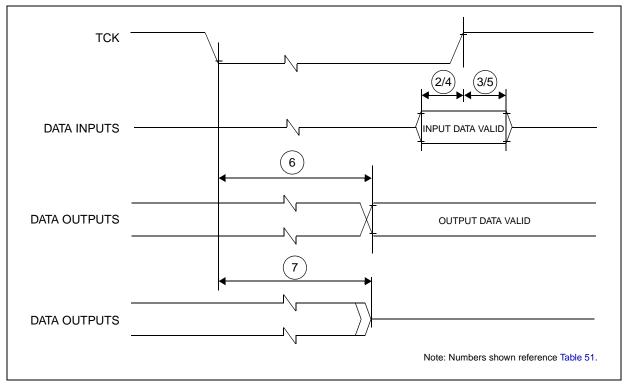

|   | 4.19  | On-chip peripherals                                       | 1  |

|   |       | 4.19.1 Current consumption 9                              | 1  |

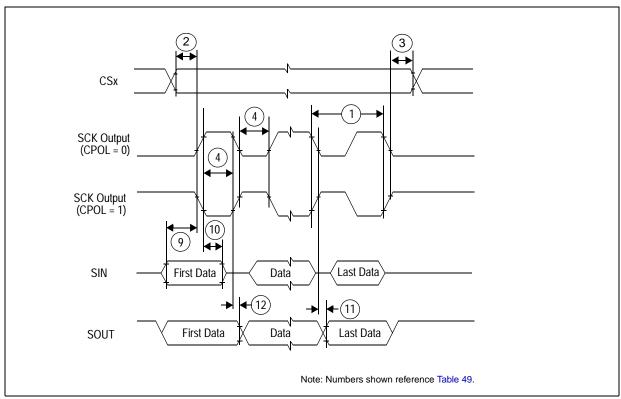

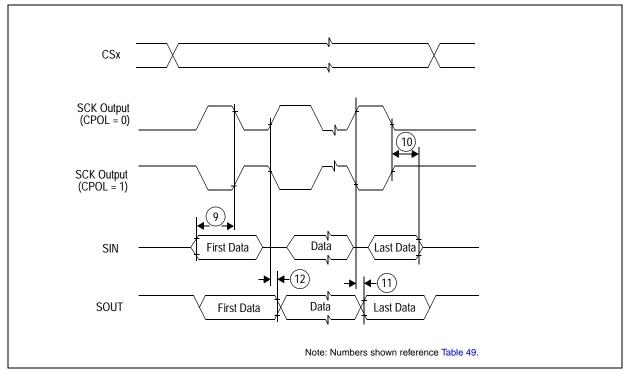

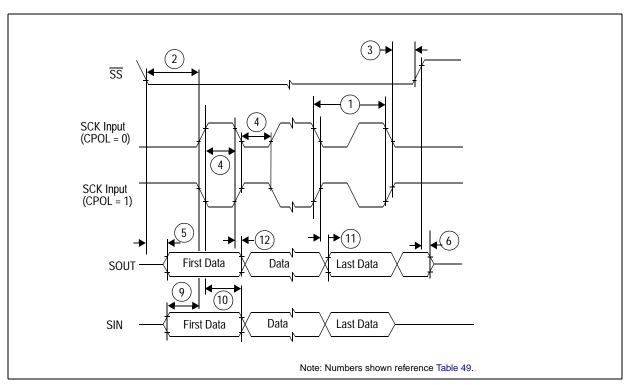

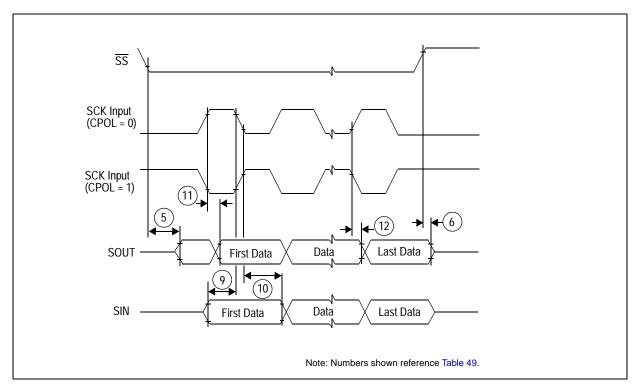

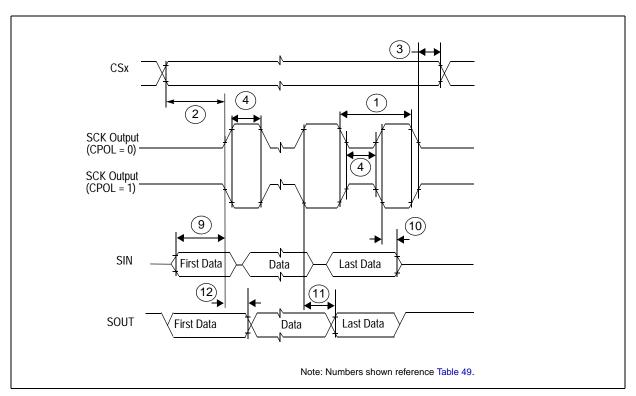

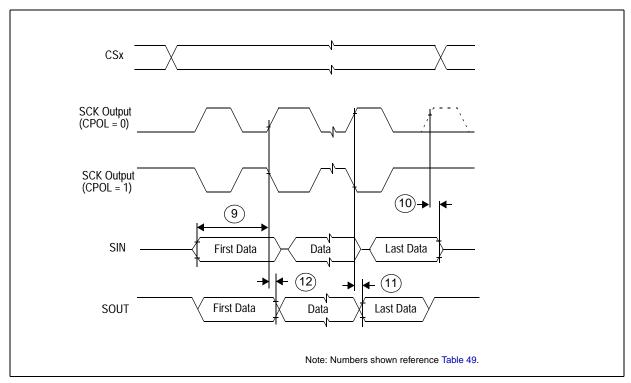

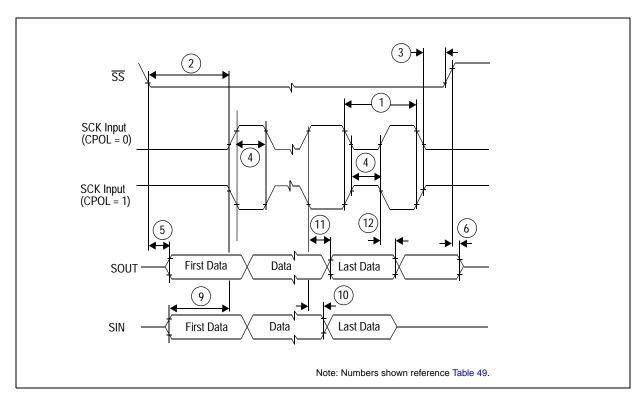

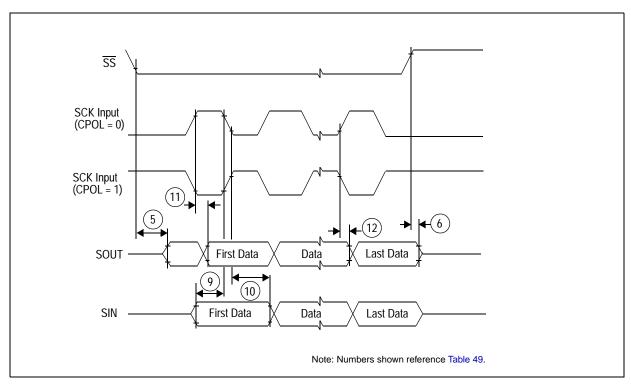

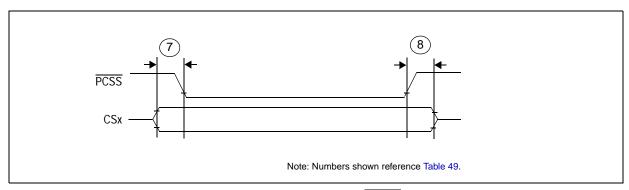

|   |       | 4.19.2 DSPI characteristics93                             | 3  |

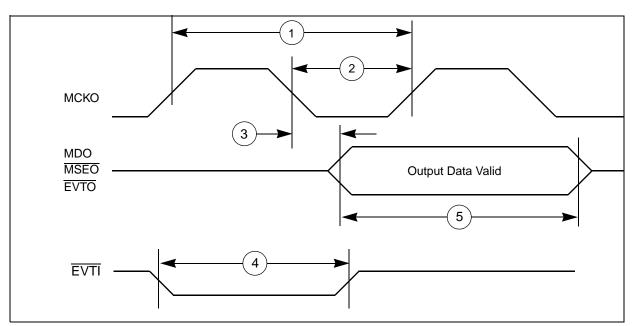

|   |       | 4.19.3 Nexus characteristics                              | 1  |

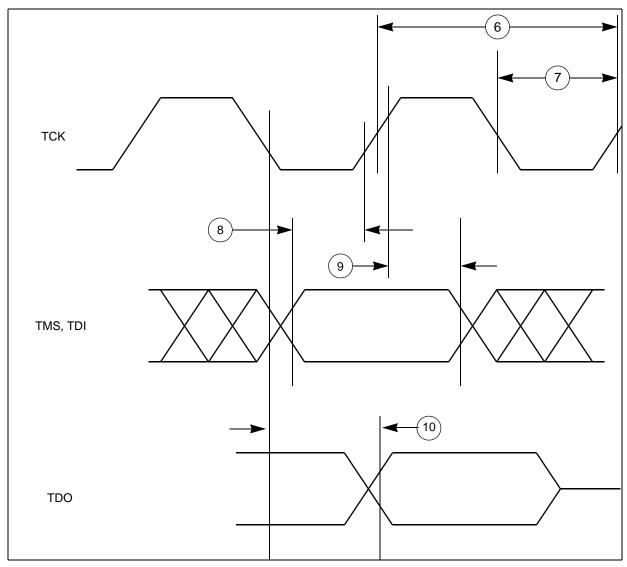

|   |       | 4.19.4 JTAG characteristics                               | 3  |

| 5 | Pack  | age characteristics                                       | 5  |

|   | 5.1   | Package mechanical data                                   | 5  |

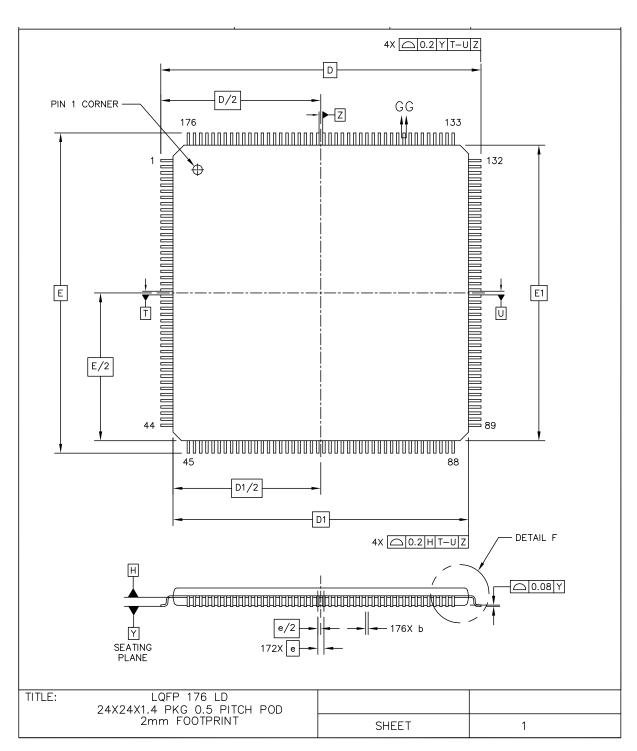

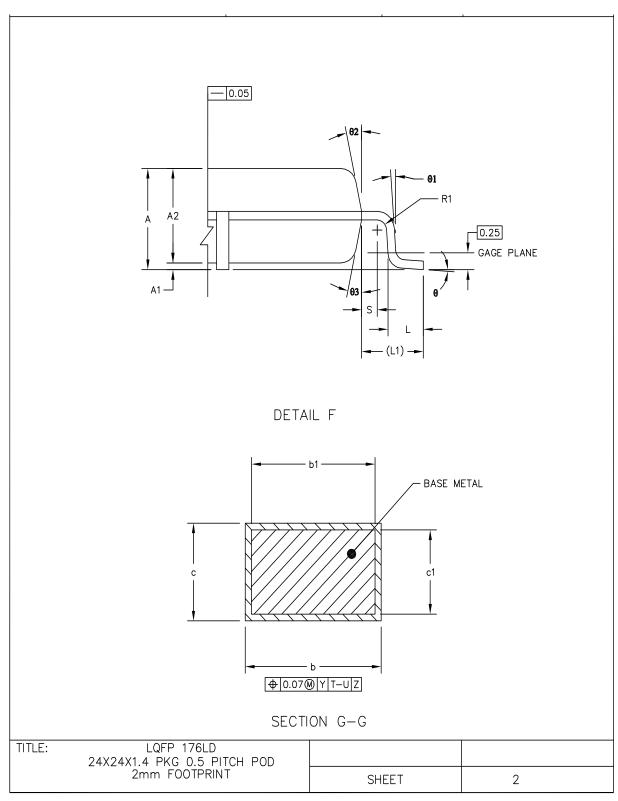

|   |       | 5.1.1 176 LQFP package mechanical drawing 109             | 5  |

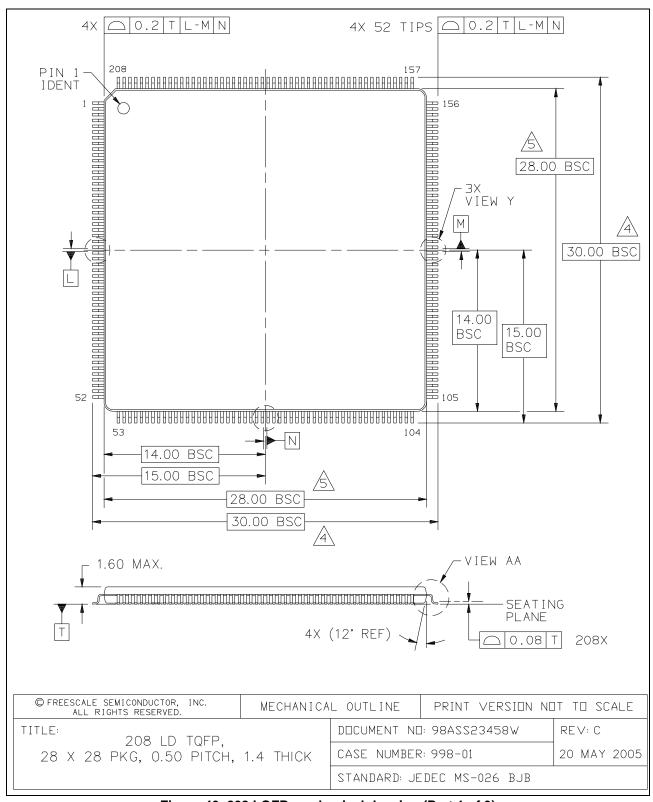

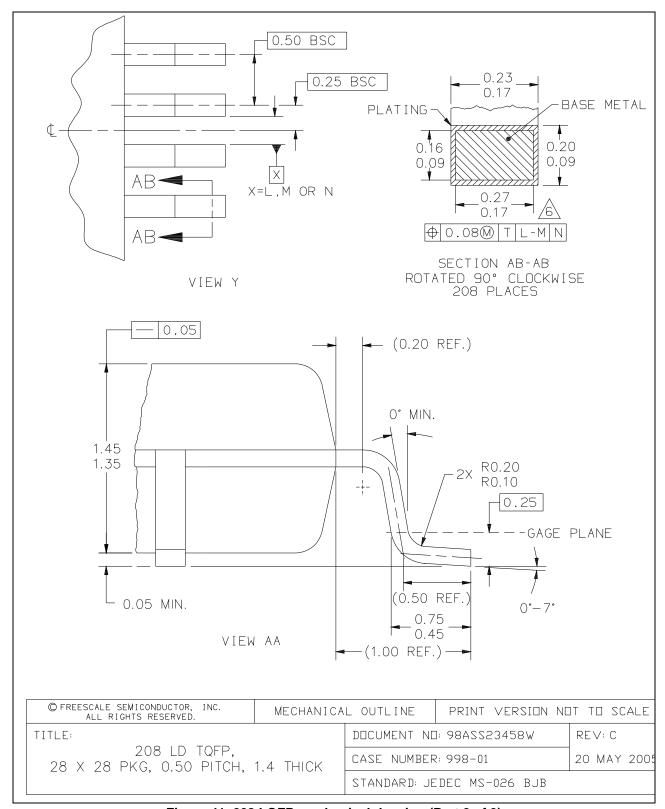

|   |       | 5.1.2 208 LQFP package mechanical drawing 108             |    |

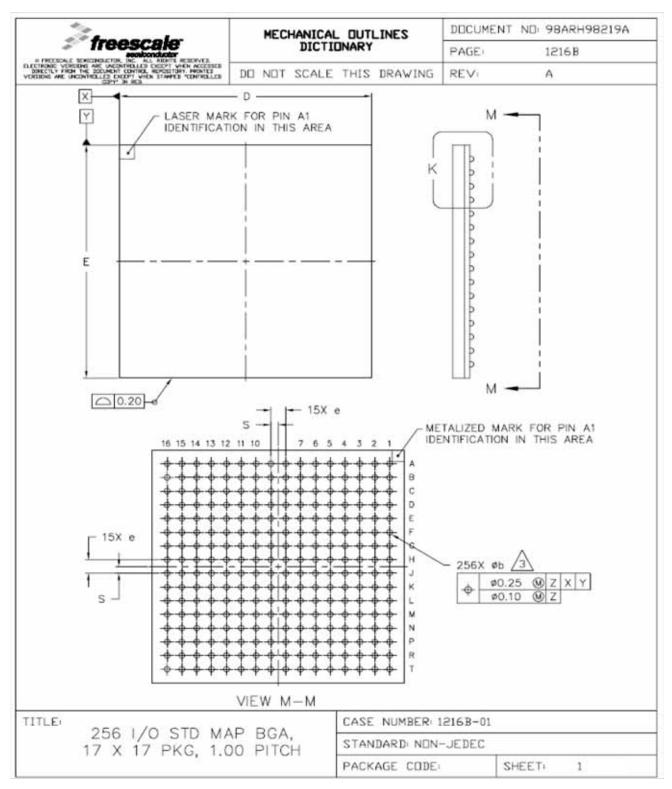

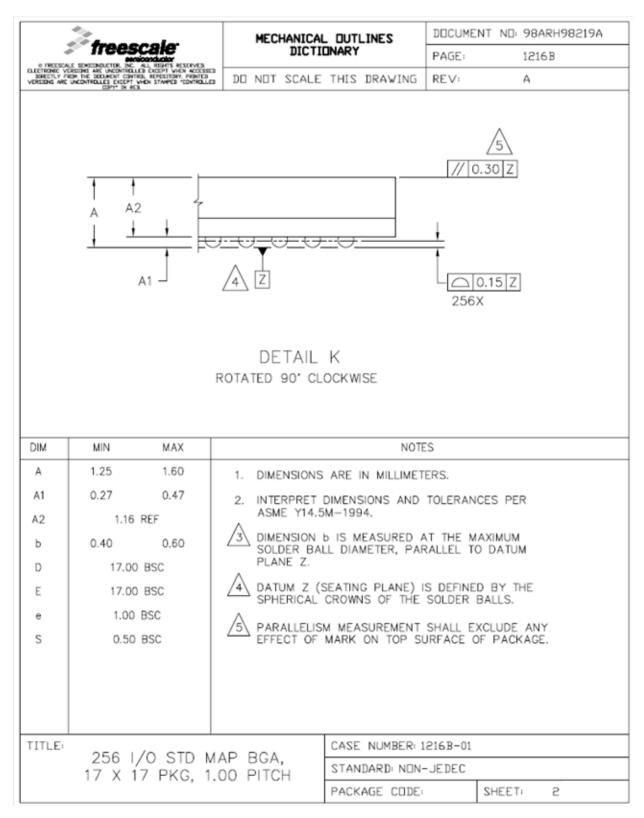

|   |       | 5.1.3 256 MAPBGA package mechanical drawing . 113         | 3  |

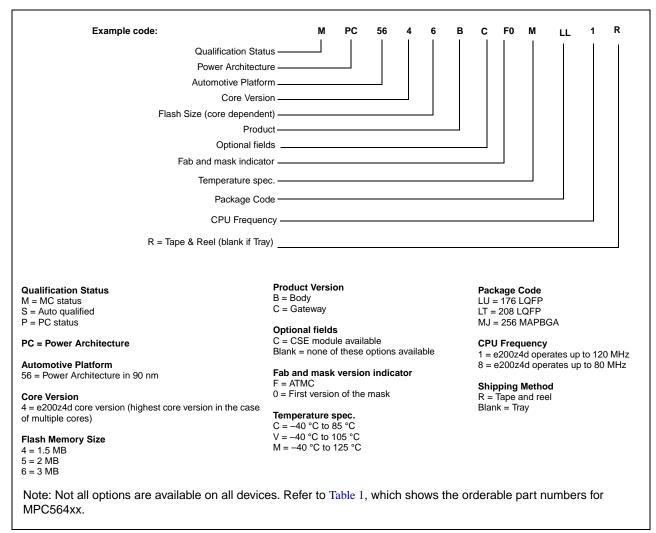

| 6 | Orde  | ring information                                          | 5  |

| 7 | Pavid | ion history 110                                           | 6  |

MPC5646C Data Sheet, Rev.6

#### **Other Features**

- System clocks sources

- 4–40 MHz external crystal oscillator

- 16 MHz internal RC oscillator

- FMPLL

- Additionally, there are two low power oscillators: 128 kHz internal RC oscillator, 32 kHz external crystal oscillator

- Real Time Counter (RTC) with clock source from internal 128 kHz or 16 MHz oscillators or external 4–40 MHz crystal

- Supports autonomous wake-up with 1 ms resolution with max timeout of 2 seconds

- Optional support from external 32 kHz crystal oscillator, supporting wake-up with 1 second resolution and max timeout of 1 hour

- 1 Real Time Interrupt (RTI) with 32-bit counter resolution

- 1 Safety Enhanced Software Watchdog Timer (SWT) that supports keyed functionality

- 1 dual-channel FlexRay Controller with 128 message buffers

- 1 Fast Ethernet Controller (FEC)

- On-chip voltage regulator (VREG)

- Cryptographic Services Engine (CSE)

- Offered in the following standard package types:

- 176-pin LQFP, 24 × 24 mm, 0.5 mm Lead Pitch

- 208-pin LQFP, 28 × 28 mm, 0.5 mm Lead Pitch

- 256-ball MAPBGA, 17 × 17mm, 1.0 mm Lead Pitch

Introduction

#### 1 Introduction

#### 1.1 Document Overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the MPC5646C device. To ensure a complete understanding of the device functionality, refer also to the MPC5646C Reference Manual.

### 1.2 Description

The MPC5646C is a new family of next generation microcontrollers built on the Power Architecture embedded category. This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

The MPC5646C family expands the range of the MPC560xB microcontroller family. It provides the scalability needed to implement platform approaches and delivers the performance required by increasingly sophisticated software architectures. The advanced and cost-efficient host processor core of the MPC5646C automotive controller family complies with the Power Architecture embedded category, which is 100 percent user-mode compatible with the original Power Architecture user instruction set architecture (UISA). It operates at speeds of up to 120 MHz and offers high performance processing optimized for low power consumption. It also capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

Table 1. MPC5646C family comparison<sup>1</sup>

| Feature                             | MPC               | MPC5644B                  | Σ           | MPC5644C                                                             | ب                       | MPC5645B                   | 645B            | Ξ                | MPC5645C                                                             |            | MPC5646B                   | 646B                 | Σ           | MPC5646C                                                             |                  |

|-------------------------------------|-------------------|---------------------------|-------------|----------------------------------------------------------------------|-------------------------|----------------------------|-----------------|------------------|----------------------------------------------------------------------|------------|----------------------------|----------------------|-------------|----------------------------------------------------------------------|------------------|

| Package                             | 176<br>LQFP       | 208<br>LQFP               | 176<br>LQFP | 208<br>LQFP                                                          | 256<br>BGA              | 176<br>LQFP                | 208<br>LQFP     | 176<br>LQFP      | 208<br>LQFP                                                          | 256<br>BGA | 176<br>LQFP                | 176 208<br>LQFP LQFP | 176<br>LQFP | 208<br>LQFP                                                          | 256<br>BGA       |

| CPU                                 | e20               | e200z4d                   | e200z       | e200z4d + e200z0h                                                    | 00z0h                   | e200                       | e200z4d         | e200z            | e200z4d + e200z0h                                                    | 40z0h      | e200                       | e200z4d              | e200z       | e200z4d + e200z0h                                                    | 40z0h            |

| Execution speed <sup>2</sup>        | Up to 12<br>(e200 | o to 120 MHz<br>(e200z4d) | dh<br>dh    | Up to 120 MHz<br>(e200z4d)<br>Up to 80 MHz<br>(e200z0h) <sup>3</sup> | 1Hz<br> )<br>  Hz<br> 3 | Up to 120 MHz<br>(e200z4d) | 20 MHz<br>)z4d) | Up t<br>(e<br>Up | Up to 120 MHz<br>(e20024d)<br>Up to 80 MHz<br>(e20020h) <sup>3</sup> | 7 Z X 8    | Up to 120 MHz<br>(e200z4d) | :0 MHz<br>)z4d)      | dn<br>e)    | Up to 120 MHz<br>(e20024d)<br>Up to 80 MHz<br>(e20020h) <sup>3</sup> | 7 7 <sub>8</sub> |

| Code flash memory                   |                   |                           | 1.5 MB      |                                                                      |                         |                            |                 | 2 MB             |                                                                      |            |                            |                      | 3 MB        |                                                                      |                  |

| Data flash memory                   |                   |                           |             |                                                                      |                         |                            | 4               | 4 x16 KB         |                                                                      |            |                            |                      |             |                                                                      |                  |

| SRAM                                | 128               | 128 KB                    |             | 192 KB                                                               |                         | 160 KB                     | KB              |                  | 256 KB                                                               |            | 192                        | 192 KB               |             | 256 KB                                                               |                  |

| MPU                                 |                   |                           |             |                                                                      |                         |                            |                 | 16-entry         |                                                                      |            |                            |                      |             |                                                                      |                  |

| eDMA <sup>4</sup>                   |                   |                           |             |                                                                      |                         |                            |                 | 32 ch            |                                                                      |            |                            |                      |             |                                                                      |                  |

| 10-bit ADC                          |                   |                           |             |                                                                      |                         |                            |                 |                  |                                                                      |            |                            |                      |             |                                                                      |                  |

| dedicated <sup>5,6</sup>            | 27 ch             | 33 ch                     | 27 ch       | 33                                                                   | 33 ch                   | 27 ch                      | 33 ch           | 27 ch            | 33 ch                                                                | 5          | 27 ch                      | 33 ch                | 27 ch       | 33 ch                                                                | 5                |

| shared with 12-bit ADC <sup>7</sup> |                   |                           |             |                                                                      |                         |                            |                 | 19 ch            |                                                                      |            |                            |                      |             |                                                                      |                  |

| 12-bit ADC                          |                   |                           |             |                                                                      |                         |                            |                 |                  |                                                                      |            |                            |                      |             |                                                                      |                  |

| dedicated <sup>8</sup>              | 5 ch              | 10 ch                     | 5 ch        | 10                                                                   | 10 ch                   | 5 ch                       | 10 ch           | 5 ch             | 10 ch                                                                | 5          | 5 ch                       | 10 ch                | 5 ch        | 10 ch                                                                | 5                |

| shared with 10-bit ADC <sup>7</sup> |                   |                           |             |                                                                      |                         |                            |                 | 19 ch            |                                                                      |            |                            |                      |             |                                                                      |                  |

| СТU                                 |                   |                           |             |                                                                      |                         |                            |                 | 64 ch            |                                                                      |            |                            |                      |             |                                                                      |                  |

| Total timer I/O9 eMIOS              |                   |                           |             |                                                                      |                         |                            | 64              | 64 ch, 16-bit    | );t                                                                  |            |                            |                      |             |                                                                      |                  |

| SCI (LINFlexD)                      |                   |                           |             |                                                                      |                         |                            |                 | 10               |                                                                      |            |                            |                      |             |                                                                      |                  |

| SPI (DSPI)                          |                   |                           |             |                                                                      |                         |                            |                 | ∞                |                                                                      |            |                            |                      |             |                                                                      |                  |

| CAN (FlexCAN) <sup>10</sup>         |                   |                           |             |                                                                      |                         |                            |                 | 9                |                                                                      |            |                            |                      |             |                                                                      |                  |

| FlexRay                             |                   |                           |             |                                                                      |                         |                            |                 | Yes              |                                                                      |            |                            |                      |             |                                                                      |                  |

| STCU <sup>11</sup>                  |                   |                           |             |                                                                      |                         |                            |                 | Yes              |                                                                      |            |                            |                      |             |                                                                      |                  |

|                                     |                   |                           |             |                                                                      |                         |                            |                 |                  |                                                                      |            |                            |                      |             |                                                                      |                  |

# Table 1. MPC5646C family comparison<sup>1</sup> (continued)

| Feature                                | MPC         | MPC5644B | Σ                             | MPC5644C    | ပ           | MPC5645B    | 645B        | Σ                                                                                | MPC5645C    | ည           | MPC5        | MPC5646B             | Σ                                                                                             | MPC5646C    | ပ           |

|----------------------------------------|-------------|----------|-------------------------------|-------------|-------------|-------------|-------------|----------------------------------------------------------------------------------|-------------|-------------|-------------|----------------------|-----------------------------------------------------------------------------------------------|-------------|-------------|

| Package                                | 176<br>LQFP |          | 208 176 208<br>LQFP LQFP LQFP | 208<br>LQFP | 256<br>BGA  | 176<br>LQFP | 208<br>LQFP | 176         208         176         208           LQFP         LQFP         LQFP | 208<br>LQFP | 256<br>BGA  | 176<br>LQFP | 176 208<br>.QFP LQFP | 176         208         176         208           LQFP         LQFP         LQFP         LQFP | 208<br>LQFP | 256<br>BGA  |

| Ethernet                               | 8           | 0        |                               | Yes         |             | 8           | 0           |                                                                                  | Yes         |             | Z           | No                   |                                                                                               | Yes         |             |

| 1 <sup>2</sup> C                       |             |          |                               |             |             |             |             | -                                                                                |             |             |             |                      |                                                                                               |             |             |

| 32 kHz oscillator (SXOSC)              |             |          |                               |             |             |             |             | Yes                                                                              |             |             |             |                      |                                                                                               |             |             |

| GPIO <sup>12</sup>                     | 147         | 177      | 147                           | 177         | 199         | 147         | 177         | 177 147 177                                                                      | 177         | 199         | 147         | 177                  | 177 147                                                                                       | 177         | 199         |

| Debug                                  |             | 15       | JTAG                          |             | Nexus<br>3+ |             | Ţ,          | JTAG                                                                             |             | Nexus<br>3+ |             | Ĺ                    | JTAG                                                                                          |             | Nexus<br>3+ |

| Cryptographic Services<br>Engine (CSE) |             |          |                               |             |             |             |             | Optional                                                                         |             |             |             |                      |                                                                                               |             |             |

# JOTES:

Feature set dependent on selected peripheral multiplexing; table shows example.

<sup>2</sup> Based on 125 °C ambient operating temperature and subject to full device characterisation.

The e20020h can run at speeds up to 80 MHz. However, if system frequency is >80 MHz (e.g., e200z4d running at 120 MHz) the e200z0h needs to run at 1/2 system frequency. There is a configurable e200z0 system clock divider for this purpose.

DMAMUX also included that allows for software selection of 32 out of a possible 57 sources.

Not shared with 12-bit ADC, but possibly shared with other alternate functions.

There are 23 dedicated ANS plus 4 dedicated ANX channels on LQPF176. For higher pin count packages, there are 29 dedicated ANS plus 4 dedicated ANX channels. 9

16x precision channels (ANP) and 3x standard (ANS).

Not shared with 10-bit ADC, but possibly shared with other alternate functions.

As a minimum, all timer channels can function as PWM or Input Capture and Output Control. Refer to the eMIOS section of the device reference manual for information on the channel configuration and functions.

<sup>10</sup> CAN Sampler also included that allows ID of CAN message to be captured when in low power mode.

<sup>11</sup> STCU controls MBIST activation and reporting.

<sup>12</sup> Estimated I/O count for proposed packages based on multiplexing with peripherals.

6

Downloaded from Arrow.com.

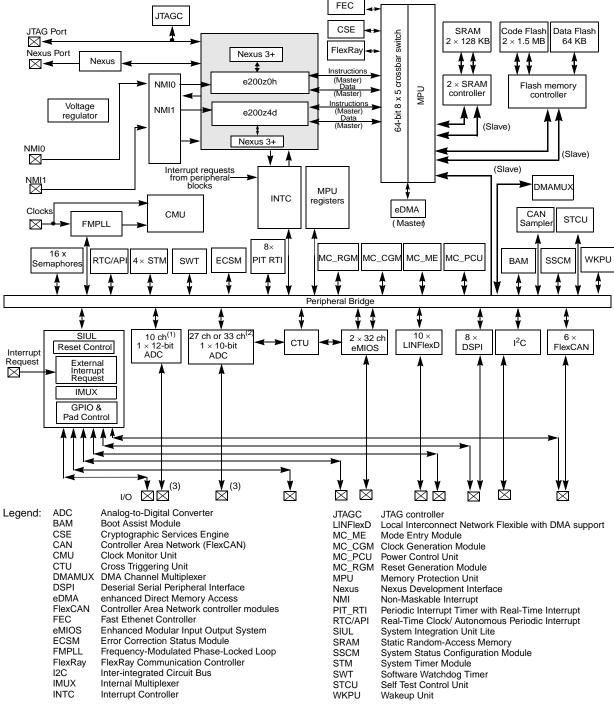

# 2 Block diagram

Figure 1 shows the detailed block diagram of the MPC5646C.

Notes:

- 1) 10 dedicated channels plus up to 19 shared channels. See the device-comparison table.

- 2) Package dependent. 27 or 33 dedicated channels plus up to 19 shared channels. See the device-comparison table.

- 3) 16 x precision channels (ANP) are mapped on input only I/O cells.

Figure 1. MPC5646C block diagram

MPC5646C Data Sheet, Rev.6

#### **Block diagram**

Table 2 summarizes the functions of the blocks present on the MPC5646C.

#### Table 2. MPC5646C series block summary

| Block                                            | Function                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                | Converts analog voltages to digital values                                                                                                                                                                                                                                                                        |

| Boot assist module (BAM)                         | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                         | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                      | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Cryptographic Security Engine (CSE)              | Supports the encoding and decoding of any kind of data                                                                                                                                                                                                                                                            |

| Crossbar (XBAR) switch                           | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width                                                                                                                                                    |

| DMA Channel Multiplexer (DMAMUX)                 | Allows to route DMA sources (called slots) to DMA channels                                                                                                                                                                                                                                                        |

| Deserial serial peripheral interface (DSPI)      | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module (ECSM)            | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access (eDMA)             | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels.                                                                                                                                                                                                    |

| Enhanced modular input output system (eMIOS)     | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                     | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| FMPLL (frequency-modulated phase-locked loop)    | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| FlexRay (FlexRay communication controller)       | Provides high-speed distributed control for advanced automotive applications                                                                                                                                                                                                                                      |

| Fast Ethernet Controller (FEC)                   | Ethernet Media Access Controller (MAC) designed to support both 10 and 100 Mbps Ethernet/IEEE 802.3 networks                                                                                                                                                                                                      |

| Internal multiplexer (IMUX) SIUL subblock        | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C™) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                      | Provides priority-based preemptive scheduling of interrupt requests for both e200z0h and e200z4d cores                                                                                                                                                                                                            |

| JTAG controller                                  | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

MPC5646C Data Sheet, Rev.6

#### Table 2. MPC5646C series block summary (continued)

| Block                                                                 | Function                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LinFlexD (Local Interconnect<br>Network Flexible with DMA<br>support) | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                                                     |

| Memory protection unit (MPU)                                          | Provides hardware access control for all memory references generated in a device                                                                                                                                                                                                                                                                       |

| Clock generation module (MC_CGM)                                      | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                                                                 |

| Power control unit (MC_PCU)                                           | Reduces the overall power consumption by disconnecting parts of the device from the power supply via a power switching device; device components are grouped into sections called "power domains" which are controlled by the PCU                                                                                                                      |

| Reset generation module (MC_RGM)                                      | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                                                          |

| Mode entry module (MC_ME)                                             | Provides a mechanism for controlling the device operational mode and modetransition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications                                                |

| Non-Maskable Interrupt (NMI)                                          | Handles external events that must produce an immediate response, such as power down detection                                                                                                                                                                                                                                                          |

| Nexus Development Interface (NDI)                                     | Provides real-time development capabilities for e200z0h and e200z4d core processor                                                                                                                                                                                                                                                                     |

| Periodic interrupt timer/ Real Time Interrupt Timer (PIT_RTI)         | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                                                              |

| Real-time counter (RTC/API)                                           | A free running counter used for time keeping applications, the RTC can be configured to generate an interrupt at a predefined interval independent of the mode of operation (run mode or low-power mode). Supports autonomous periodic interrupt (API) function to generate a periodic wakeup request to exit a low power mode or an interrupt request |

| Static random-access memory (SRAM)                                    | Provides storage for program code, constants, and variables                                                                                                                                                                                                                                                                                            |

| System integration unit lite (SIUL)                                   | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration                                                                                                                               |

| System status and configuration module (SSCM)                         | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable                                                                                                                       |

| System timer module (STM)                                             | Provides a set of output compare events to support AutoSAR and operating system tasks                                                                                                                                                                                                                                                                  |

| Semaphores                                                            | Provides the hardware support needed in multi-core systems for sharing resources and provides a simple mechanism to achieve lock/unlock operations via a single write access.                                                                                                                                                                          |

| Wake Unit (WKPU)                                                      | Supports external sources that can generate interrupts or wakeup events, of which can cause non-maskable interrupt requests or wakeup events.                                                                                                                                                                                                          |

MPC5646C Data Sheet, Rev.6

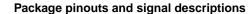

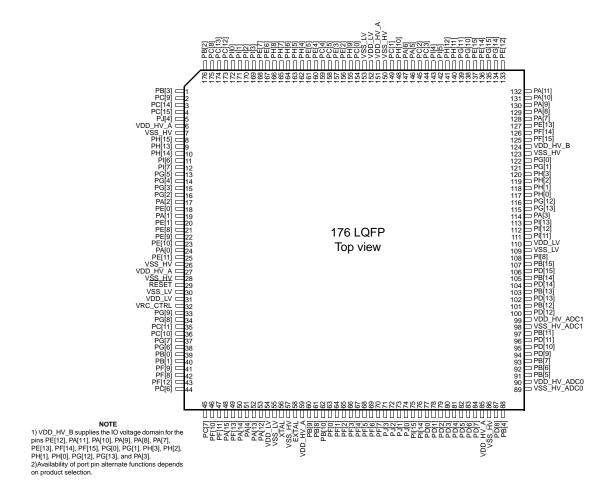

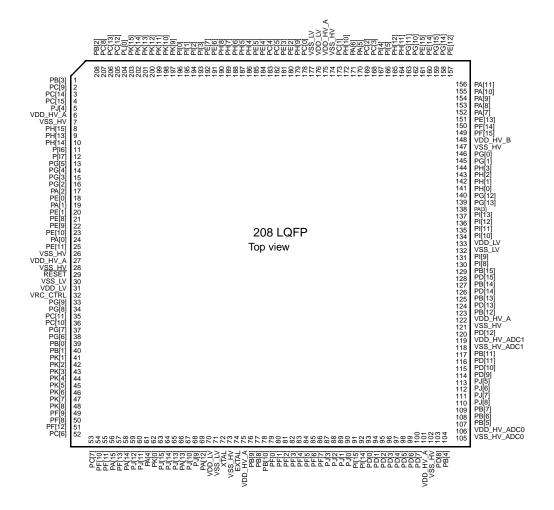

The available LQFP pinouts and the MAPBGA ballmaps are provided in the following figures. For functional port pin description, see Table 4.

Figure 2. 176-pin LQFP configuration

MPC5646C Data Sheet, Rev.6

#### NOTE

- 1) VDD\_HV\_B supplies the IO voltage domain for the pins PE[12], PA[11], PA[10], PA[9], PA[8], PA[7], PE[13], PF[14], PF[15], PG[0], PG[1], PH[3], PH[2], PH[1], PH[0], PG[12], PG[13], and PA[3].

- 2) Availability of port pin alternate functions depends on product selection.

Figure 3. 208-pin LQFP configuration

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

|---|--------|--------------|--------|--------|--------|--------------|--------|--------|--------------|--------|--------|--------|--------------|--------|-----------------|-----------------|---|

| Α | PC[15] | PB[2]        | PC[13] | PI[1]  | PE[7]  | PH[8]        | PE[2]  | PE[4]  | PC[4]        | PE[3]  | PH[9]  | PI[4]  | PH[11]       | PE[14] | PA[10]          | PG[11]          | А |

| В | PH[13] | PC[14]       | PC[8]  | PC[12] | PI[3]  | PE[6]        | PH[5]  | PE[5]  | PC[5]        | PC[0]  | PC[2]  | PH[12] | PG[10]       | PA[11] | PA[9]           | PA[8]           | В |

| С | PH[14] | VDD_HV<br>_A | PC[9]  | PL[0]  | PI[0]  | PH[7]        | PH[6]  | VSS_LV | VDD_HV<br>_A | PA[5]  | PC[3]  | PE[15] | PG[14]       | PE[12] | PA[7]           | PE[13]          | С |

| D | PG[5]  | PI[6]        | PJ[4]  | PB[3]  | PK[15] | PI[2]        | PH[4]  | VDD_LV | PC[1]        | PH[10] | PA[6]  | PI[5]  | PG[15]       | PF[14] | PF[15]          | PH[2]           | D |

| E | PG[3]  | PI[7]        | PH[15] | PG[2]  |        | I            |        | I      |              | I      |        |        | PG[0]        | PG[1]  | PH[0]           | VDD_HV<br>_A    | E |

| F | PA[2]  | PG[4]        | PA[1]  | PE[1]  | -      |              |        |        |              |        |        |        | PH[1]        | PH[3]  | PG[12]          | PG[13]          | F |

| G | PE[8]  | PE[0]        | PE[10] | PA[0]  | -      |              | VSS_HV | VSS_HV | VSS_HV       | VSS_HV |        |        | VDD_HV<br>_B | PI[13] | PI[12]          | PA[3]           | G |

| Н | PE[9]  | VDD_HV<br>_A | PE[11] | PK[1]  | -      |              | VSS_LV | VSS_HV | VSS_HV       | VSS_HV |        |        | VDD_HV<br>_A | VDD_LV | VSS_LV          | PI[11]          | н |

| J | VSS_HV | VRC_CT<br>RL | VDD_LV | PG[9]  |        |              | VSS_LV | VSS_LV | VSS_HV       | VSS_HV |        |        | PD[15]       | PI[8]  | PI[9]           | PI[10]          | J |

| К | RESET  | VSS_LV       | PG[8]  | PC[11] | -      |              | VSS_LV | VSS_LV | VSS_LV       | VDD_LV |        |        | PD[14]       | PD[13] | PB[14]          | PB[15]          | К |

| L | PC[10] | PG[7]        | PB[0]  | PK[2]  |        |              |        |        |              |        | J      |        | PD[12]       | PB[12] | PB[13]          | VDD_HV<br>_ADC1 | L |

| М | PG[6]  | PB[1]        | PK[4]  | PF[9]  |        |              |        |        |              |        |        |        | PB[11]       | PD[10] | PD[11]          | VSS_HV<br>_ADC1 | М |

| N | PK[3]  | PF[8]        | PC[6]  | PC[7]  | PJ[13] | VDD_HV<br>_A | PB[10] | PF[6]  | VDD_HV<br>_A | PJ[1]  | PD[2]  | PJ[5]  | PB[5]        | PB[6]  | PJ[6]           | PD[9]           | N |

| Р | PF[12] | PF[10]       | PF[13] | PA[14] | PJ[9]  | PA[12]       | PF[0]  | PF[5]  | PF[7]        | PJ[3]  | PI[15] | PD[4]  | PD[7]        | PD[8]  | PJ[8]           | PJ[7]           | Р |

| R | PF[11] | PA[15]       | PJ[11] | PJ[15] | PA[13] | PF[2]        | PF[3]  | PF[4]  | VDD_LV       | PJ[2]  | PJ[0]  | PD[0]  | PD[3]        | PD[6]  | VDD_HV<br>_ADC0 | PB[7]           | R |

| Т | PJ[12] | PA[4]        | PK[0]  | PJ[14] | PJ[10] | PF[1]        | XTAL   | EXTAL  | VSS_LV       | PB[9]  | PB[8]  | PI[14] | PD[1]        | PD[5]  | VSS_HV<br>_ADC0 | PB[4]           | Т |

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

#### Notes:

MPC5646C Data Sheet, Rev.6

<sup>1)</sup> VDD\_HV\_B supplies the IO voltage domain for the pins PE[12], PA[11], PA[10], PA[9], PA[8], PA[7], PE[13], PF[14], PF[15], PG[0], PG[1], PH[3], PH[2], PH[1], PH[0], PG[12], PG[13], and PA[3].

2) Availability of port pin alternate functions depends on product selection.

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

|---|--------|--------------|--------|--------|--------|--------------|--------|--------|--------------|--------|--------|--------|--------------|--------|-----------------|-----------------|---|

| Α | PC[15] | PB[2]        | PC[13] | PI[1]  | PE[7]  | PH[8]        | PE[2]  | PE[4]  | PC[4]        | PE[3]  | PH[9]  | PI[4]  | PH[11]       | PE[14] | PA[10]          | PG[11]          | A |

| В | PH[13] | PC[14]       | PC[8]  | PC[12] | PI[3]  | PE[6]        | PH[5]  | PE[5]  | PC[5]        | PC[0]  | PC[2]  | PH[12] | PG[10]       | PA[11] | PA[9]           | PA[8]           | В |

| С | PH[14] | VDD_HV_<br>A | PC[9]  | PL[0]  | PI[0]  | PH[7]        | PH[6]  | VSS_LV | VDD_HV_<br>A | PA[5]  | PC[3]  | PE[15] | PG[14]       | PE[12] | PA[7]           | PE[13]          | С |

| D | PG[5]  | PI[6]        | PJ[4]  | PB[3]  | PK[15] | PI[2]        | PH[4]  | VDD_LV | PC[1]        | PH[10] | PA[6]  | PI[5]  | PG[15]       | PF[14] | PF[15]          | PH[2]           | D |

| E | PG[3]  | PI[7]        | PH[15] | PG[2]  | VDD_LV | VSS_LV       | PK[10] | PK[9]  | PM[1]        | PM[0]  | PL[15] | PL[14] | PG[0]        | PG[1]  | PH[0]           | VDD_HV_<br>A    | Е |

| F | PA[2]  | PG[4]        | PA[1]  | PE[1]  | PL[2]  | PM[6]        | PL[1]  | PK[11] | PM[5]        | PL[13] | PL[12] | PM[2]  | PH[1]        | PH[3]  | PG[12]          | PG[13]          | F |

| G | PE[8]  | PE[0]        | PE[10] | PA[0]  | PL[3]  | VSS_HV       | VSS_HV | VSS_HV | VSS_HV       | VSS_HV | VSS_HV | PK[12] | VDD_HV_<br>B | PI[13] | PI[12]          | PA[3]           | G |

| Н | PE[9]  | VDD_HV_<br>A | PE[11] | PK[1]  | PL[4]  | VSS_LV       | VSS_LV | VSS_HV | VSS_HV       | VSS_HV | VSS_HV | PK[13] | VDD_HV_<br>A | VDD_LV | VSS_LV          | PI[11]          | н |

| J | VSS_HV | VRC_CTR<br>L | VDD_LV | PG[9]  | PL[5]  | VSS_LV       | VSS_LV | VSS_LV | VSS_HV       | VSS_HV | VSS_HV | PK[14] | PD[15]       | PI[8]  | PI[9]           | PI[10]          | J |

| К | RESET  | VSS_LV       | PG[8]  | PC[11] | PL[6]  | VSS_LV       | VSS_LV | VSS_LV | VSS_LV       | VDD_LV | VDD_LV | PM[3]  | PD[14]       | PD[13] | PB[14]          | PB[15]          | К |

| L | PC[10] | PG[7]        | PB[0]  | PK[2]  | PL[7]  | VSS_LV       | VSS_LV | VSS_LV | VSS_LV       | VDD_LV | VDD_LV | PM[4]  | PD[12]       | PB[12] | PB[13]          | VDD_HV_<br>ADC1 | L |

| М | PG[6]  | PB[1]        | PK[4]  | PF[9]  | PK[5]  | PK[6]        | PK[7]  | PK[8]  | PL[8]        | PL[9]  | PL[10] | PL[11] | PB[11]       | PD[10] | PD[11]          | VSS_HV_<br>ADC1 | М |

| N | PK[3]  | PF[8]        | PC[6]  | PC[7]  | PJ[13] | VDD_HV_<br>A | PB[10] | PF[6]  | VDD_HV_<br>A | PJ[1]  | PD[2]  | PJ[5]  | PB[5]        | PB[6]  | PJ[6]           | PD[9]           | N |

| Р | PF[12] | PF[10]       | PF[13] | PA[14] | PJ[9]  | PA[12]       | PF[0]  | PF[5]  | PF[7]        | PJ[3]  | PI[15] | PD[4]  | PD[7]        | PD[8]  | PJ[8]           | PJ[7]           | Р |

| R | PF[11] | PA[15]       | PJ[11] | PJ[15] | PA[13] | PF[2]        | PF[3]  | PF[4]  | VDD_LV       | PJ[2]  | PJ[0]  | PD[0]  | PD[3]        | PD[6]  | VDD_HV_<br>ADC0 | PB[7]           | R |

| Т | PJ[12] | PA[4]        | PK[0]  | PJ[14] | PJ[10] | PF[1]        | XTAL   | EXTAL  | VSS_LV       | PB[9]  | PB[8]  | PI[14] | PD[1]        | PD[5]  | VSS_HV_<br>ADC0 | PB[4]           | Т |

|   | 1      | 2            | 3      | 4      | 5      | 6            | 7      | 8      | 9            | 10     | 11     | 12     | 13           | 14     | 15              | 16              |   |

#### Notes:

Figure 4. 256-pin BGA configuration

## 3.1 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$$S = Slow^1$$

$M = Medium^{1, 2}$

MPC5646C Data Sheet, Rev.6

<sup>1)</sup>  $VDD_HV_B$  supplies the IO voltage domain for the pins PE[12], PA[11], PA[10], PA[9], PA[8], PA[7], PE[13], PF[14], PF[15], PG[0], PG[1], PH[3], PH[2], PH[1], PH[0], PG[13], PA[3], PA[3], and PM[4].

<sup>2)</sup> Availability of port pin alternate functions depends on product selection.

<sup>1.</sup> See the I/O pad electrical characteristics in the device data sheet for details.

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium. For example, Fast/Medium pad will be Medium by default at reset. Similarly, Slow/Medium pad will be Slow by default. Only exception is PC[1] which is in medium configuration by default (refer to PCR.SRC in the reference manual, Pad Configuration Registers (PCR0—PCR198)).

$F = Fast^{1, 2}$

I = Input only with analog feature<sup>1</sup>

A = Analog

# 3.2 System pins

The system pins are listed in Table 3.

Table 3. System pin descriptions

|          |                                                                                                                                                                            |                  |                |                                                | Pi       | in numb  | er         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------------------------------------|----------|----------|------------|

| Port pin | Function                                                                                                                                                                   | I/O<br>direction | Pad<br>type    | RESET<br>config.                               | 176 LQFP | 208 LQFP | 256 MAPBGA |

| RESET    | Bidirectional reset with Schmitt-Trigger characteristics and noise filter.                                                                                                 | I/O              | M              | Input, weak<br>pull-up only<br>after<br>PHASE2 | 29       | 29       | K1         |

| EXTAL    | Analog input of the oscillator amplifier circuit. Needs to be grounded if oscillator bypass mode is used.                                                                  | I                | A <sup>1</sup> | _                                              | 58       | 74       | Т8         |

| XTAL     | Analog output of the oscillator amplifier circuit, when the oscillator is not in bypass mode.  Analog input for the clock generator when the oscillator is in bypass mode. | I/O              | A <sup>1</sup> | _                                              | 56       | 72       | T7         |

#### NOTES

# 3.3 Functional ports

The functional port pins are listed in Table 4.

For analog pads, it is not recommended to enable IBE if APC is enabled to avoid extra current in middle range voltage.

Table 4. Functional port pin descriptions

|             |        |                                    |                                                                    |                                               |                                  |          |                  | Piı      | n numbe  | er         |

|-------------|--------|------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|----------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR    | Alternate<br>function <sup>1</sup> | Function                                                           | Peripheral                                    | I/O<br>direction <sup>2</sup>    | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PA[0]       | PCR[0] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>E0UC[13]<br>WKPU[19]<br>CAN1RX     | SIUL eMIOS_0 MC_CGM eMIOS_0 WKPU FlexCAN_1    | /O  /O  /O  /O                   | M/S      | Tristate         | 24       | 24       | G4         |

| PA[1]       | PCR[1] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[1] E0UC[1] — — WKPU[2] CAN3RX NMI[0] <sup>3</sup>             | SIUL eMIOS_0 WKPU FlexCAN_3 WKPU              | I/O<br>I/O<br>—<br>—<br>—<br>—   | S        | Tristate         | 19       | 19       | F3         |

| PA[2]       | PCR[2] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[2]<br>E0UC[2]<br>—<br>MA[2]<br>WKPU[3]<br>NMI[1] <sup>3</sup> | SIUL<br>eMIOS_0<br>—<br>ADC_0<br>WKPU<br>WKPU | I/O<br>I/O<br>—<br>O<br>I        | S        | Tristate         | 17       | 17       | F1         |

| PA[3]       | PCR[3] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[3] E0UC[3] LIN5TX CS4_1 RX_ER_CLK EIRQ[0] ADC1_S[0]           | SIUL eMIOS_0 LINFlexD_5 DSPI_1 FEC SIUL ADC_1 | I/O<br>I/O<br>O<br>O<br>I<br>I   | M/S      | Tristate         | 114      | 138      | G16        |

| PA[4]       | PCR[4] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[4]<br>E0UC[4]<br>—<br>CS0_1<br>LIN5RX<br>WKPU[9]              | SIUL eMIOS_0  DSPI_1 LINFlexD_5 WKPU          | /O<br> /O<br>  /O<br>  /O<br>  - | S        | Tristate         | 51       | 61       | T2         |

| PA[5]       | PCR[5] | AF0<br>AF1<br>AF2                  | GPIO[5]<br>E0UC[5]<br>LIN4TX                                       | SIUL<br>eMIOS_0<br>LINFlexD_4                 | I/O<br>I/O<br>O                  | M/S      | Tristate         | 146      | 170      | C10        |

| PA[6]       | PCR[6] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[6]<br>E0UC[6]<br>—<br>CS1_1<br>LIN4RX<br>EIRQ[1]              | SIUL eMIOS_0 DSPI_1 LINFlexD_4 SIUL           | I/O<br>I/O<br>—<br>O<br>I        | S        | Tristate         | 147      | 171      | D11        |

Table 4. Functional port pin descriptions (continued)

|             |         |                                         |                                                         |                                                           |                                            |          |                           | Pir      | numbe    | er         |

|-------------|---------|-----------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|----------|---------------------------|----------|----------|------------|

| Port<br>pin | PCR     | Alternate<br>function <sup>1</sup>      | Function                                                | Peripheral                                                | I/O<br>direction <sup>2</sup>              | Pad type | RESET<br>config.          | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PA[7]       | PCR[7]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[7] E0UC[7] LIN3TX — RXD[2] EIRQ[2] ADC1_S[1]       | SIUL eMIOS_0 LINFlexD_3 FEC SIUL ADC_1                    | I/O<br>I/O<br>O<br>-<br>I<br>I             | M/S      | Tristate                  | 128      | 152      | C15        |

| PA[8]       | PCR[8]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[8] E0UC[8] E0UC[14] — RXD[1] EIRQ[3] ABS[0] LIN3RX | SIUL eMIOS_0 eMIOS_0 FEC SIUL MC_RGM LINFlexD_3           | I/O<br>I/O<br>I/O<br>—<br>—<br>—<br>—<br>— | M/S      | Input,<br>weak<br>pull-up | 129      | 153      | B16        |

| PA[9]       | PCR[9]  | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[9]<br>E0UC[9]<br>—<br>CS2_1<br>RXD[0]<br>FAB       | SIUL<br>eMIOS_0<br>—<br>DSPI1<br>FEC<br>MC_RGM            | I/O<br>I/O<br>—<br>O<br>I                  | M/S      | Pull-<br>down             | 130      | 154      | B15        |

| PA[10]      | PCR[10] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[10] E0UC[10] SDA LIN2TX COL ADC1_S[2] SIN_1        | SIUL eMIOS_0 I <sup>2</sup> C LINFlexD_2 FEC ADC_1 DSPI_1 | I/O<br>I/O<br>I/O<br>O<br>I                | M/S      | Tristate                  | 131      | 155      | A15        |

| PA[11]      | PCR[11] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[11] E0UC[11] SCL — RX_ER EIRQ[16] LIN2RX ADC1_S[3] | SIUL eMIOS_0 I <sup>2</sup> C — FEC SIUL LINFlexD_2 ADC_1 | I/O<br>I/O<br>I/O<br>—<br>—<br>—<br>—<br>— | M/S      | Tristate                  | 132      | 156      | B14        |

| PA[12]      | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[12]<br>—<br>E0UC[28]<br>CS3_1<br>EIRQ[17]<br>SIN_0 | SIUL eMIOS_0 DSPI1 SIUL DSPI_0                            | I/O<br>—<br>I/O<br>O<br>I                  | S        | Tristate                  | 53       | 69       | P6         |

MPC5646C Data Sheet, Rev.6

Table 4. Functional port pin descriptions (continued)

|             |         |                                    |                                                   |                                                   |                               |          |                  | Pir      | numbe    | er         |

|-------------|---------|------------------------------------|---------------------------------------------------|---------------------------------------------------|-------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                          | Peripheral                                        | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PA[13]      | PCR[13] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[13]<br>SOUT_0<br>E0UC[29]<br>—               | SIUL<br>DSPI_0<br>eMIOS_0<br>—                    | I/O<br>O<br>I/O               | M/S      | Tristate         | 52       | 66       | R5         |

| PA[14]      | PCR[14] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[14]<br>SCK_0<br>CS0_0<br>E0UC[0]<br>EIRQ[4]  | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>SIUL       | I/O<br>I/O<br>I/O<br>I/O      | M/S      | Tristate         | 50       | 58       | P4         |

| PA[15]      | PCR[15] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[15]<br>CS0_0<br>SCK_0<br>E0UC[1]<br>WKPU[10] | SIUL<br>DSPI_0<br>DSPI_0<br>eMIOS_0<br>WKPU       | I/O<br>I/O<br>I/O<br>I/O      | M/S      | Tristate         | 48       | 56       | R2         |

| PB[0]       | PCR[16] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[16]<br>CAN0TX<br>E0UC[30]<br>LIN0TX          | SIUL<br>FlexCAN_0<br>eMIOS_0<br>LINFlexD_0        | I/O<br>O<br>I/O<br>I          | M/S      | Tristate         | 39       | 39       | L3         |

| PB[1]       | PCR[17] | AF0<br>AF1<br>AF2<br>—<br>—        | GPIO[17]  E0UC[31]  LINORX  WKPU[4]  CANORX       | SIUL eMIOS_0 LINFlexD_0 WKPU FlexCAN_0            | I/O<br><br>I/O<br>I<br>I      | S        | Tristate         | 40       | 40       | M2         |

| PB[2]       | PCR[18] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[18]<br>LIN0TX<br>SDA<br>E0UC[30]             | SIUL<br>LINFlexD_0<br>I <sup>2</sup> C<br>eMIOS_0 | I/O<br>O<br>I/O<br>I/O        | M/S      | Tristate         | 176      | 208      | A2         |

| PB[3]       | PCR[19] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[19] E0UC[31] SCL — WKPU[11] LIN0RX           | SIUL eMIOS_0 I <sup>2</sup> C — WKPU LINFlexD_0   | I/O<br>I/O<br>I/O<br>—<br>I   | S        | Tristate         | 1        | 1        | D4         |

| PB[4]       | PCR[20] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPI[20] ADC0_P[0] ADC1_P[0]                       | SIUL  ADC_0 ADC_1                                 | <br> -<br> -<br> -<br> -      | I        | Tristate         | 88       | 104      | T16        |

Table 4. Functional port pin descriptions (continued)

|                    |         |                                         |                                                                       |                                                            |                                            |          |                  | Pir      | n numbe  | er         |

|--------------------|---------|-----------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------|----------|------------------|----------|----------|------------|

| Port<br>pin        | PCR     | Alternate<br>function <sup>1</sup>      | Function                                                              | Peripheral                                                 | I/O<br>direction <sup>2</sup>              | Pad type | RESET<br>config. | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PB[5]              | PCR[21] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPI[21] ADC0_P[1] ADC1_P[1]                                           | SIUL<br><br><br>ADC_0<br>ADC_1                             | -<br>-<br>-<br>-                           | _        | Tristate         | 91       | 107      | N13        |

| PB[6]              | PCR[22] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPI[22]  ADC0_P[2] ADC1_P[2]                                          | SIUL  ADC_0 ADC_1                                          | <br> -<br> -<br> -<br> -                   | 1        | Tristate         | 92       | 108      | N14        |

| PB[7]              | PCR[23] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPI[23] ADC0_P[3] ADC1_P[3]                                           | SIUL ADC_0 ADC_1                                           | <br> -<br> -<br> -<br> -                   | I        | Tristate         | 93       | 109      | R16        |

| PB[8]              | PCR[24] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPI[24]  ADC0_S[0] ADC1_S[4] WKPU[25] OSC32k_XTAL <sup>4</sup>        | SIUL  ADC_0 ADC_1 WKPU SXOSC                               | <br> -<br> -<br> -<br> -<br> -<br> -<br> - | I        | _                | 61       | 77       | T11        |

| PB[9] <sup>5</sup> | PCR[25] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPI[25]  — — — ADC0_S[1] ADC1_S[5] WKPU[26] OSC32k_EXTAL <sup>4</sup> | SIUL  ADC_0 ADC_1 WKPU SXOSC                               | <br> -<br> -<br> -<br> -<br> -<br> -<br> - | 1        | _                | 60       | 76       | T10        |

| PB[10]             | PCR[26] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[26] SOUT_1 CAN3TX — ADC0_S[2] ADC1_S[6] WKPU[8]                  | SIUL<br>DSPI_1<br>FlexCAN_3<br>—<br>ADC_0<br>ADC_1<br>WKPU | I/O<br>O<br>—<br>—<br>I<br>I               | S        | Tristate         | 62       | 78       | N7         |

MPC5646C Data Sheet, Rev.6

Table 4. Functional port pin descriptions (continued)

|                    |         |                                    |                                             |                                          |                               |          |                           | Pir      | n numbe  | er         |

|--------------------|---------|------------------------------------|---------------------------------------------|------------------------------------------|-------------------------------|----------|---------------------------|----------|----------|------------|

| Port<br>pin        | PCR     | Alternate<br>function <sup>1</sup> | Function                                    | Peripheral                               | I/O<br>direction <sup>2</sup> | Pad type | RESET<br>config.          | 176 LQFP | 208 LQFP | 256 MAPBGA |

| PB[11]             | PCR[27] | AF0<br>AF1<br>AF2                  | GPIO[27]<br>E0UC[3]<br>—                    | SIUL<br>eMIOS_0                          | I/O<br>I/O<br>—               | S        | Tristate                  | 97       | 117      | M13        |

|                    |         | AF3<br>—                           | CS0_0<br>ADC0_S[3]                          | DSPI_0<br>ADC_0                          | I/O<br>I                      |          |                           |          |          |            |

| PB[12]             | PCR[28] | AF0<br>AF1<br>AF2                  | GPIO[28]<br>E0UC[4]<br>—                    | SIUL<br>eMIOS_0<br>—                     | I/O<br>I/O<br>—               | S        | Tristate                  | 101      | 123      | L14        |

|                    |         | AF3                                | CS1_0<br>ADC0_X[0]                          | DSPI_0<br>ADC_0                          | 0<br>1                        |          |                           |          |          |            |

| PB[13]             | PCR[29] | AF0<br>AF1<br>AF2                  | GPIO[29]<br>E0UC[5]<br>—                    | SIUL<br>eMIOS_0<br>—                     | I/O<br>I/O<br>—               | S        | Tristate                  | 103      | 125      | L15        |

|                    |         | AF3<br>—                           | CS2_0<br>ADC0_X[1]                          | DSPI_0<br>ADC_0                          | 0<br>                         |          |                           |          |          |            |

| PB[14]             | PCR[30] | AF0<br>AF1<br>AF2                  | GPIO[30]<br>E0UC[6]<br>—                    | SIUL<br>eMIOS_0<br>—                     | I/O<br>I/O<br>—               | S        | Tristate                  | 105      | 127      | K15        |

|                    |         | AF3<br>—                           | CS3_0<br>ADC0_X[2]                          | DSPI_0<br>ADC_0                          | 0<br>1                        |          |                           |          |          |            |

| PB[15]             | PCR[31] | AF0<br>AF1<br>AF2                  | GPIO[31]<br>E0UC[7]<br>—                    | SIUL<br>eMIOS_0<br>—                     | I/O<br>I/O                    | S        | Tristate                  | 107      | 129      | K16        |

|                    |         | AF3                                | CS4_0<br>ADC0_X[3]                          | DSPI_0<br>ADC_0                          | 0<br>1                        |          |                           |          |          |            |

| PC[0] <sup>6</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                   | SIUL<br>—<br>JTAGC<br>—                  | I/O<br>—<br>I<br>—            | M/S      | Input,<br>weak<br>pull-up | 154      | 178      | B10        |

| PC[1] <sup>6</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[33]<br>—<br>TDO<br>—                   | SIUL<br>—<br>JTAGC<br>—                  | I/O<br>—<br>O<br>—            | F/M      | Tristate                  | 149      | 173      | D9         |

| PC[2]              | PCR[34] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[34]<br>SCK_1<br>CAN4TX<br>—<br>EIRQ[5] | SIUL<br>DSPI_1<br>FlexCAN_4<br>—<br>SIUL | I/O<br>I/O<br>O<br>—          | M/S      | Tristate                  | 145      | 169      | B11        |

Table 4. Functional port pin descriptions (continued)

| PCR[35] | PCR     | ate<br>on <sup>1</sup>             |                                                      |                                                                                                     |                                                                                                                                                                                                                                                 |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          | er         |

|---------|---------|------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------------|

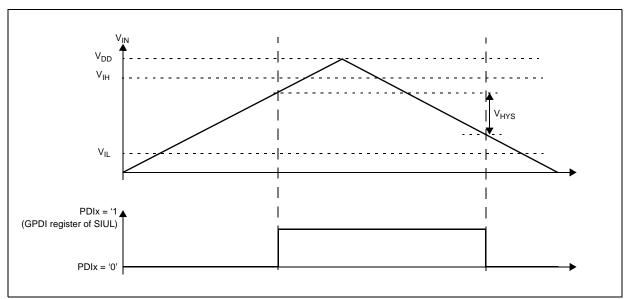

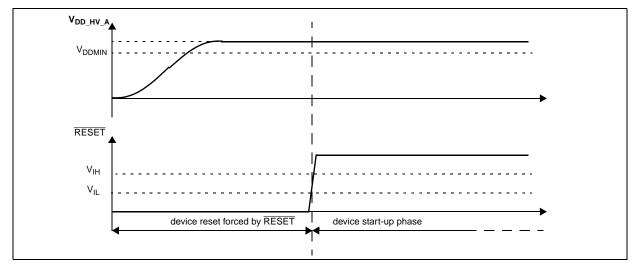

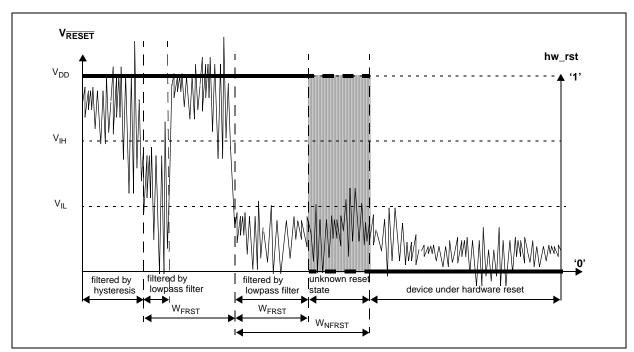

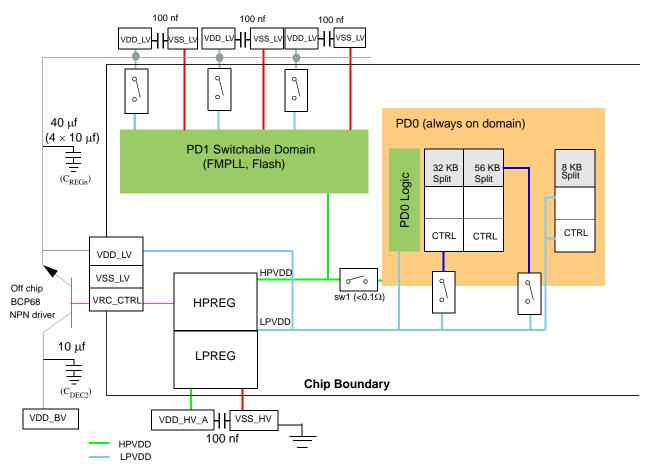

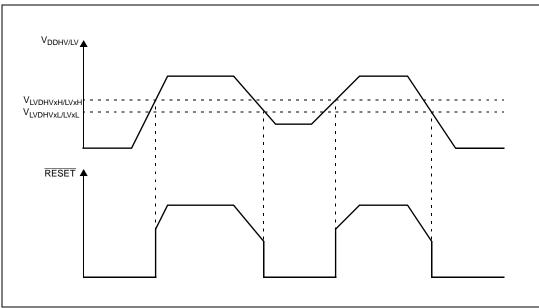

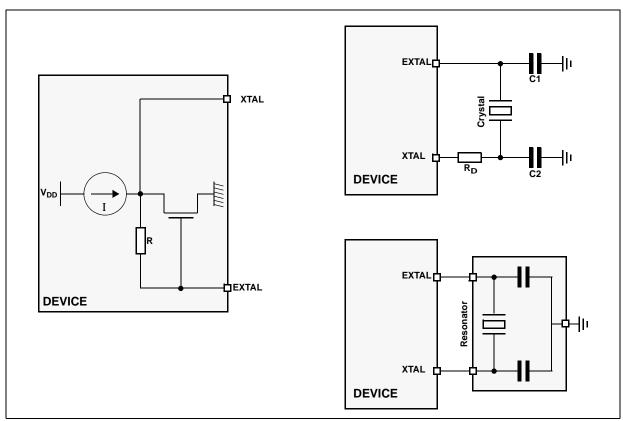

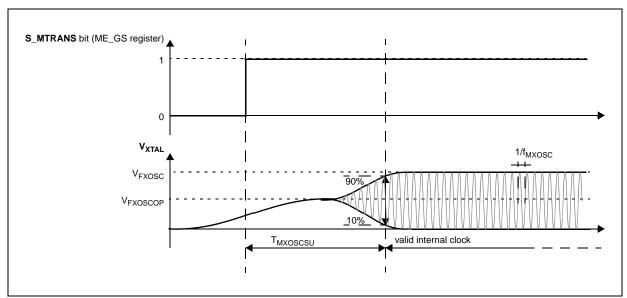

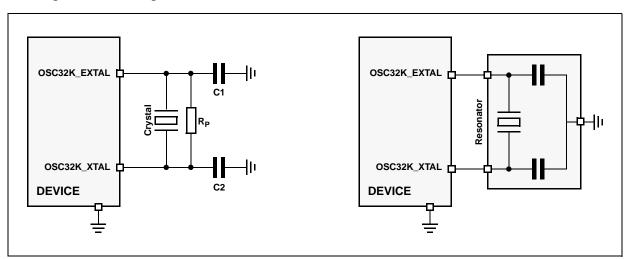

| PCR[35] |         | Alternate<br>function <sup>1</sup> | Function                                             | Peripheral                                                                                          | I/O<br>direction <sup>2</sup>                                                                                                                                                                                                                   | Pad type                                                                                   | RESET<br>config.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 176 LQFP | 208 LQFP | 256 MAPBGA |