# **AD7226\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

###

View a parametric search of comparable parts.

### DOCUMENTATION

#### **Application Notes**

- AN-317: Circuit Applications of the AD7226 Quad CMOS DAC

- AN-321: 3-Phase Sine Wave Generation Using the AD7226 Quad DAC

#### **Data Sheet**

- AD7226: Military Data Sheet

- AD7226: LC<sup>2</sup>MOS Quad 8-Bit D/A Converter Data Sheet

### REFERENCE MATERIALS

#### **Solutions Bulletins & Brochures**

Digital to Analog Converters ICs Solutions Bulletin

### DESIGN RESOURCES

- AD7226 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD7226 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

#

# **DUAL SUPPLY**

| Parameter                                       | K, B Versions <sup>2</sup> | Unit           | Conditions/Comments                                          |

|-------------------------------------------------|----------------------------|----------------|--------------------------------------------------------------|

| STATIC PERFORMANCE                              |                            |                |                                                              |

| Resolution                                      | 8                          | Bits           |                                                              |

| Total Unadjusted Error                          | ±1                         | LSB max        | $V_{DD} = 15 \text{ V} \pm 5\%, V_{REF} = 10 \text{ V}$      |

| Relative Accuracy                               | $\pm 0.5$                  | LSB max        |                                                              |

| Differential Nonlinearity                       | ±1                         | LSB max        | Guaranteed Monotonic                                         |

| Full-Scale Error                                | $\pm 0.5$                  | LSB max        |                                                              |

| Full-Scale Temperature Coefficient              | $\pm 20$                   | ppm/°C typ     | $V_{DD} = 14 \text{ V}$ to 16.5 V, $V_{REF} = +10 \text{ V}$ |

| Zero Code Error                                 | $\pm 20$                   | mV max         |                                                              |

| Zero Code Error Temperature Coefficient         | ±50                        | µV/°C typ      |                                                              |

| REFERENCE INPUT                                 |                            |                |                                                              |

| Voltage Range                                   | 2 to (V <sub>DD</sub> – 4) | V min to V max |                                                              |

| Input Resistance                                | 2                          | $k\Omega$ min  |                                                              |

| Input Capacitance <sup>3</sup>                  | 50                         | pF min         | Occurs when each DAC is loaded with all 0s.                  |

|                                                 | 200                        | pF max         | Occurs when each DAC is loaded with all 1s.                  |

| DIGITAL INPUTS                                  |                            |                |                                                              |

| Input High Voltage, V <sub>INH</sub>            | 2.4                        | V min          |                                                              |

| Input Low Voltage, V <sub>INL</sub>             | 0.8                        | V max          |                                                              |

| Input Leakage Current                           | ±1                         | µA max         | $V_{IN} = 0 V \text{ or } V_{DD}$                            |

| Input Capacitance                               | 8                          | pF max         |                                                              |

| Input Coding                                    | Binary                     |                |                                                              |

| DYNAMIC PERFORMANCE                             |                            |                |                                                              |

| Voltage Output Slew Rate <sup>4</sup>           | 2.5                        | V/µs min       |                                                              |

| Voltage Output Settling Time <sup>4</sup>       | 4                          | μs max         | $V_{REF}$ = 10 V; Settling Time to ±1/2 LSB                  |

| Digital Crosstalk                               | 10                         | nV secs typ    |                                                              |

| Minimum Load Resistance                         | 2                          | kΩ min         | $V_{OUT} = 10 V$                                             |

| POWER SUPPLIES                                  |                            |                |                                                              |

| V <sub>DD</sub> Range                           | 11.4/16.5                  | V min/V max    | For Specified Performance                                    |

| I <sub>DD</sub>                                 | 13                         | mA max         | Outputs Unloaded; $V_{IN} = V_{INL}$ or $V_{INH}$            |

| I <sub>SS</sub>                                 | 11                         | mA max         | Outputs Unloaded; $V_{IN} = V_{INL}$ or $V_{INH}$            |

| SWITCHING CHARACTERISTICS <sup>4, 5</sup>       |                            |                |                                                              |

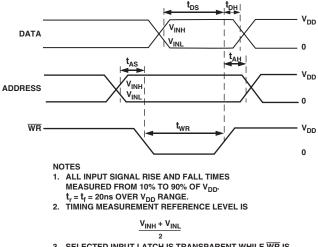

| Address to Write Setup Time, t <sub>AS</sub>    | 0                          | ns min         |                                                              |

| Address to Write Hold Time, $t_{AH}$            | 0                          | ns min         |                                                              |

| Data Valid to Write Setup Time, t <sub>DS</sub> | 50                         | ns min         |                                                              |

| Data Valid to Write Hold Time, $t_{DH}$         | 0                          | ns min         |                                                              |

| Write Pulsewidth, t <sub>WR</sub>               | 50                         | ns min         |                                                              |

NOTES

<sup>1</sup>Maximum possible reference voltage.

<sup>2</sup>Temperature ranges are as follows:

K Version: -40°C to +85°C

B Version: -40°C to +85°C

<sup>3</sup>Guaranteed by design. Not production tested.

<sup>4</sup>Sample Tested at 25°C to ensure compliance.

<sup>5</sup>Switching Characteristics apply for single and dual supply operation.

Specifications subject to change without notice.

# $\label{eq:single_signal} \begin{array}{l} (V_{DD}=15~V~\pm~5\%,~V_{SS}=AGND=DGND=0~V;~V_{REF}=10~V^1~unless~otherwise~noted.\\ \\ All specifications~T_{MIN}~to~T_{MAX}~unless~otherwise~noted.) \end{array}$

| Parameter                                 | K, B Versions <sup>2</sup> | Unit          | Conditions/Comments                               |

|-------------------------------------------|----------------------------|---------------|---------------------------------------------------|

| STATIC PERFORMANCE                        |                            |               |                                                   |

| Resolution                                | 8                          | Bits          |                                                   |

| Total Unadjusted Error                    | ±2                         | LSB max       |                                                   |

| Differential Nonlinearity                 | ±1                         | LSB max       | Guaranteed Monotonic                              |

| REFERENCE INPUT                           |                            |               |                                                   |

| Input Resistance                          | 2                          | $k\Omega$ min |                                                   |

| Input Capacitance <sup>3</sup>            | 50                         | pF min        | Occurs when each DAC is loaded with all 0s.       |

|                                           | 200                        | pF max        | Occurs when each DAC is loaded with all 1s.       |

| DIGITAL INPUTS                            |                            |               |                                                   |

| Input High Voltage, V <sub>INH</sub>      | 2.4                        | V min         |                                                   |

| Input Low Voltage, V <sub>INL</sub>       | 0.8                        | V max         |                                                   |

| Input Leakage Current                     | ±1                         | μA max        | $V_{IN} = 0 V \text{ or } V_{DD}$                 |

| Input Capacitance                         | 8                          | pF max        |                                                   |

| Input Coding                              | Binary                     |               |                                                   |

| DYNAMIC PERFORMANCE                       |                            |               |                                                   |

| Voltage Output Slew Rate <sup>4</sup>     | 2                          | V/µs min      |                                                   |

| Voltage Output Settling Time <sup>4</sup> | 4                          | μs max        | Settling Time to $\pm 1/2$ LSB                    |

| Digital Crosstalk                         | 10                         | nV secs typ   |                                                   |

| Minimum Load Resistance                   | 2                          | kΩ min        | $V_{OUT} = +10 V$                                 |

| POWER SUPPLIES                            |                            |               |                                                   |

| V <sub>DD</sub> Range                     | 14.25/15.75                | V min/V max   | For Specified Performance                         |

| I <sub>DD</sub>                           | 13                         | mA max        | Outputs Unloaded; $V_{IN} = V_{INL}$ or $V_{INH}$ |

NOTES

<sup>1</sup>Maximum possible reference voltage.

<sup>2</sup>Temperature ranges are as follows:

K Version: -40°C to +85°C

B Version: -40°C to +85°C

<sup>3</sup>Guaranteed by design. Not production tested.

<sup>4</sup>Sample Tested at 25°C to ensure compliance.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $V_{DD}$ to AGND                                                                           |

|--------------------------------------------------------------------------------------------|

| $V_{DD}$ to DGND                                                                           |

| $V_{SS}$ to AGND                                                                           |

| $V_{SS}$ to DGND                                                                           |

| $V_{DD}$ to $V_{SS}$                                                                       |

| AGND to DGND                                                                               |

| Digital Input Voltage to DGND $\dots -0.3 \text{ V}, \text{V}_{\text{DD}} + 0.3 \text{ V}$ |

| $V_{\text{REF}}$ to AGND                                                                   |

| $V_{OUT}$ to AGND <sup>2</sup>                                                             |

| Power Dissipation (Any Package) to 75°C                                                    |

| Derates above $75^{\circ}$ C by 2.0 mW/°C                                                  |

| Operating Temperature                                                                      |

| Commercial (K Version)40°C to +85°C                                                        |

| Industrial (B Version) $-40^{\circ}$ C to $+85^{\circ}$ C                                  |

| Storage Temperature                                                                        |

|                                                                                            |

| Lead Temperature (Soldering, 10 secs) 300°C                                                |

| NOTES                                                                                      |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Outputs may be shorted to AGND provided that the power dissipation of the package is not exceeded. Typically short circuit current to AGND is 50 mA.

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7226 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

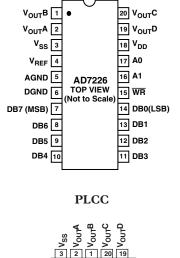

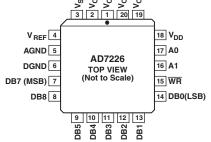

#### PIN CONFIGURATIONS

#### **DIP and SOIC/SSOP**

#### TERMINOLOGY

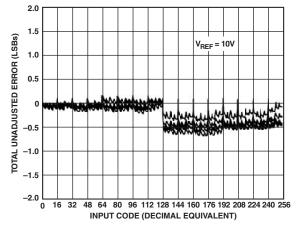

#### TOTAL UNADJUSTED ERROR

This is a comprehensive specification that includes full-scale error, relative accuracy and zero code error. Maximum output voltage is  $V_{REF} - 1$  LSB (ideal), where 1 LSB (ideal) is  $V_{REF}/256$ . The LSB size will vary over the  $V_{REF}$  range. Hence the zero code error will, relative to the LSB size, increase as  $V_{REF}$  decreases. Accordingly, the total unadjusted error, which includes the zero code error, will also vary in terms of LSB's over the  $V_{REF}$  range. As a result, total unadjusted error is specified for a fixed reference voltage of 10 V.

#### **RELATIVE ACCURACY**

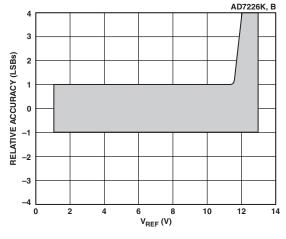

Relative Accuracy or endpoint nonlinearity, is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after allowing for zero and full-scale error and is normally expressed in LSB's or as a percentage of full-scale reading.

#### DIFFERENTIAL NONLINEARITY

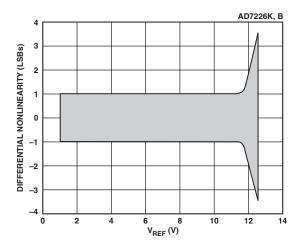

Differential Nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB max over the operating temperature range ensures monotonicity.

#### DIGITAL CROSSTALK

The glitch impulse transferred to the output of one converter due to a change in the digital input code to another of the converters. It is specified in nV secs and is measured at  $V_{REF} = 0$  V.

#### FULL SCALE ERROR

Full-Scale Error is defined as:

Measured Value - Zero Code Error - Ideal Value

# CIRCUIT INFORMATION D/A SECTION

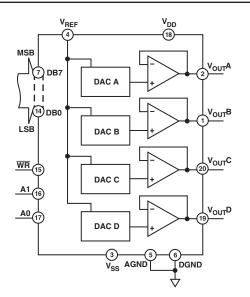

The AD7226 contains four identical, 8-bit, voltage mode digital-toanalog converters. The output voltages from the converters have the same polarity as the reference voltage allowing single supply operation. A novel DAC switch pair arrangement on the AD7226 allows a reference voltage range from 2 V to 12.5 V.

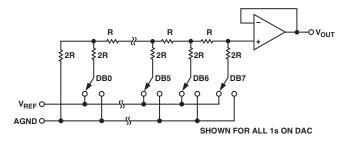

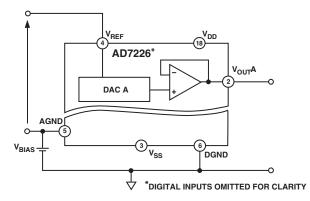

Each DAC consists of a highly stable, thin-film, R-2R ladder and eight high speed NMOS, single-pole, double-throw switches. The simplified circuit diagram for one channel is shown in Figure 1. Note that  $V_{REF}$  (Pin 4) and AGND (Pin 5) are common to all four DACs.

#### Figure 1. D/A Simplified Circuit Diagram

The input impedance at the  $V_{REF}$  pin of the AD7226 is the parallel combination of the four individual DAC reference input impedances. It is code dependent and can vary from 2 k $\Omega$  to infinity. The lowest input impedance (i.e., 2 K $\Omega$ ) occurs when all four DACs are loaded with the digital code 01010101. Therefore, it is important that the reference presents a low output impedance under changing load conditions. The nodal capacitance at the reference terminals is also code dependent and typically varies from 100 pF to 250 pF.

Each  $V_{OUT}$  pin can be considered as a digitally programmable voltage source with an output voltage of:

$$V_{OUTX} = D_X V_{REF} \tag{1}$$

where  $D_X$  is fractional representation of the digital input code and can vary from 0 to 255/256.

The source impedance is the output resistance of the buffer amplifier.

#### **OP AMP SECTION**

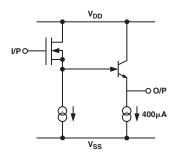

Each voltage-mode D/A converter output is buffered by a unity gain, noninverting CMOS amplifier. This buffer amplifier is capable of developing 10 V across a 2 k $\Omega$  load and can drive capacitive loads of 3300 pF. The output stage of this amplifier consists of a bipolar transistor from the V<sub>DD</sub> line and a current load to the V<sub>SS</sub>, the negative supply for the output amplifiers. This output stage is shown in Figure 2.

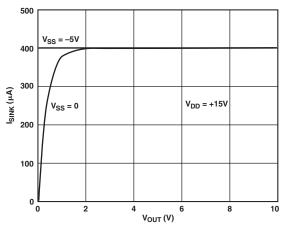

The NPN transistor supplies the required output current drive (up to 5 mA). The current load consists of NMOS transistors which normally act as a constant current sink of 400  $\mu$ A to V<sub>SS</sub>, giving each output a current sink capability of approximately 400  $\mu$ A if required.

The AD7226 can be operated single or dual supply resulting in different performance in some parameters from the output amplifiers. In single supply operation ( $V_{SS} = 0 V = AGND$ ), with the output approaching AGND (i.e., digital code approaching all 0s)

Figure 2. Amplifier Output Stage

the current load ceases to act as a current sink and begins to act as a resistive load of approximately 2 k $\Omega$  to AGND. This occurs as the NMOS transistors come out of saturation. This means that, in single supply operation, the sink capability of the amplifiers is reduced when the output voltage is at or near AGND. A typical plot of the variation of current sink capability with output voltage is shown in Figure 3.

Figure 3. Variation of ISINK with VOUT

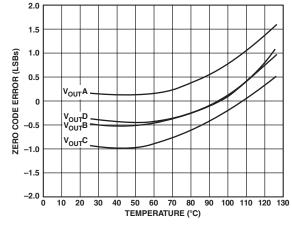

If the full sink capability is required with output voltages at or near AGND (= 0 V), then  $V_{SS}$  can be brought below 0 V by 5 V and thereby maintain the 400  $\mu$ A current sink as indicated in Figure 3. Biasing  $V_{SS}$  below 0 V also gives additional headroom in the output amplifier which allows for better zero code error performance on each output. Also improved is the slew rate and negative-going settling time of the amplifiers (discussed later).

Each amplifier offset is laser trimmed during manufacture to eliminate any requirement for offset nulling.

#### **DIGITAL SECTION**

The digital inputs of the AD7226 are both TTL and CMOS (5 V) compatible from  $V_{DD}$  = 11.4 V to 16.5 V. All logic inputs are static protected MOS gates with typical input currents of less than 1 nA. Internal input protection is achieved by an on-chip distributed diode from DGND to each MOS gate. To minimize power supply currents, it is recommended that the digital input voltages be driven as close to the supply rails (V<sub>DD</sub> and DGND) as practically possible.

#### INTERFACE LOGIC INFORMATION

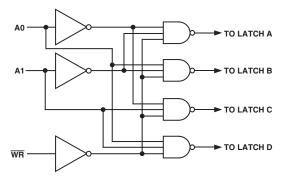

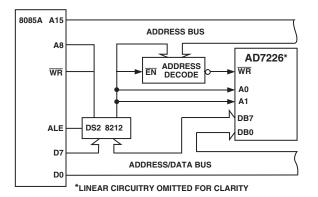

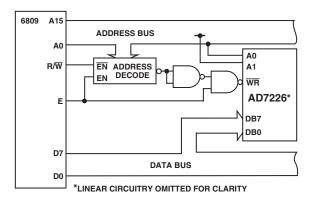

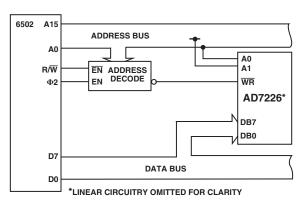

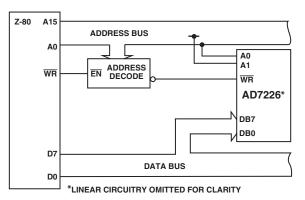

Address lines A0 and A1 select which DAC will accept data from the input port. Table I shows the selection table for the four DACs with Figure 4 showing the input control logic. When the  $\overline{WR}$  signal is LOW, the input latches of the selected DAC are transparent and its output responds to activity on the data bus. The data is latched into the addressed DAC latch on the rising edge of  $\overline{WR}$ . While  $\overline{WR}$  is high the analog outputs remain at the value corresponding to the data held in their respective latches.

Table I. AD7226 Truth Table

| <b>AD</b> 722<br>WR | 6 Control<br>A1 | Inputs<br>A0 | AD7226<br>Operation              |

|---------------------|-----------------|--------------|----------------------------------|

| Н                   | Х               | Х            | No Operation Device Not Selected |

| L                   | L               | L            | DAC A Transparent                |

| £                   | L               | L            | DAC A Latched                    |

| L                   | L               | Н            | DAC B Transparent                |

| £                   | L               | Η            | DAC B Latched                    |

| L                   | Η               | L            | DAC C Transparent                |

| 1                   | Н               | L            | DAC C Latched                    |

| L                   | Н               | Н            | DAC D Transparent                |

| ſ                   | Н               | Н            | DAC D Latched                    |

L = Low State, H = High State, X = Don't Care

Figure 4. Input Control Logic

3. SELECTED INPUT LATCH IS TRANSPARENT WHILE WR IS LOW, THUS INVALID DATA DURING THIS TIME CAN CAUSE SPURIOUS OUTPUTS.

Figure 5. Write Cycle Timing Diagram

# Typical Performance Characteristics-AD7226

$(T_A = 25^{\circ}C, V_{DD} = 15 V, V_{SS} = -5 V)$

TPC 1. Channel-to-Channel Matching

TPC 2. Relative Accuracy vs. V<sub>REF</sub>

TPC 3. Differential Nonlinearity vs. V<sub>REF</sub>

TPC 4. Zero Code Error vs. Temperature

#### SPECIFICATION RANGES

In order for the DACs to operate to their specifications, the reference voltage must be at least 4 V below the  $V_{DD}$  power supply voltage. This voltage differential is required for correct generation of bias voltages for the DAC switches.

The AD7226 is specified to operate over a V<sub>DD</sub> range from +12 V  $\pm$  5% to +15 V  $\pm$  10% (i.e., from +11.4 V to +16.5 V) with a V<sub>SS</sub> of -5 V  $\pm$  10%. Operation is also specified for a single +15 V  $\pm$  5% V<sub>DD</sub> supply. Applying a V<sub>SS</sub> of -5 V results in improved zero code error, improved output sink capability with outputs near AGND and improved negative-going settling time.

Performance is specified over a wide range of reference voltages from 2 V to  $(V_{DD} - 4 V)$  with dual supplies. This allows a range of standard reference generators to be used such as the AD780, a 2.5 V band gap reference and the AD584, a precision 10 V reference. Note that in order to achieve an output voltage range of 0 V to 10 V a nominal 15 V  $\pm$  5% power supply voltage is required by the AD7226.

#### SETTLING TIME

The output stage of the buffer amplifiers consists of a bipolar NPN transistor from the  $V_{\rm DD}$  line and a constant current load to  $V_{SS}.V_{SS}$  is the negative power supply for the output buffer amplifiers. As mentioned in the op amp section, in single supply operation the NMOS transistor will come out of saturation as the output voltage approaches AGND and will act as a resistive load of approximately 2 k $\Omega$  to AGND. As a result, the settling time for negative-going signals approaching AGND in single supply operation will be longer than for dual supply operation where the current load of 400  $\mu$ A is maintained all the way down to AGND. Positive-going settling-time is not affected by  $V_{SS}$ .

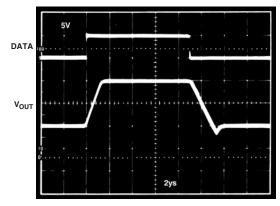

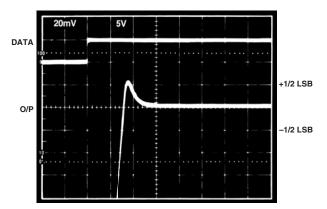

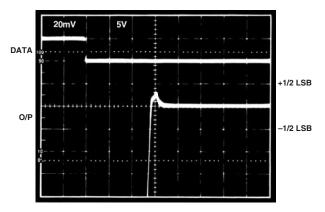

The settling-time for the AD7226 is limited by the slew-rate of the output buffer amplifiers. This can be seen from Figure 6 which shows the dynamic response for the AD7226 for a full scale change. Figures 7a and 7b show expanded settling-time photographs with the output waveforms derived from a differential input to an oscilloscope. Figure 7a shows the settling time for a positive-going step and Figure 7b shows the settling time for a negative-going output step.

Figure 6. Dynamic Response ( $V_{SS} = -5 V$ )

Figure 7a. Positive Step Settling Time ( $V_{SS} = -5 V$ )

Figure 7b. Negative Step Settling Time ( $V_{SS} = -5 V$ )

#### **GROUND MANAGEMENT**

AC or transient voltages between AGND and DGND can cause noise at the analog output. This is especially true in microprocessor systems where digital noise is prevalent. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at the AD7226. In more complex systems where the AGND and DGND intertie is on the backplane, it is recommended that two diodes be connected in inverse parallel between the AD7226 AGND and DGND pins (IN914 or equivalent).

#### **Unipolar Output Operation**

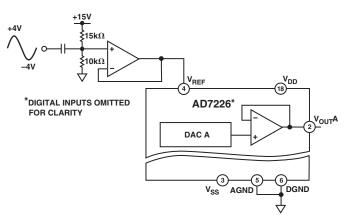

This is the basic mode of operation for each channel of the AD7226, with the output voltage having the same positive polarity as +V<sub>REF</sub>. The AD7226 can be operated single supply (V<sub>SS</sub> = AGND) or with positive/negative supplies (see op amp section which outlines the advantages of having negative V<sub>SS</sub>). The code table for unipolar output operation is shown in Table II. Note that the voltage at V<sub>REF</sub> must never be negative with respect to DGND in order to prevent parasitic transistor turn-on. Connections for the unipolar output operation are shown in Figure 8.

Figure 8. AD7226 Unipolar Output Circuit

| DAC Latch |                | Angles Output                                               |

|-----------|----------------|-------------------------------------------------------------|

| MSB       | LSB            | Analog Output                                               |

| 1111      | 1111           | $+V_{REF}\left(rac{255}{256} ight)$                        |

| 1000      | 0001           | $+V_{REF}\left(rac{129}{256} ight)$                        |

| 1000      | 0000           | $+V_{REF}\left(\frac{128}{256}\right) = +\frac{V_{REF}}{2}$ |

| 0111      | 1111           | $+V_{REF}\left(rac{127}{256} ight)$                        |

| 0000      | 0001           | $+V_{REF}\left(rac{1}{256} ight)$                          |

| 0000      | 0000           | 0 V                                                         |

|           | $(11)^{(a-8)}$ |                                                             |

#### Table II. Unipolar Code Table

Note:

$$LSB = (V_{REF})(2^{-8}) = V_{REF} \left(\frac{1}{256}\right)$$

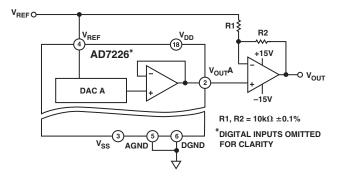

**Bipolar Output Operation**

Each of the DACs of the AD7226 can be individually configured to provide bipolar output operation. This is possible using one external amplifier and two resistors per channel. Figure 9 shows a circuit used to implement offset binary coding (bipolar operation) with DAC A of the AD7226. In this case

$$V_{OUT} = \left(1 + \frac{R^2}{R^1}\right) \times \left(D_A V_{REF}\right) - \left(\frac{R^2}{R^1}\right) \times \left(V_{REF}\right)$$

(3)

With R1 = R2

$$V_{OUT} = (2D_A - 1) \times V_{REF} \tag{4}$$

where  $D_A$  is a fractional representation of the digital word in latch A.

Mismatch between R1 and R2 causes gain and offset errors and therefore these resistors must match and track over temperature. Once again the AD7226 can be operated in single supply or from positive/negative supplies. Table III shows the digital code versus output voltage relationship for the circuit of Figure 9 with R1 = R2.

Figure 9. AD7226 Bipolar Output Circuit

| Table III. Bipola | (Offset Binary) | Code Table |

|-------------------|-----------------|------------|

|-------------------|-----------------|------------|

| DAC Latch<br>MSB | Contents<br>LSB | Analog Output                                     |

|------------------|-----------------|---------------------------------------------------|

| 1111             | 1111            | $+V_{REF}\left(\frac{127}{128}\right)$            |

| 1000             | 0001            | $+V_{REF}\left(\frac{1}{128}\right)$              |

| 1000             | 0000            | 0 V                                               |

| 0111             | 1111            | $-V_{REF}\left(rac{1}{128} ight)$                |

| 0000             | 0001            | $-V_{REF}\left(rac{127}{128} ight)$              |

| 0000             | 0000            | $-V_{REF}\left(\frac{128}{128}\right) = -V_{REF}$ |

#### AGND BIAS

(2)

The AD7226 AGND pin can be biased above system GND (AD7226 DGND) to provide an offset "zero" analog output voltage level. Figure 10 shows a circuit configuration to achieve this for channel A of the AD7226. The output voltage,  $V_{OUT}A$ , can be expressed as:

$$V_{OUT}A = V_{BLAS} + D_A(V_{IN}) \tag{5}$$

where  $D_A$  is a fractional representation of the digital input word  $(0 \le D \le 255/256)$ .

Figure 10. AGND Bias Circuit

For a given  $V_{IN}$ , increasing AGND above system GND will reduce the effective  $V_{DD}-V_{REF}$  which must be at least 4 V to ensure specified operation. Note that because the AGND pin is common to all four DACs, this method biases up the output voltages of all the DACs in the AD7226. Note that  $V_{DD}$  and  $V_{SS}$ of the AD7226 should be referenced to DGND.

#### **3-PHASE SINE WAVE**

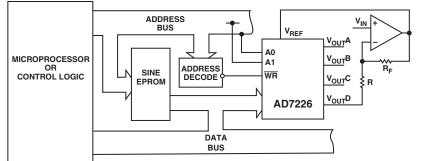

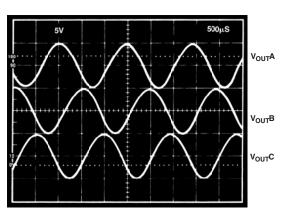

The circuit of Figure 11 shows an application of the AD7226 in the generation of 3-phase sine waves which can be used to control small 3-phase motors. The proper codes for synthesizing a full sine wave are stored in EPROM, with the required phaseshift of 120° between the three D/A converter outputs being generated in software.

Data is loaded into the three D/A converters from the sine EPROM via the microprocessor or control logic. Three loops are

generated in software with each D/A converter being loaded from a separate loop. The loops run through the look-up table producing successive triads of sinusoidal values with 120° separation which are loaded to the D/A converters producing three sine wave voltages 120° apart. A complete sine wave cycle is generated by stepping through the full look-up table. If a 256-element sine wave table is used then the resolution of the circuit will be  $1.4^{\circ}$  (360°/256). Figure 13 shows typical resulting waveforms. The sine waves can be smoothed by filtering the D/A converter outputs.

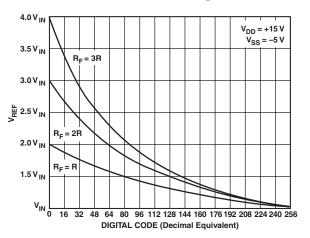

The fourth D/A converter of the AD7226, DAC D, may be used in a feedback configuration to provide a programmable reference voltage for itself and the other three converters. This configuration is shown in Figure 11. The relationship of  $V_{REF}$  to  $V_{IN}$  is dependent upon digital code and upon the ratio of  $R_F$  to R and is given by the formula.

$$V_{REF} = \frac{\left(1+G\right)}{\left(1+G \times D_D\right)} \times V_{IN} \tag{6}$$

where  $G = R_F / R$

and  $D_D$  is a fractional representation of the digital word in latch D.

Alternatively, for a given  $V_{IN}$  and resistance ratio, the required value of  $D_D$  for a given value of  $V_{REF}$  can be determined from the expression

$$D_D = \left(1 + R / R_F\right) \times \frac{V_{IN}}{V_{REF}} - \frac{R}{R_F}$$

(7)

Figure 12 shows typical plots of  $V_{REF}$  versus digital code for three different values of  $R_F$ . With  $V_{IN} = 2.5$  V and  $R_F = 3$  R the peak-to-peak sine wave voltage from the converter outputs will vary between 2.5 V and 10 V over the digital input code range of 0 to 255.

Figure 11. 3-Phase Sine Wave Generation Circuit

Figure 12. Variation of V<sub>REF</sub> with Feedback Configuration

Figure 13. 3-Phase Sine Wave Output

#### STAIRCASE WINDOW COMPARATOR

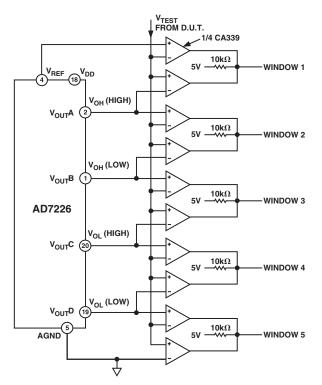

In many test systems, it is important to be able to determine whether some parameter lies within defined limits. The staircase window comparator of Figure 14a is a circuit that can be used, for example, to measure the  $V_{OH}$  and  $V_{OL}$  thresholds of a TTL device under test. Upper and lower limits on both  $V_{OH}$  and  $V_{OL}$  can be programmably set using the AD7226. Each adjacent pair of comparators forms a window of programmable size. If  $V_{TEST}$  lies within a window, then the output for that window will be high. With a reference of 2.56 V applied to the  $V_{REF}$  input, the minimum window size is 10 mV.

Figure 14a. Logic Level Measurement

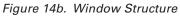

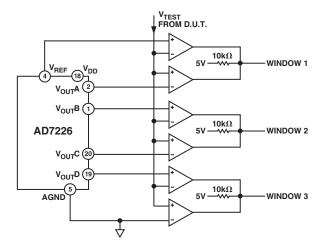

The circuit can easily be adapted to allow for overlapping of windows as shown in Figure 15a. If the three outputs from this circuit are decoded then five different nonoverlapping programmable windows can again be defined.

Figure 15a. Overlapping Windows

Figure 15b. Window Structure

Figure 16. Varying Reference Signal

#### VARYING REFERENCE SIGNAL

In some applications, it may be desirable to have a varying signal applied to the reference input of the AD7226. The AD7226 has multiplying capability within upper and lower limits of reference voltage when operated with dual supplies. The upper and lower limits are those required by the AD7226 to achieve its linearity specification. Figure 16 shows a sine wave signal applied to the reference input of the AD7226. For input signal frequencies up to 50 kHz, the output distortion typically remains less than 0.1%. Typical 3 dB bandwidth figure is 700 kHz.

#### **OFFSET ADJUST**

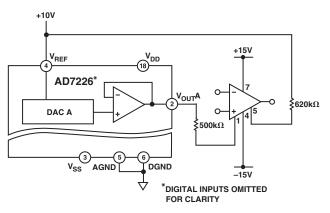

Figure 17 shows how the AD7226 can be used to provide programmable input offset voltage adjustment for the AD544 op amp. Each output of the AD7226 can be used to trim the input offset voltage on one AD544. The 620 k $\Omega$  resistor tied to 10 V provides a fixed bias current to one offset node. For symmetrical adjustment, this bias current should equal the current in the other offset node with the half-full scale code (i.e., 10000000) on the DAC. Changing the code on the DAC varies the bias current and hence provides offset adjust for the AD544. For example, the input offset voltage on the AD544J, which has a maximum of ±2 mV, can be programmably trimmed to ±10  $\mu$ V.

Figure 17. Offset Adjust for AD544

Figure 18. AD7226 to 8085A Interface

Figure 19. AD7226 to 6809 Interface

Figure 20. AD7226 to 6502 Interface

Figure 21. AD7226 to Z-80 Interface

170706-4

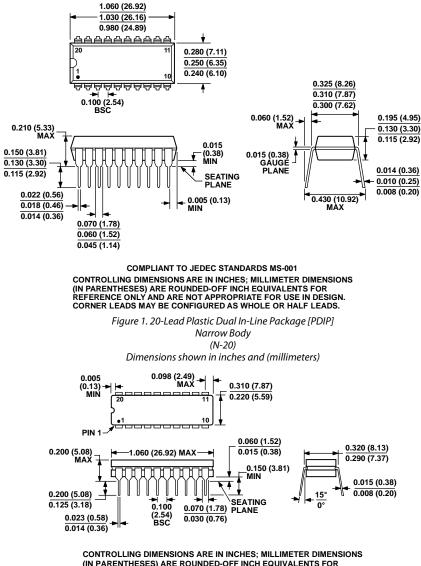

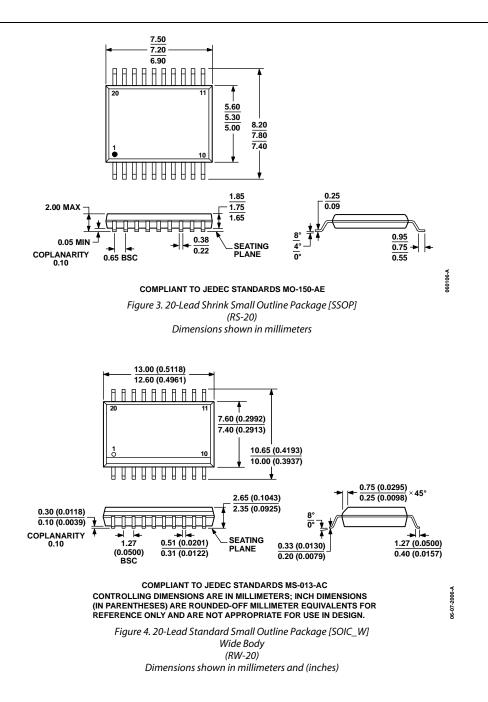

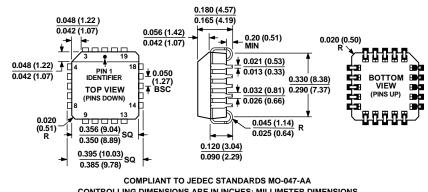

### **OUTLINE DIMENSIONS**

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 2. 20-Lead Ceramic Dual In-Line Package [CERDIP] (Q-20) Dimensions shown in inches and (millimeters)

COMPLIANT TO JEDEC STANDARDS MO-047-AA CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 5. 20-Lead Plastic Leaded Chip Carrier [PLCC] (P-20A) Dimensions shown in inches and (millimeters)

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Total Unadjusted Error <sup>2</sup> | Package Description | Package Option <sup>3</sup> |

|--------------------|-------------------|-------------------------------------|---------------------|-----------------------------|

| AD7226BQ           | -40°C to +85°C    | ±1 LSB                              | 20 Lead CERDIP      | Q-20                        |

| AD7226BRSZ         | -40°C to +85°C    | ±1 LSB                              | 20 Lead SSOP        | RS-20                       |

| AD7226KN           | -40°C to +85°C    | ±1 LSB                              | 20 Lead PDIP        | N-20                        |

| AD7226KNZ          | -40°C to +85°C    | ±1 LSB                              | 20 Lead PDIP        | N-20                        |

| AD7226KP           | -40°C to +85°C    | ±1 LSB                              | 20 Lead PLCC        | P-20A                       |

| AD7226KP-REEL      | -40°C to +85°C    | ±1 LSB                              | 20 Lead PLCC        | P-20A                       |

| AD7226KPZ          | -40°C to +85°C    | ±1 LSB                              | 20 Lead PLCC        | P-20A                       |

| AD7226KPZ-REEL     | -40°C to +85°C    | ±1 LSB                              | 20 Lead PLCC        | P-20A                       |

| AD7226KR           | -40°C to +85°C    | ±1 LSB                              | 20 Lead SOIC - Wide | RW-20                       |

| AD7226KR-REEL      | -40°C to +85°C    | ±1 LSB                              | 20 Lead SOIC - Wide | RW-20                       |

| AD7226KRZ          | -40°C to +85°C    | ±1 LSB                              | 20 Lead SOIC - Wide | RW-20                       |

| AD7226KRZ-REEL     | -40°C to +85°C    | ±1 LSB                              | 20 Lead SOIC - Wide | RW-20                       |

| AD7226BCHIPS       | -40°C to +85°C    | ±1 LSB                              | Chips or Die        |                             |

$^{1}$  Z = ROHS Compliant Part.

<sup>2</sup> Dual supply operation.

<sup>3</sup> N = plastic DIP; P = plastic leaded chip carrier; Q = CERDIP; RW = SPIC; RS = SSOP.

#### **REVISION HISTORY**

#### 1/11-Rev. C to Rev. D

#### 3/03-Rev. B to Rev. C

Title Revision ......1

#### 3/03—Rev. A to Rev. B

| Edits to Features1       |

|--------------------------|

| Edits to Specifications2 |

| Edits to Ordering Guide                  | 3  |

|------------------------------------------|----|

| Edits to Absolute Maximum Ratings        | 3  |

| Edits to Pin Configurations              | 4  |

| Edits to Specifications Ranges           | 8  |

| Outline Dimensions Updated               | 13 |

| RS-20 Package Added                      | 13 |

| Updated RS-20 Package Outline Dimensions |    |

## NOTES

©2003-2011 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00987-0-1/11(D)

www.analog.com