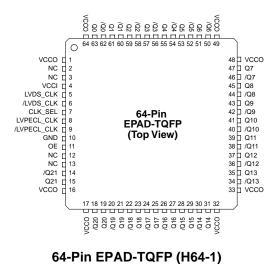

## PACKAGE/ORDERING INFORMATION

# Ordering Information<sup>(1)</sup>

| Part Number                   | Package<br>Type | Operating<br>Range | Package<br>Marking                            | Lead<br>Finish      |

|-------------------------------|-----------------|--------------------|-----------------------------------------------|---------------------|

| SY89825UHI                    | H64-1           | Industrial         | SY89825UHI                                    | Sn-Pb               |

| SY89825UHITR <sup>(2)</sup>   | H64-1           | Industrial         | SY89825UHI                                    | SN-PB               |

| SY89825UHY <sup>(3)</sup>     | H64-1           | Industrial         | SY89825UHY with<br>Pb-Free bar-line indicator | Pb-Free<br>Matte-Sn |

| SY89825UHYTR <sup>(2,3)</sup> | H64-1           | Industrial         | SY89825UHY with Pb-Free bar-line indicator    | Pb-Free<br>Matte-Sn |

Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25^{\circ}$ C, DC electricals only.

2. Tape and Reel.

3. Pb-Free package recommended for new designs.

## **PIN NAMES**

| Pin                            | Function                                                                                                          |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|

| LVDS_CLK,<br>/LVDS_CLK         | Differential LVDS Inputs<br>(Internal 100Ω termination included)                                                  |

| LVPECL_CLK,<br>/LVPECL_CLK     | Differential LVPECL Inputs.                                                                                       |

| CLK_SEL                        | Input CLK Select (LVTTL)                                                                                          |

| OE                             | Output Enable (LVTTL)                                                                                             |

| $Q_0 - Q_{21}, /Q_0 - /Q_{21}$ | Differential LVPECL Outputs. Terminate with $50\Omega$ to V <sub>CC</sub> -2V                                     |

| GND                            | Ground                                                                                                            |

| V <sub>CCI</sub>               | Power Supply. Connect to $V_{CC}$ on PCB. $V_{CCI}$ and $V_{CCO}$ are not internally connected                    |

| V <sub>cco</sub>               | Power Supply for Output Buffer. Connect to $V_{CCI}$ on PCB. $V_{CCI}$ and $V_{CCO}$ are not internally connected |

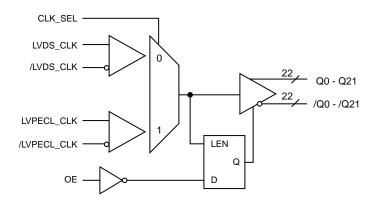

## LOGIC SYMBOL

# TRUTH TABLE

| OE <sup>(1)</sup> | CLK_SEL | $Q_0 - Q_{21}$ | /Q <sub>0</sub> -/Q <sub>21</sub> |

|-------------------|---------|----------------|-----------------------------------|

| 0                 | 0       | LOW            | HIGH                              |

| 0                 | 1       | LOW            | HIGH                              |

| 1                 | 0       | LVDS_CLK       | /LVDS_CLK                         |

| 1                 | 1       | LVPECL_CLK     | /LVPECL_CLK                       |

# SIGNAL GROUPS

| Signal                         | I/O    | Level        |

|--------------------------------|--------|--------------|

| LVDS_CLK, /LVDS_CLK            | Input  | LVDS         |

| $Q_0 - Q_{21}, /Q_0 - /Q_{21}$ | Output | LVPECL       |

| LVPECL_CLK, /LVPECL_CLK        | Input  | LVPECL       |

| CLK_SEL, OE                    | Input  | LVCMOS/LVTTL |

#### NOTE:

1. The OE (output enable) signal is synchronized with the low level of the LVDS\_CLK and LVPECL\_CLK signal.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol                             | Rating                                                                          |                                                                                                              | Value          | Unit                 |  |  |

|------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|----------------------|--|--|

| V <sub>CCI</sub> /V <sub>CCO</sub> | V <sub>CC</sub> Pin Potential to Ground Pin                                     | V <sub>CC</sub> Pin Potential to Ground Pin                                                                  |                |                      |  |  |

| V <sub>IN</sub>                    | Input Voltage                                                                   | –0.5 to V <sub>CCI</sub>                                                                                     | V              |                      |  |  |

| I <sub>OUT</sub>                   | DC Output Current                                                               | -50                                                                                                          | mA             |                      |  |  |

| Tstore                             | Storage Temperature                                                             | -65 to +150                                                                                                  | °C             |                      |  |  |

| $\theta_{JA}$                      | Package Thermal Resistance (Junction<br><u>With</u> exposed pad soldered to GND | n-to-Ambient)<br>– Still-Air (multi-layer PCB)<br>– 200lfpm (multi-layer PCB)<br>– 500lfpm (multi-layer PCB) | 23<br>18<br>15 | °C/W<br>°C/W<br>°C/W |  |  |

|                                    | Exposed pad <i>not</i> soldered to GND                                          | – Still-Air (multi-layer PCB)<br>– 200lfpm (multi-layer PCB)<br>– 500lfpm (multi-layer PCB)                  | 44<br>36<br>30 | °C/W<br>°C/W<br>°C/W |  |  |

| $\theta_{\text{JC}}$               | Package Thermal Resistance<br>(Junction-to-Case)                                |                                                                                                              | 4.3            | °C/W                 |  |  |

NOTE:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data book. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

### **Power Supply**

|                                       |                                     | $T_A = -40^{\circ}C$ |      |      | T <sub>A</sub> = +25°C |      |      | Т    |      |      |      |

|---------------------------------------|-------------------------------------|----------------------|------|------|------------------------|------|------|------|------|------|------|

| Symbol                                | Parameter                           | Min.                 | Тур. | Max. | Min.                   | Тур. | Max. | Min. | Тур. | Max. | Unit |

| V <sub>CCI,</sub><br>V <sub>CCO</sub> | Power Supply <sup>(1)</sup>         | 2.37                 | _    | 3.6  | 2.37                   | _    | 3.8  | 2.37 |      | 3.6  | V    |

| I <sub>CC</sub>                       | Total Supply Current <sup>(2)</sup> | —                    | 100  | 150  | _                      | 100  | 150  |      | 100  | 150  | mA   |

Notes:

1. V<sub>CCI</sub> and V<sub>CCO</sub> must be connected together on the PCB such that they remain at the same potential. V<sub>CCI</sub> and V<sub>CCO</sub> are not internally connected on the die.

2. No load. Outputs floating.

## **LVDS Input** ( $V_{CC} = 2.37V$ to 3.6V, GND = 0V)

|                 |                                                               | $T_A = -40^{\circ}C$ |      |      | Т     | <sub>A</sub> = +25° | C    | T     |      |      |      |

|-----------------|---------------------------------------------------------------|----------------------|------|------|-------|---------------------|------|-------|------|------|------|

| Symbol          | Parameter                                                     | Min.                 | Тур. | Max. | Min.  | Тур.                | Max. | Min.  | Тур. | Max. | Unit |

| V <sub>IN</sub> | Input Voltage Range                                           | 0                    |      | 2.4  | 0     |                     | 2.4  | 0     |      | 2.4  | V    |

| V <sub>ID</sub> | Differential Input Swing                                      | 100                  |      | _    | 100   | _                   |      | 100   |      | _    | mV   |

| IIL             | Input Low Current <sup>(1)</sup>                              | -1.25                |      |      | -1.25 |                     |      | -1.25 |      |      | mA   |

| R <sub>IN</sub> | LVDS Differential Input Resistance<br>(LVDS_CLK to /LVDS_CLK) | 80                   | 100  | 120  | 80    | 100                 | 120  | 80    | 100  | 120  | Ω    |

Note:

1. For I<sub>IL</sub>, both LVDS inputs are grounded.

## **LVPECL Input/Output** ( $V_{CC} = 2.37V$ to 3.6V, GND = 0V)

|                  |                                                  | T <sub>A</sub> = ·       | –40°C                    | T <sub>A</sub> =         | +25°C                    | T <sub>A</sub> =         | +85°C                    |      |

|------------------|--------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|

| Symbol           | Parameter                                        | Min.                     | Max.                     | Min.                     | Max.                     | Min.                     | Max.                     | Unit |

| V <sub>IH</sub>  | Input HIGH Voltage<br>(Single ended)             | V <sub>CC</sub> – 1.165  | V <sub>CC</sub> – 0.88   | V <sub>CC</sub> – 1.165  | V <sub>CC</sub> – 0.88   | V <sub>CC</sub> – 1.165  | V <sub>CC</sub> – 0.88   | V    |

| VIL              | Input LOW Voltage                                | V <sub>CC</sub> – 1.945  | V <sub>CC</sub> – 1.625  | V <sub>CC</sub> – 1.945  | V <sub>CC</sub> – 1.625  | V <sub>CC</sub> – 1.945  | V <sub>CC</sub> – 1.625  | V    |

| V <sub>PP</sub>  | Minimum Input Swing <sup>(1)</sup><br>LVPECL_CLK | 600                      | —                        | 600                      | —                        | 600                      | -                        | mV   |

| V <sub>CMR</sub> | Common Mode Range <sup>(2)</sup><br>LVPECL_CLK   | -1.5                     | -0.4                     | -1.5                     | -0.4                     | -1.5                     | -0.4                     | V    |

| V <sub>OH</sub>  | Output HIGH Voltage <sup>(3)</sup>               | V <sub>CCO</sub> – 1.085 | V <sub>CCO</sub> – 0.880 | V <sub>CCO</sub> – 1.025 | V <sub>CCO</sub> – 0.880 | V <sub>CCO</sub> – 1.025 | V <sub>CCO</sub> – 0.880 | V    |

| V <sub>OL</sub>  | Output LOW Voltage <sup>(3)</sup>                | V <sub>CCO</sub> – 1.830 | V <sub>CCO</sub> – 1.555 | V <sub>CCO</sub> – 1.810 | V <sub>CCO</sub> – 1.620 | V <sub>CCO</sub> – 1.810 | V <sub>CCO</sub> – 1.620 | V    |

| I <sub>IH</sub>  | Input HIGH Current                               | _                        | 150                      | _                        | 150                      |                          | 150                      | μA   |

| I <sub>IL</sub>  | Input LOW Current                                | 0.5                      |                          | 0.5                      | _                        | 0.5                      | _                        | μA   |

Notes:

1. The V<sub>PP</sub> (min.) is defined as the minimum input differential voltage which will cause no increase in the propagation delay.

2.  $V_{CMR}$  is defined as the range within which the  $V_{IH}$  level may vary, with the device still meeting the propagation delay specification. The numbers in the table are referenced to  $V_{CCI}$ . The  $V_{IL}$  level must be such that the peak-to-peak voltage is less than 1.0V and greater than or equal to  $V_{PP}$  (min.). The lower end of the CMR range varies 1:1 with  $V_{CCI}$ . The  $V_{CMR}$  (min) will be fixed at 3.3V –  $|V_{CMR}$  (min)|.

3. Outputs loaded with 50  $\Omega$  to V \_{cc} -2V.

## LVCMOS/LVTTL Control Inputs (OE, CLK\_SEL) (V<sub>CC</sub> = 2.37V to 3.6V, GND = 0V)

|                 |                    | T <sub>A</sub> = −40°C |      |      | T <sub>A</sub> = +25°C |      |      | Т    |      |      |      |

|-----------------|--------------------|------------------------|------|------|------------------------|------|------|------|------|------|------|

| Symbol          | Parameter          | Min.                   | Тур. | Max. | Min.                   | Тур. | Max. | Min. | Тур. | Max. | Unit |

| V <sub>IH</sub> | Input HIGH Voltage | 2.0                    | —    | -    | 2.0                    | _    | —    | 2.0  | _    |      | V    |

| V <sub>IL</sub> | Input LOW Voltage  | _                      | _    | 0.8  |                        | -    | 0.8  | _    |      | 0.8  | V    |

| I <sub>IH</sub> | Input HIGH Current | +20                    | —    | -250 | +20                    | —    | -250 | +20  | _    | -250 | μA   |

| I <sub>IL</sub> | Input LOW Current  | _                      | _    | -600 | _                      | _    | -600 | _    |      | -600 | μA   |

# AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

### $V_{CC} = 2.37V$ to 3.6V, GND = 0V

|                                      |                                                                         | Т              | $T_A = -40^{\circ}$ |            | Т              | <sub>A</sub> = +25° | C          | T <sub>A</sub> = +85°C |      |            |                     |

|--------------------------------------|-------------------------------------------------------------------------|----------------|---------------------|------------|----------------|---------------------|------------|------------------------|------|------------|---------------------|

| Symbol                               | Parameter                                                               | Min.           | Тур.                | Max.       | Min.           | Тур.                | Max.       | Min.                   | Тур. | Max.       | Unit                |

| f <sub>MAX</sub>                     | Max Toggle Frequency <sup>(2)</sup>                                     | 2              | —                   | —          | 2              | _                   | —          | 2                      | _    | _          | GHz                 |

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay<br>(Differential) <sup>(3)</sup> LVPECL IN<br>LVDS IN | 0.600<br>0.800 | _                   | 1.2<br>1.4 | 0.600<br>0.800 | 0.900<br>1.1        | 1.2<br>1.4 | 0.600<br>0.800         |      | 1.2<br>1.4 | ns                  |

| t <sub>SKEW</sub>                    | Within-Device Skew <sup>(4)</sup>                                       | _              | _                   | 35         |                | 20                  | 35         |                        |      | 35         | ps                  |

|                                      | Part-to-Part Skew <sup>(5)</sup>                                        | _              | 100                 | 200        |                | 100                 | 200        |                        | 100  | 200        | ps                  |

| t <sub>S(OE)</sub>                   | OE Set-Up Time <sup>(6)</sup>                                           | 1.0            | _                   | _          | 1.0            | —                   | _          | 1.0                    | —    | _          | ns                  |

| t <sub>H(OE)</sub>                   | OE Hold Time <sup>(6)</sup>                                             | 0.5            | —                   | _          | 0.5            | —                   | _          | 0.5                    | _    | _          | ns                  |

| t <sub>JITTER</sub>                  | Random Jitter <sup>(7)</sup>                                            | _              | —                   | 1          | —              | —                   | 1          | _                      | —    | 1          | ps <sub>(RMS)</sub> |

|                                      | Cycle-to-Cylce Jitter <sup>(8)</sup>                                    | _              | —                   | 1          | _              | —                   | 1          | _                      | _    |            | ps <sub>(RMS)</sub> |

|                                      | Total Jitter <sup>(9)</sup>                                             | _              | —                   | 10         | —              | —                   | 10         | _                      | —    | 10         | ps <sub>(PP)</sub>  |

| t <sub>r</sub><br>t <sub>f</sub>     | Output Rise/Fall Time<br>(20% – 80%)                                    | 300            | —                   | 600        | 300            | 450                 | 600        | 300                    | —    | 600        | ps                  |

| t <sub>(switchover)</sub>            | Input Switchover<br>CLK_SEL-to-valid output                             | _              |                     | 1.2        | —              | _                   | 1.2        | _                      | _    | 1.2        | ns                  |

#### Notes:

1. Outputs loaded with 50 to  $V_{CC}$  – 2V. Airflow  $\geq$  300lfpm.

- 2.  $f_{MAX}$  is defined as the maximum toggle frequency measured. Measured with a 750mV input signal, all loading with 50 $\Omega$  to V<sub>CC</sub> -2V.

- 3. Differential propagation delay is defined as the delay from the crossing point of the differential input signals to the crossing point of the differential output signals.

- 4. The within-device skew is defined as the worst case difference between any two similar delay paths within a single device operating at the same voltage and temperature.

- 5. The part-to-part skew is defined as the absolute worst case difference between any two delay paths on any two devices operating at the same voltage and temperature. Part-to-part skew is the total skew difference; pin-to-pin skew + part-to-part skew.

- 6. Set-up and hold time applies to synchronous applications that intend to enable/disable before the next clock cycle. For asynchronous applications, set-up and hold time does not apply. OE set-up time is defined with respect to the rising edge of the clock. OE HIGH to LOW transition ensures outputs remain disabled during the next clock cycle. OE LOW to HIGH transition enables normal operation of the next input clock.

- 7. Random jitter is measured using K28.7 pattern, measured at  $\leq$  f<sub>MAX</sub>.

- 8. Cycle-to-cycle definition: the variation of periods between adjacent cycles, Tn–Tn-1 where T is the time between rising edges of the output signal.

- Total jitter definition: with an ideal clock input of frequency ≤ f<sub>MAX</sub>, no more than one output edge in 10<sup>20</sup> output edges will d eviate by more than the specified peak-to-peak jitter value.

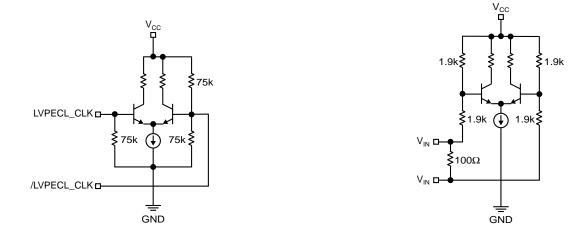

# LVDS/LVPECL INPUTS

LVPECL Input Stage

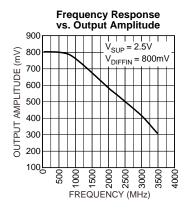

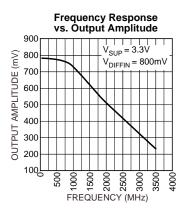

# **TYPICAL CHARACTERISTICS**

Frequency Response vs. Output Amplitude @2.5V

Frequency Response vs. Output Amplitude @3.3V

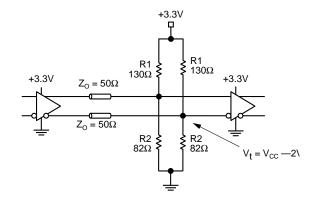

## LVPECL TERMINATION RECOMMENDATIONS

#### **Output Considerations**

Be sure to properly terminate all outputs as shown below, or equivalent. For AC coupled applications, be sure to include a pull down resistor at the output of each driver. The emmiter follower outputs requires a DC current path to GND. Unused outputs can be left floating with minimal impact on skew and jitter.

Figure 1. Parallel Termination-Thevenin Equivalent

#### Notes:

- 1. For +2.5V systems: R1 =  $250\Omega$

- $R_1 = 250\Omega_2$  $R_2 = 62.5\Omega_2$

R2 = 02.312

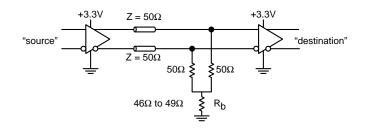

Figure 2. Three-Resistor "Y-Termination"

#### Notes:

- 1. Power-saving alternative to Thevenin termination.

- 2. Place termination resistors as close to destination inputs as possible.

- 3. R<sub>b</sub> resistor sets the DC bias voltage equal to V<sub>t</sub>. For +3.3V systems R<sub>b</sub> = 46 $\Omega$  to 49 $\Omega$ .

- 4. Precision, low-cost 3-Resistor networks are available from resistor manufacturers such as Thin Film Technology (www.thinfilm.com).

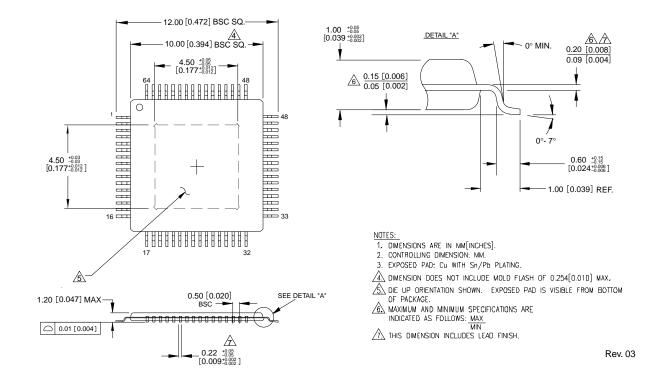

## 64-PIN EPAD-TQFP (DIE UP) (H64-1)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2005 Micrel, Incorporated.