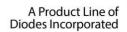

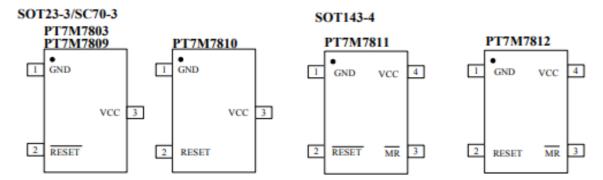

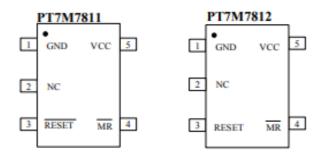

# **Pin Configuration**

#### SOT23-5

**Pin Description**

| Pin                                                                                                                                                                                                                                                                                | Type | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MR                                                                                                                                                                                                                                                                                 | I    | <b>Manual-Reset:</b> (CMOS). Active low. Pull low to force a reset. Reset remains asserted for the duration of the Reset Timeout Period after MR transitions from low to high. Leave unconnected or connected to VCC if not used.                                                                                                                                                           |  |  |  |

| VCC Power Supply Voltage. Reset is asserted when $V_{CC}$ drops below the Reset Threshold Voltage ( $V_{RST}$ ). For remains asserted until $V_{CC}$ rises above $V_{RST}$ and keep asserted for the duration of the Reset Time ( $t_{RS}$ ) once $V_{CC}$ rises above $V_{RST}$ . |      |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| GND                                                                                                                                                                                                                                                                                | -    | Ground Reference for all signals.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| WDI                                                                                                                                                                                                                                                                                | I    | <b>Watchdog Input (CMOS).</b> If WDI remains high or low for the duration of the watchdog timeout period (t <sub>WD</sub> ), the internal watchdog timer trigger a reset output. Floating WDI or connecting WDI to a high-impedance three-state buffer disables the watchdog feature. The internal watchdog timer clears whenever reset is asserted or WDI occurs a rising or falling edge. |  |  |  |

| RESET                                                                                                                                                                                                                                                                              | О    | Active-Low Reset Output (Push-Pull or Open-Drain). It goes low when Vcc is below the reset threshold. It remains low for about 200ms after one of the following occurs: Vcc rises above the reset threshold (VRST), the watchdog triggers a reset, or MR goes from low to high.                                                                                                             |  |  |  |

| RESET                                                                                                                                                                                                                                                                              | О    | The inverse of RESET, active high. Whenever RESET is high, RESET is low.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| NC                                                                                                                                                                                                                                                                                 | -    | No connection.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

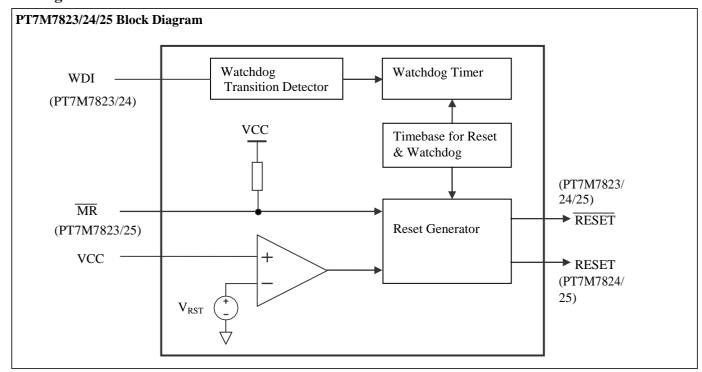

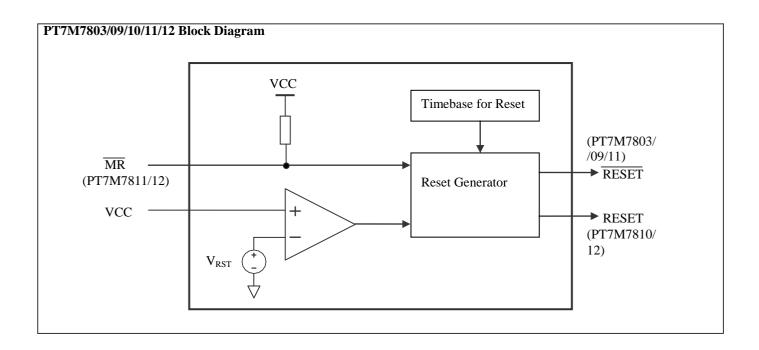

# **Block Diagram**

#### **Maximum Ratings**

| Storage Temperature65°C to +150°C                                             |

|-------------------------------------------------------------------------------|

| Ambient Temperature with Power Applied40°C to +85°C                           |

| Supply Voltage to Ground Potential (Vcc to GND)0.3V to +7.0V                  |

| DC Input Voltage (All inputs except Vcc and GND)0.3V to V <sub>CC</sub> +0.3V |

| Open-drain RESET0.3V to +7.0V                                                 |

| DC Output Current (All                                                        |

| outputs)20mA                                                                  |

| Power Dissipation                                                             |

|                                                                               |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Recommended Operation Conditions**

| Sym               | Description                             | Test Conditions | Min.        | Тур. | Max.        | Unit          |

|-------------------|-----------------------------------------|-----------------|-------------|------|-------------|---------------|

|                   | Supply Voltage for 78xxL/M/J            | -               | 4.5         | 5.0  | 5.5         | V             |

| $V_{CC}$          | Supply Voltage for 78xxT/S              | -               | 3.0         | 3.3  | 5.5         | V             |

|                   | Supply Voltage for 78xxR/Z/Y/K/G        | -               | 2.7         | 3.0  | 5.5         | V             |

| $V_{\mathrm{IH}}$ | Input High Voltage (WDI, MR)            | -               | $0.7V_{CC}$ | -    | $V_{CC}$    | V             |

| V IH              | Input High Voltage for Open-drain RESET |                 | 0           |      | 5.5         | V             |

| V <sub>IL</sub>   | Input Low Voltage                       | -               | -           | -    | $0.3V_{CC}$ | V             |

| $T_A$             | Operating Temperature                   | -               | -40         | -    | 85          | ${\mathbb C}$ |

# **DC Electrical Characteristics**

$(V_{CC} = V_{RN} + 5\% \text{ to } 5.5V, T_A = -40 \sim 85 ^{\circ}\text{C}, \text{ unless otherwise noted.})$ (Note 1)

| Symbol              | Description                                      | Test Conditions                                         |                           | Min.                   | Тур.     | Max.                   | Unit |

|---------------------|--------------------------------------------------|---------------------------------------------------------|---------------------------|------------------------|----------|------------------------|------|

| $V_{CC}$            | Operating Voltage Range                          | -                                                       |                           | 1.0                    | -        | 5.5                    | V    |

| I <sub>CC</sub>     | Supply Current                                   | Vcc = 5V, No                                            | 7803/09/10/11/12          | -                      | 10       | 30                     | μA   |

|                     | 11.7                                             | load                                                    | 7823/24/25                | -                      | 13       | 36                     |      |

| $V_{IH}$            | Input High Voltage                               | Pin: MR, WDI                                            |                           | $0.7V_{CC}$            | -        | $V_{CC}$               | V    |

| $V_{IL}$            | Input Low Voltage                                | Pin: MR, WDI                                            |                           | -                      | -        | $0.3V_{CC}$            | V    |

|                     | Threshold Voltage(Falling-                       | T <sub>A</sub> = 25℃                                    |                           | V <sub>RN</sub> - 1.5% | $V_{RN}$ | $V_{RN} + 1.5\%$       |      |

| $V_{RST}$           | edge)(Note 2)                                    | T <sub>A</sub> = -40 ~ 85°C                             | 78xx                      | V <sub>RN</sub> - 2.5% | $V_{RN}$ | V <sub>RN</sub> + 2.5% | V    |

|                     |                                                  | V. a sanisa                                             | 7823/24/25L/M             | -                      | 12       | -                      |      |

| $V_{RTH}$           | Reset Threshold Hysteresis (Note 2)              | Vcc varies<br>between                                   | 7823/24/25<br>T/S/R/K/Z/Y | -                      | 4        | -                      | mV   |

|                     |                                                  | $V_{\rm RN} \pm 5\%$                                    | Others                    | -                      | 50       | -                      |      |

|                     |                                                  | Vcc ≥ 4.5V Isource=800μA                                |                           | Vcc-1.5                | -        | -                      | V    |

|                     | Output High<br>Voltage(Except<br>7823/24/25)     | Vcc ≥ 2.7V Isour                                        | 0.8×Vcc                   | -                      | -        |                        |      |

|                     |                                                  | Vcc ≥ 1.8V Isour                                        | 0.8×Vcc                   | -                      | -        |                        |      |

| $V_{OH}$            | , , , , , , , , , , , , , , , , , , , ,          | Vcc ≥ 1.0V Isource=4μA                                  |                           | 0.8×Vcc                | -        | -                      |      |

|                     | Output High<br>Voltage(7823/24/25)               | 7823/24/25L/M, Vcc=V <sub>RST</sub><br>Isource=120μA    |                           | Vcc-1.5                | -        | -                      | V    |

|                     |                                                  | 7823/24/25T/S/R/K, Vcc=V <sub>RST</sub><br>Isource=30µA |                           | 0.8×Vcc                | -        | -                      | V    |

|                     | Output Low Voltage                               | Vcc ≥ 4.5V Isink                                        | -                         | -                      | 0.4      |                        |      |

| $V_{OL}$            |                                                  | Vcc ≥ 2.7V Isink                                        | -                         | -                      | 0.3      | V                      |      |

|                     |                                                  | Vcc ≥ 1.0V Isink                                        | -                         | -                      | 0.3      |                        |      |

| $I_{LKG}$           | Open-Drain Output<br>Leakage Current             | $V_{\rm CC} > V_{\rm TH(MAX)}$ f                        | For 7803                  | -                      | -        | 1                      | μΑ   |

| т                   | Average WDI Input                                | WDI connected to V <sub>CC</sub> : 5.5V                 |                           | -                      | 120      | 160                    |      |

| $I_{WDI}$           | Current (Note 3)                                 | WDI connected t                                         | -20                       | -15                    | -        | μA                     |      |

| $I_{\text{source}}$ | RESET Output Short-<br>Circuit Current (only for | PT7M782xL/M, RESET=0V,<br>Vcc=5.5V                      |                           | -                      | -,       | 800                    | 4    |

|                     | PT7M7823/24/25)                                  | PT7M782xT/S/R/K/Z/Y, RESET=0V, Vcc=3.6V                 |                           | -                      | -        | 400                    | - μΑ |

| -                   | MR pull-up resistor                              | PT7M7811/7812                                           |                           | 10                     | 20       | 40                     | 1.0  |

| r                   | (internal)                                       | PT7M7823/7824                                           | 35                        | 52                     | 75       | kΩ                     |      |

Note: 1. Parameters of room temperature guaranteed by production test and parameters of full-temperature guaranteed by design.

<sup>2.</sup> Valid for both RESET and RESET.  $V_{RST}$  ( $V_{RTH}$ ) is the Reset threshold voltage when  $V_{CC}$  from high to low level, and  $V_{RTH}$ + is the Reset threshold voltage when  $V_{CC}$  from low to high level.  $V_{RN}$  is nominal reset threshold voltage.

3. WDI is internally serviced within the watchdog period if WDI is left unconnected.

# **AC Electrical Characteristics**

| Symbol            | Description             | <b>Test Conditions</b>                                     | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------|------------------------------------------------------------|------|------|------|------|

| t <sub>RS</sub>   | Reset Pulse Width       | MR from low to High.                                       | 140  | 200  | 400  | ms   |

| $t_{ m WD}$       | Watchdog Timeout Period | WDI, $\overline{MR}$ tied to Vcc, Vcc>V <sub>RN</sub> +5%. | 1.12 | 1.6  | 2.25 | S    |

| t <sub>MR</sub>   | MR Pulse Width          | -                                                          | 200  | -    | -    | ns   |

| t <sub>MD</sub>   | MR to RESET Delay       | Vcc=5V                                                     | -    | -    | 250  | ns   |

| $t_{\mathrm{WP}}$ | WDI Pulse Width         | -                                                          | 150  | -    | -    | ns   |

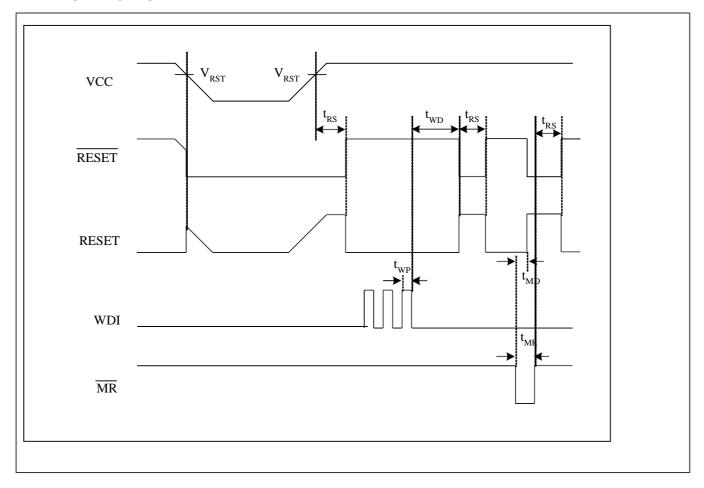

# **Watchdog Timing Diagram**

#### **Functional Description**

#### **Reset Output**

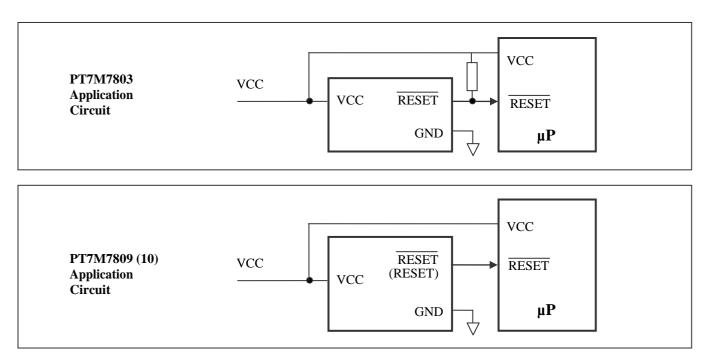

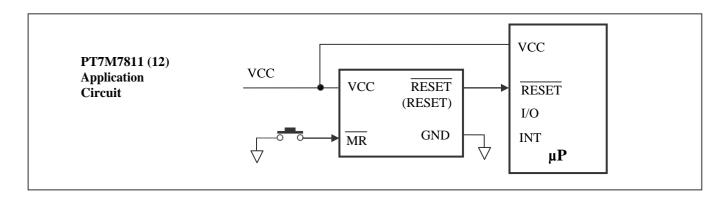

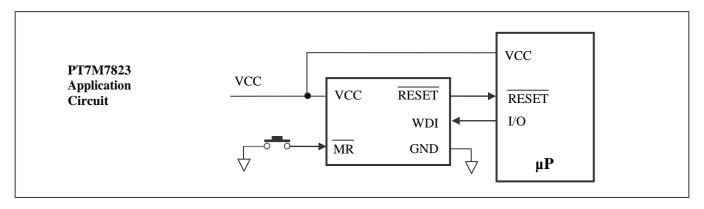

A microprocessor ( $\mu P$ ) reset input starts the  $\mu P$  in a known state. Whenever the  $\mu P$  is in an unknown state, it should be held in reset. The supervisory circuits assert reset during power-up and prevent code execution errors during power-down or brownout conditions.

On power-up, once Vcc reaches about 1.0V, RESET is a guaranteed logic low of 0.4V or less. As Vcc rises, RESET stays low. When Vcc rises above the reset threshold, an internal timer releases RESET after about 200ms. RESET pulses low whenever Vcc drops below the reset threshold, i.e. brownout condition. If brownout occurs in the middle of a previously initiated reset pulse, the pulse continues for at least another 200ms. On power-down, once Vcc falls below the reset threshold, RESET stays low and is guaranteed to be 0.4V or less until Vcc drops below 1.0V. Watchdog Timing Diagram shows the timing relationship.

The active-high RESET output is simply the inverse of the RESET output, and is guaranteed to be valid with Vcc down to 1.0V.

#### **Watchdog Timer**

The PT7M78xx watchdog circuit monitors the  $\mu P$  activity. If the  $\mu P$  does not toggle the watch-dog input (WDI) within 1.6s, reset asserts. As long as reset is asserted or the WDI input is toggled, the watchdog timer will stay clear and will not count. As soon as reset is released, the timer will start counting. WDI input pulses as short as 150ns can be detected.

Disable the watchdog function by leaving WDI unconnected or by three-stating driver connected to WDI. Do not apply voltage level on DCI over Vcc.

#### **Manual Reset**

The manual-reset input (MR) allows reset to be triggered by a push button switch.  $\overline{MR}$  has an internal pullup resistor, so it can be left open when not used. Do not apply voltage level over Vcc.

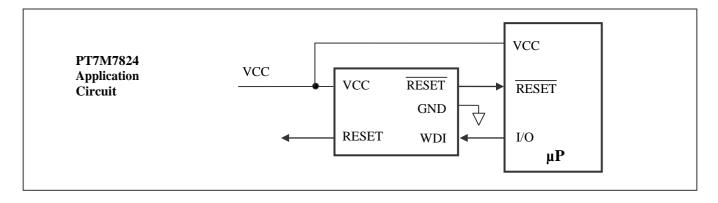

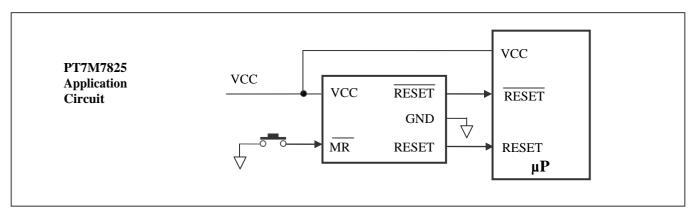

# **Typical Application Circuit**

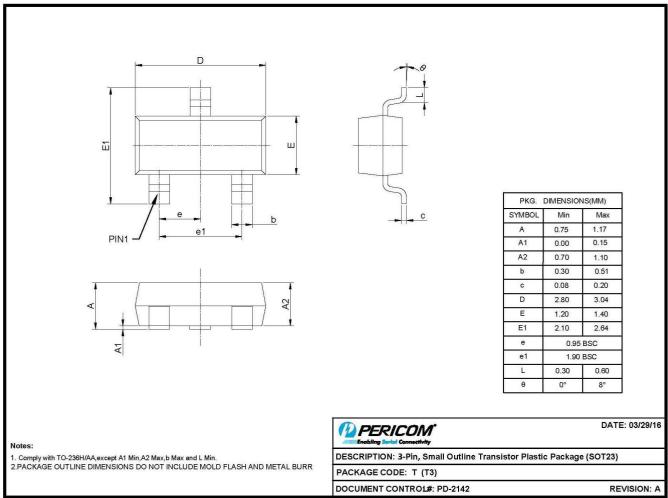

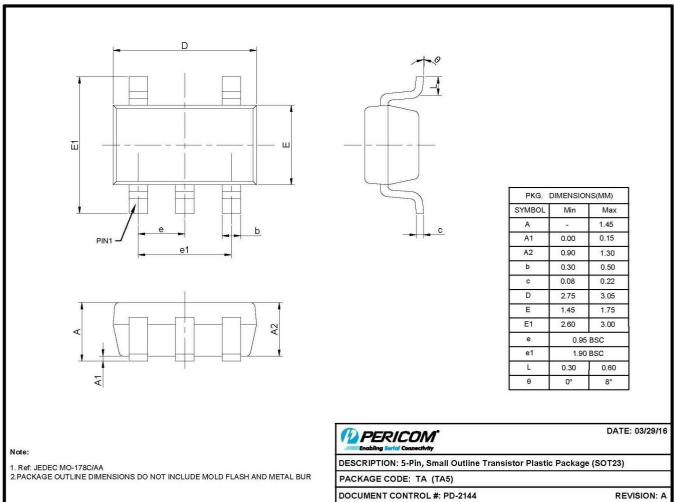

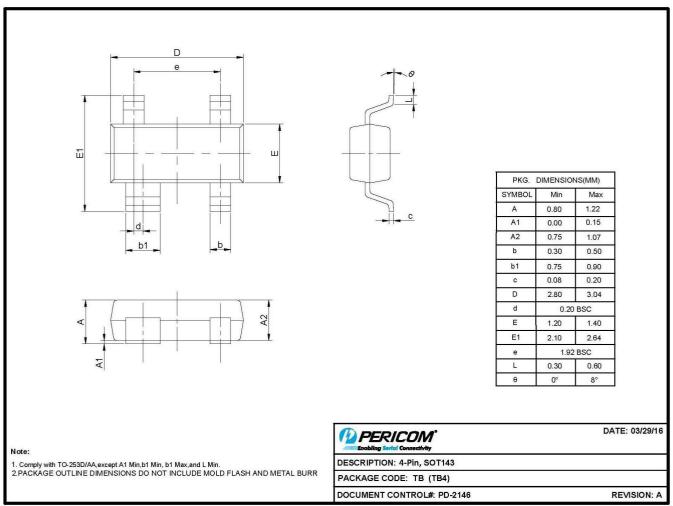

# **Mechanical Information**

T (SOT23)

16-0079

Downloaded from Arrow.com.

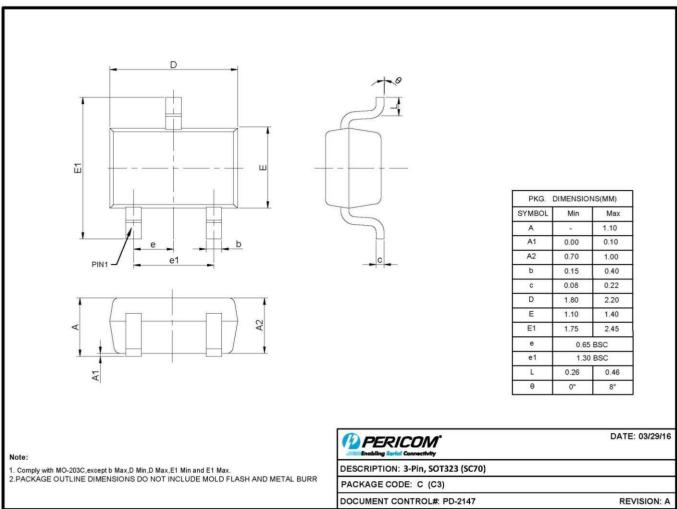

#### C (SC70)

16-0077

#### **TA (SOT23)**

16-0081

#### **TB** (SOT143)

16-0083

For latest package info.

$please\ check:\ http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/packaging/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanical-and-thermal-characteristics/packaging-mechanical-and-thermal-characteristics/packa$

# **Ordering Information**

| Part Number   | Package Code | Package                                                              | Status      |

|---------------|--------------|----------------------------------------------------------------------|-------------|

| PT7M7803XTEX  | Т            | 3-Pin, Small Outline Transistor Plastic (SOT23), Tape & Reel         | NRND        |

| PT7M7809XTEX  | Т            | 3-Pin, Small Outline Transistor Plastic (SOT23), Tape & Reel         | NRND        |

| PT7M7810XTEX  | Т            | 3-Pin, Small Outline Transistor Plastic (SOT23), Tape & Reel         | NRND        |

| PT7M7803XC3EX | C3           | 3-Pin, SOT323 (SC70), Tape & Reel                                    | NRND        |

| PT7M7809XC3EX | C3           | 3-Pin, SOT323 (SC70), Tape & Reel                                    | End of life |

| PT7M7810XC3EX | C3           | 3-Pin, SOT323 (SC70), Tape & Reel                                    | End of life |

| PT7M7811XTAEX | TA           | 5-Pin, Small Outline Transistor Plastic Package (SOT23), Tape & Reel | NRND        |

| PT7M7812XTAEX | TA           | 5-Pin, Small Outline Transistor Plastic Package (SOT23), Tape & Reel | End of life |

| PT7M7823XTAEX | TA           | 5-Pin, Small Outline Transistor Plastic Package (SOT23), Tape & Reel | NRND        |

| PT7M7824XTAEX | TA           | 5-Pin, Small Outline Transistor Plastic Package (SOT23), Tape & Reel | NRND        |

| PT7M7825XTAEX | TA           | 5-Pin, Small Outline Transistor Plastic Package (SOT23), Tape & Reel | NRND        |

| PT7M7811XTBEX | ТВ           | 4-Pin (SOT143), Tape & Reel                                          | NRND        |

| PT7M7812XTBEX | ТВ           | 4-Pin (SOT143), Tape & Reel                                          | End of life |

| *PT7M7809XUWF | UWF          | Wafer form                                                           | End of life |

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- $E = Pb\text{-}free \ and \ Green$

- Adding X Suffix= Tape/Reel

"\*" for UWF package, please check the storage with related sales.

# Suffix: X—Monitored Voltage

| X                   | L    | M    | T    | S    | R    | Z    | Y    | J    | K    | G    |

|---------------------|------|------|------|------|------|------|------|------|------|------|

| Reset Threshold (V) | 4.63 | 4.38 | 3.08 | 2.93 | 2.63 | 2.32 | 2.20 | 4.00 | 2.25 | 2.80 |

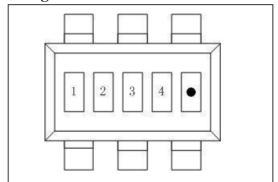

# **Marking Information**

| Code | Description        |

|------|--------------------|

| 1 2  | Part Number        |

| 3    | Year               |

| 4    | Work Week          |

| •    | Only for PT7M7809M |

#### **Part Number Code**

| Code 1 2 | Part No   |

|----------|-----------|----------|-----------|----------|-----------|----------|-----------|

| AA       | PT7M7809L | AO       | PT7M7811L | ВС       | PT7M7803L | BQ       | PT7M7824L |

| AB       | PT7M7809M | AP       | PT7M7811M | BD       | PT7M7803M | BR       | PT7M7824M |

| AC       | PT7M7809T | AQ       | PT7M7811T | BE       | PT7M7803T | BS       | PT7M7824T |

| AD       | PT7M7809S | AR       | PT7M7811S | BF       | PT7M7803S | BT       | PT7M7824S |

| AE       | PT7M7809R | AS       | PT7M7811R | BG       | PT7M7803R | BU       | PT7M7824R |

| AF       | PT7M7809Z | AT       | PT7M7811Z | ВН       | PT7M7803Z | BV       | PT7M7824Z |

| AG       | PT7M7809Y | AU       | PT7M7811Y | BI       | PT7M7803Y | BW       | PT7M7824Y |

| jm       | PT7M7809J | sf       | PT7M7811J | sc       | PT7M7803J | si       | PT7M7824J |

| pЕ       | PT7M7809G |          |           |          |           | mQ       | PT7M7824K |

| AH       | PT7M7810L | AV       | PT7M7812L | BJ       | PT7M7823L | BX       | PT7M7825L |

| AI       | PT7M7810M | AW       | PT7M7812M | BK       | PT7M7823M | BY       | PT7M7825M |

| AJ       | PT7M7810T | AX       | PT7M7812T | BL       | PT7M7823T | BZ       | PT7M7825T |

| AK       | PT7M7810S | AY       | PT7M7812S | BM       | PT7M7823S | CA       | PT7M7825S |

| AL       | PT7M7810R | AZ       | PT7M7812R | BN       | PT7M7823R | СВ       | PT7M7825R |

| AM       | PT7M7810Z | BA       | PT7M7812Z | ВО       | PT7M7823Z | CC       | PT7M7825Z |

| AN       | PT7M7810Y | BB       | PT7M7812Y | BP       | PT7M7823Y | CD       | PT7M7825Y |

| se       | PT7M7810J | sg       | PT7M7812J | sh       | PT7M7823J | sj       | PT7M7825J |

|          |           |          |           | mP       | PT7M7823K |          |           |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2020, Diodes Incorporated

www.diodes.com