## **Pin Descriptions**

| Pin Name                                       | Type   | Pin #                                                             | Descriptions                                                                                                                          |

|------------------------------------------------|--------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| SRC_DIV#                                       | Input  | 1                                                                 | 3.3V LVTTL input for selecting input frequency divide by 2, active LOW.                                                               |

| SRC & SRC#                                     | Input  | 4, 5                                                              | 0.7V Differential SRC input from PI6C410 clock synthesizer                                                                            |

| OE [0:7]                                       | Input  | 6, 7, 14, 15, 35, 36,<br>43, 44                                   | 3.3V LVTTL input for enabling outputs, active HIGH.                                                                                   |

| OE_INV Input 40 PWRDWN# When 0 = sa When 1 = O |        | 40                                                                | 3.3V LVTTL input for inverting the OE, SRC_STOP# and PWRDWN# pins. When 0 = same stage When 1 = OE[0:7], SRC_STOP#, PWRDWN# inverted. |

| OUT[0:7] & OUT[0:7]#                           | Output | 8, 9, 12, 13, 16 17,<br>20, 21, 29, 30, 33, 34,<br>37, 38, 41, 42 | 0.7V Differential outputs                                                                                                             |

| PLL/BYPASS# Input                              |        | 22                                                                | 3.3V LVTTL input for selecting fan-out of PLL operation.                                                                              |

| SCLK                                           | Input  | 23                                                                | SMBus compatible SCLOCK input                                                                                                         |

| SDA                                            | I/O    | 24                                                                | SMBus compatible SDATA                                                                                                                |

| $I_{REF}$                                      | Input  | 46                                                                | External resistor connection to set the differential output current                                                                   |

| SRC_STOP#                                      | Input  | 27                                                                | 3.3V LVTTL input for SRC stop, active LOW                                                                                             |

| PLL_BW#                                        | Input  | 28                                                                | 3.3V LVTTL input for selecting the PLL bandwidth                                                                                      |

| PWRDWN#                                        | Input  | 26                                                                | 3.3V LVTTL input for Power Down operation, active LOW                                                                                 |

| LOCK                                           | Output | 45                                                                | 3.3V LVTTL output, transition high when PLL lock is achieved (Latched output)                                                         |

| $V_{\mathrm{DD}}$                              | Power  | 2, 11, 19, 31, 39                                                 | 3.3V Power Supply for Outputs                                                                                                         |

| $V_{SS}$                                       | Ground | 3, 10, 18, 25, 32                                                 | Ground for Outputs                                                                                                                    |

| V <sub>SS_A</sub>                              | Ground | 47                                                                | Ground for PLL                                                                                                                        |

| V <sub>DD_A</sub>                              | Power  | 48                                                                | 3.3V Power Supply for PLL                                                                                                             |

### **Serial Data Interface (SMBus)**

This part is a slave only SMBus device that supports indexed block read and indexed block write protocol using a single 7-bit address and read/write bit as shown below.

### Address assignment

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | W/R |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0/1 |

## Data Write Protocol<sup>(1)</sup>

| 1 | bit       | 7 bits        | 1 | 1   | 8 bits             | 1   | 8 bits               | 1   | 8 bits                 | 1   | 8 bits                | 1   | 1 bit    |

|---|-----------|---------------|---|-----|--------------------|-----|----------------------|-----|------------------------|-----|-----------------------|-----|----------|

|   | art<br>it | Slave<br>Addr | W | Ack | Register<br>offset | Ack | Byte<br>Count<br>= N | Ack | Data<br>Byte<br>Offset | Ack | Data<br>Byte N<br>- 1 | Ack | Stop bit |

#### Note:

<sup>1.</sup> Register offset for indicating the starting register for indexed block write and indexed block read. Byte Count in write mode cannot be 0.

# Data Read Protocol<sup>(2)</sup>

| 1 bit        | 7 bits        | 1 | 1   | 8 bits             | 1   | 1               | 7 bits        | 1 | 1   | 8 bits               | 1   | 8 bits                 | 1   | 8 bits                | 1          | 1 bit       |  |

|--------------|---------------|---|-----|--------------------|-----|-----------------|---------------|---|-----|----------------------|-----|------------------------|-----|-----------------------|------------|-------------|--|

| Start<br>bit | Slave<br>Addr | W | Ack | Register<br>offset | Ack | Repeat<br>Start | Slave<br>Addr | R | Ack | Byte<br>Count<br>= N | Ack | Data<br>Byte<br>Offset | Ack | Data<br>Byte<br>N - 1 | Not<br>Ack | Stop<br>bit |  |

#### Note:

2. Register offset for indicating the starting register for indexed block write and indexed block read.

## **Data Byte 0: Control Register**

| Bit | Descriptions                                        | Туре | Power Up Condition      | Output(s) Affected  | Pin |

|-----|-----------------------------------------------------|------|-------------------------|---------------------|-----|

| 0   | SRC_DIV#<br>0 = Divide by 2<br>1 = Normal           | RW   | 1 = x1                  | OUT[0:7], OUT[0:7]# | NA  |

| 1   | PLL/BYPASS# 0 = Fanout 1 = PLL                      | RW   | 1 = PLL                 | OUT[0:7], OUT[0:7]# | NA  |

| 2   | PLL Bandwidth 0 = HIGH Bandwidth, 1 = LOW Bandwidth | RW   | 1 = Low                 | OUT[0:7], OUT[0:7]# | NA  |

| 3   | RESERVED                                            |      |                         |                     |     |

| 4   | RESERVED                                            |      |                         |                     |     |

| 5   | RESERVED                                            |      |                         |                     |     |

| 6   | SRC_STOP# 0 = Driven when stopped 1 = Tristate      | RW   | 0 = Driven when stopped | OUT[0:7], OUT[0:7]# |     |

| 7   | PWRDWN# 0 = Driven when stopped 1 = Tristate        | RW   | 0 = Driven when stopped | OUT[0:7], OUT[0:7]# | NA  |

## **Data Byte 1: Control Register**

| Bit | Descriptions                                  | Type | Power Up Condition | Output(s) Affected | Pin |

|-----|-----------------------------------------------|------|--------------------|--------------------|-----|

| 0   |                                               | RW   | 1 = Enabled        | OUT0, OUT0#        | NA  |

| 1   |                                               | RW   | 1 = Enabled        | OUT1, OUT1#        | NA  |

| 2   | OUTPUTS enable<br>1 = Enabled<br>0 = Disabled | RW   | 1 = Enabled        | OUT2, OUT2#        | NA  |

| 3   |                                               | RW   | 1 = Enabled        | OUT3, OUT3#        | NA  |

| 4   |                                               | RW   | 1 = Enabled        | OUT4, OUT4#        | NA  |

| 5   |                                               | RW   | 1 = Enabled        | OUT5, OUT5#        | NA  |

| 6   |                                               | RW   | 1 = Enabled        | OUT6, OUT6#        | NA  |

| 7   |                                               | RW   | 1 = Enabled        | OUT7, OUT7#        | NA  |

## **Data Byte 2: Control Register**

| Bit | Descriptions                                                                                       | Type | Power Up Condition | Output(s) Affected | Pin |

|-----|----------------------------------------------------------------------------------------------------|------|--------------------|--------------------|-----|

| 0   |                                                                                                    | RW   | 0 = Free running   | OUT0, OUT0#        | NA  |

| 1   |                                                                                                    | RW   | 0 = Free running   | OUT1, OUT1#        | NA  |

| 2   | Allow control of OUTPUTS with assertion of SRC_STOP#  0 = Free running  1 = Stopped with SRC_Stop# | RW   | 0 = Free running   | OUT2, OUT2#        | NA  |

| 3   |                                                                                                    | RW   | 0 = Free running   | OUT3, OUT3#        | NA  |

| 4   |                                                                                                    | RW   | 0 = Free running   | OUT4, OUT4#        | NA  |

| 5   |                                                                                                    | RW   | 0 = Free running   | OUT5, OUT5#        | NA  |

| 6   |                                                                                                    | RW   | 0 = Free running   | OUT6, OUT6#        | NA  |

| 7   |                                                                                                    | RW   | 0 = Free running   | OUT7, OUT7#        | NA  |

# **Data Byte 3: Control Register**

| Bit | Descriptions | Type | Power Up Condition | Output(s) Affected | Pin |

|-----|--------------|------|--------------------|--------------------|-----|

| 0   |              | RW   |                    |                    |     |

| 1   |              | RW   |                    |                    |     |

| 2   |              | RW   |                    |                    |     |

| 3   | RESERVED     | RW   |                    |                    |     |

| 4   |              | RW   |                    |                    |     |

| 5   |              | RW   |                    |                    |     |

| 6   |              | RW   |                    |                    |     |

| 7   |              | RW   |                    |                    |     |

## **Data Byte 4: Pericom ID Register**

| Bit | Descriptions | Type | Power Up Condition | Output(s) Affected | Pin |

|-----|--------------|------|--------------------|--------------------|-----|

| 0   |              | R    | 0                  | NA                 | NA  |

| 1   |              | R    | 0                  | NA                 | NA  |

| 2   |              | R    | 0                  | NA                 | NA  |

| 3   | Pericom ID   | R    | 0                  | NA                 | NA  |

| 4   |              | R    | 0                  | NA                 | NA  |

| 5   |              | R    | 1                  | NA                 | NA  |

| 6   |              | R    | 0                  | NA                 | NA  |

| 7   |              | R    | 0                  | NA                 | NA  |

## **Functionality**

| PWRDWN# | OUT                         | OUT#   | SRC_Stop# | OUT                         | OUT#   |

|---------|-----------------------------|--------|-----------|-----------------------------|--------|

| 1       | Normal                      | Normal | 1         | Normal                      | Normal |

| 0       | $I_{REF} \times 2$ or Float | LOW    | 0         | $I_{REF} \times 6$ or Float | LOW    |

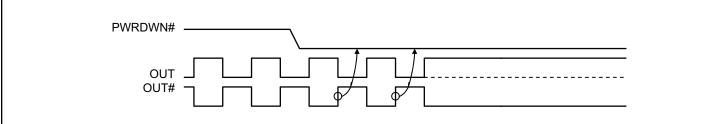

Figure 1. Power down sequence

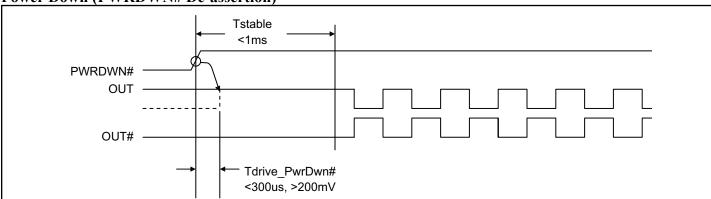

Figure 2. Power down de-assert sequence

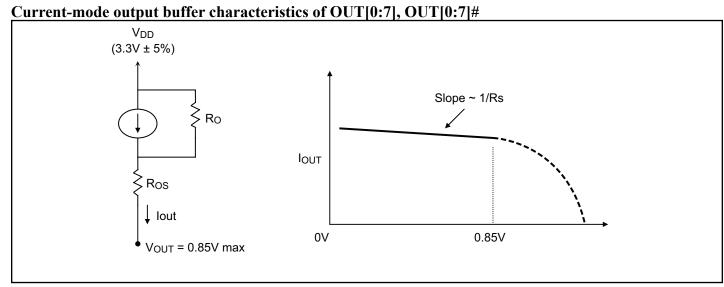

Figure 9. Simplified diagram of current-mode output buffer

### **Differential Clock Buffer characteristics**

| Symbol          | Minimum     | Maximum     |  |  |

|-----------------|-------------|-------------|--|--|

| $R_{O}$         | 3000Ω       | N/A         |  |  |

| R <sub>OS</sub> | unspecified | unspecified |  |  |

| $V_{ m OUT}$    | N/A         | 850mV       |  |  |

## **Current Accuracy**

| Sym             | bol | Conditions              | Configuration                                          | Load                                      | Min.                         | Max.                         |

|-----------------|-----|-------------------------|--------------------------------------------------------|-------------------------------------------|------------------------------|------------------------------|

| I <sub>Ot</sub> | UT  | $V_{DD} = 3.30 \pm 5\%$ | $R_{REF} = 475\Omega \ 1\%$ $I_{REF} = 2.32 \text{mA}$ | Nominal test load for given configuration | -12%<br>I <sub>nominal</sub> | +12%<br>I <sub>nominal</sub> |

#### Note:

## **Differential Clock Output Current**

| Board Target Trace/Term Z                     | Reference R, Iref = $V_{DD}/(3xRr)$             | Output Current              | V <sub>OH</sub> @ Z |

|-----------------------------------------------|-------------------------------------------------|-----------------------------|---------------------|

| 100Ω (100Ω differential ≈ 15% coupling ratio) | $R_{REF} = 475\Omega \ 1\%,$ $I_{REF} = 2.32mA$ | $I_{OH} = 6 \times I_{REF}$ | 0.7V @ 50           |

<sup>1.</sup> I<sub>NOMINAL</sub> refers to the expected current based on the configuration of the device.

# Absolute Maximum Ratings(1) (Over operating free-air temperature range)

| Symbol               | Parameters               | Min. | Max. | Units |

|----------------------|--------------------------|------|------|-------|

| $V_{\mathrm{DD\_A}}$ | 3.3V Core Supply Voltage | -0.5 | 4.6  |       |

| $V_{\mathrm{DD}}$    | 3.3V I/O Supply Voltage  | -0.5 | 4.6  | v     |

| $V_{\mathrm{IH}}$    | Input HIGH Voltage       |      | 4.6  | \ \ \ |

| $V_{ m IL}$          | Input LOW Voltage        | -0.5 |      |       |

| Ts                   | Storage Temperature      | -65  | 150  | °C    |

| V <sub>ESD</sub>     | ESD Protection           | 2000 |      | V     |

#### Note:

## **DC** Electrical Characteristics (V<sub>DD</sub> = 3.3±5%, V<sub>DD</sub> <sub>A</sub> = 3.3±5%)

| Symbol            | Parameters                  | Condition                                                                        | Min.           | Max.               | Units     |

|-------------------|-----------------------------|----------------------------------------------------------------------------------|----------------|--------------------|-----------|

| V <sub>DD_A</sub> | 3.3V Core Supply Voltage    |                                                                                  | 3.135          | 3.465              |           |

| $V_{\mathrm{DD}}$ | 3.3V I/O Supply Voltage     |                                                                                  | 3.135          | 3.465              | $_{ m V}$ |

| $V_{\mathrm{IH}}$ | 3.3V Input HIGH Voltage     |                                                                                  | 2.0            | $V_{\rm DD} + 0.3$ | ]         |

| V <sub>IL</sub>   | 3.3V Input LOW Voltage      |                                                                                  | $V_{SS} - 0.3$ | 0.8                |           |

| I <sub>IK</sub>   | Input Leakage Current       | $0 < V_{IN} < V_{DD}$                                                            | -5             | +5                 | μА        |

| V <sub>OH</sub>   | 3.3V Output HIGH Voltage    | $I_{OH} = -1 \text{mA}$                                                          | 2.4            |                    | V         |

| V <sub>OL</sub>   | 3.3V Output LOW Voltage     | $I_{OL} = 1 \text{mA}$                                                           |                | 0.4                | ]         |

| I                 | Outrout HIGH Commant        | Output HIGH Current $I_{OH} = 6 \text{ x } I_{REF}, \\ I_{REF} = 2.32 \text{mA}$ | 12.2           |                    | mA        |

| I <sub>OH</sub>   | Output HIGH Current         |                                                                                  |                | 15.6               |           |

| C <sub>IN</sub>   | Logic Input Pin Capacitance |                                                                                  | 1.5            | 5                  | nE        |

| C <sub>OUT</sub>  | Output Pin Capacitance      |                                                                                  |                | 6                  | рF        |

| L <sub>PIN</sub>  | Pin Inductance              |                                                                                  |                | 7                  | nН        |

| I <sub>DD</sub>   | Power Supply Current        | $V_{DD} = 3.465V, F_{CPU} = 100MHz$                                              |                | 250                |           |

| I <sub>SS</sub>   | Power Down Current          | Driven outputs                                                                   |                | 80                 | mA        |

| I <sub>SS</sub>   | Power Down Current          | Tristate outputs                                                                 |                | 12                 |           |

| T <sub>A</sub>    | Ambient Temperature         | Commercial (PI6C20800S)                                                          | 0              | 70                 | °C        |

|                   | Ambient Temperature         | Industrial (PI6C20800SI)                                                         | -40            | 85                 |           |

<sup>1.</sup> Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

# AC Switching Characteristics (1,2,3) $(V_{DD} = 3.3\pm5\%, V_{DDA} = 3.3\pm5\%)$

| Symbol                                | Parameters                                                               |                                      |             | Min      | Max. | Units | Notes |

|---------------------------------------|--------------------------------------------------------------------------|--------------------------------------|-------------|----------|------|-------|-------|

| F                                     | SRC/SRC# Input Frequency PLL Mode                                        |                                      | 95          | 105      | MHz  | 6     |       |

| $F_{in}$                              | SRC/SRC# Input Frequency                                                 | SRC/SRC# Input Frequency Bypass Mode |             |          | 400  | MHz   | 6     |

| T <sub>rise</sub> / T <sub>fall</sub> | Rise and Fall Time (measure                                              | d between 0.175V                     | to 0.525V)  | 175      | 700  |       | 2     |

| $\Delta T_{rise} / \Delta T_{fall}$   | Rise and Fall Time Variation                                             |                                      |             |          | 125  | ps    | 2     |

|                                       | Input to Output Propagation                                              | PLL Mode PI6C20800S PI6C20800SI      | PI6C20800S  | -250     | 250  |       |       |

| TT.                                   |                                                                          |                                      | -450        | 450      | ps   |       |       |

| $T_{pd}$                              | Delay                                                                    | D 14.1                               | PI6C20800S  | -6       | 6    |       |       |

|                                       |                                                                          | Bypass Mode PI6C                     | PI6C20800SI | -8       | 8    | ns    |       |

| T                                     | Output-to-Output Skew (PI60                                              | C20800S)                             |             |          | 50   |       | 3     |

| $T_{skew}$                            | Output-to-Output Skew (PI6C20800SI)                                      |                                      |             |          | 65   | ps    | 3     |

| V <sub>HIGH</sub>                     | Voltage HIGH (Measured at 100MHz @ 3.3V)                                 |                                      |             | 600      | 900  | mV    | 2     |

| V <sub>OVS</sub>                      | Max. Voltage                                                             |                                      |             |          | 1150 |       |       |

| V <sub>UDS</sub>                      | Min. Voltage                                                             |                                      |             | -300     |      |       |       |

| $V_{LOW}$                             | Voltage LOW                                                              |                                      |             | -150     | +150 |       | 2     |

| V <sub>cross</sub>                    | Absolute crossing poing voltages                                         |                                      |             | 250      | 550  |       | 2     |

| $\Delta V_{cross}$                    | Total Variation of V <sub>cross</sub> over all edges                     |                                      |             |          | 140  |       | 2     |

| T <sub>DC</sub>                       | Duty Cycle (Measured at 100 MHz)                                         |                                      |             | 45       | 57   | %     | 3     |

| T <sub>jcyc-cyc</sub>                 | Jitter, Cycle-to-cycle (PLL Mode, Measurement for differential waveform) |                                      |             | 70       | ps   | 4     |       |

|                                       | Jitter, Cycle-to-cycle (BYPASS mode as additive jitter)                  |                                      |             | <u> </u> |      |       |       |

| J <sub>add</sub>                      | Additive RMS phase jitter for PCIe 2.0                                   |                                      |             | <0       | 1    | ps    | 5     |

#### **Notes:**

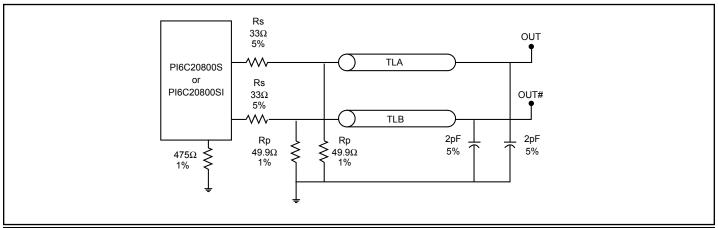

- 1. Test configuration is  $R_S = 33.2\Omega$ ,  $Rp = 49.9\Omega$ , and 2pF.

- 2. Measurement taken from Single Ended waveform.

- 3. Measurement taken from Differential waveform.

- 4. Measured using M1 timing analyzer from Amherst.

- 5. Additive jitter is calculated from input and output RMS phase jitter by using PCIe 2.0 filter.  $(J_{add} = \sqrt{(output\ jitter)^2 (input\ jitter)^2})$

- 6. -0.5% downnspread input

### **Configuration Test Load Board Termination**

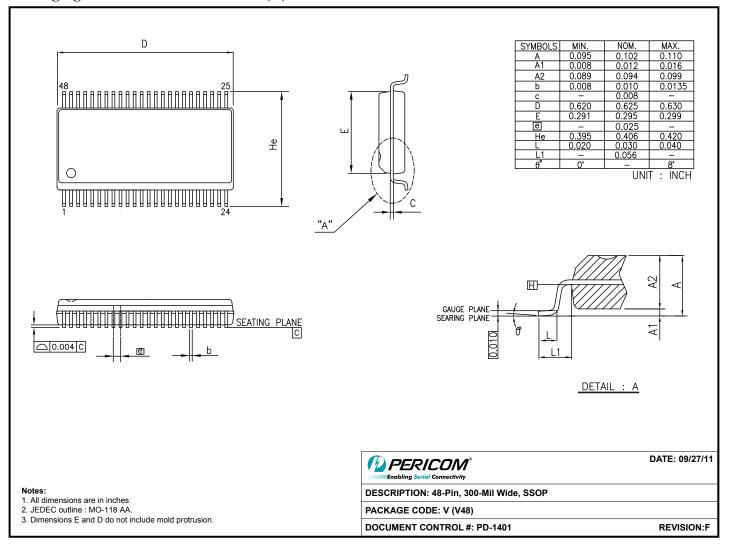

## Packaging Mechanical: 48-Pin SSOP (V)

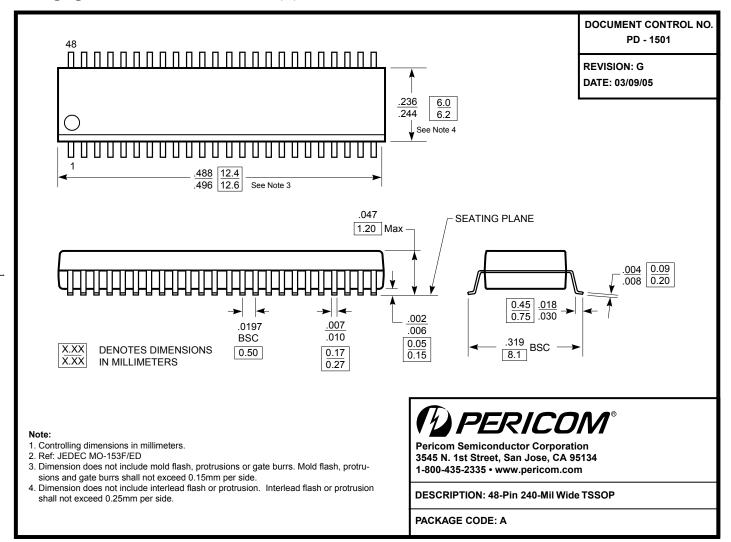

### Packaging Mechanical: 48-Pin TSSOP (A)

## Ordering Information<sup>(1,2)</sup>

| Ordering Code | Package Code | Package Description                                         |

|---------------|--------------|-------------------------------------------------------------|

| PI6C20800SVE  | VE           | 48-pin, 300-mil wide, SSOP, Pb-Free and Green               |

| PI6C20800SAE  | AE           | 48-pin, 240-mil wide, TSSOP, Pb-Free and Green              |

| PI6C20800SIVE | VE           | 48-pin, 300-mil wide, SSOP, Pb-Free and Green (Industrial)  |

| PI6C20800SIAE | AE           | 48-pin, 240-mil wide, TSSOP, Pb-Free and Green (Industrial) |

#### Notes:

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com