# LV8712T

# Allowable Operating Ratings at Ta = 25°C

| Parameter                  | Symbol          | Conditions | Ratings                      | Unit |

|----------------------------|-----------------|------------|------------------------------|------|

| Motor supply voltage range | VM              |            | 4 to 16                      | V    |

| Logic supply voltage range | Vcc             |            | 2.7 to 5.5                   | ٧    |

| Logic input voltage        | V <sub>IN</sub> |            | -0.3 tp V <sub>CC</sub> +0.3 | V    |

| VREF input voltage range   | VREF            |            | 0 to V <sub>CC</sub> -1.8    | V    |

# **Electrical Characteristics** at Ta = 25°C, VM = 12V, $V_{CC} = 3.3VVREF = 1.0V$

| Para                                                              | ameter              | Symbol              | Conditions                                             | ļ     | Ratings |       | Unit  |

|-------------------------------------------------------------------|---------------------|---------------------|--------------------------------------------------------|-------|---------|-------|-------|

|                                                                   |                     | ,                   |                                                        | min   | typ     | max   | J.III |

| Standby mode current drain                                        |                     | IMstn               | PS = "L", no load                                      |       |         | 1     | μΑ    |

|                                                                   |                     | I <sub>CC</sub> stn | PS = "L", no load                                      |       |         | 1     | μΑ    |

| Current drain                                                     |                     | IM                  | PS = "H", no load                                      | 0.3   | 0.5     | 0.7   | mA    |

|                                                                   |                     | Icc                 | PS = "H", no load                                      | 0.9   | 1.3     | 1.7   | mA    |

| Thermal shutdow                                                   | n temperature       | TSD                 | Design guarantee                                       |       | 180     |       | °C    |

| Thermal hysteres                                                  | sis width           | ΔTSD                | Design guarantee                                       |       | 40      |       | °C    |

| V <sub>CC</sub> low voltage                                       | cutting voltage     | VthV <sub>CC</sub>  |                                                        | 2.1   | 2.4     | 2.7   | V     |

| Low voltage hyst                                                  | eresis voltage      | VthHIS              |                                                        | 100   | 130     | 160   | mV    |

| REG5 output vol                                                   | tage                | Vreg5               | I <sub>O</sub> = -1mA                                  | 4.5   | 5       | 5.5   | V     |

| Output on resista                                                 | ance                | RonU                | I <sub>O</sub> = -800mA, Source-side on resistance     |       | 0.78    | 1.0   | Ω     |

|                                                                   |                     | RonD                | I <sub>O</sub> = 800mA, Sink-side on resistance        |       | 0.32    | 0.43  | Ω     |

| Output leakage o                                                  | current             | l <sub>O</sub> leak | V <sub>O</sub> = 15V                                   |       |         | 10    | μΑ    |

| Diode forward vo                                                  | ltage               | VD                  | ID = -800mA                                            |       | 1.0     | 1.2   | V     |

| Logic pin input cu                                                | urrent              | I <sub>IN</sub> L   | V <sub>IN</sub> = 0.8V                                 | 4     | 8       | 12    | μΑ    |

|                                                                   |                     | I <sub>IN</sub> H   | V <sub>IN</sub> = 3.3V                                 | 22    | 33      | 45    | μΑ    |

| Logic high-level i                                                | nput voltage        | V <sub>IN</sub> H   |                                                        | 2.0   |         |       | V     |

| Logic low-level in                                                | put voltage         | V <sub>IN</sub> L   |                                                        |       |         | 0.8   | V     |

| VREF input curre                                                  | ent                 | I <sub>REF</sub>    | VREF = 1.0V                                            | -0.5  |         |       | μΑ    |

| Current setting                                                   | 2W1-2-phase         | Vtdac0_2W           | Step 0 (When initialized : channel 1                   | 0.191 | 0.2     | 0.209 | V     |

| comparator<br>threshold<br>voltage<br>(current step<br>switching) | drive               |                     | comparator level)                                      |       |         |       |       |

|                                                                   |                     | Vtdac1_2W           | Step 1 (Initial state+1)                               | 0.187 | 0.196   | 0.205 | V     |

|                                                                   |                     | Vtdac2_2W           | Step 2 (Initial state+2)                               | 0.175 | 0.184   | 0.193 | V     |

|                                                                   |                     | Vtdac3_2W           | Step 3 (Initial state+3)                               | 0.158 | 0.166   | 0.174 | V     |

| Switching)                                                        |                     | Vtdac4_2W           | Step 4 (Initial state+4)                               | 0.132 | 0.140   | 0.148 | V     |

|                                                                   |                     | Vtdac5_2W           | Step 5 (Initial state+5)                               | 0.102 | 0.110   | 0.118 | V     |

|                                                                   |                     | Vtdac6_2W           | Step 6 (Initial state+6)                               | 0.068 | 0.076   | 0.084 | V     |

|                                                                   |                     | Vtdac7_2W           | Step 7 (Initial state+7)                               | 0.032 | 0.040   | 0.048 | V     |

|                                                                   | W1-2-phase          | Vtdac0_W            | Step 0 (When initialized : channel 1                   | 0.191 | 0.200   | 0.209 | V     |

|                                                                   | drive               | )// L 0 14/         | comparator level)                                      | 0.475 | 0.404   | 0.400 |       |

|                                                                   |                     | Vtdac2_W            | Step 2 (Initial state+1)                               | 0.175 | 0.184   | 0.193 | V     |

|                                                                   |                     | Vtdac4_W            | Step 4 (Initial state+2)                               | 0.132 | 0.140   | 0.148 | V     |

|                                                                   |                     | Vtdac6_W            | Step 6 (Initial state+3)                               | 0.068 | 0.076   | 0.084 | V     |

|                                                                   | 1-2 phase drive     | Vtdac0_H            | Step 0 (When initialized : channel 1 comparator level) | 0.191 | 0.200   | 0.209 | V     |

|                                                                   |                     | Vtdac4_H            | Step 4 (Initial state+1)                               | 0.132 | 0.140   | 0.148 | V     |

|                                                                   | 2 phase drive       | Vtdac4_F            | Step 4' (When initialized : channel 1                  | 0.191 | 0.200   | 0.209 | V     |

| Current setting or                                                | <br>omparator       | Vtatt00             | comparator level)  ATT1 = L, ATT2 = L                  | 0.191 | 0.200   | 0.209 | V     |

| threshold voltage                                                 | •                   | Vtatt01             | ATT1 = H, ATT2 = L                                     | 0.152 | 0.160   | 0.168 |       |

| (current attenuat                                                 | ion rate switching) | Vtatt10             | ATT1 = L, ATT2 = H                                     | 0.112 | 0.120   | 0.128 |       |

| 5,                                                                |                     | Vtatt11             | ATT1 = H, ATT2 = H                                     | 0.072 | 0.080   | 0.088 |       |

| Chopping freque                                                   | ncv                 | Fchop               | Cchop = 220pF                                          | 36    | 45      | 54    | k-    |

| CHOP pin thresh                                                   |                     |                     | 30/10p = 220pi                                         |       |         |       |       |

| orior pili tillesn                                                | ioiu voitage        | VCHOPH              |                                                        | 0.6   | 0.7     | 0.8   |       |

| CHOD -:                                                           | o /dio ob g         | VCHOPL              |                                                        | 0.17  | 0.2     | 0.23  |       |

| CHOP pin charge/discharge current                                 |                     | Ichop               |                                                        | 7     | 10      | 13    | μ     |

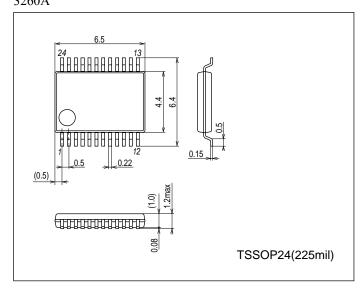

# **Package Dimensions**

unit: mm (typ) 3260A

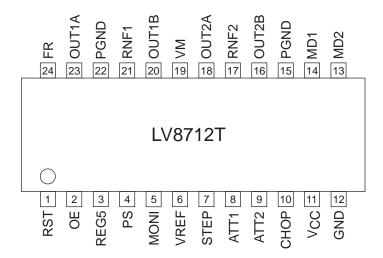

## **Pin Assignment**

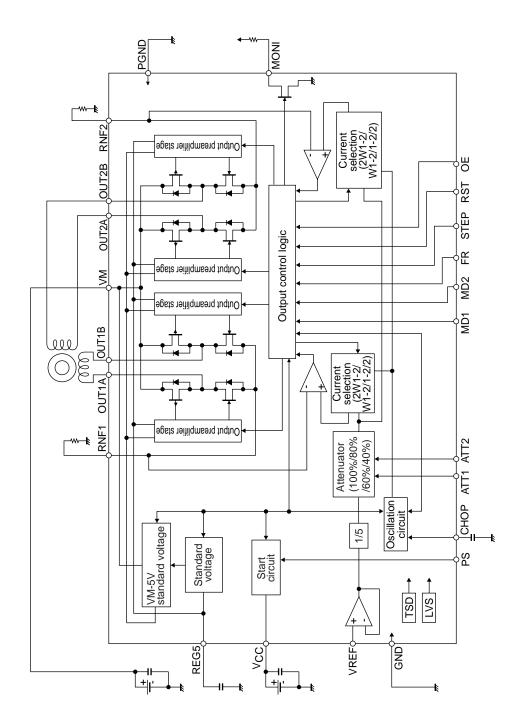

## **Block Diagram**

## **Pin Functions**

| FIIIFU  | inctions |                                      |                                                       |

|---------|----------|--------------------------------------|-------------------------------------------------------|

| Pin No. | Pin Name | Pin Functtion                        | Equivalent Circuit                                    |

| 1       | RST      | Excitation reset signal input pin.   | V                                                     |

| 2       | OE       | Output enable signal input pin.      | VCC O P                                               |

| 7       | STEP     | STEP signal input pin.               |                                                       |

| 8       |          |                                      |                                                       |

|         | ATT1     | Motor holding current switching pin. | <b>★</b>   <del> </del>                               |

| 9       | ATT2     | Motor holding current switching pin. |                                                       |

| 13      | MD2      | Excitation mode switching pin 2.     | 6kΩ • F                                               |

| 14      | MD1      | Excitation mode switching pin 1.     | → • • • • • • • • • • • • • • • • • • •               |

| 24      | FR       | CW / CCW switching signal input pin. |                                                       |

|         |          |                                      |                                                       |

|         |          |                                      | <b>★</b> \$100kΩ <b>+</b>                             |

|         |          |                                      | 1 1 1 1 1 1 1                                         |

|         |          |                                      |                                                       |

|         |          |                                      | GND O-                                                |

|         |          |                                      | GINDO                                                 |

| 4       | PS       | Power save signal input pin.         | Vac                                                   |

|         |          |                                      | VCC ○ •                                               |

|         |          |                                      | <u> </u>                                              |

|         |          |                                      | <b>↑</b>                                              |

|         |          |                                      |                                                       |

|         |          |                                      | 4                                                     |

|         |          |                                      |                                                       |

|         |          |                                      |                                                       |

|         |          |                                      | 6kΩ "                                                 |

|         |          |                                      | • · · · · ·                                           |

|         |          |                                      | <b>★</b>   "                                          |

|         |          |                                      | \$70kΩ                                                |

|         |          |                                      |                                                       |

|         |          |                                      | GND O • • •                                           |

| 16      | OUT2B    | Channel 2 OUTB output pin.           | \/A4                                                  |

| 17      | RNF2     | Channel 2 current-sense resistor     | VM                                                    |

|         |          | connection pin.                      |                                                       |

| 18      | OUT2A    | Channel 2 OUTA output pin.           |                                                       |

| 20      | OUT1B    | Channel 1 OUTB output pin.           |                                                       |

| 21      | RNF1     | Channel 1 current-sense resistor     | 23(18)                                                |

| 21      | IXINI    | connection pin.                      |                                                       |

| 23      | OUT1A    | Channel 1 OUTA output pin.Power      |                                                       |

| 23      | OUTTA    | Channel 1 00 1A output pin.Power     |                                                       |

|         |          |                                      | 560Ω 1κΩ                                              |

|         |          |                                      |                                                       |

|         |          |                                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|         |          |                                      |                                                       |

|         |          |                                      | GND O-                                                |

| 6       | VREF     | Constant current control reference   | V                                                     |

|         |          | voltage input pin.                   | VCC O                                                 |

|         |          |                                      |                                                       |

|         |          |                                      | <b>↓</b>                                              |

|         |          |                                      | T                                                     |

|         |          |                                      | 5000                                                  |

|         |          |                                      | 6 500Ω                                                |

|         |          |                                      |                                                       |

|         |          |                                      |                                                       |

|         |          |                                      | Ţ                                                     |

|         |          |                                      |                                                       |

|         |          |                                      | GND O •                                               |

|         |          |                                      |                                                       |

Continued on next page.

# LV8712T

|         | from preceding | page.                                                |                                                     |

|---------|----------------|------------------------------------------------------|-----------------------------------------------------|

| Pin No. | Pin Name       | Pin Functtion                                        | Equivalent Circuit                                  |

| 3       | REG5           | Internal power supply capacitor connection pin.      | $50\Omega$ $6k\Omega$ $186k\Omega$ $64k\Omega$      |

| 5       | MONI           | Position detection monitor pin.                      | VCC<br>\$ 100Ω<br>GND Φ                             |

| 10      | CHOP           | Chopping frequency setting capacitor connection pin. | VCC 0 500Ω 500Ω 100 100 100 100 100 100 100 100 100 |

## **Description of operation**

#### Stepping motor control

## (1) Power save function

This IC is switched between standby and operating mode by setting the PS pin. In standby mode, the IC is set to power-save mode and all logic is reset. In addition, the internal regulator circuit do not operate in standby mode.

| PS          | Mode           | Internal regulator |  |

|-------------|----------------|--------------------|--|

| Low or Open | Standby mode   | Standby            |  |

| High        | Operating mode | Operating          |  |

#### (2) The order of turning on recommended power supply

The order of turning on each power supply recommends the following.

VCC power supply order  $\rightarrow$  VM power supply order  $\rightarrow$  PS pin = High

It becomes the above-mentioned opposite for power supply OFF.

However, the above-mentioned is a recommendation, the overcurrent is not caused by not having defended this, and IC is destroyed.

#### (3) STEP pin function

| Input |          | Operating mode           |

|-------|----------|--------------------------|

| PS    | STP      |                          |

| Low   | *        | Standby mode             |

| High  |          | Excitation step proceeds |

| High  | <b>—</b> | Excitation step is kept  |

#### (4) Excitation mode setting function(initial position)

| MD1  | MD2  | Excitation mode                | Initial position    |       |

|------|------|--------------------------------|---------------------|-------|

|      |      |                                | Channel 1 Channel 2 |       |

| Low  | Low  | 2 phase excitation             | 100%                | -100% |

| High | Low  | 1-2 phase excitation           | 100%                | 0%    |

| Low  | High | W1-2 phase excitation          | 100%                | 0%    |

| High | High | 2W1-2 phase excitation 100% 0% |                     | 0%    |

This is the initial position of each excitation mode in the initial state after power-on and when the counter is reset.

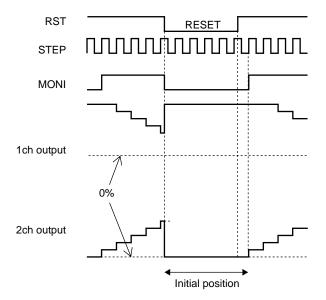

## (5) Position detection monitoring function

The MONI position detection monitoring pin is of an open drian type.

When the excitation position is in the initial position, the MONI output is placed in the ON state.

(Refer to "(12) Examples of current waveforms in each of the excitation modes.")

#### (6) Reset function

| RST  | Operating mode   |  |

|------|------------------|--|

| High | Normal operation |  |

| Low  | Reset state      |  |

When the RST pin is set to Low, the excitation position of the output is forcibly set to the initial position, and the MONI output is placed in the ON state. When RST is then set to High, the excitation position is advanced by the next STEP input.

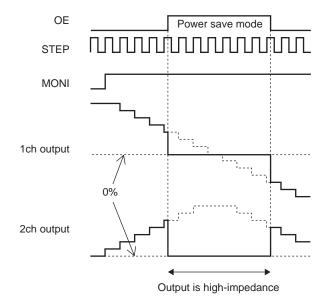

## (7) Output enable function

| OE   | Operating mode |

|------|----------------|

| Low  | Output ON      |

| High | Output OFF     |

When the OE pin is set High, the output is forced OFF and goes to high impedance.

However, the internal logic circuits are operating, so the excitation position proceeds when the STEP signal is input.

Therefore, when OE is returned to Low, the output level conforms to the excitation position proceeded by the STEP input.

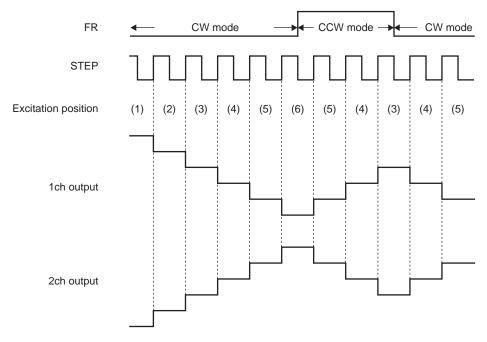

(8) Forward/reverse switching function

| FR   | Operating mode          |  |  |

|------|-------------------------|--|--|

| Low  | Clockwise (CW)          |  |  |

| High | Counter-clockwise (CCW) |  |  |

The internal D/A converter proceeds by one bit at the rising edge of the input STEP pulse.

In addition, CW and CCW mode are switched by setting the FR pin.

In CW mode, the channel 2 current phase is delayed by 90° relative to the channel 1 current.

In CCW mode, the channel 2 current phase is advanced by 90° relative to the channel 1 current.

#### (9) Setting constant-current control

The setting of STM driver's constant current control is decided the VREF voltage from the resistance connected between RNF and GND by the following expression.

$$I_{OUT} = (VREF/5)/RNF$$

resistance

The voltage input to the VREF pin can be switched to four-step settings depending on the statuses of the two inputs, ATT1 and ATT2. This is effective for reducing power consumption when motor holding current is supplied.

Attenuation function for VREF input voltage

| ATT1 | ATT2 | Current setting reference voltage attenuation rati |  |  |

|------|------|----------------------------------------------------|--|--|

| Low  | Low  | 100%                                               |  |  |

| High | Low  | 80%                                                |  |  |

| Low  | High | 60%                                                |  |  |

| High | High | 40%                                                |  |  |

The formula used to calculate the output current when using the function for attenuating the VREF input voltage is given below.

$I_{OUT} = (VREF/5) \times (attenuation ratio)/RNF resistance$

Example : At VREF of 1.0V, a reference voltage setting of 100% [(ATT1, ATT2) = (L, L)] and an RNF resistance of  $0.5\Omega$ , the output current is set as shown below.

$$I_{OUT} = 1.0V/5 \times 100\%/0.5\Omega = 400 \text{mA}$$

If, in this state, (ATT1, ATT2) is set to (H, H), IOUT will be as follows:

$$I_{OUT} = 400 \text{mA} \times 40\% = 160 \text{mA}$$

In this way, the output current is attenuated when the motor holding current is supplied so that power can be conserved.

<sup>\*</sup> The above setting is the output current at 100% of each excitation mode.

## (10) Chopping frequency setting

For constant-current control, this IC performs chopping operations at the frequency determined by the capacitor (Cchop) connected between the CHOP pin and GND.

The chopping frequency is set as shown below by the capacitor (Cchop) connected between the CHOP pin and GND.

Tchop

$$\approx C \times V \times 2 / I$$

(s)

V: Width of suresshu voltage, typ 0.5V

I: Charge/discharge current, typ 10μA

For instance, when Cchop is 200pF, the chopping frequency will be as follows:

Fchop

$$\approx 1 / \text{Tchop (Hz)}$$

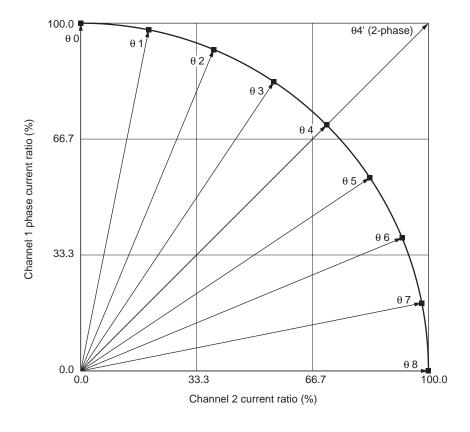

## (11) Output current vector locus (one step is normalized to 90 degrees)

## Setting current ration in each excitation mode

| STEP | 2W1-2 phase (%) |           | 2W1-2 phase (%) W1-2 phase (%) 1-2 phase (%) |           | ase (%)   | 2-phase (%) |           |           |

|------|-----------------|-----------|----------------------------------------------|-----------|-----------|-------------|-----------|-----------|

|      | Channel 1       | Channel 2 | Channel 1                                    | Channel 2 | Channel 1 | Channel 2   | Channel 1 | Channel 2 |

| θ0   | 100             | 0         | 100                                          | 0         | 100       | 0           |           |           |

| θ1   | 98              | 20        |                                              |           |           |             |           |           |

| θ2   | 92              | 38        | 92                                           | 38        |           |             |           |           |

| θ3   | 83              | 55        |                                              |           |           |             |           |           |

| θ4   | 70              | 70        | 70                                           | 70        | 70        | 70          | 100       | 100       |

| θ5   | 55              | 83        |                                              |           |           |             |           |           |

| θ6   | 38              | 92        | 38                                           | 92        |           |             |           |           |

| θ7   | 20              | 98        |                                              |           |           |             |           |           |

| θ8   | 0               | 100       | 0                                            | 100       | 0         | 100         |           |           |

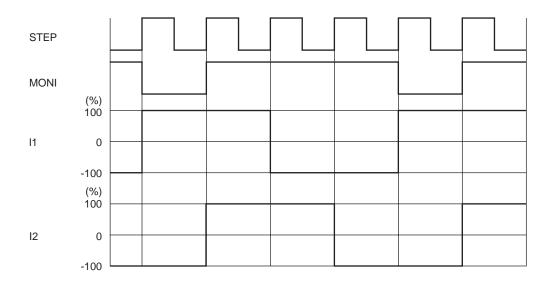

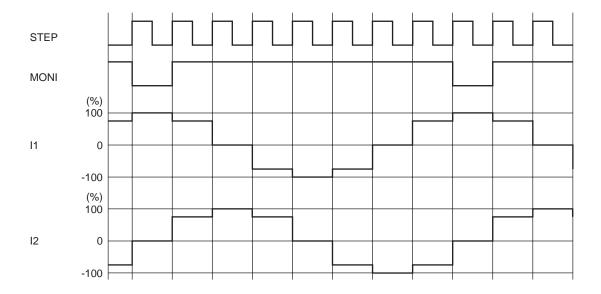

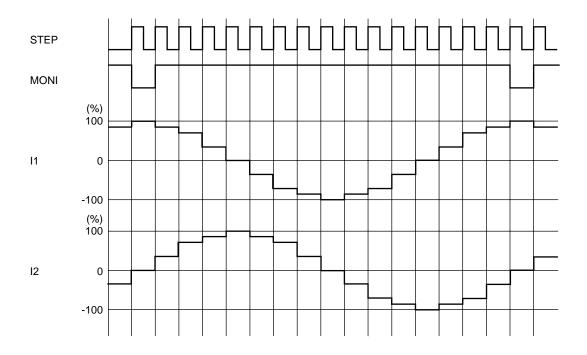

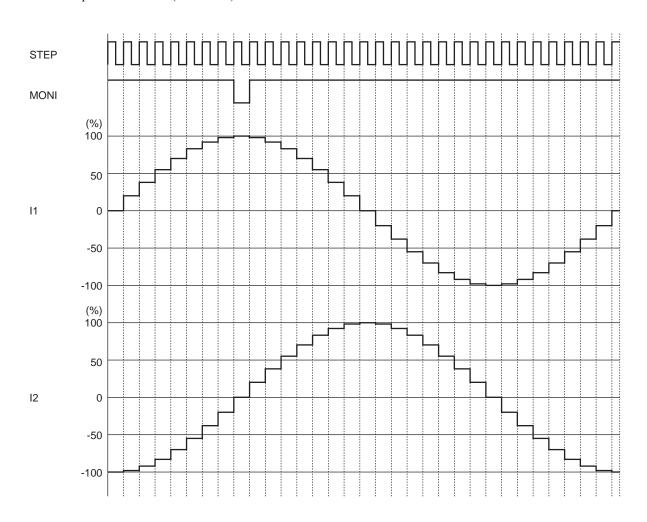

# (12) Typical current waveform in each excitation mode

2-phase excitation (CW mode)

# 1-2 phase excitation (CW mode)

W1-2 phase excitation (CW mode)

2W1-2 phase excitation (CW mode)

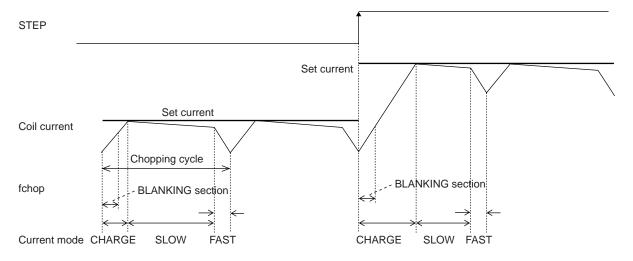

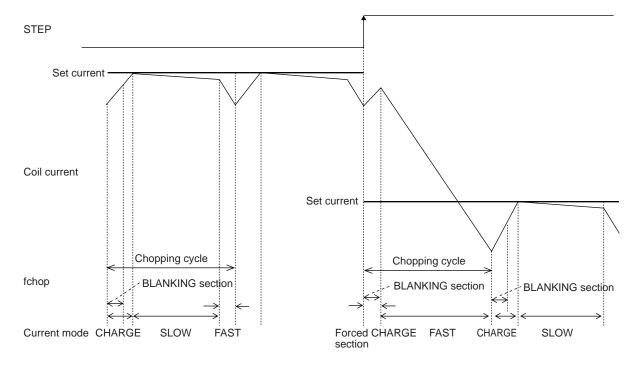

## (13) Current control timing chart(Chopping operation)

(Sine wave increasing direction)

(Sine wave decreasing direction)

In each current mode, the operation sequence is as described below:

- At rise of chopping frequency, the CHARGE mode begins. (The Blanking section in which the CHARGE mode is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF) exists for 1μs.)

- The coil current (ICOIL) and set current (IREF) are compared in this blanking time.

When (ICOIL < IREF) state exists;

The CHARGE mode up to ICOIL  $\geq$  IREF, then followed by changeover to the SLOW DECAY mode, and finally by the FAST DECAY mode for approximately 1 $\mu$ s.

When (ICOIL < IREF) state does not exist;

The FAST DECAY mode begins. The coil current is attenuated in the FAST DECAY mode till one cycle of chopping is over.

Above operations are repeated. Normally, the SLOW (+FAST) DECAY mode continues in the sine wave increasing direction, then entering the FAST DECAY mode till the current is attenuated to the set level and followed by the SLOW DECAY mode.

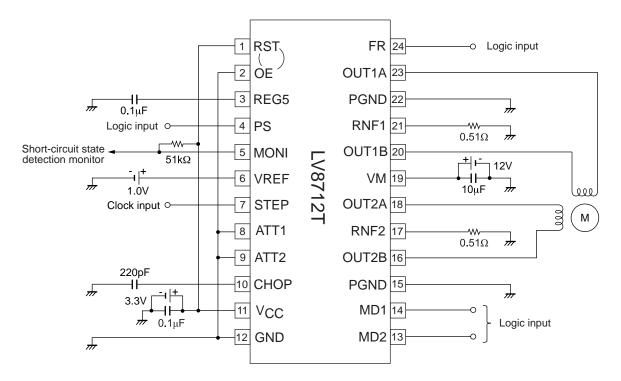

## **Application Circuit Example**

The formulae for setting the constants in the examples of the application circuits above are as follows: Constant current (100%) setting

When VREF = 1.0V

$$I_{OUT} = VREF/5/RNF \text{ resistance}$$

$$= 1.0V/5/0.51\Omega = 0.392A$$

Chopping frequency setting

Fchop = Ichop/ (Cchop × Vtchop × 2) =  $10\mu$ A/ (220pF × 0.5V × 2) = 45kHz

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa