## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| ` ,                                     |                         |

|-----------------------------------------|-------------------------|

| Total Supply Voltage (V+ to GND)        | 6V                      |

| Maximum Voltage                         |                         |

| on any Pin(GND $- 0.3V$ ) $\leq V$      | $PIN \leq (V^+ + 0.3V)$ |

| Output Short-Circuit Duration (Note 2). | Indefinite              |

| Operating Temperature Range (Note 3)    |                         |

| LTC6903CMS8/LTC6904CMS8                 | 40°C to 85°C            |

| LTC6903IMS8/LTC6904IMS8                 | 40°C to 85°C            |

| LTC6903HMS8/LTC6904HMS8                 | 40°C to 125°C           |

| LTC6904MPMS8                            | 55°C to 125°C           |

| Specified Temperature Range (Note 4)    |                         |

| LTC6903CMS8/LTC6904CMS8                 | 0°C to 70°C             |

| LTC6903IMS8/LTC6904IMS8                 | 40°C to 85°C            |

| LTC6903HMS8/LTC6904HMS8                 | 40°C to 125°C           |

| LTC6904MPMS8                            | 55°C to 125°C           |

| Storage Temperature Range               | 65°C to 150°C           |

| Lead Temperature (Soldering, 10 sec)    | 300°C                   |

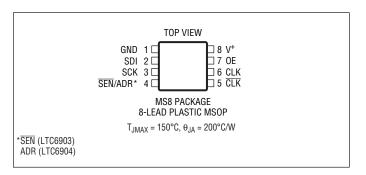

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION | SPECIFIED TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------|-----------------------------|

| LTC6903CMS8#PBF  | LTC6903CMS8#TRPBF  | LTABN         | 8-Lead Plastic MSOP | 0°C to 70°C                 |

| LTC6903IMS8#PBF  | LTC6903IMS8#TRPBF  | LTABN         | 8-Lead Plastic MSOP | -40°C to 85°C               |

| LTC6903HMS8#PBF  | LTC6903HMS8#TRPBF  | LTABN         | 8-Lead Plastic MSOP | -40°C to 125°C              |

| LTC6904CMS8#PBF  | LTC6904CMS8#TRPBF  | LTAES         | 8-Lead Plastic MSOP | 0°C to 70°C                 |

| LTC6904IMS8#PBF  | LTC6904IMS8#TRPBF  | LTAES         | 8-Lead Plastic MSOP | -40°C to 85°C               |

| LTC6904HMS8#PBF  | LTC6904HMS8#TRPBF  | LTAES         | 8-Lead Plastic MSOP | -40°C to 125°C              |

| LTC6904MPMS8#PBF | LTC6904MPMS8#TRPBF | LTFDX         | 8-Lead Plastic MSOP | -55°C to 125°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . V<sup>+</sup> = 2.7V to 5.5V, GND = 0V, unless otherwise noted.

| SYMBOL              | PARAMETER                         | CONDITIONS                                                                                                                                                                                                        |   | MIN        | TYP          | MAX         | UNITS    |

|---------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|--------------|-------------|----------|

| Δfi                 | Initial Frequency Accuracy        | f = 1.039kHz, V <sup>+</sup> = 3V, C <sub>LOAD</sub> = 5pF                                                                                                                                                        |   |            |              | ±0.75       | %        |

| $\Delta f$          | Total Frequency Accuracy (Note 7) | Single Output Active:  Over All Settings, V <sup>+</sup> = 2.7V, C <sub>LOAD</sub> = 5pF  Over All Settings, V <sup>+</sup> = 5.5V, C <sub>LOAD</sub> = 5pF                                                       |   |            | 0.5<br>0.5   | 1.1<br>1.6  | %<br>%   |

|                     |                                   | LTC6903CMS8, LTC6904CMS8:<br>Over All Settings, V <sup>+</sup> = 2.7V, $C_{LOAD}$ = 5pF<br>Over All Settings, V <sup>+</sup> = 5.5V, $C_{LOAD}$ = 5pF                                                             | • |            | 0.5<br>0.5   | 1.65<br>2   | %        |

|                     |                                   | LTC6903HMS8, LTC6903IMS8,<br>LTC6904HMS8, LTC6904IMS8,<br>LTC6904MPMS8:<br>Over All Settings, V <sup>+</sup> = 2.7V, C <sub>LOAD</sub> = 5pF<br>Over All Settings, V <sup>+</sup> = 5.5V, C <sub>LOAD</sub> = 5pF | • |            | 0.5<br>0.5   | 1.9<br>2.2  | %<br>%   |

| f <sub>MAX</sub>    | Maximum Operating Frequency       |                                                                                                                                                                                                                   |   |            | 68           |             | MHz      |

| f <sub>MIN</sub>    | Minimum Operating Frequency       |                                                                                                                                                                                                                   |   |            | 1.039        |             | kHz      |

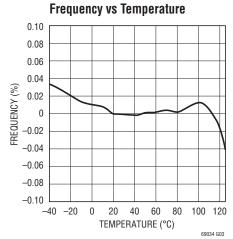

| $\Delta f/\Delta T$ | Frequency Drift Over Temperature  |                                                                                                                                                                                                                   |   |            | 10           |             | ppm/°C   |

| $\Delta f/\Delta V$ | Frequency Drift Over Supply       |                                                                                                                                                                                                                   |   |            | 0.05         |             | %/V      |

|                     | Long-Term Frequency Stability     |                                                                                                                                                                                                                   |   |            | 300          |             | ppm/√kHr |

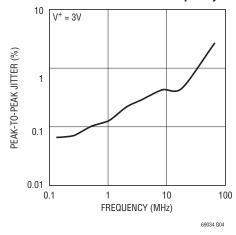

|                     | Timing Jitter (See Graph)         | 1.039kHz to 8.5MHz<br>1.039kHz to 68MHz                                                                                                                                                                           |   |            | 0.4<br>1     |             | %<br>%   |

|                     | Duty Cycle                        | 1.039kHz to 1MHz<br>1.039kHz to 68MHz                                                                                                                                                                             | • | 49         | 50<br>50     | 51          | %<br>%   |

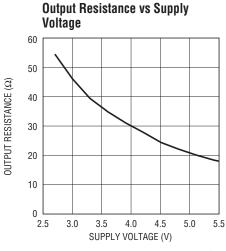

| R <sub>OUT</sub>    | Output Resistance                 | CLK, CLK Pins, V <sup>+</sup> = 2.7V                                                                                                                                                                              |   |            | 45           |             | Ω        |

| $V_{OH}$            | High Level Output Voltage         | $V^{+} = 5.5V$ , 4mA Load $V^{+} = 2.7V$ , 4mA Load                                                                                                                                                               | • | 4.8<br>2   | 5.3<br>2.3   |             | V<br>V   |

|                     |                                   | $V^{+} = 5.5V$ , 1mA Load $V^{+} = 2.7V$ , 1mA Load                                                                                                                                                               | • | 5.2<br>2.3 | 5.45<br>2.55 |             | V        |

| V <sub>OL</sub>     | Low Level Output Voltage          | $V^{+} = 5.5V$ , 4mA Load $V^{+} = 2.7V$ , 4mA Load                                                                                                                                                               | • |            | 0.15<br>0.25 | 0.3<br>0.45 | V        |

|                     |                                   | V <sup>+</sup> = 5.5V, 1mA Load<br>V <sup>+</sup> = 2.7V, 1mA Load                                                                                                                                                | • |            | 0.05<br>0.05 | 0.15<br>0.2 | V        |

| t <sub>r</sub>      | Output Rise Time (10% - 90%)      | $V^+ = 5.5V$ , $R_{LOAD} = \infty$ , $C_{LOAD} = 5pF$<br>$V^+ = 2.7V$ , $R_{LOAD} = \infty$ , $C_{LOAD} = 5pF$                                                                                                    |   |            | 1            |             | ns<br>ns |

| t <sub>f</sub>      | Output Fall Time (10% - 90%)      | $V^+ = 5.5V$ , $R_{LOAD} = \infty$ , $C_{LOAD} = 5pF$<br>$V^+ = 2.7V$ , $R_{LOAD} = \infty$ , $C_{LOAD} = 5pF$                                                                                                    |   |            | 1            |             | ns<br>ns |

# **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . V<sup>+</sup> = 2.7V to 5.5V, GND = 0V, unless otherwise noted.

| SYMBOL                | PARAMETER                                               | CONDITIONS                                                                                                                                                     |   | MIN | TYP                    | MAX                   | UNITS                |

|-----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------------------------|-----------------------|----------------------|

| V <sub>S</sub>        | Supply Voltage                                          | Applied Between V <sup>+</sup> and GND                                                                                                                         | • | 2.7 |                        | 5.5                   | V                    |

| I <sub>S</sub> , SHDN | V <sup>+</sup> Supply Current, Shutdown                 | V <sub>S</sub> = 2.7V<br>V <sub>S</sub> = 5.5V                                                                                                                 | • |     | 0.25<br>0.6            | 0.6<br>2.2            | mA<br>mA             |

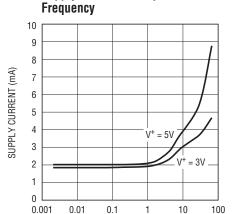

| I <sub>S</sub> , DC   | V <sup>+</sup> Supply Current, Single Output<br>Enabled | f = 68MHz, 5pF Load, V <sup>+</sup> = 2.7V<br>f < 1MHz, V <sup>+</sup> = 2.7V<br>f = 68MHz, 5pF Load, V <sup>+</sup> = 5.5V<br>f < 1MHz, V <sup>+</sup> = 5.5V | • |     | 3.6<br>1.7<br>7<br>1.9 | 7<br>3.1<br>15<br>4.5 | mA<br>mA<br>mA<br>mA |

## **SERIAL PORT ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V^+ = 2.7V$ to 5.5V, GND = 0V, unless otherwise noted.

| SYMBOL              | PARAMETER                                       | CONDITIONS |   | MIN     | TYP | MAX     | UNITS |

|---------------------|-------------------------------------------------|------------|---|---------|-----|---------|-------|

| V <sub>IH</sub>     | Min High Level Input Voltage SEN, SCK, SDI Pins |            | • |         |     | 0.67 V+ | V     |

| $\overline{V_{IL}}$ | Max Low Level Input Voltage SEN, SCK, SDI Pins  |            | • | 0.33 V+ |     |         | V     |

| I <sub>IN</sub>     | Digital Input Leakage<br>SEN, SCK, SDI Pins     |            | • |         |     | 10      | μА    |

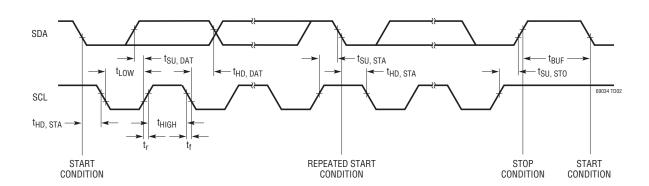

## **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . V<sup>+</sup> = 2.7V to 5.5V, GND = 0V, unless otherwise noted.

| SYMBOL               | PARAMETER                                      | MIN | TYP | MAX | UNITS |     |  |  |

|----------------------|------------------------------------------------|-----|-----|-----|-------|-----|--|--|

| LTC6903 (Notes 5, 6) |                                                |     |     |     |       |     |  |  |

| f <sub>SCK</sub>     | Serial Port Clock Frequency                    | •   |     |     | 20    | MHz |  |  |

| t <sub>CKHI</sub>    | Min Clock HIGH Time                            | •   |     |     | 25    | ns  |  |  |

| t <sub>CKLO</sub>    | Min Clock LOW Time                             | •   |     |     | 25    | ns  |  |  |

| t <sub>SU</sub>      | Min Setup Time – SDI to SCK                    | •   |     |     | 10    | ns  |  |  |

| t <sub>HLD</sub>     | Min Hold Time – SCK to SDI                     | •   |     |     | 10    | ns  |  |  |

| t <sub>LCH</sub>     | Min Latch Time – SEN to SEN                    | •   |     |     | 400   | ns  |  |  |

| t <sub>FCK</sub>     | Min First Clock – SEN to SCK                   | •   |     |     | 20    | ns  |  |  |

| LTC6904 (No          | otes 5, 6)                                     |     |     |     |       |     |  |  |

| f <sub>SMB</sub>     | SMBus Operating Frequency                      | •   | 10  |     | 100   | kHz |  |  |

| t <sub>BUF</sub>     | Bus Free Time Between STOP and START Condition | •   | 4.7 |     |       | μs  |  |  |

| t <sub>HD,STA</sub>  | Hold Time After (Repeated) START Condition     | •   | 4.0 |     |       | μs  |  |  |

| t <sub>SU,STA</sub>  | Repeated START Condition Setup Time            | •   | 4.7 |     |       | μs  |  |  |

| t <sub>SU,STO</sub>  | STOP Condition Setup Time                      | •   | 4.0 |     |       | μs  |  |  |

| LTC6904 (No          | otes 5, 6)                                     |     |     |     |       |     |  |  |

| t <sub>HD,DAT</sub>  | Data Hold Time                                 | •   | 300 |     |       | ns  |  |  |

| t <sub>SU,DAT</sub>  | Data Setup Time                                | •   | 250 |     |       | ns  |  |  |

| t <sub>LOW</sub>     | Clock LOW Period                               | •   | 4.7 |     |       | μs  |  |  |

| t <sub>HIGH</sub>    | Clock HIGH Period                              | •   | 4.0 |     | 50    | μs  |  |  |

| t <sub>f</sub>       | Clock, Data Fall Time                          | •   |     |     | 300   | ns  |  |  |

| $\overline{t_r}$     | Clock, Data Rise Time                          | •   |     |     | 1000  | ns  |  |  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** A heat sink may be required to keep the junction temperature below the absolute maximum when the output is shorted indefinitely.

**Note 3:** The LTC6903CMS8, LTC6904CMS8, LTC6903IMS8 and LTC6904IMS8 are guaranteed functional over the operating temperature range of -40°C to 85°C.

**Note 4:** The LTC6903CMS8 and LTC6904CMS8 are guaranteed to meet the specified performance limits over the 0°C to 70°C temperature range and are designed, characterized and expected to meet the specified

performance from -40°C to 85°C but are not tested or QA sampled at these temperatures. The LTC6903IMS8 and LTC6904IMS8 are guaranteed to meet the specified performance limits over the -40°C to 85°C temperature range. The LTC6903HMS8 and LTC6904HMS8 are guaranteed to meet the specified performance limits over the -40°C to 125°C temperature range. The LTC6904MPMS8 is guaranteed to meet the specified performance limits over the -55°C to 125°C temperature range.

Note 5: All values are referenced to  $V_{IH}$  and  $V_{IL}$  levels.

Note 6: Guaranteed by design and not subject to test.

**Note 7:** Parts with tighter frequency accuracy are available. Consult LTC Marketing for details.

69034fe

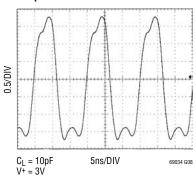

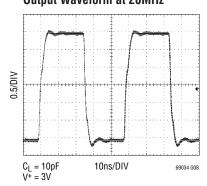

## TYPICAL PERFORMANCE CHARACTERISTICS

**Supply Current vs Output**

#### Peak-to-Peak Jitter vs Frequency

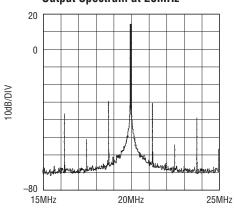

#### Output Spectrum at 20MHz

69034 G07

FREQUENCY (MHz)

69034 G05

#### Output Waveform at 20MHz

69034fe

## LTC6903/LTC6904

## PIN FUNCTIONS

**GND (Pin 1):** Negative Power Supply (Ground). Should be tied directly to a ground plane for best performance.

**SDI (Pin 2):** Serial Data Input. Data for serial transfer is presented on this pin.

**SCK (Pin 3):** Serial Port Clock. Input, positive edge triggered. Clocks serial data in on rising edge.

**SEN (Pin 4):** Serial Port Enable (LTC6903 Only). Input, active LOW. Initiates serial transaction when brought LOW, finalizes transaction when brought HIGH after 16 clocks.

**ADR (Pin 4):** Serial Port Address (LTC6904 Only). Sets the I<sup>2</sup>C serial port address.

**CLK** (**Pin 5**): Auxiliary Clock Output. Frequency set by serial port.

**CLK (Pin 6):** Main Clock Output. Frequency set by serial port.

**OE (Pin 7):** Asynchronous Output Enable. CLK and  $\overline{\text{CLK}}$  are set LOW when this pin is LOW.

**V**<sup>+</sup> (**Pin 8**): Positive Power Supply. This supply must be kept free from noise and ripple. It should be bypassed directly to a ground plane with a quality  $0.1\mu F$  capacitor. Additional bypass may be necessary for operation at high frequency or under larger loads.

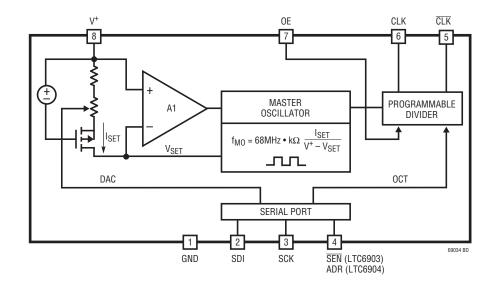

## **BLOCK DIAGRAM**

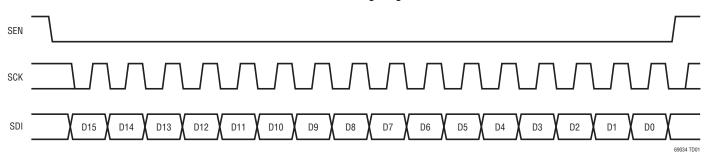

## TIMING DIAGRAMS

#### LTC6903 Timing Diagram

#### LTC6904 Timing Diagram

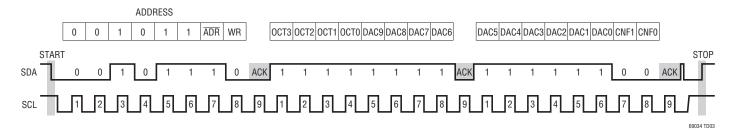

## LTC6904 Typical Input Waveform— Programming Frequency to 68MHz (ADR Pin Set LOW)

### THEORY OF OPERATION

The LTC6903/LTC6904 contain an internal feedback loop which controls a high frequency square wave VCO operating between 34MHz and 68MHz. The internal feedback loop frequency is set over an octave by a 10-bit resistor DAC. The VCO tracks the internal feedback loop frequency and the output frequency of the VCO is divided by one of sixteen possible powers of two.

Higher VCO frequencies and lower output divider settings can result in higher output jitter. Random jitter at the

lower frequency ranges is very low because of the high output divisor.

The higher frequency settings will display some deterministic jitter from coupling between the control loop and the output. This shows up in the frequency spectrum as spurs separated from the fundamental frequency by 1MHz to 2MHz.

### APPLICATIONS INFORMATION

#### **Frequency Setting Information**

The frequency output of the LTC6903/LTC6904 is determined by the following equation:

$$f = 2^{OCT} \bullet \frac{2078(Hz)}{\left(2 - \frac{DAC}{1024}\right)}$$

where DAC is the integer value from 0-1023 represented by the serial port register bits DAC[9:0] and OCT is the integer value from 0-15 represented by the serial port register bits OCT [3:0].

Use the following two steps to choose binary numbers "OCT" and "DAC" in order to set frequency "f":

1) Use Table 1 to Choose "OCT" or use the following formula, rounding down to the integer value less than or equal to the result.

$$OCT = 3.322 log \left(\frac{f}{1039}\right)$$

2) Choose "DAC" by the following formula, rounding DAC to the nearest integer:

DAC =

$$2048 - \frac{2078(Hz) \cdot 2^{(10+OCT)}}{f}$$

For example, to set a frequency of 6.5MHz, first look at Table 1 to find an OCT value. 6.5MHz falls between

4.25MHz and 8.5MHz yielding an OCT value of 12 or 1100. Substituting the OCT value of 12 and the desired frequency of 6.5MHz into the previous equation results in:

DAC =

$$2048 - \frac{2078(Hz) \cdot 2^{(10+12)}}{6.5e6(Hz)} = 707.113$$

Rounding 707.113 to the nearest integer yields a DAC value of 707 (or a 10-bit digital word of 1011000011.)

Table 1. Output Frequency Range vs OCT Settling (Frequency Resolution 0.001 • f)

| f≥       | f<       | OCT |

|----------|----------|-----|

| 34.05MHz | 68.03MHz | 15  |

| 17.02MHz | 34.01MHz | 14  |

| 8.511MHz | 17.01MHz | 13  |

| 4.256MHz | 8.503MHz | 12  |

| 2.128MHz | 4.252MHz | 11  |

| 1.064MHz | 2.126MHz | 10  |

| 532kHz   | 1063kHz  | 9   |

| 266kHz   | 531.4kHz | 8   |

| 133kHz   | 265.7kHz | 7   |

| 66.5kHz  | 132.9kHz | 6   |

| 33.25kHz | 66.43kHz | 5   |

| 16.62kHz | 33.22kHz | 4   |

| 8.312kHz | 16.61kHz | 3   |

| 4.156kHz | 8.304kHz | 2   |

| 2.078kHz | 4.152kHz | 1   |

| 1.039kHz | 2.076kHz | 0   |

69034fe

## APPLICATIONS INFORMATION

#### **Power-Up State**

When power is first applied to the LTC6903/LTC6904, all register values are automatically reset to 0. This results in an output frequency of 1.039kHz with both outputs active.

#### **Output Spectrum**

In most frequency ranges, the output of the LTC6903/LTC6904 is generated as a division of the higher internal clock frequency. This helps to minimize jitter and subharmonics at the output of the device. In the highest frequency ranges, the division ratio is reduced, which will result in greater cycle-to-cycle jitter as well as spurs at the internal sampling frequency. Because the internal control loop runs at 1MHz to 2MHz without regard to the output frequency, output spurs separated from the set frequency by 1MHz to 2MHz may be observed. These spurs are characteristically more than 30dB below the level of the set frequency.

#### **Frequency Settling**

When frequency settings change, the settling time and shape differ depending on which bits are changed. Changing only the OCT bits will result in an instantaneous change in frequency for OCT values below 10. Values of 10 and above may take up to  $100\mu s$  to settle due to the action of internal power conservation circuitry.

Changing the DAC bits will result in a smooth transition between the frequencies, occupying at most  $100\mu s$ , with little overshoot.

Changing both the OCT and DAC bits simultaneously may result in considerable excursion beyond the frequencies requested before settling.

It should be noted that changing the DAC bits at the lower frequency ranges will result in a seemingly instantaneous frequency change because the settling time depends on the internal loop frequency rather than the set frequency.

#### **Power Supply Bypass**

In order to obtain the accuracies represented in this data sheet, it is necessary to provide excellent bypass on the power supply. Adequate bypass is a  $1\mu F$  capacitor in parallel with a  $0.01\mu F$  capacitor connected within a few millimeters of the power supply leads.

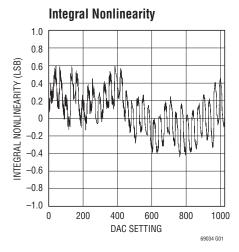

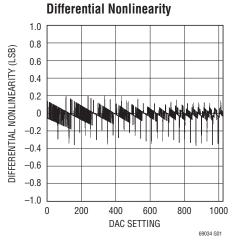

#### **Monotonicity and Linearity**

The DAC in the LTC6903/LTC6904 is guaranteed to be 10-bit monotonic. Nonlinearity of the DAC is less than 1%.

Additionally, the LTC6903/LTC6904 is guaranteed to be monotonic when switching between octaves with the OCT setting bits. For example, the frequency output with a DAC setting of "11111111111" and an OCT setting of "1100" will always be lower than the frequency output with a DAC setting of "0000000000" and an OCT setting of "1101". Linearity at these transition points is typically around 3 LSBs.

#### **Output Loading and Accuracy**

Improper loading of the outputs of the LTC6903/LTC6904, especially with poor power supply bypassing, will result in accuracy problems. At low frequencies, capacitive loading of the output is not a concern. At frequencies above 1MHz, attention should be paid to minimize the capacitive load on the CLK and  $\overline{\text{CLK}}$  pins.

The LTC6903/LTC6904 is designed to drive up to 5pF on each output with no degradation in accuracy. 5pF is equivalent to one to two HC series logic inputs. A standard 10x oscilloscope probe usually presents between 10pF and 15pF of capacitive load.

It is strongly suggested that a high speed buffer is used when driving more than one or two logic inputs, when driving a line more than 5 centimeters in length, or a capacitive load greater than 5pF.

## APPLICATIONS INFORMATION

#### **Output Control**

The CLK and  $\overline{\text{CLK}}$  outputs of the LTC6903/LTC6904 are individually controllable through the serial port as described in Table 2 below. The low power mode may also be accessed through these control bits. It is preferred that unused outputs be disabled in order to reduce power dissipation and improve accuracy.

Disabling an unused output will improve accuracy of operation at frequencies above 1MHz. An unused output running with no load typically degrades frequency accuracy up to 0.2% at 68MHz. An unused output running into a 5pF load typically degrades frequency accuracy up to 0.5% at 68MHz.

**Table 2. Output Configuration**

|      | 3    |               |            |  |  |  |  |  |

|------|------|---------------|------------|--|--|--|--|--|

| CNF1 | CNF0 | CLK           | CLK        |  |  |  |  |  |

| 0    | 0    | ON            | CLK + 180° |  |  |  |  |  |

| 0    | 1    | OFF           | ON         |  |  |  |  |  |

| 1    | 0    | ON            | OFF        |  |  |  |  |  |

| 1    | 1    | Powered-Down* |            |  |  |  |  |  |

<sup>\*</sup>Powered-Down: When in this mode, the chip is in a low power state and will require approximately 100µs to recover. This is not the same effect as the OE pin, which is fast, but uses more power supply current.

## Serial Port Bitmap (LTC6903/LTC6904)

(All serial port register bits default LOW at power up)

Table 3

| D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   |

|------|------|------|------|------|------|------|------|

| ОСТ3 | OCT2 | OCT1 | OCT0 | DAC9 | DAC8 | DAC7 | DAC6 |

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| DAC5 | DAC4 | DAC3 | DAC2 | DAC1 | DAC0 | CNF1 | CNF0 |

#### **Serial Port Register Description**

OCT[3:0] – Frequency Divider Setting. (See Frequency Setting Information Section)

DAC[9:0] - Master Oscillator Frequency Setting. (See Frequency Setting Information Section)

CNF[1:0] — Output Configuration. This controls outputs CLK and CLK according to Table 2.

#### LTC6903 SPI Compatible Interface

A serial data transfer is composed of sixteen (16) bits of data labeled D15 through D0. D15 is the first bit of data presented in each transaction. All serial port register bits are set LOW on power-up.

#### Writing Data (LTC6903 Only)

When the SEN line is brought LOW, serial data presented on the SDI input is clocked in on the rising edges of SCK until SEN is brought HIGH. On every eighth rising edge of SCK, the preceding 8-bits of data are clocked into the internal register. It is therefore possible to clock in only the 8 {D15 - D8} most significant bits of data rather than completing an entire transfer.

The serial data transfer starts with the most significant bit and ends with the least significant bit of the data, as shown in the Timing Diagrams section.

## APPLICATIONS INFORMATION

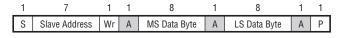

#### LTC6904 I<sup>2</sup>C Interface

The LTC6904 communicates with a host (master) using the standard I $^2$ C 2-wire interface. The Timing Diagram shows the timing relationship of the signals on the bus. The two bus lines, SDA and SCL, must be HIGH when the bus is not in use. External pull-up resistors or current sources, such as the LTC1694 SMBus accelerator, are required on these lines. If the I $^2$ C interface is not driven with a standard I $^2$ C compatible device, care must be taken to ensure that the SDA line is released during the ACK cycle to prevent bus contention.

The LTC6904 is a receive-only (slave) device. The master can communicate with the LTC6904 using the write word protocols as explained later.

#### The START and STOP Conditions

When the bus is not in use, both SCL and SDA must be HIGH. A bus master signals the beginning of a communication to a slave device by transmitting a START condition. A START condition is generated by transitioning SDA from HIGH to LOW while SCL is HIGH.

When the master has finished communicating with the slave, it issues a STOP condition. A STOP condition is generated by transitioning SDA from LOW to HIGH while SCL is HIGH. The bus is then free for communication with another SMBus device.

#### Acknowledge

The acknowledge signal is used for handshaking between the master and the slave. An acknowledge (active LOW) generated by the slave lets the master know that the latest byte of information was received. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The slave-receiver must pull down the SDA line during the acknowledge clock pulse so that it remains a stable LOW during the HIGH period of this clock pulse.

#### Write Word Protocol

The master initiates communication with the LTC6904 with a START condition and a 7-bit address followed by the write bit (Wr) = 0. The LTC6904 acknowledges and the master delivers the most significant data byte. Again the LTC6904 acknowledges and the data is latched into the most significant data byte input register. The master then delivers the least significant data byte. The LTC6904 acknowledges once more and latches the data into the least significant data byte input register. Lastly, the master terminates the communication with a STOP condition.

#### Slave Address

The LTC6904 can respond to one of two 7-bit addresses. The first 6 bits (MSBs) have been factory programmed to 001011. The address pin, ADR (Pin 4) is programmed by the user and determines the LSB of the slave address, as shown in the table below:

| ADR (Pin 4) | LTC6904 Address |

|-------------|-----------------|

| 0           | 0010111         |

| 1           | 0010110         |

#### Write Word Protocol Used by the LTC6904

S = START Condition, Wr = Write Bit = 0, A = Acknowledge, P = STOP Condition

69034 F0

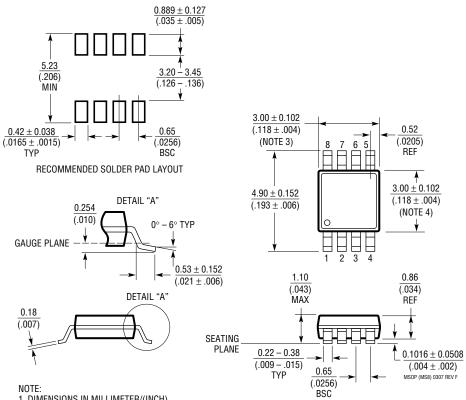

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### MS8 Package 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660 Rev F)

- 1. DIMENSIONS IN MILLIMETER/(INCH)

- 2. DRAWING NOT TO SCALE

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

## **REVISION HISTORY** (Revision history begins at Rev D)

| REV | DATE  | DESCRIPTION                                                                                                    | PAGE NUMBER |  |  |

|-----|-------|----------------------------------------------------------------------------------------------------------------|-------------|--|--|

| D   | 12/11 | orrected LTC6903 Timing Diagram.                                                                               |             |  |  |

|     |       | Corrected references to Frequency Setting Information section within Serial Port Register Description section. | 10          |  |  |

| Е   | 3/12  | Jpdated Absolute Maximum Ratings and Order Information.                                                        |             |  |  |

|     |       | Revised Notes 3 and 4 in Timing Characteristics.                                                               | 4           |  |  |

## TYPICAL APPLICATION

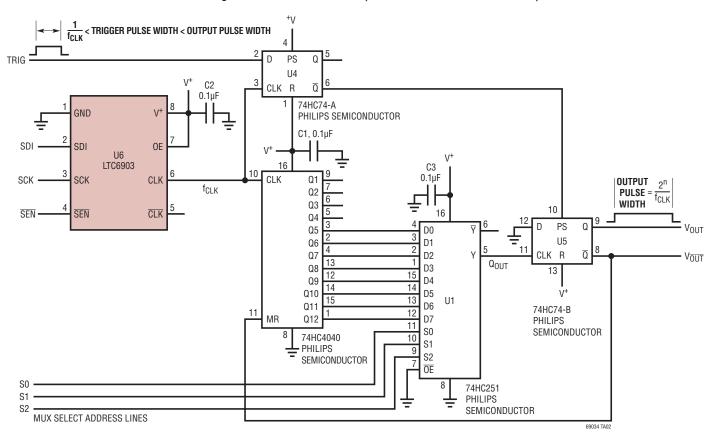

#### Wide Range Time Interval Generator (1.97 Seconds to 4 Microseconds)

|           | MUX INPUTS |    |    |                       |

|-----------|------------|----|----|-----------------------|

| <b>S2</b> | <b>S</b> 1 | SO | n  | Output<br>Pulse Width |

| 0         | 0          | 0  | 4  | 16/f <sub>CLK</sub>   |

| 1         | 0          | 0  | 5  | 32/f <sub>CLK</sub>   |

| 0         | 1          | 0  | 6  | 64/f <sub>CLK</sub>   |

| 1         | 1          | 0  | 7  | 128/f <sub>CLK</sub>  |

| 0         | 0          | 1  | 8  | 256/f <sub>CLK</sub>  |

| 1         | 0          | 1  | 9  | 512/f <sub>CLK</sub>  |

| 0         | 1          | 1  | 10 | 1024/f <sub>CLK</sub> |

| 1         | 1          | 1  | 11 | 2048/f <sub>CLK</sub> |

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                           | COMMENTS                                  |

|-------------|-------------------------------------------------------|-------------------------------------------|

| LTC1799     | 1kHz to 30MHz ThinSOT™ Oscillator                     | Single Output, Higher Frequency Operation |

| LTC6900     | 1kHz to 20MHz ThinSOT Oscillator                      | Single Output, Lower Power                |

| LTC6902     | Mulitphase Oscillator with Spread Spectrum Modulation | 1, 3 or 4-Phase Outputs                   |

LT 0312 REV E • PRINTED IN USA © LINEAR TECHNOLOGY CORPORATION 2003