## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                    |                                        |

|-----------------------------|----------------------------------------|

| Supply Voltage              | 6.5V                                   |

| Input Voltage               |                                        |

|                             | $-0.3V$ to $(V_{CC} + 0.3V)$           |

|                             | –18V to 18V                            |

| Logic Pins                  | $-0.3V$ to $(V_{CC} + 0.3V)$           |

| Output Voltage              |                                        |

| Transmitters                | $(V_{EE} - 0.3V)$ to $(V_{DD} + 0.3V)$ |

|                             | $-0.3V$ to $(V_{CC} + 0.3V)$           |

| Logic Pins                  | $-0.3V$ to $(V_{CC} + 0.3V)$           |

|                             | 10V to 0.3V                            |

| V <sub>DD</sub>             | 0.3V to 10V                            |

| Short-Circuit Duration      |                                        |

|                             | Indefinite                             |

| Receiver Output             | Indefinite                             |

| V <sub>EE</sub>             | 30 sec                                 |

| Operating Temperature Range | •                                      |

| LTC1343C                    | 0°C to 70°C                            |

|                             | 40°C to 85°C                           |

|                             | 65°C to 150°C                          |

| Lead Temperature (Solderin  | g, 10 sec) 300°C                       |

|                             |                                        |

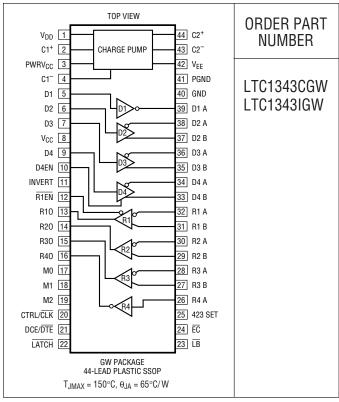

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ (Notes 2, 3)

| SYMBOL          | PARAMETER                                                                                | CONDITIONS                                                                                                                              |   | MIN          | TYP                      | MAX            | UNITS                |

|-----------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|--------------|--------------------------|----------------|----------------------|

| Supplies        |                                                                                          |                                                                                                                                         |   |              |                          |                |                      |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current (DCE Mode,<br>All Digital Pins = GND or V <sub>CC</sub> ) | V.10 Mode, No Load<br>V.10 Mode, Full Load<br>RS530, RS530-A, X.21 Modes, No Load                                                       | • |              | 12<br>80<br>80           | 150            | mA<br>mA<br>mA       |

|                 |                                                                                          | RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode, No Load                                                                             | • |              | 160<br>20                | 200            | mA<br>mA             |

|                 |                                                                                          | V.35 Mode, Full Load<br>V.28 Mode, No Load<br>V.28 Mode, Full Load<br>No-Cable Mode                                                     | • |              | 115<br>20<br>30<br>0.05  | 160<br>90<br>1 | mA<br>mA<br>mA<br>mA |

| $P_{D}$         | Internal Power Dissipation (DCE Mode,<br>All Digital Pins = GND or V <sub>CC</sub> )     | V.10 Mode, Full Load<br>RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode, Full Load<br>V.28 Mode, Full Load                           |   |              | 400<br>680<br>500<br>150 |                | mW<br>mW<br>mW<br>mW |

| V+              | Positive Charge Pump Output Voltage                                                      | Any Mode, No Load<br>V.28 Mode, with Load                                                                                               | • | 8.5<br>8.0   | 9.1<br>7.0               |                | V                    |

| V-              | Negative Charge Pump Output Voltage                                                      | V.28 Mode, Full Load                                                                                                                    | • | -7.8         | -8.4                     |                | V                    |

|                 |                                                                                          | $ \begin{array}{l} V.35 \; \text{Mode, Full Load} \\ -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C} \end{array} $ | • | -5.8<br>-5.5 | -6.7                     |                | V                    |

|                 |                                                                                          | V.10, RS530, RS530A, X.21 Modes, Full Load $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C}$                       | • | -5.0<br>-4.8 | -6.1                     |                | V                    |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ (Notes 2, 3)

| SYMBOL                          | PARAMETER                                                        | CONDITIONS                                                                                                                                                                                                                                                                              |   | MIN         | TYP       | MAX        | UNITS    |  |

|---------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|-----------|------------|----------|--|

| t <sub>r</sub>                  | Supply Rise Time                                                 | No-Cable Mode or Power-Up to Turn On                                                                                                                                                                                                                                                    |   |             | 2         |            | ms       |  |

| Logic Input                     | s and Outputs                                                    |                                                                                                                                                                                                                                                                                         |   |             |           |            |          |  |

| $V_{IH}$                        | Logic Input High Voltage                                         |                                                                                                                                                                                                                                                                                         | • | 2           |           |            | V        |  |

| $V_{IL}$                        | Logic Input Low Voltage                                          |                                                                                                                                                                                                                                                                                         | • |             |           | 0.8        | V        |  |

| I <sub>IN</sub>                 | Logic Input Current                                              |                                                                                                                                                                                                                                                                                         | • |             |           | ±10        | μΑ       |  |

| V <sub>OH</sub>                 | Output High Voltage                                              | $I_0 = -4mA$                                                                                                                                                                                                                                                                            | • | 3           | 4.5       |            | V        |  |

| $V_{OL}$                        | Output Low Voltage                                               | I <sub>0</sub> = 4mA                                                                                                                                                                                                                                                                    | • |             | 0.3       | 0.8        | V        |  |

| I <sub>OSR</sub>                | Output Short-Circuit Current                                     | $ \begin{array}{c} 0V \leq V_0 \leq V_{CC}, \ 0^{\circ}C \leq T_A \leq 70^{\circ}C \\ 0V \leq V_0 \leq V_{CC}, \ -40^{\circ}C \leq T_A \leq 85^{\circ}C \end{array} $                                                                                                                   | • | -60<br>-70  |           | 60<br>70   | mA<br>mA |  |

| I <sub>OZR</sub>                | Three-State Output Current                                       | $M0 = M1 = M2 = V_{CC}, 0V \le V_0 \le V_{CC}$                                                                                                                                                                                                                                          |   |             | ±1        |            | μΑ       |  |

| V.11 Driver                     |                                                                  |                                                                                                                                                                                                                                                                                         |   |             |           |            |          |  |

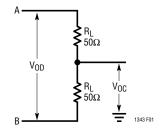

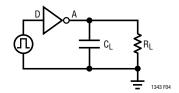

| V <sub>OD</sub>                 | Differential Output Voltage                                      | Open Circuit, $R_L$ = 1.95k $R_L$ = 50 $\Omega$ (Figure 1), $V_{0D}$ at 50 $\Omega$ > 1/2 $V_{0D}$ at $R_L$ = 1.95k                                                                                                                                                                     | • | ±2          |           | ±6         | V        |  |

| $\Delta V_{0D}$                 | Change in Magnitude of Differential<br>Output Voltage            | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                                                                                                             | • |             |           | 0.2        | V        |  |

| V <sub>OC</sub>                 | Common Mode Output Voltage                                       | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                                                                                                             | • |             |           | 3.0        | V        |  |

| ΔV <sub>OC</sub>                | Change in Magnitude of Common Mode<br>Output Voltage             | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                                                                                                             | • |             |           | 0.2        | V        |  |

| I <sub>SS</sub>                 | Short-Circuit Current                                            | $-0.25V \le V_0 \le 0.25V$ , Power Off or No-Cable Mode or Driver Disabled                                                                                                                                                                                                              |   |             |           | ±150       | mA       |  |

| I <sub>OZ</sub>                 | Output Leakage Current                                           | $-0.25V \le V_0 \le 0.25V$ , Power Off or No-Cable Mode or Driver Disabled                                                                                                                                                                                                              | • |             | ±0.01     | ±100       | μА       |  |

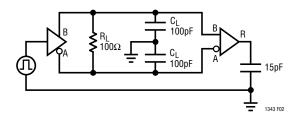

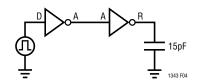

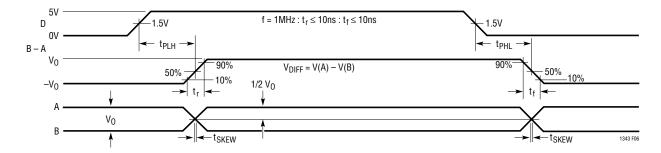

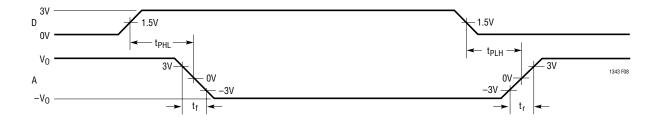

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 2, 6)                                                                                                                                                                                                                                                                          | • | 4           | 13        | 25         | ns       |  |

| t <sub>PLH</sub>                | Input to Output                                                  | (Figures 2, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 2, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                                                          | • | 25<br>25    | 55<br>55  | 80<br>90   | ns<br>ns |  |

| t <sub>PHL</sub>                | Input to Output                                                  | (Figures 2, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 2, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                                                          | • | 25<br>25    | 55<br>55  | 80<br>90   | ns<br>ns |  |

| Δt                              | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 2, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 2, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                                                          | • | 0<br>0      | 3<br>3    | 17<br>25   | ns<br>ns |  |

| t <sub>SKEW</sub>               | Output to Output Skew                                            | (Figures 2, 6)                                                                                                                                                                                                                                                                          |   |             | 3         |            | ns       |  |

| V.11 Receiv                     | ver                                                              |                                                                                                                                                                                                                                                                                         |   |             |           |            |          |  |

| $V_{TH}$                        | Input Threshold Voltage                                          | $\begin{array}{l} -7\text{V} \leq \text{V}_{CM} \leq 7\text{V}, \ 0^{\circ}\text{C} \leq \text{T}_{A} \leq 70^{\circ}\text{C} \\ -7\text{V} \leq \text{V}_{CM} \leq 7\text{V}, \ -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C} \end{array}$                             | • | -0.2 $-0.3$ |           | 0.2<br>0.3 | V        |  |

| $\Delta V_{TH}$                 | Input Hysteresis                                                 | $ \begin{array}{l} -7\text{V} \leq \text{V}_{\text{CM}} \leq 7\text{V},  0^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 70^{\circ}\text{C} \\ -7\text{V} \leq \text{V}_{\text{CM}} \leq 7\text{V},  -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C} \end{array} $ | • |             | 15        | 40<br>60   | mV<br>mV |  |

| I <sub>IN</sub>                 | Input Current (A, B)                                             | $-10V \le V_{A, B} \le 10V$                                                                                                                                                                                                                                                             | • |             |           | ±0.50      | mA       |  |

| R <sub>IN</sub>                 | Input Impedance                                                  | $-10V \le V_{A, B} \le 10V$                                                                                                                                                                                                                                                             | • | 20          | 32        |            | kΩ       |  |

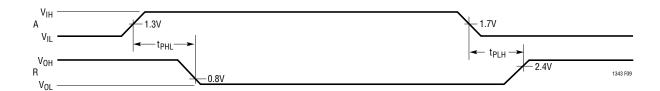

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 2, 7)                                                                                                                                                                                                                                                                          |   |             | 15        |            | ns       |  |

| t <sub>PLH</sub>                | Input to Output                                                  | (Figures 2, 7), CTRL = GND, $0^{\circ}C \le T_A \le 70^{\circ}C$<br>CTRL = $V_{CC}$ , $0^{\circ}C \le T_A \le 70^{\circ}C$                                                                                                                                                              | • | 35          | 80<br>400 | 115        | ns<br>ns |  |

|                                 |                                                                  | $ \begin{array}{c} \text{(Figures 2, 7), CTRL = GND, } -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C} \\ \text{CTRL = V}_{CC}, -40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C} \\ \end{array} $                                                            | • | 25          | 80<br>400 | 130        | ns<br>ns |  |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ (Notes 2, 3)

| SYMBOL                          | PARAMETER                                                        | CONDITIONS                                                                                                                                                                                                                                     |   | MIN          | TYP        | MAX          | UNITS    |

|---------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|------------|--------------|----------|

| t <sub>PHL</sub>                | Input to Output                                                  | (Figures 2, 7), CTRL = GND, $0^{\circ}C \le T_A \le 70^{\circ}C$<br>CTRL = $V_{CC}$ , $0^{\circ}C \le T_A \le 70^{\circ}C$                                                                                                                     |   | 35           | 80<br>400  | 115          | ns<br>ns |

|                                 |                                                                  | $ \begin{array}{l} \text{(Figures 2, 7), CTRL = GND, } -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C} \\ \text{CTRL = V}_{\text{CC}}, -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85^{\circ}\text{C} \end{array} $ | • | 25           | 80<br>400  | 130          | ns<br>ns |

| Δt                              | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 2, 7), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 2, 7), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • | 0            | 5<br>5     | 17<br>25     | ns<br>ns |

| V.35 Drive                      | r                                                                |                                                                                                                                                                                                                                                |   |              |            |              |          |

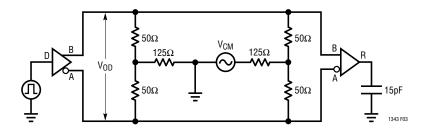

| V <sub>OD</sub>                 | Differential Output Voltage                                      | Open Circuit With Load, $-4.0V \le V_{CM} = 4.0V$ (Figure 3)                                                                                                                                                                                   | • | ±0.44        | ±0.55      | 6.0<br>±0.66 | V<br>V   |

| I <sub>OH</sub>                 | Transmitter Output High Current                                  | V <sub>A, B</sub> = 0V                                                                                                                                                                                                                         | • | -12.6        | -11        | -9.4         | mA       |

| I <sub>OL</sub>                 | Transmitter Output Low Current                                   | $V_{A, B} = 0V$                                                                                                                                                                                                                                | • | 9.4          | 11         | 12.6         | mA       |

| $I_{OZ}$                        | Transmitter Output Leakage Current                               | $-0.25V \le V_{A, B} \le 0.25V$                                                                                                                                                                                                                | • |              | $\pm 0.01$ | ±100         | μΑ       |

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 3, 6)                                                                                                                                                                                                                                 |   |              | 5          |              | ns       |

| t <sub>PLH</sub>                | Input to Output                                                  | (Figures 3, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • | 25<br>25     | 45<br>45   | 75<br>90     | ns<br>ns |

| t <sub>PHL</sub>                | Input to Output                                                  | (Figures 3, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • | 25<br>25     | 45<br>45   | 75<br>90     | ns<br>ns |

| Δt                              | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 3, 6), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 6), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • | 0<br>0       | 5<br>5     | 17<br>25     | ns<br>ns |

| t <sub>SKEW</sub>               | Output to Output Skew                                            | (Figures 3, 6)                                                                                                                                                                                                                                 |   |              | 4          |              | ns       |

| V.35 Recei                      | ver                                                              |                                                                                                                                                                                                                                                |   |              |            |              |          |

| $\overline{V_{TH}}$             | Differential Receiver Input<br>Threshold Voltage                 | $-2V \le (V_A + V_B)/2 \le 2V$ (Figure 3)                                                                                                                                                                                                      | • | -0.2         |            | 0.2          | V        |

| $\Delta V_{TH}$                 | Receiver Input Hysteresis                                        | $-2V \le (V_A + V_B)/2 \le 2V$ (Figure 3)                                                                                                                                                                                                      | • |              | 11         | 40           | mV       |

| I <sub>IN</sub>                 | Receiver Input Current (A, B)                                    | $-10V \le V_{A, B} \le 10V$                                                                                                                                                                                                                    | • |              |            | ±0.50        | mA       |

| R <sub>IN</sub>                 | Receiver Input Impedance                                         | $-10V \le V_{A, B} \le 10V$                                                                                                                                                                                                                    | • | 20           | 32         |              | kΩ       |

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 3, 7)                                                                                                                                                                                                                                 |   |              | 15         |              | ns       |

| t <sub>PLH</sub>                | Input to Output                                                  | (Figures 3, 7), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 7), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • |              | 80<br>80   | 115<br>130   | ns<br>ns |

| t <sub>PHL</sub>                | Input to Output                                                  | (Figures 3, 7), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 7), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • |              | 100<br>100 | 115<br>130   | ns<br>ns |

| Δt                              | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 3, 7), $0^{\circ}C \le T_A \le 70^{\circ}C$<br>(Figures 3, 7), $-40^{\circ}C \le T_A \le 85^{\circ}C$                                                                                                                                 | • |              | 4 4        | 17<br>25     | ns<br>ns |

| V.10 Drive                      | r                                                                |                                                                                                                                                                                                                                                |   |              |            |              |          |

| V <sub>0</sub>                  | Output Voltage                                                   | Open Circuit, $R_L=3.9k$ $R_L=450\Omega$ (Figure 4) $V_0$ at $450\Omega > 0.9$ $V_0$ at $R_L=3.9k$ Driver 1 Only                                                                                                                               |   | ±4.0<br>±3.6 |            | ±6.0         | V        |

| I <sub>SS</sub>                 | Short-Circuit Current                                            | V <sub>0</sub> = GND; EIA-530, X.21, EIA-530-A Modes                                                                                                                                                                                           |   |              |            | ±150         | mA       |

| I <sub>OZ</sub>                 | Output Leakage Current                                           | $-0.25V \le V_0 \le 0.25V$ , Power Off or No-Cable Mode or Driver Disabled                                                                                                                                                                     | • |              | ±0.1       | ±100         | μА       |

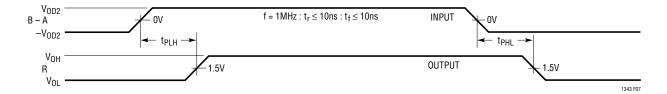

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 4, 8), $R_L$ = 450 $\Omega$ , $C_L$ = 100pF $R_{423SET}$ = 100k                                                                                                                                                                       |   |              | 4          |              | μS       |

| t <sub>PLH</sub>                | Input to Output                                                  | (Figures 4, 8), $R_L = 450\Omega$ , $C_L = 100pF$<br>$R_{423SET} = 100k$                                                                                                                                                                       |   |              | 8          |              | μS       |

| t <sub>PHL</sub>                | Input to Output                                                  | (Figures 4, 8), $R_L = 450\Omega$ , $C_L = 100pF$<br>$R_{423SET} = 100k$                                                                                                                                                                       |   |              | 8          |              | μS       |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ (Notes 2, 3)

| SYMBOL                          | PARAMETER                        | CONDITIONS                                                                                                                                   | CONDITIONS |              | TYP        | MAX        | UNITS    |

|---------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------|------------|----------|

| V.10 Recei                      | iver                             | ·                                                                                                                                            |            |              |            |            |          |

| $V_{TH}$                        | Receiver Input Threshold Voltage | $ \begin{array}{c} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -7V \leq V_{CM} \leq 7V, -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array} $ | •          | -0.2<br>-0.3 |            | 0.2<br>0.3 | V        |

| $\Delta V_{TH}$                 | Receiver Input Hysteresis        |                                                                                                                                              | •          |              | 11         | 50         | mV       |

| I <sub>IN</sub>                 | Receiver Input Current           | $-10V \le V_A \le 10V$                                                                                                                       | •          |              |            | ±0.50      | mA       |

| R <sub>IN</sub>                 | Receiver Input Impedance         | $-10V \le V_A \le 10V$                                                                                                                       | •          | 20           | 30         |            | kΩ       |

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                | (Figures 5, 9)                                                                                                                               |            |              | 15         |            | ns       |

| t <sub>PLH</sub>                | Input to Output                  | (Figures 5, 9)                                                                                                                               |            |              | 350        |            | ns       |

| t <sub>PHL</sub>                | Input to Output                  | (Figures 5, 9)                                                                                                                               |            |              | 350        |            | ns       |

| V.28 Drive                      | r                                |                                                                                                                                              |            |              |            |            |          |

| $V_0$                           | Output Voltage                   | Open Circuit<br>R <sub>L</sub> = 3k (Figure 4)                                                                                               | •          | ±5           | 7.6        | ±10        | V        |

| I <sub>SS</sub>                 | Short-Circuit Current            | $V_0 = GND$                                                                                                                                  | •          |              |            | ±150       | mA       |

| I <sub>OZ</sub>                 | Output Leakage Current           | $-0.25V \le V_0 \le 0.25V$ , Power Off or No-Cable Mode or Driver Disabled                                                                   | •          |              | ±0.01      | ±100       | μА       |

| SR                              | Slew Rate                        | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                                                                                  | •          | 4.0          |            | 30.0       | V/µs     |

| t <sub>PLH</sub>                | Input to Output                  | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                                                                                  | •          |              | 1.6        | 2.5        | μS       |

| t <sub>PHL</sub>                | Input to Output                  | (Figures 4, 8), $R_L = 3k$ , $C_L = 2500pF$                                                                                                  | •          |              | 1.6        | 2.5        | μS       |

| V.28 Recei                      | iver                             |                                                                                                                                              |            |              |            |            |          |

| $V_{THL}$                       | Input Low Threshold Voltage      |                                                                                                                                              | •          |              | 1.4        | 0.8        | V        |

| $V_{TLH}$                       | Input High Threshold Voltage     |                                                                                                                                              | •          | 2.0          | 1.4        |            | V        |

| $\Delta V_{TH}$                 | Receiver Input Hysteresis        |                                                                                                                                              | •          | 0.1          | 0.4        | 1.0        | V        |

| R <sub>IN</sub>                 | Receiver Input Impedance         | $-15V \le V_A \le 15V$                                                                                                                       | •          | 3            | 5          | 7          | kΩ       |

| $t_r$ , $t_f$                   | Rise or Fall Time                | (Figures 5, 9)                                                                                                                               |            |              | 15         |            | ns       |

| t <sub>PLH</sub>                | Input to Output                  | (Figures 5, 9), CTRL = $0V$<br>CTRL = $V_{CC}$                                                                                               | •          |              | 110<br>330 | 800        | ns<br>ns |

| t <sub>PHL</sub>                | Input to Output                  | (Figures 5, 9), CTRL = $0V$<br>CTRL = $V_{CC}$                                                                                               | •          |              | 170<br>480 | 800        | ns<br>ns |

**Note 1:** Absolute Maximum Ratings are those beyond which the safety of a device may be impaired.

**Note 2:** All currents into device pins are positive; all currents out of device are negative. All voltages are referenced to device ground unless otherwise specified.

**Note 3:** All typicals are given for  $V_{CC}$  = 5V, C1 = C2 =  $C_{VCC}$  =  $C_{VDD}$  = 1 $\mu$ F,  $C_{VEE}$  = 3.3 $\mu$ F tantalum capacitors and  $T_A$  = 25°C.

## PIN FUNCTIONS

$V_{DD}$  (Pin 1): Generated Positive Supply Voltage for RS232. Connect a  $1\mu F$  capacitor to ground.

C1+ (Pin 2): Capacitor C1 Positive Terminal. Connect a  $1\mu F$  capacitor between C1+ and C1-.

**PWRV**<sub>CC</sub> (**Pin 3**): Positive Supply for the Charge Pump.  $4.75V \le PWRV_{CC} \le 5.25V$ . Tie to  $V_{CC}$  (**Pin 8**) and bypass with a  $1\mu F$  capacitor to ground.

C1<sup>-</sup> (Pin 4): Capacitor C1 Negative Terminal.

**D1** (Pin 5): TTL Level Driver 1 Input.

D2 (Pin 6): TTL Level Driver 2 Input.

**D3** (Pin 7): TTL Level Driver 3 Input. Becomes a CMOS level output when the chip is in the echoed clock mode  $(\overline{EC} = 0V)$ .

#### PIN FUNCTIONS

**V<sub>CC</sub> (Pin 8):** Positive Supply for the Transceivers.  $4.75V \le V_{CC} \le 5.25V$ . Tie to PWRV<sub>CC</sub> (Pin 3).

**D4 (Pin 9):** TTL Level Driver 4 Input.

**D4EN (Pin 10):** TTL Level Enable Input for Driver 4. When high, driver 4 outputs are enabled. When low, driver 4 outputs are forced into a high impedance state. D4EN is not affected by the  $\overline{\text{LATCH}}$  pin.

**INVERT (Pin 11):** TTL Level Signal Invert Input. When high, an extra inverter will be added to the driver 4 and receiver 1 signal path. The data stream will change polarity, i.e., a 1 becomes 0 and a 0 becomes a 1. When the pin is low the data flows through with no polarity change. INVERT is not affected by the LATCH pin.

R1EN (Pin 12): Logic Level Enable Input for Receiver 1. When low, receiver 1 output is enabled. When high, receiver 1 output is forced into a high impedance state.

R10 (Pin 13): CMOS Level Receiver 1 Output.

R20 (Pin 14): CMOS Level Receiver 2 Output.

R30 (Pin 15): CMOS Level Receiver 3 Output.

R40 (Pin 16): CMOS Level Receiver 4 Output.

**M0 (Pin 17):** TTL Level Mode Select Input 0. The data on M0 is latched when LATCH is high.

M1 (Pin 18): TTL Level Mode Select Input 1. The data on M1 is latched when LATCH is high.

**M2** (**Pin 19**): TTL Level Mode Select Input 2. The data on M2 is latched when LATCH is high.

CTRL/CLK (Pin 20): TTL Level Mode Select Input. When the pin is low the chip will be configured for clock and data signals. When the pin is high the chip will be configured for control signals. The data on CTRL/CLK is latched when LATCH is high.

**DCE/DTE** (**Pin 21**): TTL Level Mode Select Input. When high, the DCE mode is selected. When low the DTE mode is selected. The data on DCE/DTE is latched when LATCH is high.

LATCH (Pin 22): TTL Level Logic Signal Latch Input. When low the input buffers on M0, M1, M2, CTRL/CLK, DCE/DTE, LB and EC are transparent. When LATCH is pulled high the data on the logic pins is latched into their

respective input buffers. The data latch allows the logic lines to be shared between multiple I/O ports.

**LB (Pin 23):** TTL Level Loop-Back Select Input. When low the chip enters the loop-back configuration and is configured for normal operation when  $\overline{LB}$  is high. The data on  $\overline{LB}$  is latched when  $\overline{LATCH}$  is high.

**EC** (**Pin 24**): TTL Level Echoed Clock Select Input. When low the part enters the echoed clock configuration and is configured for normal operation when EC is high. The data on EC is latched when LATCH is high.

**423 SET (Pin 25):** Analog Input Pin for the RS423 Driver Output Rise and Fall Time Set Resistor. Connect the resistor from the pin to ground.

R4 A (Pin 26): Receiver 4 Inverting Input.

R3 B (Pin 27): Receiver 3 Noninverting Input.

R3 A (Pin 28): Receiver 3 Inverting Input.

R2 B (Pin 29): Receiver 2 Noninverting Input.

R2 A (Pin 30): Receiver 2 Inverting Input.

R1 B (Pin 31): Receiver 1 Noninverting Input.

R1 A (Pin 32): Receiver 1 Inverting Input.

D4 B (Pin 33): Driver 4 Noninverting Output.

**D4 A (Pin 34):** Driver 4 Inverting Output.

D3 B (Pin 35): Driver 3 Noninverting Output.

D3 A (Pin 36): Driver 3 Inverting Output.

D2 B (Pin 37): Driver 2 Noninverting Output.

D2 A (Pin 38): Driver 2 Inverting Output.

D1 A (Pin 39): Driver 1 Inverting Output.

**GND (Pin 40):** Signal Ground. Connect to PGND (Pin 41).

**PGND (Pin 41):** Charge Pump Power Ground. Connect to the GND (Pin 40).

$V_{EE}$  (Pin 42): Generated Negative Supply Voltage. Connect a 3.3 $\mu$ F capacitor to ground.

**C2**<sup>-</sup> (**Pin 43**): Capacitor C2 Negative Terminal. Connect a  $1\mu F$  capacitor between C2<sup>+</sup> and C2<sup>-</sup>.

**C2**<sup>+</sup> (**Pin 44**): Capacitor C2 Positive Terminal. Connect a  $1\mu F$  capacitor between C2<sup>+</sup> and C2<sup>-</sup>.

## **TEST CIRCUITS**

Figure 1. RS422 Driver Test Circuit

Figure 2. RS422 Driver/Receiver AC Test Circuit

Figure 3. V.35 Driver/Receiver Test Circuit

Figure 4. V.10/V.28 Driver Test Circuit

Figure 5. V.10/V.28 Receiver Test Circuit

## **MODE SELECTION**

| LTC1343 MODE NAME        | M2 | M1 | МО | CTRL/CLK | D1   | D2   | D3   | D4   | R1   | R2   | R3   | R4   |

|--------------------------|----|----|----|----------|------|------|------|------|------|------|------|------|

| V.10, RS423              | 0  | 0  | 0  | Х        | V.10 |

| EIA-530-A Clock and Data | 0  | 0  | 1  | 0        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| EIA-530-A Control        | 0  | 0  | 1  | 1        | V.10 | V.11 | V.10 | V.11 | V.11 | V.10 | V.11 | V.10 |

| Reserved                 | 0  | 1  | 0  | Х        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| X.21                     | 0  | 1  | 1  | Х        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| V.35 Clock and Data      | 1  | 0  | 0  | 0        | V.28 | V.35 | V.35 | V.35 | V.35 | V.35 | V.35 | V.28 |

| V.35 Control             | 1  | 0  | 0  | 1        | V.28 |

| EIA-530, RS449, V.36     | 1  | 0  | 1  | Х        | V.10 | V.11 | V.11 | V.11 | V.11 | V.11 | V.11 | V.10 |

| V.28, RS232              | 1  | 1  | 0  | Х        | V.28 |

| No Cable                 | 1  | 1  | 1  | Х        | Z    | Z    | Z    | Z    | Z    | Z    | Z    | Z    |

## **SWITCHING TIME WAVEFORMS**

Figure 6. V.11, V.35 Driver Propagation Delays

Figure 7. V.11, V.35 Receiver Propagation Delays

Figure 8. V.10, V.28 Driver Propagation Delays

Figure 9. V.10, V.28 Receiver Propagation Delays

#### **Overview**

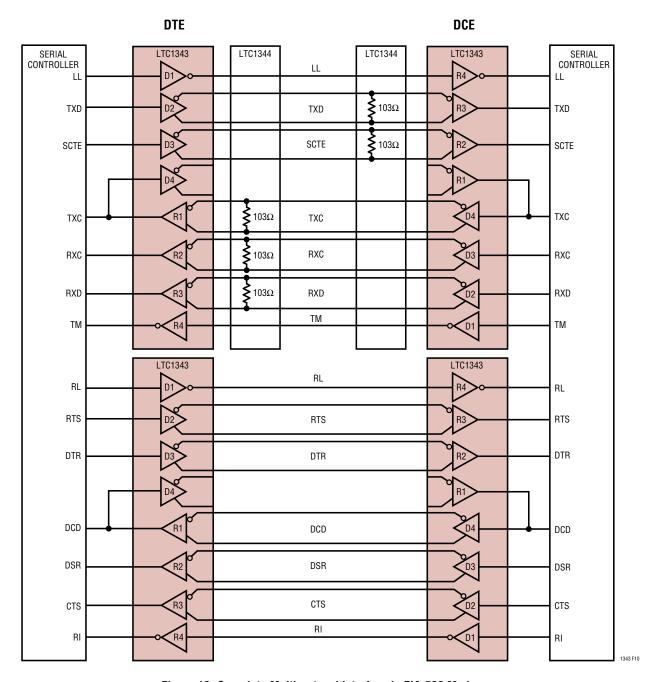

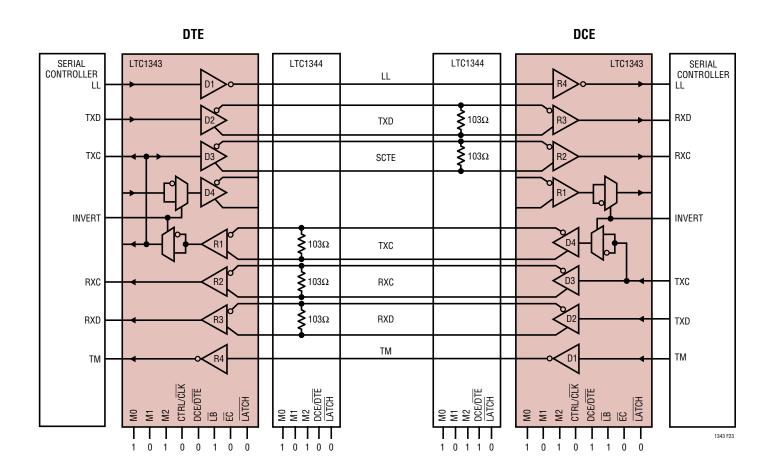

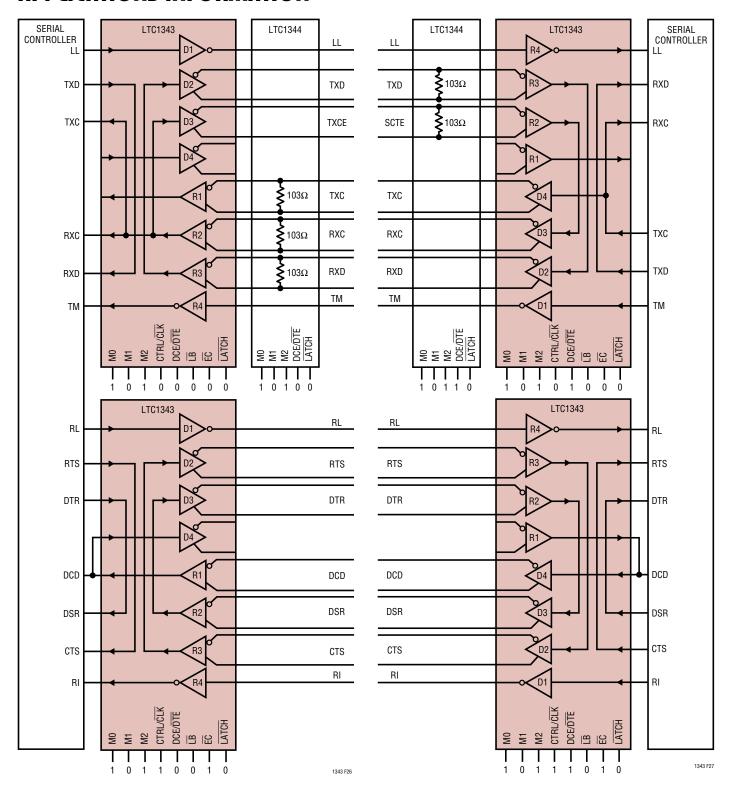

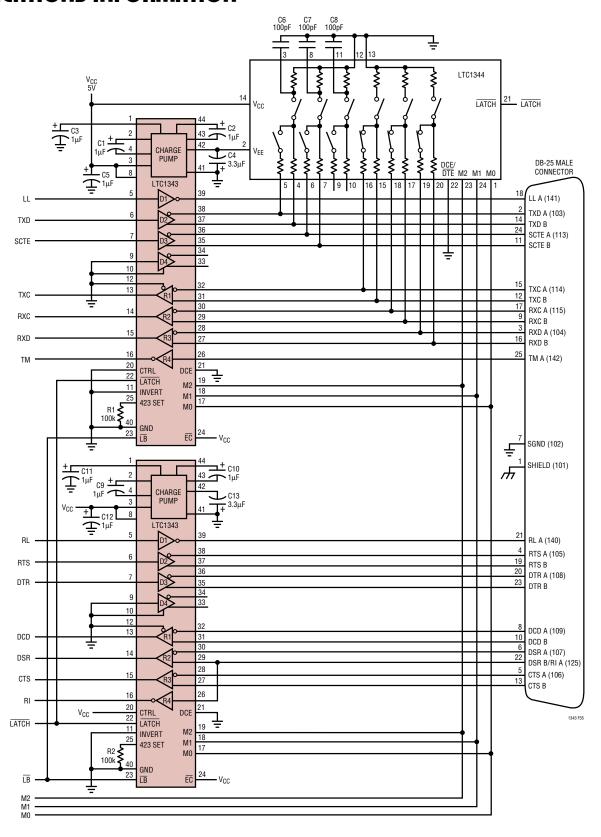

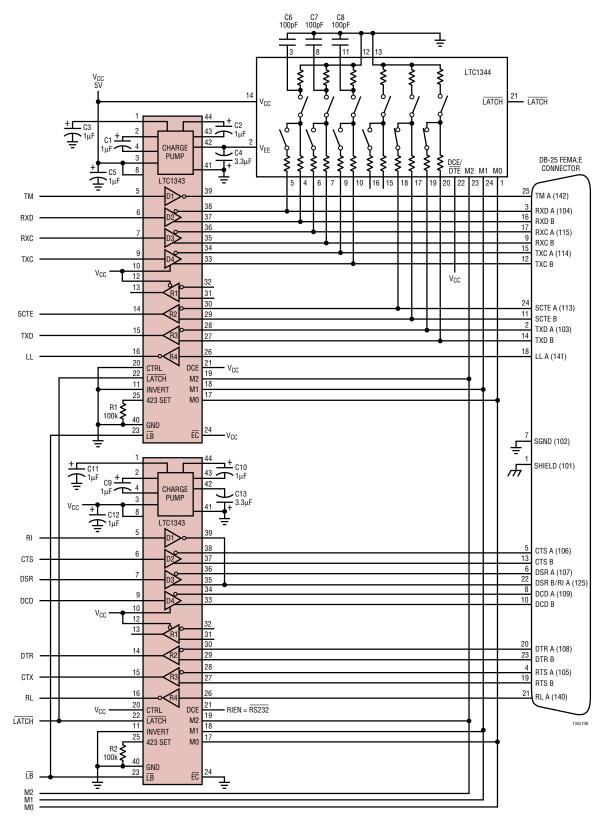

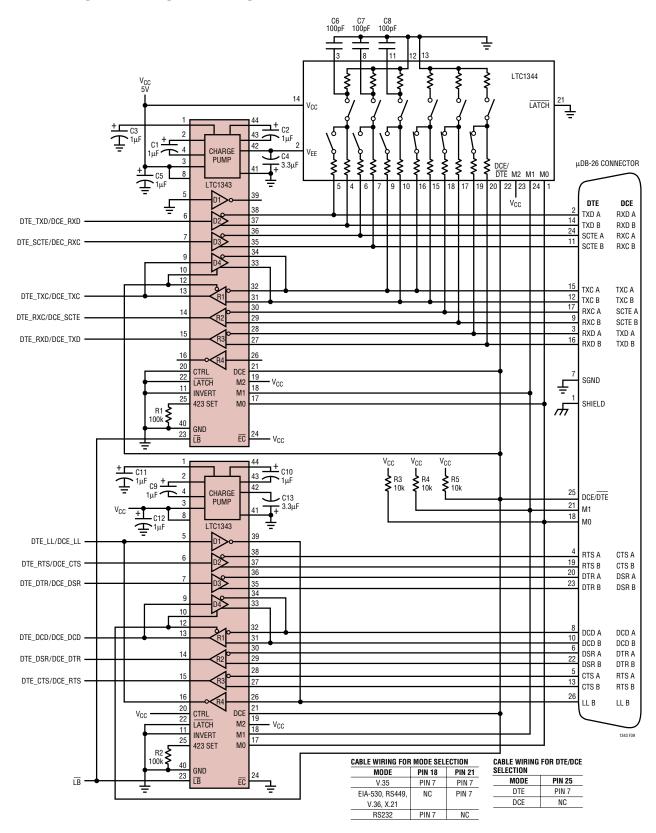

The LTC1343 is a 4-driver/4-receiver multiprotocol transceiver that operates from a single 5V supply. Two LTC1343s form the core of a complete software-selectable DTE or DCE interface port that supports the RS232, RS449, EIA-530, EIA-530-A, V.35, V.36 or X.21 protocols. Cable termination may be implemented using the LTC1344

software-selectable cable termination chip or by using existing discrete designs.

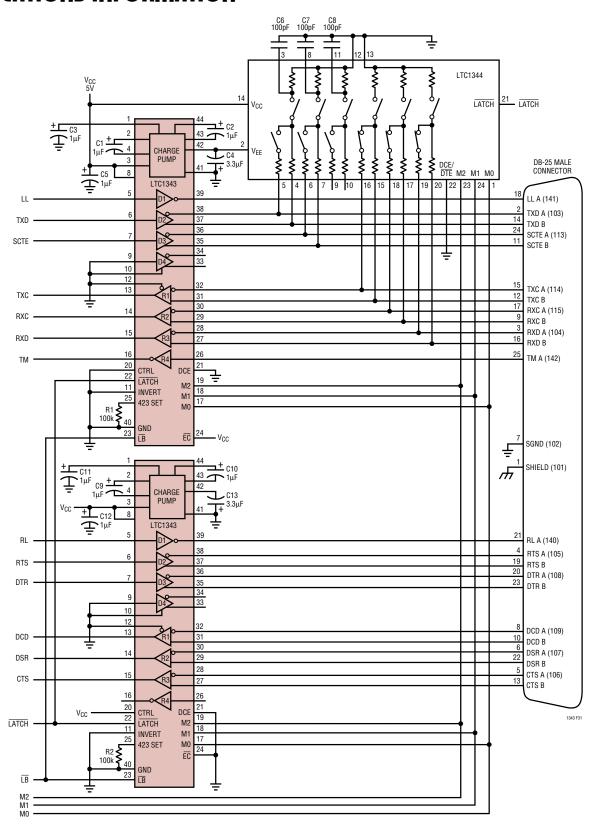

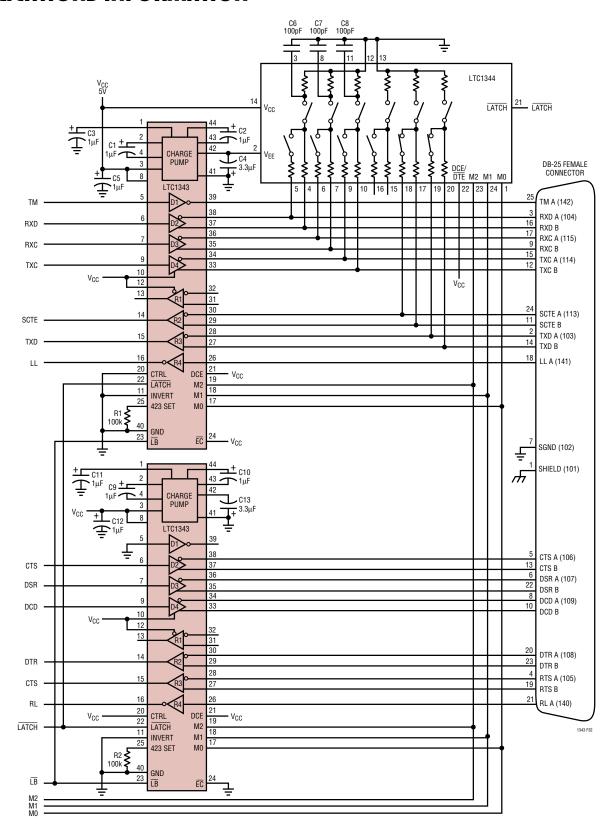

A complete DCE-to-DTE interface operating in EIA-530 mode is shown in Figure 10. The first LTC1343 of each port is used to generate the clock and data signals along with LL (Local Loop-back) and TM (Test Mode). The second LTC1343 is used to generate the control signals along with

Figure 10. Complete Multiprotocol Interface in EIA-530 Mode

RL (Remote Loop-back) and RI (Ring Indicate). The LTC1344 cable termination chip is used only for the clock and data signals because they must support V.35 cable termination. The control signals do not need any external resistors.

#### **Mode Selection**

The interface protocol is selected using the mode select pins M0, M1, M2 and CTRL/CLK (see the Mode Selection table). The CTRL/CLK pin should be pulled high if the LTC1343 is being used to generate control signals and pulled low if used to generate clock and data signals.

For example, if the port is configured as a V.35 interface, the mode selection pins should be M2 = 1, M1 = 0, M0 = 0. For the control signals, CTRL/ $\overline{\text{CLK}}$  = 1 and the drivers and receivers will operate in RS232 (V.28) electrical mode. For the clock and data signals, CTRL/ $\overline{\text{CLK}}$  = 0 and the drivers and receivers will operate in V.35 electrical mode, except for the single-ended driver and receiver which will operate in the RS232 (V.28) electrical mode. The DCE/ $\overline{\text{DTE}}$  pin

will configure the port for DCE mode when high, and DTE when low.

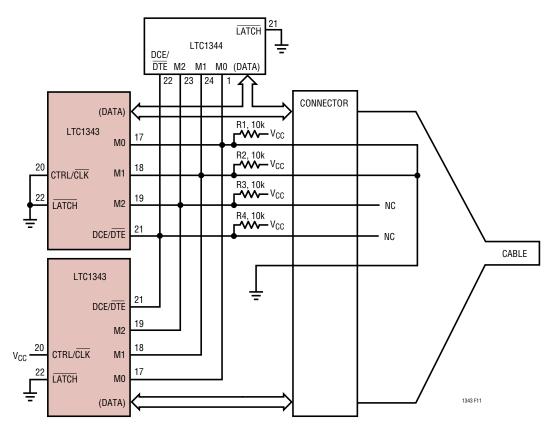

The interface protocol may be selected simply by plugging the appropriate interface cable into the connector. The mode pins are routed to the connector and are left unconnected (1) or wired to ground (0) in the cable as shown in Figure 11.

The pull-up resistors R1 through R4 will ensure a binary 1 when a pin is left unconnected and that the two LTC1343s and the LTC1344 enter the no-cable mode when the cable is removed. In the no-cable mode the LTC1343 supply current drops to less than 200 $\mu$ A and all LTC1343 driver outputs and LTC1344 resistive terminations are forced into a high impedance state. Note that the data latch pin, LATCH, is shorted to ground for all chips.

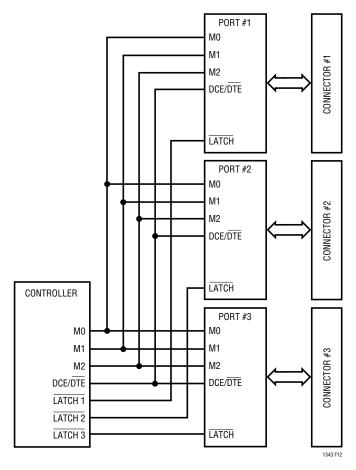

The interface protocol may also be selected by the serial controller or host microprocessor as shown in Figure 12.

The mode selection pins M0, M1, M2 and DCE/DTE can be shared between multiple interface ports, while each port

Figure 11: Single Port DCE/V.35 Mode Selection in the Cable

Figure 12: Mode Selection by the Controller

has a unique data latch signal which acts as a write enable. When the  $\overline{LATCH}$  pin is low the buffers on the M0, M1, M2, CTRL/ $\overline{CLK}$ ,  $\overline{DCE/DTE}$ ,  $\overline{LB}$  and  $\overline{EC}$  pins are transparent. When the  $\overline{LATCH}$  pin is pulled high the buffers latch the data and changes on the input pins will no longer affect the chip.

The mode selection may also be accomplished by using jumpers to connect the mode pins to ground or  $V_{CC}$ .

#### **Cable Termination**

Traditional implementations have included switching resistors with expensive relays, or requiring the user to change termination modules every time the interface standard has changed. Custom cables have been used with the termination in the cable head, or separate terminations are built on the board and a custom cable routes the signals to the appropriate termination. Switching the terminations with FETs is difficult because the FETs must

remain off even though the signal voltage is beyond the supply voltage for the FET drivers or the power is off.

Using the LTC1344 along with the LTC1343 solves the cable termination switching problem. Via software control, the LTC1344 provides termination for the V.10 (RS423), V.11 (RS422), V.28 (RS232) and V.35 electrical protocols.

#### V.10 (RS423) Interface

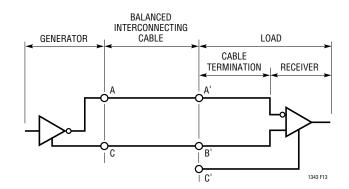

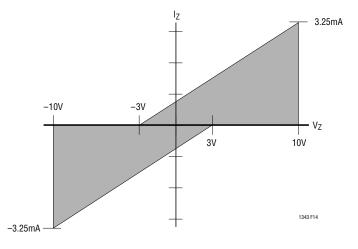

A typical V.10 unbalanced interface is shown in Figure 13. A V.10 single-ended generator output A with ground C is connected to a differential receiver with inputs A' connected to A, and input B' connected to the signal return ground C. The receiver's ground C' is separate from the signal return. Usually, no cable termination is required for V.10 interfaces, but the receiver inputs must be compliant with the impedance curve shown in Figure 14.

Figure 13. Typical V.10 Interface

Figure 14. V.10 Receiver Input Impedance

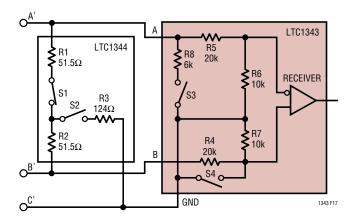

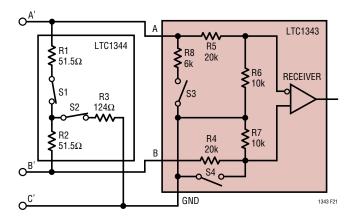

The V.10 receiver configuration in the LTC1343 and LTC1344 is shown in Figure 15. In V.10 mode switches S1 and S2 inside the LTC1344 and S3 inside the LTC1343 are turned off. Switch S4 inside the LTC1343 shorts the noninverting receiver input to ground so the B input at the connector can be left floating. The cable termination is then the 30k input impedance to ground of the LTC1343 V.10 receiver.

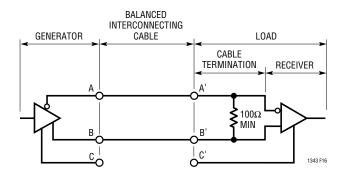

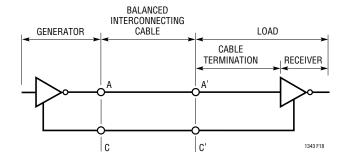

#### V.11 (RS422) Interface

A typical V.11 balanced interface is shown in Figure 16. A V.11 differential generator with outputs A and B with ground C is connected to a differential receiver with ground C', inputs A' connected to A, B' connected to B. The V.11 interface has a differential termination at the receiver end that has a minimum value of  $100\Omega$ . The termination resistor is optional in the V.11 specification, but for the high speed clock and data lines, the termination is required to prevent reflections from corrupting the data. The re-

LTC1343 LTC1344 **₹**88 51.5Ω **₹**R6 RECEIVER S3 R3 124Ω R7 10k  $51.5\Omega$ 20k В GND 1343 F15

Figure 15. V.10 Receiver Configuration

Figure 16. Typical V.11 Interface

ceiver inputs must also be compliant with the impedance curve shown in Figure 14.

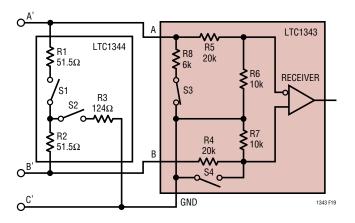

In V.11 mode, all switches are off except S1 inside the LTC1344 which connects a  $103\Omega$  differential termination impedance to the cable as shown in Figure 17.

#### V.28 (RS232) Interface

A typical V.28 unbalanced interface is shown in Figure 18. A. V.28 single-ended generator output A with ground C is connected to a single-ended receiver with inputs A' connected to A, ground C' connected via the signal return ground C.

In V.28 mode all switches are off except S3 inside the LTC1343 which connects a 6k (R8) impedance to ground in parallel with 20k (R5) plus 10k (R6) for a combined impedance of 5k as shown in Figure 19. The noninverting input is disconnected inside the LTC1343 receiver and connected to a TTL level reference voltage for a 1.4V receiver trip point.

Figure 17. V.11 Receiver Configuration

Figure 18. Typical V.28 Interface

Figure 19. V.28 Receiver Configuration

#### V.35 Interface

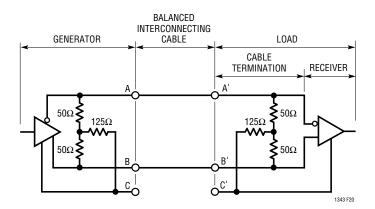

A typical V.35 balanced interface is shown in Figure 20. A V.35 differential generator with outputs A and B with ground C is connected to a differential receiver with ground C', inputs A' connected to A, B' connected to B. The V.35 interface requires a T or delta network termination at the receiver end and the generator end. The receiver differential impedance measured at the connector must be  $100\Omega \pm 10\Omega$ , and the impedance between shorted terminals (A' and B) and ground C' must be  $150\Omega \pm 15\Omega$ .

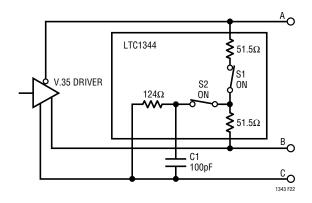

In V.35 mode, both switches S1 and S2 inside the LTC1344 are on, connecting the T network impedance as shown in Figure 21. Both switches in the LTC1343 are off. The 30k input impedance of the receiver is placed in parallel with the T network termination, but does not affect the overall input impedance significantly.

Figure 20. Typical V.35 Interface

Figure 21. V.35 Receiver Configuration

The generator differential impedance must be  $50\Omega$  to  $150\Omega$  and the impedance between shorted terminals (A and B) and ground C must be  $150\Omega$  ±15 $\Omega$ . For the generator termination, switches S1 and S2 are both on and the top side of the center resistor is brought out to a pin so it can be bypassed with an external capacitor to reduce common mode noise as shown in Figure 22.

Any mismatch in the driver rise and fall times or skew in the driver propagation delays will force current through the center termination resistor to ground, causing a high frequency common mode spike on the A and B terminals. The common mode spike can cause EMI problems that are reduced by capacitor C1 which shunts much of the common mode energy to ground rather than down the cable.

Figure 22. V.35 Driver Using the LTC1344

#### **Echoed Clock Mode**

The LTC1343 contains the logic to generate the echoed clock when using a serial controller with only two clock pins. Figure 23 shows the chip in both the DTE and DCE echoed clock in EIA-530 mode. The control signals are not shown. The echoed clock configuration is selected by pulling the EC pin low. On the DTE side the transmit clock TXC receiver output is connected to the echoed clock, SCTE, driver input. The TXC pin on the serial controller is configured as an input. On the DCE side, the transmit clock from the serial controller is used to generate both TXC and RXC. A phase inverter is placed in the TXC signal path on both the DTE and DCE side to help correct phase problems with long cables. If the Invert pin is high, the phase of the data is inverted.

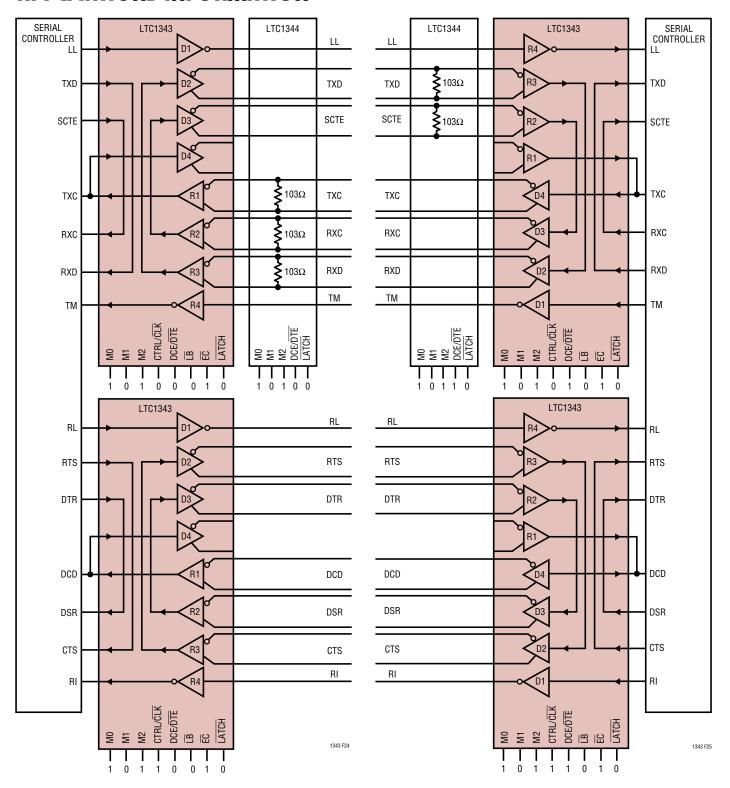

#### Loop-Back

The LTC1343 contains logic for placing the interface into a loop-back configuration for testing. Both DTE and DCE loop-back configurations are supported. Figure 24 shows a complete DTE interface in the loop-back configuration with the  $\overline{\text{EC}}$  pin pulled high. The loop-back configuration is selected by pulling the  $\overline{\text{LB}}$  pin low. Both the line side and logic side signals are looped back. The DCE loop-back configuration is shown in Figure 25.

If the echoed clock mode is selected by pulling  $\overline{EC}$  low, D3 becomes an output and is connected to receiver 2's output R3 in DTE mode as shown in Figure 26. In the echoed clock DCE loop-back mode, driver 4 is connected to driver 3's input D3 as shown in Figure 27.

Figure 23. EIA-530 Echoed Clock Configuration

Figure 24. Normal DTE Loop-Back

Figure 25. Normal DCE Loop-Back

Figure 26. Echoed Clock, DTE Loop-Back

Figure 27. Echoed Clock, DCE Loop-Back

#### **No-Cable Mode**

The no-cable mode (M0 = M1 = M2 = 1) is intended for the case when the cable is disconnected from the connector. The charge pump, bias circuitry, drivers and receivers are turned off, the driver outputs are forced into a high impedance state, and the supply current drops to less than  $200\mu A$ . It can also be used to share I/O lines with other drivers and receivers without loading down the signals.

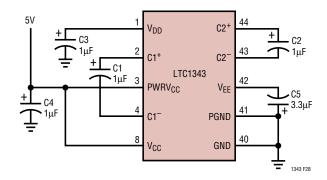

#### **Charge Pump**

The LTC1343 uses an internal capacitive charge pump to generate  $V_{DD}$  and  $V_{EE}$  as shown in Figure 28. A voltage doubler generates about 8V on  $V_{DD}$  and a voltage inverter generates about -7.5V for  $V_{EE}$ . Four  $1\mu F$  surface mounted tantalum or ceramic capacitors are required for C1, C2, C3 and C4. The  $V_{EE}$  capacitor C5 should be a minimum of  $3.3\mu F$ . All capacitors are 16V.

#### Receiver Fail-Safe and Glitch Filter

All LTC1343 receivers feature fail-safe operation in all modes except no-cable mode. If the receiver inputs are left floating or shorted together by a termination resistor, the receiver output will always be forced to a logic high. External pull-up resistors are required on receiver outputs if fail-safe operation in the no-cable mode is desired.

When the chip is configured for control signals by pulling the CTRL/CLK pin high, a glitch filter is connected to all receiver inputs. The filter will reject any glitches at the receiver inputs less than 300ns.

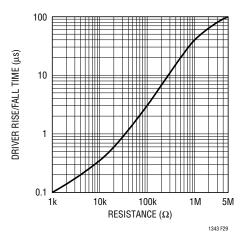

#### V.10 Driver Rise and Fall Times

The rise and fall times of the V.10 drivers is programmed by placing a 1/8W, 5% resistor between the 423 SET (Pin 25) and ground. The graph of Driver Rise and Fall Times vs Resistor Value is shown in Figure 29.

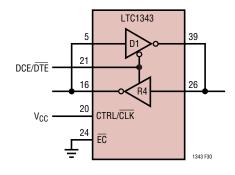

#### **Enabling the Single-Ended Driver and Receiver**

When the LTC1343 is being used to generate the control signals (CTRL/ $\overline{CLK}$  = high) and the  $\overline{EC}$  pin is pulled low, the DCE/ $\overline{DTE}$  pin becomes an enable for driver 1 and receiver 4 so their inputs and outputs can be tied together as shown in Figure 30.

Figure 28. Charge Pump

Figure 29. V.10 Driver Rise and Fall Time vs Resistor Value

Figure 30. Single-Ended Driver and Receiver Enable

The  $\overline{EC}$  pin has no affect on the configuration when CTRL/  $\overline{CLK}$  is high except to allow the DCE/ $\overline{DTE}$  pin to become an enable. When DCE/ $\overline{DTE}$  is low, the driver 1 output is enabled. The receiver 4 output goes into three-state and the input presents a  $30k\Omega$  load to ground.

When DCE/ $\overline{DTE}$  is high, the driver 1 output goes into three-state and the receiver 4 output is enabled. The receiver 4 input presents a  $30k\Omega$  load to ground in all modes except when configured for RS232 operation when the input impedance is  $5k\Omega$  to ground.

#### **DTE vs DCE Operation**

The DCE/DTE pin does not allow a given LTC1343 pin to be reconfigured as a driver or receiver. The DCE/DTE pin only selects the loop-back topology and acts as an enable for the single-ended driver and receiver for control signals.

However, the LTC1343 can be configured for either DTE or DCE operation in one of three ways: a dedicated DTE or DCE port with a connector of appropriate gender, a port with one connector that can be configured for DTE or DCE operation by rerouting the signals to the LTC1343 using a dedicated DTE cable or dedicated DCE cable, or a port with one connector and one cable using four LTC1343s.

A dedicated DTE port using a DB-25 male connector is shown in Figure 31. The interface mode is selected by logic outputs from the controller or from jumpers to either  $V_{CC}$  or GND on the mode select pins. A dedicated DCE port using a DB-25 female connector is shown in Figure 32.

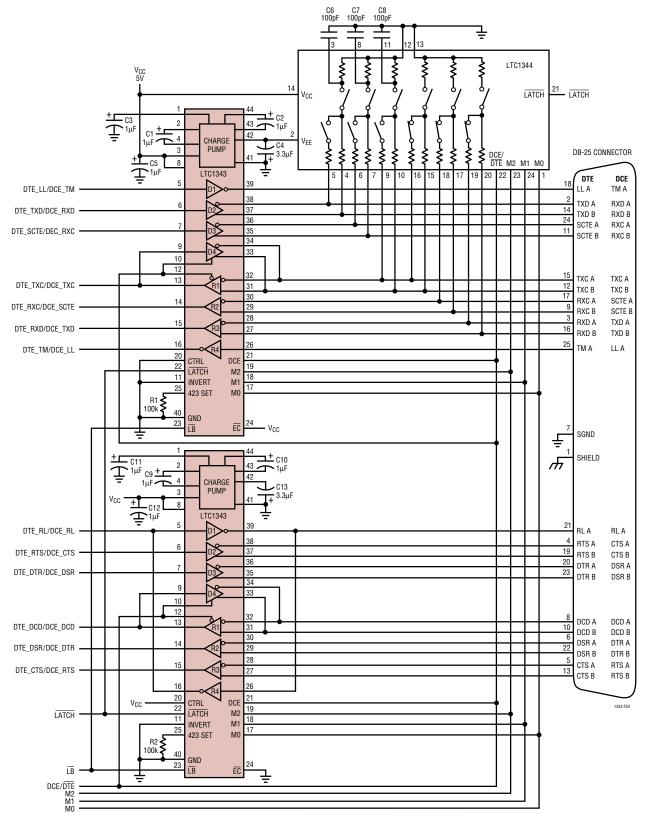

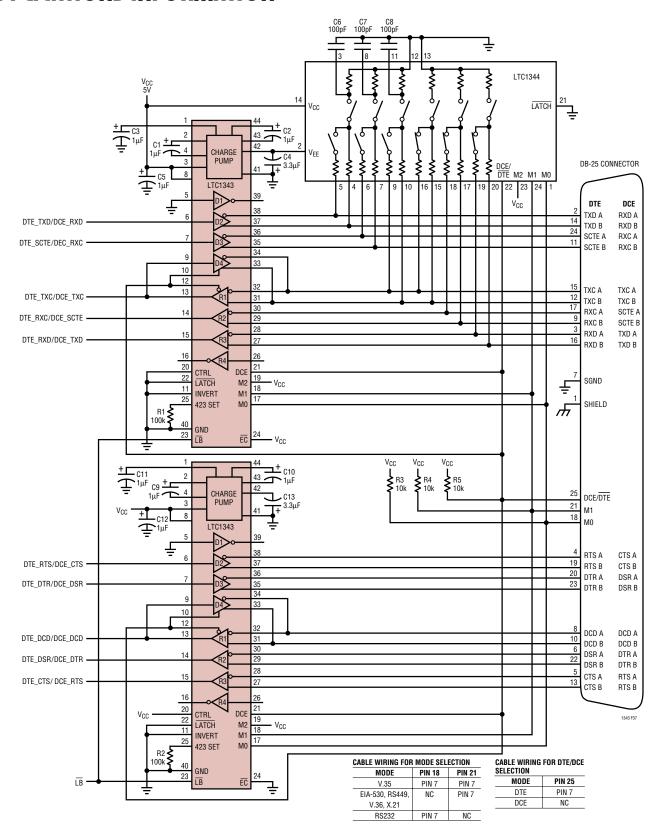

A port with one DB-25 connector that can be configured for either DTE or DCE operation is shown in Figure 33. The configuration requires separate cables for proper signal routing in DTE or DCE operation. For example, in DTE mode, the TXD signal is routed to connector Pins 2 and 14 via driver 2 in the LTC1343. In DCE mode, driver 2 now routes the RXD signal to Pins 2 and 14.

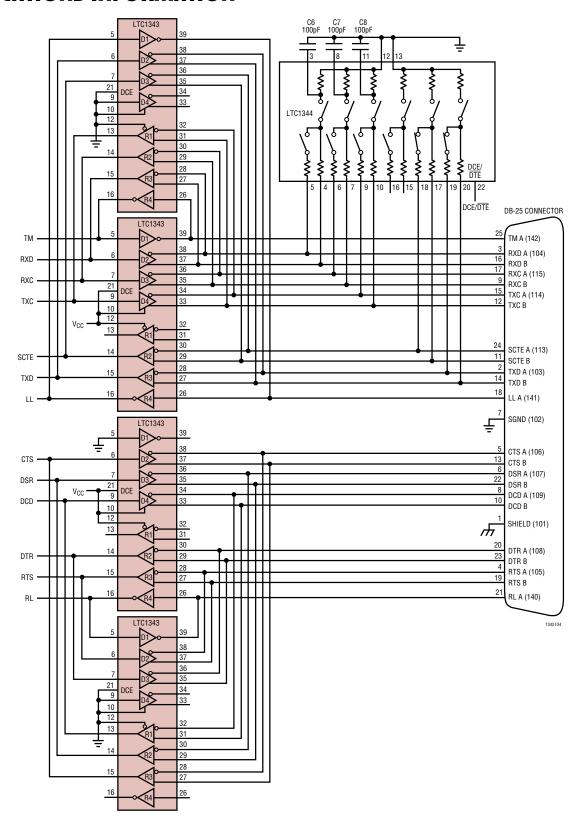

A combination DTE/DCE port that doesn't require separate DCE/DTE cables is shown in Figure 34. In DTE mode, the top and bottom LTC1343s are enabled and the middle two are placed in the no-cable mode, which forces all of the

drivers and receivers into a high impedance state. In the DCE mode, the middle two LTC1343s are enabled and the top and bottom LTC1343s disabled. With this scheme, any connector pin can be configured for sending or receiving signals. Note that only one LTC1344 is required.

## Multiprotocol Interface with Ring-Indicate and a DB-25 Connector

If the RI signal in RS232 mode is implemented, driver 4 and receiver 1 in the control chip can be tied to connector Pin 22 in order to implement the RI signal in RS232 mode and DSR B signal for the other modes. Figure 35 shows the DTE configuration and Figure 36 the DCE configuration. In DCE mode, the DCE/DTE pin should be driven with a logic signal from the controller that goes low only when the interface is in the RS232 mode. Since the receiver 4 input impedance is greater than  $30k\Omega$  in all modes except RS232, it can be enabled at all other times and not load down the line. When driver 1 is disabled, it remains in a high impedance state and does not load the line.

#### Cable-Selectable Multiprotocol Interface

A cable-selectable multiprotocol DTE/DCE interface is shown in Figure 37. The control signals LL, RL and TM are not implemented. The select lines M0, M1 and DCE/DTE are brought out to the connector. The mode is selected through the cable by wiring M0 (connector Pin 18), M1 (connector Pin 21) and DCE/DTE (connector Pin 25) to ground (connector Pin 7) or letting them float. If M0, M1 or DCE/DTE are floating, pull-up resistors R3, R4 and R5 will pull the signals to  $V_{CC}$ . The select bit M1 is hard wired to  $V_{CC}$ . When the cable is pulled out, the interface will go into the no-cable mode.

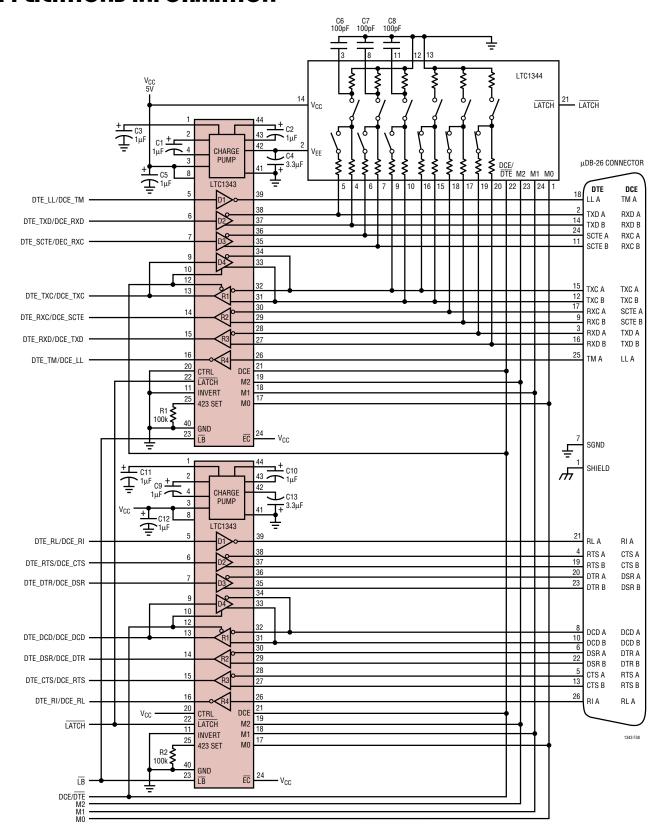

#### Multiprotocol Interface with a µDB-26 Connector

The controller-selectable multiprotocol DTE/DCE interface with a standard  $\mu$ DB-26 connector is shown in Figure 38. The RL, LL and TM signals are implemented and RI is mapped to Pin 26 on the connector. A cable-selectable version is shown in Figure 39. The TM and RL signals have been dropped, but LL is still implemented.

Figure 31: Controller-Selectable Multiprotocol DTE Port with DB-25 Connector

Figure 32: Controller-Selectable Multiprotocol DCE Port with DB-25 Connector

Figure 33. Controller-Selectable Multiprotocol DTE/DCE Port with DB-25 Connector

Figure 34. Controller-Selectable Multiprotocol DTE/DCE Port with DB-25

Figure 35. Controller-Selectable Multiprotocol DTE Port with RI and DB-25 Connector

Figure 36. Controller-Selectable Multiprotocol DCE Port with RI and DB-25 Connector

Figure 37. Cable-Selectable Multiprotocol DTE/DCE Port with DB-25 Connector

Figure 38. Controller-Selectable Multiprotocol DTE/DCE Port with DB-26 Connector

Figure 39. Cable-Selectable Multiprotocol DTE Port with DB-26 Connector

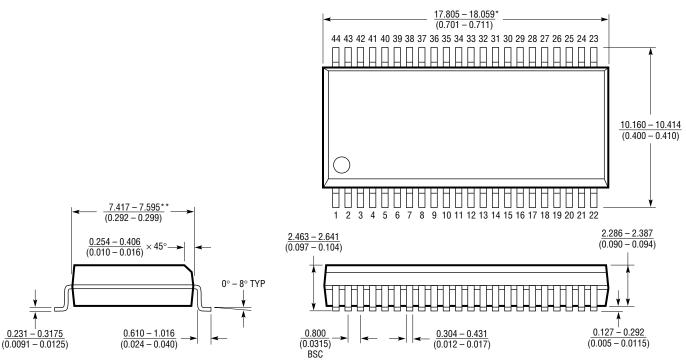

#### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

#### **GW Package** 44-Lead Plastic SSOP (Wide 0.300)

(LTC DWG # 05-08-1642)

NOTE: DIMENSIONS ARE IN MILLIMETERS

G44 SSDP 1098

## **RELATED PARTS**

| PART NUMBER      | DESCRIPTION                                     | COMMENTS                                                       |

|------------------|-------------------------------------------------|----------------------------------------------------------------|

| LTC1321          | Dual RS232/RS485 Transceiver                    | 2 RS232 Driver/Receiver Pairs or 2 RS485 Driver/Receiver Pairs |

| LTC1334          | Single 5V RS232/RS485 Multiprotocol Transceiver | 2 RS232 Driver/Receiver or 4 RS232 Driver/Receiver Pairs       |

| LTC1344/LTC1344A | Software-Selectable Cable Terminator            | Perfect for Terminating the LTC1343                            |

| LTC1345          | Single Supply V.35 Transceiver                  | 3 Driver/3 Receiver for Data and Clock Signals                 |

| LTC1346A         | Dual Supply V.35 Transceiver                    | 3 Driver/3 Receiver for Data and Clock Signals                 |

| LTC1543          | Software-Selectable Multiprotocol Transceiver   | 3 Driver/3 Receiver for Data and Clock Signals                 |

| LTC1544          | Software-Selectable Multiprotocol Transceiver   | 4 Driver/4 Receiver for Control Signals Including LL           |

| LTC1545          | Software-Selectable Multiprotocol Transceiver   | 5 Driver/5 Receiver for Control Signals Including LL, RL, TM   |

<sup>\*</sup>DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH. \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD SHALL NOT EXCEED 0.152mm (0.006") PER SIDE FLASH SHALL NOT EXCEED 0.254mm (0.010") PER SIDE