### **ORDER NUMBER:**

EMC2102-DZK FOR 28-PIN QFN LEAD-FREE ROHS COMPLIANT PACKAGE (ADDRESS - 011\_1101)

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2007 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC's SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap  | oter 1 Block Diagram                                  | 7  |

|-------|-------------------------------------------------------|----|

| Chap  | oter 2 Pinout                                         |    |

| 2.1   | Pin Layout for EMC2102                                | 8  |

| 2.2   | Pin Description for EMC2102                           | 9  |

| Char  | oter 3 Electrical Specifications                      | 1  |

| 3.1   | Absolute Maximum Ratings                              |    |

| 3.2   | Electrical Specifications                             |    |

| 3.3   | SMBus Electrical Specifications                       |    |

| Char  | oter 4 System Management Bus Interface Protocol       | 15 |

| 4.1   | Write Byte                                            | 15 |

| 4.2   | Read Byte                                             |    |

| 4.3   | Send Byte                                             |    |

| 4.4   | Receive Byte                                          |    |

| 4.5   | Alert Response Address                                |    |

| 4.6   | SMBus Address                                         |    |

| 4.7   | SMBus Time-out                                        | 17 |

| Char  | oter 5 General Description                            | 18 |

| 5.1   | Temperature Monitoring                                |    |

| • • • | 5.1.1 Resistance Error Correction                     |    |

|       | 5.1.2 Beta Compensation                               |    |

|       | 5.1.3 Fault Queue                                     |    |

| 5.2   | Fan Control Modes of Operation                        |    |

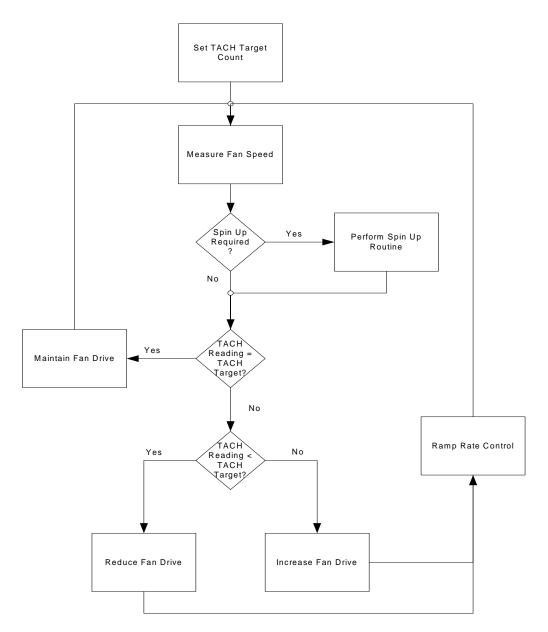

| 5.3   | RPM based Fan Control Algorithm                       |    |

|       | 5.3.1 Programming the RPM based Fan Control Algorithm |    |

|       | 5.3.2 TACH Measurement                                |    |

| 5.3.2 | .1 Stalled Fan23                                      |    |

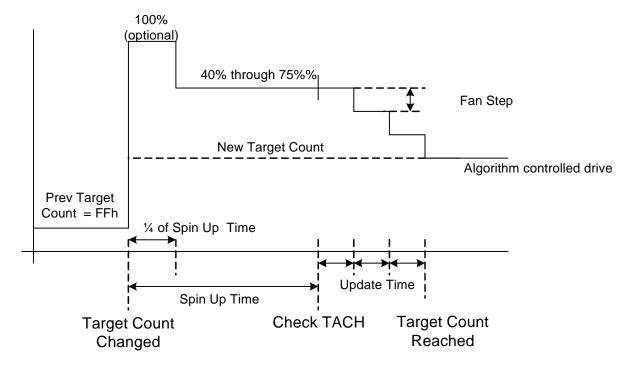

|       | 5.3.3 Spin Up Routine                                 | 23 |

|       | 5.3.4 FAN_MODE Pin                                    | 25 |

|       | 5.3.5 32.768KHz Clock Source                          | 25 |

| 5.4   | Watchdog Timer                                        |    |

| 5.5   | High Side Fan Driver                                  |    |

|       | 5.5.1 Overcurrent Limit                               |    |

| 5.6   | Internal Thermal Shutdown (TSD)                       |    |

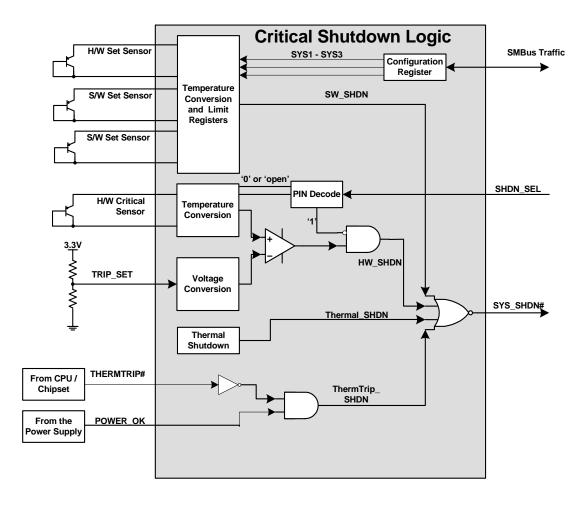

| 5.7   | Critical/Thermal Shutdown                             |    |

|       | 5.7.1 TRIP_SET                                        |    |

|       | 5.7.2 SHDN_SEL Pin                                    |    |

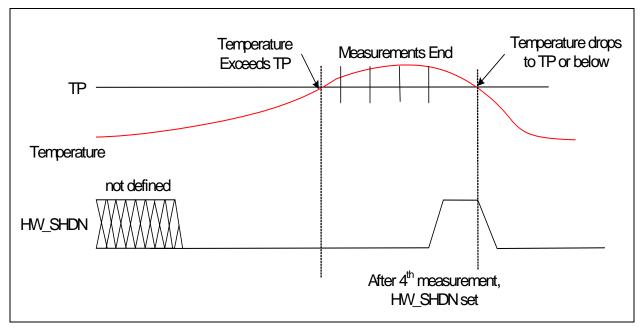

|       | 5.7.3 Internal HW_SHDN Signal                         |    |

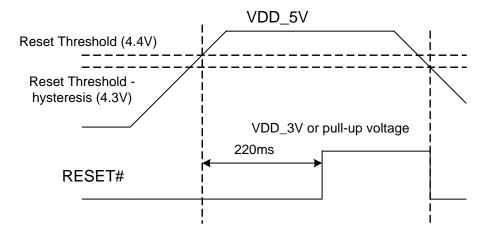

| 5.8   | 5V Reset Controller                                   | 30 |

| Char  | oter 6 Register Set3                                  | 31 |

| 6.1   | Register Map                                          | 31 |

|       | 6.1.1 Lock Entries                                    |    |

| 6.2   | Temperature Data Registers                            |    |

| 6.3   | Critical/Thermal Shutdown Temperature Register        |    |

| 6.4   | Configuration Register                                |    |

| 6.5   | Conversion Rate Register                              |    |

| 6.6   | Interrupt Status Register 1                           | 36 |

|      |                                             | - 414.01.001 |

|------|---------------------------------------------|--------------|

| 6.7  | Interrupt Status Register 2                 | 37           |

| 6.8  | Interrupt Mask Register                     |              |

| 6.9  | Beta Configuration Registers                | 38           |

| 6.10 | REC Configuration Register                  | 39           |

| 6.11 | Temperature Limit Registers                 | 40           |

| 6.12 | Fan Driver Setting Register                 |              |

| 6.13 | Fan Configuration Register                  | 41           |

| 6.14 | Fan Spin Up Configuration Register          | 42           |

| 6.15 | Fan Step Register                           | 43           |

| 6.16 | Fan Minimum Drive Register                  | 43           |

| 6.17 | Valid TACH Count Register                   | 44           |

| 6.18 | TACH Target Register                        | 44           |

| 6.19 | TACH Reading Register                       | 44           |

| 6.20 | Product ID Register                         | 45           |

| 6.21 | Revision Register                           | 46           |

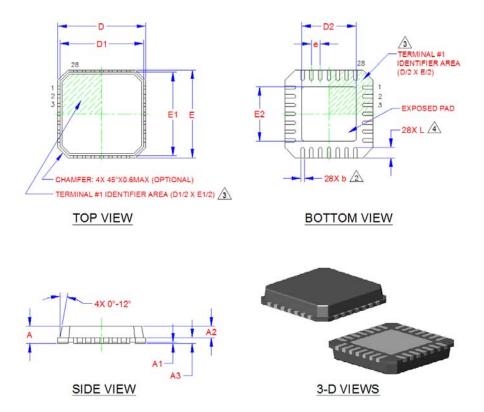

| Chap | pter 7 Package Drawing                      | 47           |

| Appo | endix A TACH Reading Table - 2000 RPM Range | 48           |

| Appo | endix B TACH Reading Table - 500RPM Range   | 51           |

# **List of Figures**

| Figure 1.1 | EMC2102 Block Diagram                                   | . 7 |

|------------|---------------------------------------------------------|-----|

| Figure 2.1 | EMC2102 Pin Diagram                                     | . 8 |

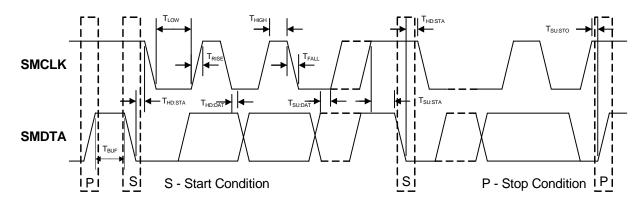

| Figure 4.1 | SMBus Timing Diagram                                    | 15  |

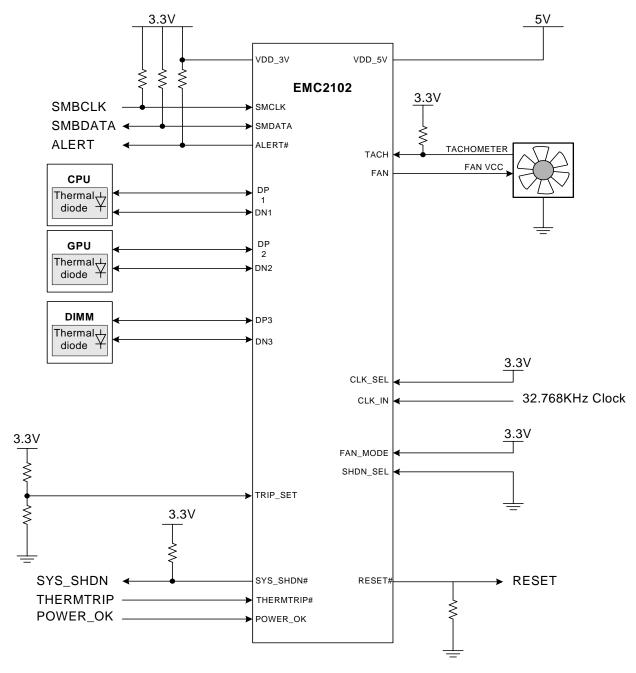

| Figure 5.1 | EMC2102 System Diagram                                  | 19  |

| Figure 5.2 | RPM based Fan Control Algorithm                         | 22  |

| Figure 5.3 | Spin Up Routine                                         | 24  |

| Figure 5.4 | EMC2102 Critical/Thermal Shutdown Block Diagram         | 27  |

| Figure 5.5 | HW_SHDN Operation                                       | 29  |

| Figure 5.6 | 5V Reset Controller Timing                              | 30  |

| Figure 7.1 | EMC2102 28-Pin 5x5mm QFN Package Outline and Parameters | 47  |

# **List of Tables**

| Table 2.1 | Pin Description                                | Ć  |

|-----------|------------------------------------------------|----|

| Table 3.1 | Absolute Maximum Ratings                       | 11 |

| Table 3.2 | Electrical Specifications                      | 11 |

| Table 3.3 | SMBus Electrical Specifications                | 13 |

| Table 4.1 | Protocol Format                                | 15 |

| Table 4.2 | Write Byte Protocol                            | 15 |

| Table 4.3 | Read Byte Protocol                             | 16 |

|           | Send Byte Protocol                             |    |

| Table 4.5 | Receive Byte Protocol                          | 16 |

|           | Alert Response Address Protocol                |    |

| Table 5.1 | Fan Controls Active for Operating Mode         | 21 |

| Table 5.2 | FAN_MODE Pin Functions                         | 25 |

|           | CLK_SEL Pin Functions                          |    |

|           | SHDN_SEL Pin Configuration                     |    |

| Table 6.1 | EMC2102 Register Set                           | 31 |

|           | Temperature data Registers                     |    |

|           | Temperature Data Format                        |    |

|           | Critical/Thermal Shutdown Temperature Register |    |

|           | Configuration Register                         |    |

|           | Fault Queue                                    |    |

|           | Conversion Rate Register                       |    |

|           | Conversion Rate                                |    |

|           | Interrupt Status Register 1                    |    |

|           | Interrupt Status Register 2                    |    |

|           | Interrupt Mask Register                        |    |

|           | Beta Configuration Registers                   |    |

|           | Beta Compensation Look Up Table                |    |

|           | REC Configuration Register                     |    |

|           | Temperature Limit Registers                    |    |

|           | Fan Driver Setting Register                    |    |

|           | Fan Control Configuration Register             |    |

|           | Minimum Edges for Fan Rotation                 |    |

|           | Update Time                                    |    |

|           | Fan TACH Configuration Register                |    |

|           | Spin Time                                      |    |

|           | Fan Step Register                              |    |

|           | Minimum Fan Drive Register                     |    |

|           | Valid TACH Count Register                      |    |

|           | TACH Reading Registers                         |    |

|           | TACH Reading Register                          |    |

|           | Example TACH Reading for Specific Fan Speeds   |    |

|           | Product ID Register                            |    |

|           | Revision Register                              |    |

|           | TACH Count to RPM (2k Range)                   |    |

| Table 7.2 | TACH Count to RPM (500 Range)                  | 51 |

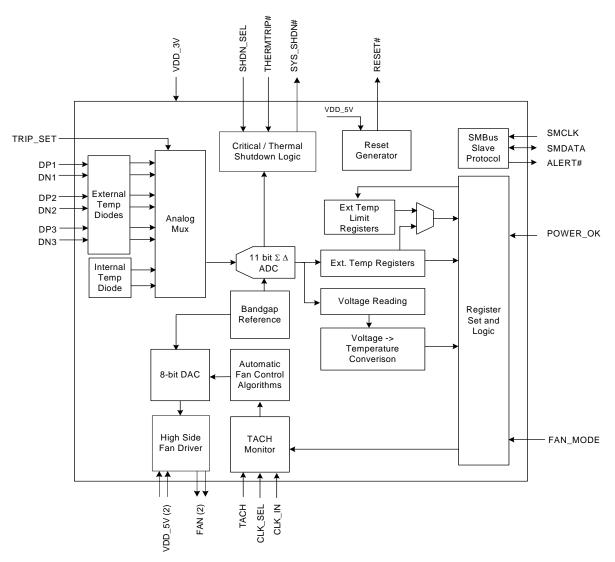

# **Chapter 1 Block Diagram**

Figure 1.1 EMC2102 Block Diagram

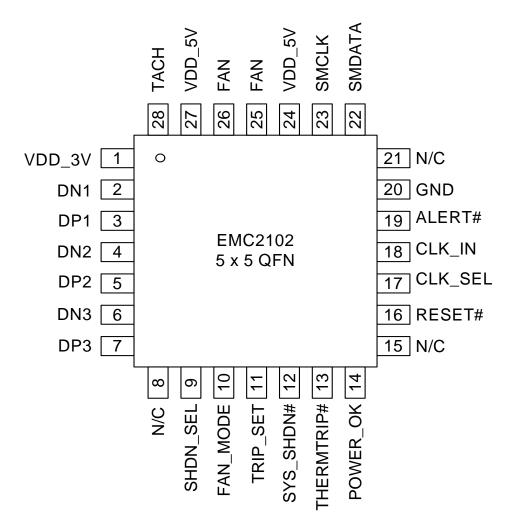

## 2.1 Pin Layout for EMC2102

Figure 2.1 EMC2102 Pin Diagram

# 2.2 Pin Description for EMC2102

**Table 2.1 Pin Description**

| PIN | NAME       | FUNCTION                                                                                  | TYPE                                               |

|-----|------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1   | VDD_3V     | Supply Connection of 3.3V.                                                                | Power                                              |

| 2   | DN1        | Negative (cathode) Analog Input for External Diode 1.                                     | AIO                                                |

| 3   | DP1        | Positive (anode) Analog Input for External Diode 1.                                       | AIO                                                |

| 4   | DN2        | Negative (cathode) Analog Input for External Diode 2.                                     | AIO                                                |

| 5   | DP2        | Positive (anode) Analog Input for External Diode 2.                                       | AIO                                                |

| 6   | DN3        | Negative (cathode) Analog Input for External Diode 3.                                     | AIO                                                |

| 7   | DP3        | Positive (anode) Analog Input for External Diode 3.                                       | AIO                                                |

| 8   | N/C        | Not internally connected.                                                                 | N/A                                                |

| 9   | SHDN_SEL   | Determines HW Shutdown temperature channel (see Table 5.4, "SHDN_SEL Pin Configuration".) | DIT                                                |

| 10  | FAN_MODE   | Selects power-up default for fan drive setting.                                           | DIT                                                |

| 11  | TRIP_SET   | Voltage input to determine HW<br>Shutdown threshold temperature                           | Al                                                 |

| 12  | SYS_SHDN#  | Active low Critical System Shutdown output                                                | OD (5V)                                            |

| 13  | THERMTRIP# | Active low Critical temperature limit signal from the CPU or chipset.                     | IP                                                 |

| 14  | POWER_OK   | Active high power good input.                                                             | DI (5V)                                            |

| 15  | N/C        | Not internally connected.                                                                 | N/A                                                |

| 16  | RESET#     | Active low reset output.                                                                  | DO                                                 |

| 17  | CLK_SEL    | Selects internal oscillator or external clock.                                            | DI (5V)                                            |

| 18  | CLK_IN     | 32.768KHz clock input.                                                                    | DI (5V)                                            |

| 19  | ALERT#     | Active low interrupt.                                                                     | OD (5V)                                            |

| 20  | GND        | GND connection.                                                                           | Power                                              |

| 21  | N/C        | Not internally connected.                                                                 | N/A                                                |

| 22  | SMDATA     | SMBus data input/output.                                                                  | DIOD (5V) - requires external upll-<br>up resistor |

| 23  | SMCLK      | SMBus clock input.                                                                        | DI (5V) - requires external pull-up resistor       |

### Table 2.1 Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                           | TYPE    |

|-----|--------|----------------------------------------------------------------------------------------------------|---------|

| 24  | VDD_5V | 5V supply input for the linear fan driver. Both VDD_5V pins should be connected to same 5V supply. | Power   |

| 25  | FAN    | Linear fan drive signal. Both FAN pins should be connected together.                               | AO      |

| 26  | FAN    | Linear fan drive signal. Both FAN pins should be connected together.                               | AO      |

| 27  | VDD_5V | 5V supply input for the linear fan driver. Both VDD_5V pins should be connected to same 5V supply. | Power   |

| 28  | TACH   | Input from the tachometer pin of the fan.                                                          | DI (5V) |

The pin type are described in detail below. All pins labelled with (5V) are 5V tolerant.:

Power - this pin is used to supply power to the device.

- DI Digital Input this pin is used as a digital input. This pin is 5V tolerant.

- AI Analog Input this pin is used as an input for analog signals.

- AO Analog Output this pin is used as an output for analog signals.

- AIO Analog Input / Output this pin is used as an I/O for analog signals.

- DO Push / Pull Digital Output this pin is used as a digital output. It can both source and sink current and doesn't require a pull-up resistor.

- DIOD Open Drain Digital Input / Output this pin is used as an digital I/O. It is open drain and requires a pull-up resistor. This pin is 5V tolerant.

- OD Open Drain Digital Output this pin is used as a digital output. It is open drain and requires a pull-up resistor.

- DIT Tri-stated Digital Input this pin is a digital input that supports 3 logic levels at the input: logic high, logic low, or high impedance (open).

- IP Digital Input this pin has an internal 30uA pull-up current to VDD\_3V.

# **Chapter 3 Electrical Specifications**

# 3.1 Absolute Maximum Ratings

**Table 3.1 Absolute Maximum Ratings**

| Voltage on VDD_5V Pins and 5V tolerant pins (see Table 2.1, "Pin Description") | -0.3 to 6.5                              | V    |

|--------------------------------------------------------------------------------|------------------------------------------|------|

| Voltage on VDD_3V pin                                                          | -0.3 to 4                                | V    |

| Voltage on FAN pins                                                            | -0.3 to VDD_5V + 0.3                     | V    |

| Voltage on any other pin to GND                                                | -0.3 to VDD_3V + 0.3                     | V    |

| Package Power Dissipation                                                      | 0.9 up to T <sub>A</sub> = 85°C Note 3.2 | W    |

| Junction to Ambient (θ <sub>JA</sub> ) Note 3.3                                | 37                                       | °C/W |

| Operating Ambient Temperature Range                                            | 0 to 85                                  | °C   |

| Operating Die Temperature Range                                                | 0 to 125                                 | °C   |

| Storage Temperature Range                                                      | -55 to 150                               | °C   |

| ESD Rating, All Pins, HBM                                                      | 2000                                     | V    |

These ratings are absolute maximum values. Exceeding these values or operating at these values for an extended period of time may cause permanent damage to the device.

- Note 3.1 All voltages are relative to ground.

- **Note 3.2** The Package Power Dissipation specification assumes a thermal via design consisting of four 20mil vias connected to the ground plane with a 3.1mm x 3.1mm thermal landing.

- Note 3.3 Junction to Ambient  $(\theta_{JA})$  is dependent on the design of the thermal vias. Without thermal vias and a thermal landing, the  $\theta_{JA}$  is approximately 60°C/W including localized PCB temperature increase.

# 3.2 Electrical Specifications

**Table 3.2 Electrical Specifications**

| VDD_3V = 3V to 3.6V, VDD_5V = 4.6V - 5.5V, $T_A$ = 0°C to 85°C all Typical values at $T_A$ = 27°C unless otherwise noted. |                    |     |        |     |    |                    |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------|-----|----|--------------------|--|--|--|

| CHARACTERISTIC SYMBOL MIN TYP MAX UNIT CONDITIONS                                                                         |                    |     |        |     |    |                    |  |  |  |

|                                                                                                                           | 1                  |     | DC Pow | /er |    |                    |  |  |  |

| 3.3V Supply Voltage                                                                                                       | V <sub>DD_3V</sub> | 3   | 3.3    | 3.6 | V  |                    |  |  |  |

| 5V Supply Voltage                                                                                                         | V <sub>DD_5V</sub> | 4.6 | 5      | 5.5 | V  |                    |  |  |  |

| Supply Current from VDD_3V pin                                                                                            | I <sub>DD3</sub>   |     | 500    | 750 | uA | Fan Driver enabled |  |  |  |

| Supply Current from VDD_5V pin                                                                                            | I <sub>DD5</sub>   |     | 200    |     | uA | Fan Driver enabled |  |  |  |

### Table 3.2 Electrical Specifications (continued)

| ±1 ±3 °C   0°C < T <sub>DIDE</sub> < 125°C, 0°C < T <sub>DIDE</sub> < 115°C (Note 3.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VDD_3V = 3V to 3.6V, VDD_5V = 4.6V - 5.5V, $T_A = 0^{\circ}C$ to 85°C all Typical values at $T_A = 27^{\circ}C$ unless otherwise noted. |                             |         |            |                  |      |                                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|------------|------------------|------|--------------------------------------------------------------------------------|--|--|--|

| #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CHARACTERISTIC                                                                                                                          | SYMBOL                      | MIN     | TYP        | MAX              | UNIT | CONDITIONS                                                                     |  |  |  |

| ±1 ±3 °C   0°C < T <sub>DIDE</sub> < 125°C, 0°C < T <sub>DIDE</sub> < 115°C (Note 3.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | External Temperature Monitors                                                                                                           |                             |         |            |                  |      |                                                                                |  |  |  |

| Temperature Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |                             |         | ±1         | ±1.5             | °C   | 60°C < T <sub>DIODE</sub> < 100°C<br>30°C < T <sub>DIE</sub> < 85°C (Note 3.4) |  |  |  |

| Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         |                             |         | ±1         | ±3               | °C   | 0°C < T <sub>DIODE</sub> < 125°C,<br>0°C < T <sub>DIE</sub> < 115°C (Note 3.4) |  |  |  |

| 2200   pF   2N3904 diode or AMD diode (Note 3.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Temperature<br>Resolution                                                                                                               |                             |         | 1          |                  | °C   |                                                                                |  |  |  |

| Resistance Error Corrected         R <sub>SERIES</sub> 100         Ohm         Series resistance in DP and D lines           Internal Temperature Monitor           Temperature Accuracy         ±3         °C         (Note 3.4 )           Temperature Accuracy           1         °C         (Note 3.4 )           Temperature Resolution           Reset Generator           Reset Voltage           V <sub>RESET</sub> 4.3         4.4         4.5         V         V <sub>DD_SV</sub> rising edge 3V < V <sub>DD_3V</sub> < 3.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                         | C <sub>FILTER</sub>         |         |            | 2200             | pF   | 2N3904 diode or AMD diode                                                      |  |  |  |

| Corrected         RSERIES         INternal Temperature Monitor           Temperature Accuracy         ±3         °C         (Note 3.4 )           Temperature Resolution         1         °C         (Note 3.4 )           Temperature Resolution           Reset Generator           Reset Voltage           VRESET         4.3         4.4         4.5         V         VDD_5 vrising edge 3V < VDD_3 v < VDD_4 v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                         |                             |         |            | 470              | pF   | Connected across CPU or GPU thermal diode (Note 3.5)                           |  |  |  |

| Temperature Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                       | R <sub>SERIES</sub>         |         |            | 100              | Ohm  | Series resistance in DP and DN lines                                           |  |  |  |

| Accuracy         ±3         C           Temperature Resolution           Reset Generator           Reset Voltage           V <sub>RESET</sub> 4.3         4.4         4.5         V         V <sub>DD_5</sub> vrising edge 3V < V <sub>DD_3V</sub> < 3.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                         |                             | Interna | al Tempera | ture Monito      | or   |                                                                                |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |                             |         | ±3         |                  | °C   | (Note 3.4)                                                                     |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Temperature<br>Resolution                                                                                                               |                             |         | 1          |                  | °C   |                                                                                |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                         |                             |         | Reset Gen  | erator           |      |                                                                                |  |  |  |

| Time Delay $t_{RESET}$ 220 ms  High Side Fan Driver  Output High Voltage from 5V supply $t_{DL} = t_{DV} = t_{$ | Reset Voltage                                                                                                                           | V <sub>RESET</sub>          | 4.3     | 4.4        | 4.5              | V    | $V_{DD_{-5V}}$ rising edge $3V < V_{DD_{-3V}} < 3.6V$                          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hysteresis                                                                                                                              | $\Delta$ V <sub>RESET</sub> |         | 100        |                  | mV   |                                                                                |  |  |  |

| Output High Voltage from 5V supply     VOH_5V     VDD_5 V - 0.4     V Isource = 600mA, VDD_5V = 5V       Fan Drive Current     Isource = 600mA, VDD_5V = 5V       Overcurrent Limit     Isource = 600mA, VDD_5V = 5V       Overcurrent Limit     Isource = 600mA, VDD_5V = 5V       Overcurrent Limit     Isource = 600mA, VDD_5V = 5V       Momentary Current drive at startup for < 2 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Time Delay                                                                                                                              | t <sub>RESET</sub>          |         | 220        |                  | ms   |                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         |                             | Hi      | gh Side Fa | n Driver         | •    |                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output High Voltage from 5V supply                                                                                                      | V <sub>OH_5V</sub>          |         |            | VDD_5<br>V - 0.4 | V    | I <sub>SOURCE</sub> = 600mA, VDD_5V =                                          |  |  |  |

| DC Short Circuit Current Limit $I_{SHORT}$ | Fan Drive Current                                                                                                                       | I <sub>SOURCE</sub>         |         |            | 600              | mA   |                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Overcurrent Limit                                                                                                                       | I <sub>OVER</sub>           |         | 1500       |                  | mA   | Momentary Current drive at startup for < 2 seconds                             |  |  |  |

| Output Capacitive Load 100 uF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                         | I <sub>SHORT</sub>          |         | 800        |                  | mA   | shutdown not triggered,                                                        |  |  |  |

| Load CLOAD 100 UF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Short circuit delay                                                                                                                     | t <sub>DFS</sub>            |         | 2          |                  | S    |                                                                                |  |  |  |

| ESR on Cross Resp. 0 2 Ohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         | C <sub>LOAD</sub>           |         |            | 100              | uF   |                                                                                |  |  |  |

| ZON OLOGIO   NESR   V   Z   Olill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ESR on C <sub>LOAD</sub>                                                                                                                | R <sub>ESR</sub>            | 0       |            | 2                | Ohm  |                                                                                |  |  |  |

### Table 3.2 Electrical Specifications (continued)

| VDD_3V = 3V to 3.6V, VDD_5V = 4.6V - 5.5V, $T_A$ = 0°C to 85°C all Typical values at $T_A$ = 27°C unless otherwise noted. |                     |                |           |        |     |                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|-----------|--------|-----|--------------------------------------------------------|--|--|--|

| CHARACTERISTIC                                                                                                            | CONDITIONS          |                |           |        |     |                                                        |  |  |  |

| TACH Range                                                                                                                | TACH                | 480            |           | 16000  | RPM |                                                        |  |  |  |

| TACH Setting<br>Accuracy                                                                                                  | $\Delta_{TACH}$     |                | ±1        | ±2     | %   | External oscillator 32.768kHz                          |  |  |  |

| Accuracy                                                                                                                  | $\Delta_{TACH}$     |                | ±5        | ±7.5   | %   | Internal Oscillator<br>40°C < T <sub>DIE</sub> < 100°C |  |  |  |

|                                                                                                                           |                     | Т              | hermal Sh | utdown |     |                                                        |  |  |  |