#### Order Number:

UFX7000-VE for 225-Ball LFBGA RoHS Compliant Package (0 TO +70°C Temp Range)

This product meets the halogen maximum concentration values per IEC61249-2-21

For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Please contact your SMSC sales representative for additional documentation related to this product such as application notes, anomaly sheets, and design guidelines.

Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC listerature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The MIcrochip name and logo, and the Microchip logo are registered trademarks of MIcrochip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Revision 1.4 (06-24-13)

# **Table of Contents**

| <b>Cha</b><br>1.1<br>1.2<br>1.3<br>1.4 | Deter 1 Introduction       USB Device Controller         USB Device Controller       Graphics Subsystem         DDR2 SDRAM Interface       Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6<br>7<br>7      |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| <b>Cha</b> j<br>2.1<br>2.2             | Pin Description and Configuration       2         Pin Assignments       2         Buffer Types       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                |

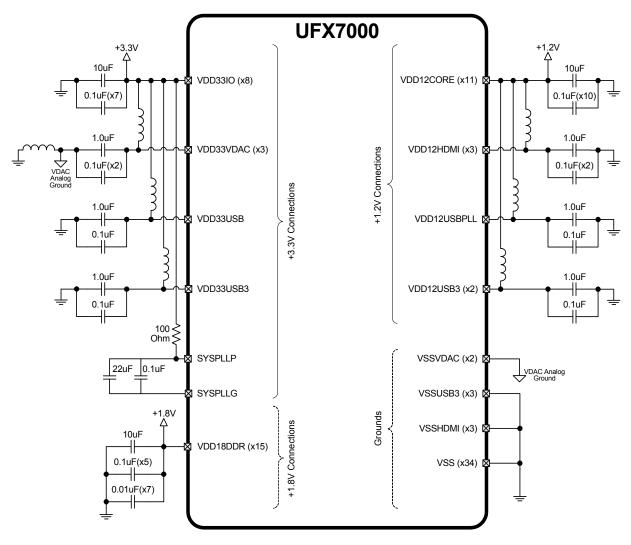

| Chaj                                   | pter 3 Power Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                |

| Chaj<br>4.1<br>4.2<br>4.3<br>4.4       | a EEPROM       3         EEPROM Format       3         EEPROM Defaults       3         EEPROM Auto-Load       3         Customized Operation Without EEPROM       3                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0<br>7<br>7      |

| Chaj<br>5.1<br>5.2<br>5.3<br>5.4       | Absolute Maximum Ratings*.       3         Operating Conditions**.       3         Package Thermal Specifications       3         Current Consumption       3         5.4.1       SUSPEND Power State.       3         5.4.2       Operational       4                                                                                                                                                                                                                                                                                                                                                                | 8<br>9<br>9<br>9 |

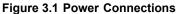

| 5.5<br>5.6<br>5.7                      | DC Specifications4AC Specifications45.6.1Power Sequence Timing5.6.2Power-On Reset Timing5.6.3Reset Timing5.6.4Video DAC Timing5.6.5Digital RGB Timing5.6.6EEPROM Timing45.6.75.6.7JTAG Timing45Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5Solution5 <td>123455689</td> | 123455689        |

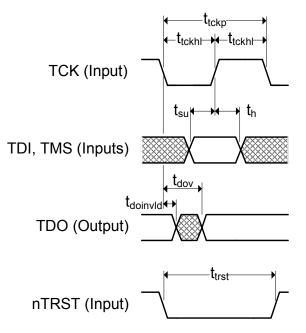

| <b>Cha</b> j<br>6.1                    | pter 6 Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| Cha                                    | oter 7 Datasheet Revision History5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                |

# List of Figures

| Internal Block Diagram.                | . 6                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Assignments (TOP VIEW)             | . 8                                                                                                                                                                                                                                                                                                                                |

| Power Connections                      | 29                                                                                                                                                                                                                                                                                                                                 |

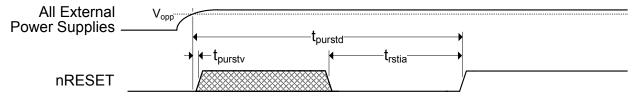

| Power-On Timing                        | 43                                                                                                                                                                                                                                                                                                                                 |

| nRESET Power-On Timing                 | 44                                                                                                                                                                                                                                                                                                                                 |

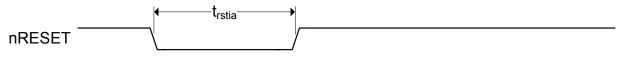

| nRESET Timing                          | 45                                                                                                                                                                                                                                                                                                                                 |

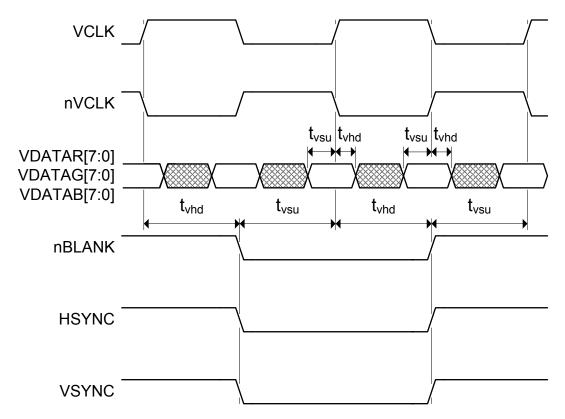

| Digital RGB Timing - DDR Mode          | 46                                                                                                                                                                                                                                                                                                                                 |

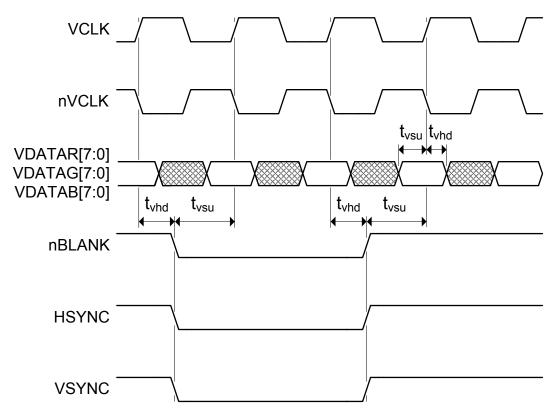

| Digital RGB Timing - SDR Mode          | 47                                                                                                                                                                                                                                                                                                                                 |

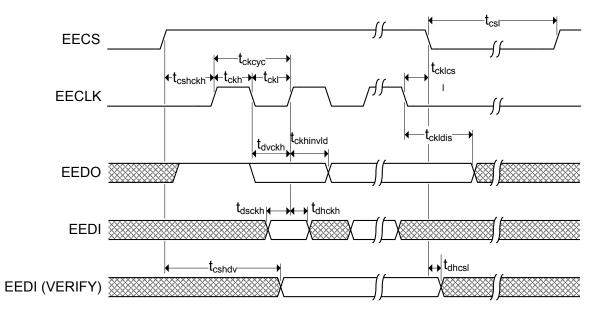

| EEPROM Timing                          | 48                                                                                                                                                                                                                                                                                                                                 |

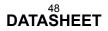

| JTAG Timing                            | 49                                                                                                                                                                                                                                                                                                                                 |

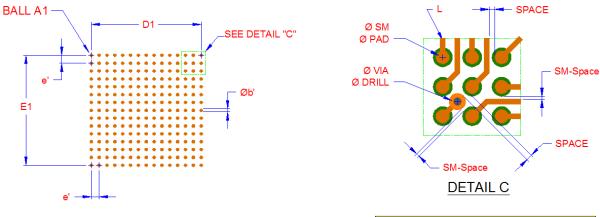

| 225-LFBGA Package Definition           | 51                                                                                                                                                                                                                                                                                                                                 |

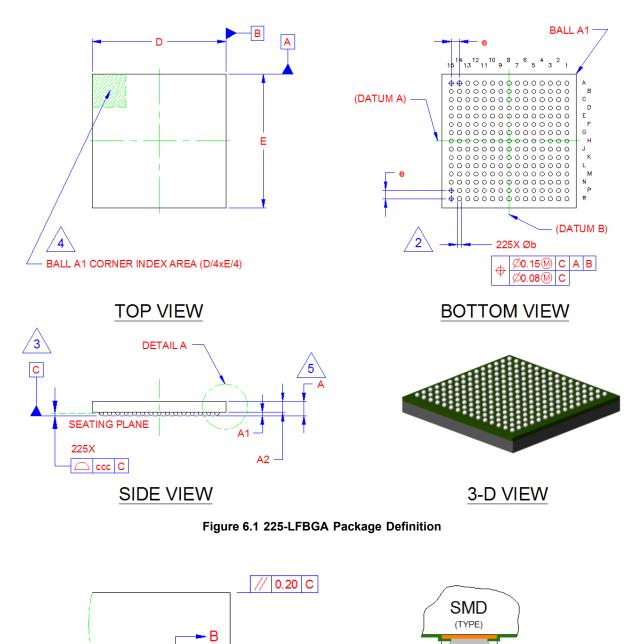

| 225-LFBGA Package Ball Detail          | 51                                                                                                                                                                                                                                                                                                                                 |

| 225-LFBGA Recommended PCB Land Pattern | 52                                                                                                                                                                                                                                                                                                                                 |

|                                        | Pin Assignments (TOP VIEW)         Power Connections         Power-On Timing         nRESET Power-On Timing         nRESET Timing         Digital RGB Timing - DDR Mode         Digital RGB Timing - SDR Mode         EEPROM Timing         JTAG Timing         225-LFBGA Package Definition         225-LFBGA Package Ball Detail |

# **List Of Tables**

| Table 2.1  | USB Pins                                            | . 9 |

|------------|-----------------------------------------------------|-----|

| Table 2.2  | Digital RGB Pins                                    | 10  |

| Table 2.3  | RGB / DDR Mode Mapping Table                        | 15  |

| Table 2.4  | VDAC Pins.                                          |     |

| Table 2.5  | DDR2 Memory Pins.                                   | 18  |

|            | HDMI Pins                                           |     |

|            | EEPROM Pins                                         |     |

|            | JTAG Pins                                           |     |

|            | Miscellaneous Pins                                  |     |

|            | I/O Power Pins, Core Power Pins, and Ground Pins.   |     |

|            | No-Connect Pins                                     |     |

|            | 225-LFBGA Package Pin Assignments                   |     |

| Table 2.13 | Buffer Types                                        | 28  |

|            | EEPROM Format                                       |     |

| Table 4.2  | Configuration Flags 0                               |     |

| Table 4.3  | Configuration Flags 1                               |     |

| Table 4.4  | Configuration Flags 2                               |     |

| Table 4.5  | Configuration Flags 3                               |     |

| Table 4.6  | EEPROM Defaults                                     |     |

| Table 5.1  | Package Thermal Parameters                          |     |

| Table 5.2  | SUSPEND Supply Current                              |     |

| Table 5.3  | Typical Super-Speed Operational Supply Current (mA) |     |

| Table 5.4  | Typical High-Speed Operational Supply Current (mA)  |     |

| Table 5.5  | I/O Buffer Characteristics                          |     |

|            | Video DAC - DC Characteristics                      |     |

| Table 5.7  | Power-On Timing Values                              | 43  |

|            | nRESET Power-On Timing Values                       |     |

|            | nRESET Timing Values                                |     |

|            | Video DAC - AC Characteristics                      |     |

| Table 5.11 | Digital RGB Timing Values - DDR Mode                | 46  |

|            | Digital RGB Timing Values - SDR Mode                |     |

| Table 5.13 | EEPROM Timing Values                                | 48  |

|            | JTAG Timing Values                                  |     |

|            | Crystal Specifications                              |     |

|            | 225-LFBGA Package Parameters                        |     |

| Table 7.1  | Customer Revision History                           | 53  |

# **Chapter 1 Introduction**

The UFX7000 is a high performance USB 3.0 graphics adapter with multiple graphics interfaces. The UFX7000 is an ideal solution for extending a PC workspace to an additional monitor without the need for an additional internal graphics card. With applications ranging from docking stations, USB port replicators, USB monitors/projectors, and embedded systems, the UFX7000 is targeted as a high performance, low cost USB-to-graphics solution.

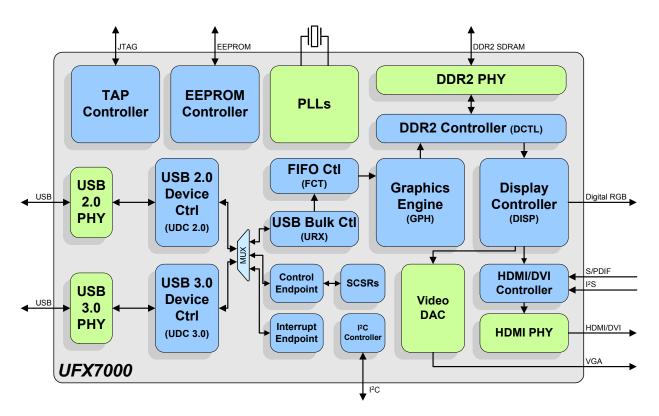

The UFX7000 contains integrated USB 3.0 and 2.0 Device Controllers, USB 3.0 and 2.0 PHYs, a USB Bulk-Out Controller, Control Endpoint, Interrupt-In Endpoint, DDR2 SDRAM Controller/PHY, Graphics Engine, HDMI/DVI Controller/PHY, Video DAC, TAP Controller, EEPROM Controller, and I<sup>2</sup>C Controller. Figure 1.1 details an internal block diagram of the UFX7000.

Figure 1.1 Internal Block Diagram

## 1.1 USB Device Controller

The USB Device Controller is fully compliant with the USB 3.0 Specification, enabling the device to operate in Super-Speed (5 Gbps) or Hi-Speed (480 Mbps) mode. Integrated USB 3.0 and 2.0 PHYs are provided on the USB port.

The controller implements three USB endpoints: Control, Bulk-Out, and Interrupt-In. The Bulk-Out endpoint allows for uncompressed or compressed graphics data reception from the USB port. The USB Bulk-Out Controller collects the graphics information and transfers it to the Graphics Engine. Implementation of vendor-specific commands allows for access to the device System Control and Status Registers (SCSRs).

## 1.2 Graphics Subsystem

The Graphics Subsystem consists of the following main blocks: the Graphics Engine, Display Controller, HDMI/DVI Controller/PHY, Video DAC, and the Digital RGB Interface. Together, these blocks support high definition resolutions of up to 2048x1152 (QWXGA) with 32-bit true color in both standard and wide screen aspect ratios. The HDMI/DVI interface is compliant with the HDMI v1.3 and DVI v1.0 specifications and supports 2-channel uncompressed PCM audio via a S/PDIF or I<sup>2</sup>S input. The Display Controller also supports 8-bit and 16-bit color, gamma correction, Color Look-Up Table (CLUT) and triple-buffered animations. The DDC2B/EDID VESA standard is supported, allowing the host OS and device drivers to query the monitor's frequency, resolution, and other features for true plug-and-play and intelligent mode setting capabilities.

Once the graphics data has been received via the USB Bulk-Out Controller, it is sent to the Graphics Engine. If the data is compressed, the Graphics Engine decompresses it via algorithms that have been optimized for speed and quality. The device's decompression algorithms have been designed to work seamlessly with the compression algorithms utilized in the software device drivers.

The graphics data is then transferred to the SDRAM via the DDR2 SDRAM Controller. The Display Controller generates all display and interface timing signals, retrieves the graphics data from the DDR2 SDRAM, and sends it to the HDMI/DVI Controller/PHY, Video DAC, or Digital RGB Interface.

The Digital RGB Interface may be used to connect external display interface IC's (e.g., DisplayPort, etc.) via the provided RGB data channel busses and control signals. The Digital RGB Interface supports two modes of operation: 24-bit single data rate mode and 12/15-bit double data rate mode. 24-bit mode is single edge triggered and utilizes the full 24-bit data bus width. The 12/15-bit mode is triggered on both clock edges and utilizes 12/15-bits of the data bus width.

### 1.3 DDR2 SDRAM Interface

The UFX7000 provides a full JEDEC compliant (JESD79-2E) DDR2 SDRAM Controller and PHY for interfacing to external DDR2 SDRAM. The DDR2 SDRAM interface is comprised of JEDEC standard 1.8V I/O signals grouped into control signals, a 16-bit data bus, and a 13-bit address bus.

The DDR2 SDRAM Controller transfers the graphics data in and out of external SDRAM through the DDR2 SDRAM PHY. External SDRAM is used as storage for the graphics and acts a a buffer between the Graphics Engine and Display Controller.

### 1.4 Peripherals

The UFX7000 also contains an EEPROM Controller, I<sup>2</sup>C Controller, and TAP Controller.

The EEPROM Controller allows connection to an external EEPROM for automatic loading of static configuration data upon power-on, pin reset, or software reset. The EEPROM can be configured to load USB descriptors and USB device configuration.

The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

# **Chapter 2 Pin Description and Configuration**

SMSC

|              |                        |                        |                        |                    |           | 22                     |                        | GA                     |                        |                                  |            |                 |                     |                              |   |

|--------------|------------------------|------------------------|------------------------|--------------------|-----------|------------------------|------------------------|------------------------|------------------------|----------------------------------|------------|-----------------|---------------------|------------------------------|---|

|              |                        |                        |                        |                    |           | тс                     | OP VIE                 | EW                     |                        |                                  |            |                 |                     |                              |   |

| 1            | 2                      | 3                      | 4                      | 5                  | 6         | 7                      | 8                      | 9                      | 10                     | 11                               | 12         | 13              | 14                  | 15                           | - |

| DDRFIFOWE_IN |                        | DDRDQ7                 | nDDRDQS0               | DDRDM0             | ODRDQ1    | nDDRWE                 | DDRA10                 | DDRA3                  | DDRA9                  | DDRCK                            | nDDRCAS    | DDRA2           | DDRA4               | DDRA8                        | A |

| DDRVREF0     | ODRDQ5                 | DDRDQ0                 | DDRDQS0                | DDRDQ6             | DDRDQ3    | DDRCKE                 | DDRBA0                 | DDRA7                  | DDRA12                 | nDDRCK                           | nDDRCS     | DDRA6           | DDRA11              | vss                          | в |

|              | DDRDQ11                | DDRDQ12                | DDRDQ2                 | VDD18DDR           | DDRDQ4    | DDRBA1                 | DDRA1                  | DDRA5                  | nDDRRAS                | VDD18DDR                         | DDRA0      | DDRODT          | vss                 | EXTSWING                     | с |

| DDRDQS1      | ODRDM1                 | DDRDQ14                | VDD18DDR               | VDD18DDR           | DDRVREF2  | VDD18DDR               | VDD18DDR               | VDD18DDR               | VDD18DDR               | VDD18DDR                         | VDD18DDR   | VDD18DDR        | TX2P                | TX2N                         | D |

| nDDRDQS1     | DDRDQ8                 | DDRDQ15                | VDD18DDR               | VDD18DDR           | VDD12CORE | vss                    | VDD12CORE              | vss                    | VDD12CORE              | VDD18DDR                         | VSSHDMI    | VDD12HDMI       | TX1P                | TX1N                         | E |

| DDRDQ13      | ODRDQ10                | DDRVREF1               | VDD18DDR               | VDD12CORE          | vss       | vss                    | vss                    | vss                    | vss                    | VDD12CORE                        | VSSHDMI    | VDD12HDMI       | тхор                | TXON                         | F |

| VSSUSB3      | •<br>VSSUSB3           | VDD33USB3              | vss                    | vss                | vss       | vss                    | vss                    | vss                    | vss                    | VDD12CORE                        | VSSHDMI    | VDD12HDMI       | тхср                | TXCN                         | G |

| USB3TXDP     | USB3TXDM               | VDD12USB3              | VDD12USB3              | VDD12CORE          | vss       | vss                    | vss                    | vss                    | vss                    | VSSVDAC                          | IREF       | VSSVDAC         | VDACR               | nVDACR                       | н |

| USB3RXDP     | USB3RXDM               | VSSUSB3                | REXT                   | vss                | vss       | vss                    | vss                    | vss                    | vss                    | VDD33VDAC                        | VDD33VDAC  | VDD33VDAC       | VDACG               | nVDACG                       | J |

| GPIO27       | e<br>I2CSDA0           | I2CSCL1/<br>GPIO28     | I2CSCLO                | VDD12CORE          | vss       | vss                    | vss                    | vss                    | vss                    | VDACREF                          | VDAC_HSYNC | •<br>VDAC_VSYNC | VDACB               | nVDACB                       | к |

| USBDP        | USBDM                  | VBUS_DET               | AUDIO_DIS/<br>GPIO30   | VDD33IO            | VDD12CORE | vss                    | VDD12CORE              | vss                    | VDD12CORE              | VDD33IO                          | VDD33IO    | ●<br>WS/GPIO29  | MCLK/<br>GPIO25     | SPDIF/<br>I2SDATA/<br>GPIO26 | L |

| VDD33USB     | ●<br>NC                | HPD                    | VDATAB4/<br>VD3/GPIO20 | VDD33IO            | VDD33IO   | VDD33IO                | VDATAG4/<br>VD9/GPI012 | VDD33IO                | VDATAR5/<br>GPIO5      | VDD33IO                          |            | ●<br>INT        | EECS                | EECLK                        | м |

| ●<br>XI      | VDD12USBPLL            | USBRBIAS               | VDATAB3/<br>VD4/GPI019 | VDATAB0/<br>GPIO16 | nBLANK    | VDATAG7/<br>GPIO15     | VDATAG3/<br>GPIO11     | VDATAG0/<br>VD11/GPIO8 | VDATAR4/<br>VD13/GPIO4 | VDATAR1/<br>GPIO1                | тро        | nEXTRST         | NC                  | NC                           | N |

| •<br>xo      | •<br>SYSPLLG           | VDATAB6/<br>VD1/GPIO22 | VDATAB2/<br>VD5/GPI018 | HSYNC              | nVCLK     | VDATAG6/<br>VD7/GPI014 | VDATAG2/<br>GPIO10     | VDATAR7/<br>VD12/GPI07 | VDATAR3/<br>VD14/GPIO3 | VDATAR0/<br>I2SCLKALT0/<br>GPIO0 | тск        | nSW_MODE        | nRESET              | EEDI                         | Р |

| SYSPLLP      | VDATAB7/<br>VD0/GPI023 | VDATAB5/<br>VD2/GPIO21 | VDATAB1/<br>VD6/GPI017 | VSYNC              | VCLK      | VDATAG5/<br>VD8/GPI013 | VDATAG1/<br>VD10/GPI09 | VDATAR6/<br>GPIO6      | VDATAR2/<br>VD15/GPI02 | nTRST                            | тмя        | ●<br>NC         | LED/<br>I2SCLKALT1/ | EEDO                         | R |

Figure 2.1 Pin Assignments (TOP VIEW)

| NUM PINS | NAME                                        | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                  |

|----------|---------------------------------------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | USB<br>DMINUS                               | USBDM    | AIO            | USB Data Minus.<br>Note: The functionality of this pin may be<br>swapped to USB DPLUS via the Port<br>Swap bit of Configuration Flags 0 of the<br>EEPROM.                                    |

| 1        | USB<br>DPLUS                                | USBDP    | AIO            | USB Data Plus.<br>Note: The functionality of this pin may be<br>swapped to USB DMINUS via the Port<br>Swap bit of Configuration Flags 0 of the<br>EEPROM.                                    |

| 1        | External USB<br>Bias Resistor               | USBRBIAS | AI             | Used for setting HS transmit current level and on-<br>chip termination impedance. Connect to an<br>external 12K 1.0% resistor to ground.                                                     |

| 1        | Crystal Input                               | XI       | ICLK           | External 25 MHz crystal input.<br><b>Note:</b> This pin can also be driven by a single-<br>ended clock oscillator. When this<br>method is used, XO should be left<br>unconnected. (Note 2.1) |

| 1        | Crystal<br>Output                           | XO       | OCLK           | External 25 MHz crystal output.                                                                                                                                                              |

| 1        | USB3 RX<br>DMINUS                           | USB3RXDM | AIO            | Super-Speed Differential Receive Minus.                                                                                                                                                      |

| 1        | USB3 RX<br>DPLUS                            | USB3RXDP | AIO            | Super-Speed Differential Receive Plus.                                                                                                                                                       |

| 1        | USB3 TX<br>DMINUS                           | USB3TXDM | AIO            | Super-Speed Differential Transmit Minus.                                                                                                                                                     |

| 1        | USB3 TX<br>DPLUS                            | USB3TXDP | AIO            | Super-Speed Differential Transmit Plus.                                                                                                                                                      |

| 1        | USB3<br>External<br>Reference<br>Resistance | REXT     | AI             | Connect to an external 200 ohm 1.0% resistor to ground.                                                                                                                                      |

Table 2.1 USB Pins

**Note 2.1** A 25MHz oscillator, or other single-ended clock source that meets the specifications in Section 5.5, "DC Specifications," on page 41 and Section 5.7, "Clock Circuit," on page 50, is required when utilizing the Digital RGB interface. Do not use a crystal when operating in Digital RGB mode.

| NUM PINS | NAME                                | SYMBOL  | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                |

|----------|-------------------------------------|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Video Clock<br>High                 | VCLK    | RGB                               | Active high video clock.                                                                                                                   |

| 1        | Video Clock<br>Low                  | nVCLK   | RGB                               | Active low video clock.                                                                                                                    |

| 1        | Horizontal<br>Sync                  | HSYNC   | RGB                               | Video horizontal synchronization output.                                                                                                   |

| 1        | Vertical Sync                       | VSYNC   | RGB                               | Video vertical synchronization output.                                                                                                     |

| 1        | Video<br>Blanking                   | nBLANK  | RGB                               | Active low video blanking signal.                                                                                                          |

|          | Blue Pixel<br>Data Channel<br>Bit 7 | VDATAB7 | RGB                               | Blue Pixel Video Data Bit 7, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 0                   | VD0     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>23        | GPIO23  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Blue Pixel<br>Data Channel<br>Bit 6 | VDATAB6 | RGB                               | Blue Pixel Video Data Bit 6, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 1                   | VD1     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>22        | GPIO22  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Blue Pixel<br>Data Channel<br>Bit 5 | VDATAB5 | RGB                               | Blue Pixel Video Data Bit 5, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 2                   | VD2     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>21        | GPIO21  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Blue Pixel<br>Data Channel<br>Bit 4 | VDATAB4 | RGB                               | Blue Pixel Video Data Bit 4, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 3                   | VD3     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>20        | GPIO20  | IS/08/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

#### Table 2.2 Digital RGB Pins

Revision 1.4 (06-24-13)

|          |                                      |         |                                   | 1                                                                                                                                          |

|----------|--------------------------------------|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                 | SYMBOL  | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                |

|          | Blue Pixel<br>Data Channel<br>Bit 3  | VDATAB3 | RGB                               | Blue Pixel Video Data Bit 3, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 4                    | VD4     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>19         | GPIO19  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Blue Pixel<br>Data Channel<br>Bit 2  | VDATAB2 | RGB                               | Blue Pixel Video Data Bit 2, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 5                    | VD5     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>18         | GPIO18  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

|          | Blue Pixel<br>Data Channel<br>Bit 1  | VDATAB1 | RGB                               | Blue Pixel Video Data Bit 1, RGB Single Ended Mode.                                                                                        |

| 1        | DDR RGB<br>Data 6                    | VD6     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>17         | GPIO17  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

|          | Blue Pixel<br>Data Channel<br>Bit 0  | VDATAB0 | RGB                               | Blue Pixel Video Data Bit 0, RGB Single Ended Mode.                                                                                        |

| 1        | General<br>Purpose I/O<br>16         | GPIO16  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

|          | Green Pixel<br>Data Channel<br>Bit 7 | VDATAG7 | RGB                               | Green Pixel Video Data Bit 7, RGB Single Ended Mode.                                                                                       |

| 1        | General<br>Purpose I/O<br>15         | GPIO15  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

Table 2.2 Digital RGB Pins (continued)

### Table 2.2 Digital RGB Pins (continued)

| NUM PINS | NAME                                 | SYMBOL  | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                |

|----------|--------------------------------------|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          | Green Pixel<br>Data Channel<br>Bit 6 | VDATAG6 | RGB                               | Green Pixel Video Data Bit 6, RGB Single Ended Mode.                                                                                       |

| 1        | DDR RGB<br>Data 7                    | VD7     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>14         | GPIO14  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Green Pixel<br>Data Channel<br>Bit 5 | VDATAG5 | RGB                               | Green Pixel Video Data Bit 5, RGB Single Ended Mode.                                                                                       |

| 1        | DDR RGB<br>Data 8                    | VD8     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>13         | GPIO13  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Green Pixel<br>Data Channel<br>Bit 4 | VDATAG4 | RGB                               | Green Pixel Video Data Bit 4, RGB Single Ended Mode.                                                                                       |

| 1        | DDR RGB<br>Data 9                    | VD9     | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O<br>12         | GPIO12  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Green Pixel<br>Data Channel<br>Bit 3 | VDATAG3 | RGB                               | Green Pixel Video Data Bit 3, RGB Single Ended Mode.                                                                                       |

| 1        | General<br>Purpose I/O<br>11         | GPIO11  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Green Pixel<br>Data Channel<br>Bit 2 | VDATAG2 | RGB                               | Green Pixel Video Data Bit 2, RGB Single Ended Mode.                                                                                       |

| 1        | General<br>Purpose I/O<br>10         | GPIO10  | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

| NUM PINS | NAME                                 | SYMBOL  | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                |  |  |  |  |

|----------|--------------------------------------|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | Green Pixel<br>Data Channel<br>Bit 1 | VDATAG1 | RGB                               | Green Pixel Video Data Bit 1, RGB Single Ended Mode.                                                                                       |  |  |  |  |

| 1        | DDR RGB<br>Data 10                   | VD10    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |  |  |  |  |

|          | General<br>Purpose I/O 9             | GPIO9   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |  |  |  |  |

|          | Green Pixel<br>Data Channel<br>Bit 0 | VDATAG0 | RGB                               | Green Pixel Video Data Bit 0, RGB Single Ended Mode.                                                                                       |  |  |  |  |

| 1        | DDR RGB<br>Data 11                   | VD11    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |  |  |  |  |

|          | General<br>Purpose I/O 8             | GPIO8   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |  |  |  |  |

|          | Red Pixel<br>Data Channel<br>Bit 7   | VDATAR7 | RGB                               | Red Pixel Video Data Bit 7, RGB Single Ended Mode.                                                                                         |  |  |  |  |

| 1        | DDR RGB<br>Data 12                   | VD12    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |  |  |  |  |

|          | General<br>Purpose I/O 7             | GPIO7   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |  |  |  |  |

|          | Red Pixel<br>Data Channel<br>Bit 6   | VDATAR6 | RGB                               | Red Pixel Video Data Bit 6, RGB Single Ended Mode.                                                                                         |  |  |  |  |

| 1        | General<br>Purpose I/O 6             | GPIO6   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |  |  |  |  |

|          | Red Pixel<br>Data Channel<br>Bit 5   | VDATAR5 | RGB                               | Red Pixel Video Data Bit 5, RGB Single Ended Mode.                                                                                         |  |  |  |  |

| 1        | General<br>Purpose I/O 5             | GPIO5   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |  |  |  |  |

Table 2.2 Digital RGB Pins (continued)

### Table 2.2 Digital RGB Pins (continued)

| NUM PINS | NAME                               | SYMBOL  | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                |

|----------|------------------------------------|---------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          | Red Pixel<br>Data Channel<br>Bit 4 | VDATAR4 | RGB                               | Red Pixel Video Data Bit 4, RGB Single Ended Mode.                                                                                         |

| 1        | DDR RGB<br>Data 13                 | VD13    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O4            | GPIO4   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Red Pixel<br>Data Channel<br>Bit 3 | VDATAR3 | RGB                               | Red Pixel Video Data Bit 3, RGB Single Ended Mode.                                                                                         |

| 1        | DDR RGB<br>Data 14                 | VD14    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O 3           | GPIO3   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Red Pixel<br>Data Channel<br>Bit 2 | VDATAR2 | RGB                               | Red Pixel Video Data Bit 2, RGB Single Ended Mode.                                                                                         |

| 1        | DDR RGB<br>Data 15                 | VD15    | RGB                               | Used in RGB DDR Mode, refer to Table 2.3.                                                                                                  |

|          | General<br>Purpose I/O 2           | GPIO2   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input. |

|          | Red Pixel<br>Data Channel<br>Bit 1 | VDATAR1 | RGB                               | Red Pixel Video Data Bit 1, RGB Single Ended Mode.                                                                                         |

| 1        | General<br>Purpose I/O 1           | GPIO1   | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.       |

| NUM PINS | NAME                                           | SYMBOL     | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                   |

|----------|------------------------------------------------|------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|          | Red Pixel<br>Data Channel<br>Bit 0             | VDATAR0    | RGB                               | Red Pixel Video Data Bit 0, RGB Single Ended Mode.                                                                                            |

|          | I <sup>2</sup> S Clock<br>Alternate<br>Input 0 | I2SCLKALT0 | IS                                | I <sup>2</sup> S Clock alternate input 0. The I <sup>2</sup> S clock input<br>pin is selectable between the I2SCLKALT0 or<br>I2SCLKALT1 pins. |

| 1        |                                                |            |                                   | Note: If the single data rate RGB interface is<br>enabled, I2SCLKALT1 should be used.<br>I2SCLKALT0 should be used in all other<br>cases.     |

|          | General GPIO0<br>Purpose I/O 0                 |            | IS/O8/<br>OD8<br>(PU)<br>Note 2.2 | This General Purpose I/O pin is fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input.          |

Table 2.2 Digital RGB Pins (continued)

**Note:** A 25MHz oscillator, or other single-ended clock source that meets the specifications in Section 5.5, "DC Specifications," on page 41 and Section 5.7, "Clock Circuit," on page 50, is required when utilizing the Digital RGB interface. Do not use a crystal when operating in Digital RGB mode.

Note 2.2 The internal pull-up is disabled when the GPIO is configured as an O8 buffer type.

| SDR           |          | DDR (12-6           | BIT MODE)            | DDR (15-BIT MODE)   |                      |  |  |  |  |  |  |

|---------------|----------|---------------------|----------------------|---------------------|----------------------|--|--|--|--|--|--|

| (24-BIT MODE) | DDR NAME | VCLK<br>RISING EDGE | VCLK<br>FALLING EDGE | VCLK<br>RISING EDGE | VCLK<br>FALLING EDGE |  |  |  |  |  |  |

| VCLK          |          |                     |                      |                     |                      |  |  |  |  |  |  |

|               | nVCLK    |                     |                      |                     |                      |  |  |  |  |  |  |

|               |          | HS                  | SYNC                 |                     |                      |  |  |  |  |  |  |

|               |          | VS                  | YNC                  |                     |                      |  |  |  |  |  |  |

|               |          | nBl                 | _ANK                 |                     |                      |  |  |  |  |  |  |

| VDATAB7       | VD0      | -                   | -                    | BLUE0               | GREEN5               |  |  |  |  |  |  |

| VDATAB6       | VD1      | -                   | -                    | BLUE1               | GREEN6               |  |  |  |  |  |  |

| VDATAB5       | VD2      | BLUE0               | GREEN4               | BLUE2               | GREEN7               |  |  |  |  |  |  |

| VDATAB4       | VD3      | BLUE1               | GREEN5               | BLUE3               | GREEN8               |  |  |  |  |  |  |

| VDATAB3       | VD4      | BLUE2               | GREEN6               | BLUE4               | GREEN9               |  |  |  |  |  |  |

| VDATAB2       | VD5      | BLUE3               | GREEN7               | BLUE5               | RED0                 |  |  |  |  |  |  |

| VDATAB1       | VD6      | BLUE4               | RED0                 | BLUE6               | RED1                 |  |  |  |  |  |  |

| VDATAB0       | VDATABO  |                     | -                    | -                   | -                    |  |  |  |  |  |  |

| VDATAG7       | -        | -                   | -                    | -                   | -                    |  |  |  |  |  |  |

#### Table 2.3 RGB / DDR Mode Mapping Table

| SDR           |                      | DDR (12-6 | BIT MODE)            | DDR (15-BIT MODE)   |                      |  |

|---------------|----------------------|-----------|----------------------|---------------------|----------------------|--|

| (24-BIT MODE) | 4-BIT MODE) DDR NAME |           | VCLK<br>FALLING EDGE | VCLK<br>RISING EDGE | VCLK<br>FALLING EDGE |  |

| VDATAG6       | VD7                  | BLUE5     | RED1                 | BLUE7               | RED2                 |  |

| VDATAG5       | VD8                  | BLUE6     | RED2                 | BLUE8               | RED3                 |  |

| VDATAG4       | VD9                  | BLUE7     | RED3                 | BLUE9               | RED4                 |  |

| VDATAG3       | -                    | -         | -                    | -                   | -                    |  |

| VDATAG2       | -                    | -         | -                    | -                   | -                    |  |

| VDATAG1       | VD10                 | -         | -                    | GREEN0              | RED5                 |  |

| VDATAG0       | VD11                 | -         | -                    | GREEN1              | RED6                 |  |

| VDATAR7       | VD12                 | GREEN0    | RED4                 | GREEN2              | RED7                 |  |

| VDATAR6       | -                    | -         | -                    | -                   | -                    |  |

| VDATAR5       | -                    | -         | -                    | -                   | -                    |  |

| VDATAR4       | VD13                 | GREEN1    | RED5                 | GREEN3              | RED8                 |  |

| VDATAR3       | VD14                 | GREEN2    | RED6                 | GREEN4              | RED9                 |  |

| VDATAR2       | VD15                 | GREEN3    | RED7                 | -                   | -                    |  |

| VDATAR1       | -                    | -         | -                    | -                   | -                    |  |

| VDATAR0       | -                    | -         | -                    | -                   | -                    |  |

#### Table 2.3 RGB / DDR Mode Mapping Table (continued)

#### Table 2.4 VDAC Pins

| NUM PINS | NAME                               | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                |

|----------|------------------------------------|------------|----------------|--------------------------------------------|

| 1        | VDAC<br>VSYNC                      | VDAC_VSYNC | RGB            | VDAC vertical synchronization output.      |

| 1        | VDAC<br>HSYNC                      | VDAC_HSYNC | RGB            | VDAC horizontal synchronization output.    |

| 1        | Positive Red<br>Analog<br>Output   | VDACR      | AO             | Positive Red VDAC analog output current.   |

| 1        | Negative Red<br>Analog<br>Output   | nVDACR     | AO             | Negative Red VDAC analog output current.   |

| 1        | Positive<br>Green Analog<br>Output | VDACG      | AO             | Positive Green VDAC analog output current. |

| 1        | Negative<br>Green Analog<br>Output | nVDACG     | AO             | Negative Green VDAC analog output current. |

| NUM PINS | NAME                              | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                           |

|----------|-----------------------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Positive Blue<br>Analog<br>Output | VDACB  | AO             | Positive Blue VDAC analog output current.                                                                                                             |

| 1        | Negative Blue<br>Analog<br>Output | nVDACB | AO             | Negative Blue VDAC analog output current.                                                                                                             |

| 1        | VDAC<br>Reference<br>Current      | IREF   | AI             | VDAC reference current. Output current when<br>using External Reference Resistor or Input<br>Reference Current when using external current<br>source. |

### Table 2.4 VDAC Pins (continued)

| NUM PINS | NAME                                          | SYMBOL      | BUFFER<br>TYPE  | DESCRIPTION                                                     |  |

|----------|-----------------------------------------------|-------------|-----------------|-----------------------------------------------------------------|--|

| 13       | DDR2<br>Memory<br>Address Bus                 | DDRA[12:0]  | DDR2O           | Bits 12:0 of the external DDR2 memory address bus.              |  |

| 16       | DDR2<br>Memory Data<br>Bus                    | DDRDQ[15:0] | DDR2I/<br>DDR2O | Bits 15:0 of the external DDR2 memory data bus.                 |  |

| 2        | DDR2<br>Memory Bank<br>Address                | DDRBA[1:0]  | DDR2O           | DDR2 memory bank address.                                       |  |

| 1        | DDR2<br>Memory<br>Clock High                  | DDRCK       | DDR2O           | Active high DDR2 clock. This clock is the complement of nDDRCK. |  |

| 1        | DDR2<br>Memory<br>Clock Low                   | nDDRCK      | DDR2O           | Active low DDR2 clock. This clock is the complement of DDRCK.   |  |

| 1        | DDR2<br>Memory<br>Clock Enable<br>Output      | DDRCKE      | DDR2O           | DDR2 clock enable signal.                                       |  |

| 1        | DDR2<br>Memory Chip<br>Select                 | nDDRCS      | DDR2O           | Active low chip select.                                         |  |

| 1        | DDR2<br>Memory Row<br>Address<br>Strobe       | nDDRRAS     | DDR2O           | Active low row address strobe.                                  |  |

| 1        | DDR2<br>Memory<br>Column<br>Address<br>Strobe | nDDRCAS     | DDR2O           | Active low column address strobe.                               |  |

| 1        | DDR2<br>Memory Write<br>Enable                | nDDRWE      | DDR2O           | Active low write enable.                                        |  |

| 1        | DDR2 On Die<br>Termination                    | DDRODT      | DDR2O           | DDR2 on die termination.                                        |  |

| 1        | DDR2<br>Memory<br>Lower Byte<br>Mask          | DDRDM0      | DDR2O           | Mask bit for lower byte of DDR2 data word.                      |  |

| 1        | DDR2<br>Memory<br>Upper Byte<br>Mask          | DDRDM1      | DDR2O           | Mask bit for upper byte of DDR2 data word.                      |  |

#### Table 2.5 DDR2 Memory Pins

|          |                                             |               | 1               | 1                                                                                              |

|----------|---------------------------------------------|---------------|-----------------|------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                        | SYMBOL        | BUFFER<br>TYPE  | DESCRIPTION                                                                                    |

| 1        | DDR2<br>Memory<br>Lower Byte<br>Strobe High | DDRDQS0       | DDR2I/<br>DDR2O | Active high data strobe for lower byte of DDR2 data word.                                      |

| 1        | DDR2<br>Memory<br>Lower Byte<br>Strobe Low  | nDDRDQS0      | DDR2I/<br>DDR2O | Active low data strobe for upper byte of DDR2 data word.                                       |

| 1        | DDR2<br>Memory<br>Upper Byte<br>Strobe High | DDRDQS1       | DDR2I/<br>DDR2O | Active high data strobe for upper byte of DDR2 data word.                                      |

| 1        | DDR2<br>Memory<br>Upper Byte<br>Strobe Low  | nDDRDQS1      | DDR2I/<br>DDR2O | Active low data strobe for upper byte of DDR2 data word.                                       |

| 1        | DDR2<br>Memory<br>Reference<br>Voltage 0    | DDRVREF0      | AI              | Reference voltage input pin for DDR2 Memory.<br>DDRVREF0 must be half the VDD18DDR<br>voltage. |

| 1        | DDR2<br>Memory<br>Reference<br>Voltage 1    | DDRVREF1      | AI              | Reference voltage input pin for DDR2 Memory.<br>DDRVREF1 must be half the VDD18DDR<br>voltage. |

| 1        | DDR2<br>Memory<br>Reference<br>Voltage 2    | DDRVREF2      | AI              | Reference voltage input pin for DDR2 Memory.<br>DDRVREF2 must be half the VDD18DDR<br>voltage. |

| 1        | DQS Enable<br>Timing Match<br>Input         | DDRFIFOWE_IN  | DDR2I           | DQS enable input for timing match between DQS and system clock.                                |

| 1        | DQS Enable<br>Timing Match<br>Output        | DDRFIFOWE_OUT | DDR2O           | DQS enable output for timing match between DQS and system clock.                               |

### Table 2.5 DDR2 Memory Pins (continued)

#### Table 2.6 HDMI Pins

| NUM PINS | NAME                      | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                     |

|----------|---------------------------|--------|----------------|-------------------------------------------------|

| 1        | TMDS<br>Clock<br>Positive | ТХСР   | AO             | TMDS clock output differential positive signal. |

| 1        | TMDS Clock<br>Negative    | TXCN   | AO             | TMDS clock output differential negative signal. |

| 1        | TMDS Out0<br>Positive     | TX0P   | AO             | TMDS Output 0 differential positive signal.     |

|          |                         |          | 1              |                                                                                                                                                                                             |

|----------|-------------------------|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                    | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                 |

| 1        | TMDS Out0<br>Negative   | TX0N     | AO             | TMDS Output 0 differential negative signal.                                                                                                                                                 |

| 1        | TMDS Out1<br>Positive   | TX1P     | AO             | TMDS Output 1 differential positive signal.                                                                                                                                                 |

| 1        | TMDS Out1<br>Negative   | TX1N     | AO             | TMDS Output 1 differential negative signal.                                                                                                                                                 |

| 1        | TMDS Out2<br>Positive   | TX2P     | AO             | TMDS Output 2 differential positive signal.                                                                                                                                                 |

| 1        | TMDS Out2<br>Negative   | TX2N     | AO             | TMDS Output 2 differential negative signal.                                                                                                                                                 |

| 1        | Voltage<br>Swing Adjust | EXTSWING | AI             | Connect this pin to an external resistor going to ground. The resistor determines the amplitude of the voltage swing. A low capacitive connection is allowed. A value of 5K is recommended. |

| 1        | Hot Plug<br>Detect      | HPD      | IS             | Hot plug detect signal.                                                                                                                                                                     |

#### Table 2.6 HDMI Pins (continued)

#### Table 2.7 EEPROM Pins

| NUM PINS | NAME                  | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | EEPROM<br>Data In     | EEDI   | IS<br>(PD)     | This pin is driven by the EEDO output of the external EEPROM.                                                                                                                                                                                                                                                                                                                                                             |

| 1        | EEPROM<br>Data Out    | EEDO   | 08             | <ul> <li>This pin drives the EEDI input of the external EEPROM.</li> <li>Note: This pin is also used for internal production test purposes and should never be pulled high. If connected to a load, use of an external 4.7K pull-down resistor is recommended.</li> </ul>                                                                                                                                                 |

| 1        | EEPROM<br>Chip Select | EECS   | O8             | <ul> <li>This pin drives the chip select output of the external EEPROM.</li> <li>Note: The EECS output may tri-state briefly during power-up. Some EEPROM devices may be prone to false selection during this time. When an EEPROM is used, an external pull-down resistor is recommended on this signal to prevent false selection. Refer to your EEPROM manufacturer's datasheet for additional information.</li> </ul> |

| 1        | EEPROM<br>Clock       | EECLK  | O8             | This pin drives the EEPROM clock of the external EEPROM.                                                                                                                                                                                                                                                                                                                                                                  |

| NUM PINS | NAME                     | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                    |

|----------|--------------------------|--------|----------------|--------------------------------------------------------------------------------|

| 1        | JTAG Test<br>Data Out    | TDO    | O8             | JTAG data output.                                                              |

| 1        | JTAG Test<br>Clock       | тск    | IS             | JTAG test clock.<br>The maximum operating frequency of this clock is<br>25MHz. |

| 1        | JTAG Test<br>Mode Select | TMS    | IS             | JTAG test mode select.                                                         |

| 1        | JTAG Test<br>Data Input  | TDI    | IS             | JTAG data input.                                                               |

| 1        | JTAG Test<br>Port Reset  | nTRST  | IS             | JTAG test port reset input.                                                    |

Table 2.8 JTAG Pins

#### Table 2.9 Miscellaneous Pins

| NUM PINS | NAME                                           | SYMBOL     | BUFFER<br>TYPE                    | DESCRIPTION                                                                                                                                                             |  |

|----------|------------------------------------------------|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | LED                                            | LED        | 08/<br>OD8<br>(PU)                | Can be used to provide device status.<br>Alternatively, the LED can be configured for a fast<br>or slow blink in accordance with the USB<br>graphics data receive rate. |  |

|          | I <sup>2</sup> S Clock<br>Alternate<br>Input 1 | I2SCLKALT1 | IS                                | I <sup>2</sup> S Clock alternate input 1. The I <sup>2</sup> S clock input<br>pin is selectable between the I2SCLKALT0 or<br>I2SCLKALT1 pins.                           |  |

| 1        |                                                |            |                                   | Note: If the single data rate RGB interface is<br>enabled, I2SCLKALT1 should be used.<br>I2SCLKALT0 should be used in all other<br>cases.                               |  |

|          | General<br>Purpose I/O<br>24                   | GPIO24     | IS/O8/<br>OD8<br>(PU)<br>Note 2.4 | This General Purpose I/O pin is fully<br>programmable as either a push-pull output, an<br>open-drain output, or a Schmitt-triggered input.                              |  |

| 1        | Interrupt                                      | INT        | IS                                | For use by external transmitter to signal an event requiring servicing.                                                                                                 |  |

| 1        | External<br>Reset Output                       | nEXTRST    | O8                                | Used to reset the external transmitter. The<br>polarity and period of the reset signal generated<br>on this pin is programmable via internal registers                  |  |

|          | Switching<br>Regulator<br>Mode                 | nSW_MODE   | O8                                | When asserted, this pin can be used to place the external switching regulator into power saving mode.                                                                   |  |

| 1        |                                                |            |                                   | Note: The SW_MODE Polarity bit of<br>Configuration Flags 0 controls the<br>polarity of the pin.                                                                         |  |

| Table 2.9 Miscellaneous | Pins | (continued) |

|-------------------------|------|-------------|

|-------------------------|------|-------------|

| NUM PINS | NAME                         | SYMBOL   | BUFFER<br>TYPE                        | DESCRIPTION                                                                                                                                                                                                                                                                      |

|----------|------------------------------|----------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | System Reset<br>Input        | nRESET   | IS                                    | This active-low pin allows external hardware to reset the device.                                                                                                                                                                                                                |

| I        |                              |          |                                       | Note: Assertion of nRESET is required following power-on.                                                                                                                                                                                                                        |

|          | Detect<br>Upstream           | VBUS_DET | IS                                    | Detects the state of the upstream bus power.                                                                                                                                                                                                                                     |

| 1        | VBUS Power                   |          |                                       | For bus powered operation, this pin must be tied to VDD33IO.                                                                                                                                                                                                                     |

|          |                              |          |                                       | For self powered operation, refer to the device reference schematics.                                                                                                                                                                                                            |