### **Ordering Information**

| Part Number | Part Marking | Input | Junction Temperature Range | Package                   |

|-------------|--------------|-------|----------------------------|---------------------------|

| MIC4604YMT  | 463          | TTL   | –40° to +125°C             | 10-Pin 2.5mm × 2.5mm TDFN |

| MIC4604YM   | MIC4604 YM   | TTL   | –40° to +125°C             | 8-Pin SOIC                |

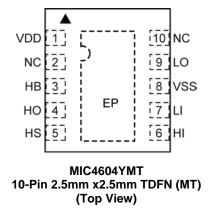

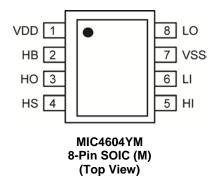

# **Pin Configurations**

### **Pin Description**

| Pin N | umber | Pin  | Die Erweiten                                                                                                                                                              |

|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDFN  | SOIC  | Name | Pin Function                                                                                                                                                              |

| 1     | 1     | VDD  | Input supply for gate drivers. Decouple this pin to VSS with a >2.2µF capacitor. Anode connection to internal bootstrap diode.                                            |

| 2, 10 |       | NC   | No Connect                                                                                                                                                                |

| 3     | 2     | НВ   | High-side bootstrap supply. External bootstrap capacitor is required. Connect bootstrap capacitor across this pin and HS. Cathode connection to internal bootstrap diode. |

| 4     | 3     | НО   | High-side drive output. Connect to gate of the external high-side power MOSFET.                                                                                           |

| 5     | 4     | HS   | High-side drive reference connection. Connect to source of the external high-side power MOSFET. Connect this pin to the bootstrap capacitor.                              |

| 6     | 5     | HI   | High-side drive input.                                                                                                                                                    |

| 7     | 6     | LI   | Low-side drive input.                                                                                                                                                     |

| 8     | 7     | VSS  | Driver reference supply input. Connected to power ground of external circuitry and to source of low-side power MOSFET.                                                    |

| 9     | 8     | LO   | Low-side drive output. Connect to gate of the external low-side power MOSFET.                                                                                             |

| EP    |       | EPAD | Exposed pad. Connect to VSS.                                                                                                                                              |

# Absolute Maximum Ratings<sup>(1, 4)</sup>

| Supply Voltage (V <sub>DD</sub> , V <sub>HB</sub> – V <sub>HS</sub> ) –0.3V to 18V                   |

|------------------------------------------------------------------------------------------------------|

| Input Voltages (V <sub>LI</sub> , V <sub>HI</sub> , V <sub>EN</sub> )–0.3V to V <sub>DD</sub> + 0.3V |

| Voltage on LO (V <sub>LO</sub> ) –0.3V to V <sub>DD</sub> + 0.3V                                     |

| Voltage on HO (V <sub>HO</sub> )V <sub>HS</sub> – 0.3V to V <sub>HB</sub> + 0.3V                     |

| Voltage on HS (continuous)1V to 90V                                                                  |

| Voltage on HB108V                                                                                    |

| Average Current in VDD to HB Diode                                                                   |

| Storage Temperature (T <sub>s</sub> )–60°C to +150°C                                                 |

| ESD Rating <sup>(3)</sup>                                                                            |

| HBM1.5kV                                                                                             |

| MM200V                                                                                               |

# Operating Ratings<sup>(2)</sup>

| Supply Voltage ( $V_{DD}$ ) [decreasing $V_{DD}$ ] | 5.25V to 16V                |

|----------------------------------------------------|-----------------------------|

| Supply Voltage ( $V_{DD}$ ) [increasing $V_{DD}$ ] | 5.5V to 16V                 |

| Voltage on HS                                      | –1V to 85V                  |

| Voltage on HS (repetitive transient)               | –5V to 90V                  |

| HS Slew Rate                                       | 50V/ns                      |

| Voltage on HB $V_{HS}$ + 4.5                       | 5V to V <sub>HS</sub> + 16V |

| and/orV <sub>DD</sub> - 1                          | V to $V_{DD}$ + 85V         |

| Junction Temperature (T <sub>J</sub> )             | 40°C to +125°C              |

| Junction Thermal Resistance                        |                             |

| 2.5mm x 2.5mm TDFN-10L (θ <sub>JA</sub> )          | 75°C/W                      |

| SOIC-8L (θ <sub>JA</sub> )                         | 98.9°C/W                    |

## Electrical Characteristics<sup>(4)</sup>

$V_{DD} = V_{HB} = 12V$ ;  $V_{SS} = V_{HS} = 0V$ ; No load on LO or HO;  $T_A = +25^{\circ}C$ ; unless otherwise noted. Bold values indicate  $-40^{\circ}C \le T_{L} \le +125^{\circ}C$

| Symbol           | Parameter                               | Condition                                                | Min. | Тур. | Max. | Units |

|------------------|-----------------------------------------|----------------------------------------------------------|------|------|------|-------|

| Supply C         | urrent                                  | · · · ·                                                  |      |      |      |       |

| I <sub>DD</sub>  | V <sub>DD</sub> Quiescent Current       | LI = HI = 0V                                             |      | 48   | 200  | μA    |

| I <sub>DDO</sub> | V <sub>DD</sub> Operating Current       | f = 20kHz                                                |      | 136  | 300  | μA    |

| I <sub>HB</sub>  | Total HB Quiescent Current              | LI = HI = 0V  or  LI = 0V  and  HI = 5V                  |      | 20   | 75   | μA    |

| I <sub>HBO</sub> | Total HB Operating Current              | f = 20kHz                                                |      | 29   | 200  | μA    |

| I <sub>HBS</sub> | HB to V <sub>SS</sub> Quiescent Current | $V_{HS} = V_{HB} = 90V$                                  |      | 0.5  | 5    | μA    |

| Input (LI,       | HI)                                     |                                                          |      |      |      |       |

| VIL              | Low-Level Input Voltage                 |                                                          |      |      | 0.8  | V     |

| VIH              | High-Level Input Voltage                |                                                          | 2.2  |      |      | V     |

| V <sub>HYS</sub> | Input Voltage Hysteresis                |                                                          |      | 0.05 |      | V     |

| Rı               | Input Pull-Down Resistance              |                                                          | 100  | 240  | 500  | kΩ    |

| Undervol         | tage Protection                         |                                                          |      |      |      |       |

| V <sub>DDF</sub> | V <sub>DD</sub> Falling Threshold       |                                                          | 4.0  | 4.4  | 4.9  | V     |

| V <sub>DDH</sub> | V <sub>DD</sub> Threshold Hysteresis    | Rising $V_{DD}$ Threshold; $V_{DDR} = V_{DDF} + V_{DDH}$ |      | 0.21 |      | V     |

| V <sub>HBF</sub> | HB Falling Threshold                    |                                                          | 4.0  | 4.4  | 4.9  | V     |

| V <sub>HBH</sub> | HB Threshold Hysteresis                 | Rising $V_{HB}$ Threshold; $V_{HBR} = V_{HBF} + V_{HBH}$ |      | 0.23 |      | V     |

| Bootstrap        | Diode                                   |                                                          |      |      |      |       |

| V <sub>DL</sub>  | Low-Current Forward Voltage             | I <sub>VDD-HB</sub> = 100µА                              |      | 0.42 | 0.70 | V     |

| V <sub>DH</sub>  | High-Current Forward Voltage            | I <sub>VDD-HB</sub> = 50mA                               |      | 0.75 | 1.0  | V     |

| R <sub>D</sub>   | Dynamic Resistance                      | I <sub>VDD-HB</sub> = 50mA                               |      | 2.8  | 5.0  | Ω     |

#### Notes:

1. Exceeding the absolute maximum ratings may damage the device.

2. The device is not guaranteed to function outside its operating ratings.

3. Devices are ESD sensitive. Handling precautions are recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

4. Specification s are for packaged product only.

# Electrical Characteristics<sup>(4)</sup> (Continued)

$V_{DD} = V_{HB} = 12V; V_{SS} = V_{HS} = 0V; No \text{ load on LO or HO}; T_A = +25^{\circ}C; unless otherwise noted.$ Bold values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$

| Symbol             | Parameter                                                      | Condition                                           | Min. | Тур. | Max. | Units |

|--------------------|----------------------------------------------------------------|-----------------------------------------------------|------|------|------|-------|

| LO Gate            | Driver                                                         | ·                                                   |      |      |      |       |

| V <sub>OLL</sub>   | Low-Level Output Voltage                                       | $I_{LO} = 50 \text{mA}$                             |      | 0.17 | 0.4  | V     |

| V <sub>OHL</sub>   | High-Level Output Voltage                                      | $I_{LO} = -50 \text{mA}, V_{OHL} = V_{DD} - V_{LO}$ |      | 0.25 | 1.0  | V     |

| I <sub>OHL</sub>   | Peak Sink Current                                              | $V_{LO} = 5V$                                       |      | 1    |      | Α     |

| I <sub>OLL</sub>   | Peak Source Current                                            | $V_{LO} = 5V$                                       |      | 1    |      | А     |

| HO Gate            | Driver                                                         | -                                                   |      |      |      |       |

| V <sub>OLH</sub>   | Low-Level Output Voltage                                       | $I_{HO} = 50 \text{mA}$                             |      | 0.2  | 0.6  | V     |

| V <sub>OHH</sub>   | High-Level Output Voltage                                      | $I_{HO} = -50 \text{mA}, V_{OHH} = V_{HB} - V_{HO}$ |      | 0.22 | 1.0  | V     |

| I <sub>OHH</sub>   | Peak Sink Current                                              | V <sub>HO</sub> = 5V                                |      | 1.5  |      | Α     |

| I <sub>OLH</sub>   | Peak Source Current                                            | $V_{HO} = 5V$                                       |      | 1    |      | А     |

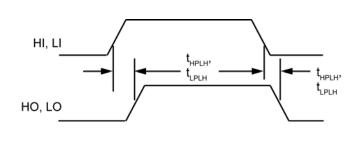

| Switchin           | g Specifications <sup>(5)</sup>                                | -                                                   |      |      |      |       |

| t <sub>LPHL</sub>  | Lower Turn-Off Propagation Delay<br>(LI Falling to LO Falling) |                                                     |      | 37   | 75   | ns    |

| t <sub>HPHL</sub>  | Upper Turn-Off Propagation Delay<br>(HI Falling to HO Falling) |                                                     |      | 34   | 75   | ns    |

| t <sub>LPLH</sub>  | Lower Turn-On Propagation Delay<br>(LI Rising to LO Rising)    |                                                     |      | 39   | 75   | ns    |

| t <sub>HPLH</sub>  | Upper Turn-On Propagation Delay<br>(HI Rising to HO Rising)    |                                                     |      | 33   | 75   | ns    |

| t <sub>RC/FC</sub> | Output Rise/Fall Time                                          | C <sub>L</sub> = 1000pF                             |      | 20   |      | ns    |

| t <sub>R/F</sub>   | Output Rise/Fall Time (3V to 9V)                               | $C_L = 0.1 \mu F$                                   |      | 0.8  |      | μs    |

| t <sub>PW</sub>    | Minimum Input Pulse Width that<br>Changes the Output           |                                                     |      | 50   |      | ns    |

| t <sub>BS</sub>    | Bootstrap Diode Turn-On or Turn-Off<br>Time                    |                                                     |      | 10   |      | ns    |

Note:

5. Guaranteed by design. Not production tested.

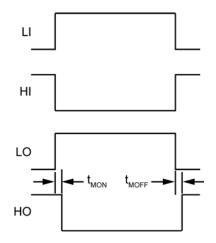

### **Timing Diagrams**

#### Note:

6. All propagation delays are measured from the 50% voltage level.

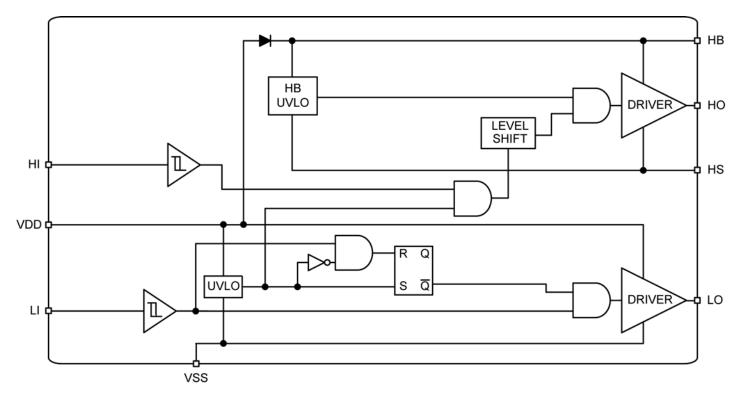

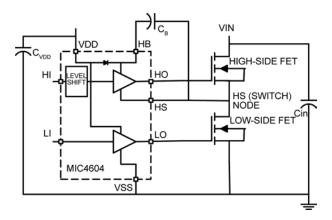

### **Block Diagram**

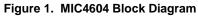

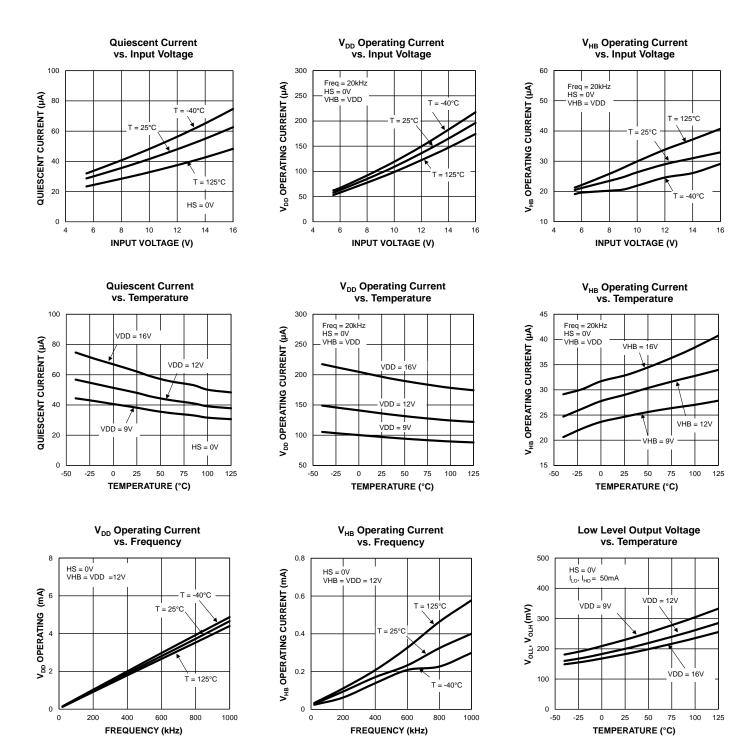

# **Typical Characteristics**

125

1.0

# **Typical Characteristics (Continued)**

REVERSE VOLTAGE (V)

### **Functional Description**

The MIC4604 is a high-voltage, non-inverting, dual MOSFET driver that is designed to independently drive both high-side and low-side N-Channel MOSFETs. The block diagram of the MIC4604 is shown in Figure 1.

Both drivers contain an input buffer with hysteresis, a UVLO circuit, and an output buffer. The high-side output buffer includes a high-speed level-shifting circuit that is referenced to the HS pin. An internal diode is used as part of a bootstrap circuit to provide the drive voltage for the high-side output.

### Startup and UVLO

The UVLO circuit forces the driver output low until the supply voltage exceeds the UVLO threshold. The low-side UVLO circuit monitors the voltage between the VDD and VSS pins. The high-side UVLO circuit monitors the voltage between the HB and HS pins. Hysteresis in the UVLO circuit prevents noise and finite circuit impedance from causing chatter during turn-on.

### Input Stage

Both the HI and LI pins of the MIC4604 are referenced to the VSS pin. The voltage state of the input signal does not change the quiescent current draw of the driver.

The MIC4604 has a TTL-compatible input range and can be used with input signals with amplitude less than the supply voltage. The threshold level is independent of the VDD supply voltage and there is no dependence between  $I_{VDD}$  and the input signal amplitude with the MIC4604. This feature makes the MIC4604 an excellent level translator that will drive high-threshold MOSFETs from a low-voltage PWM IC.

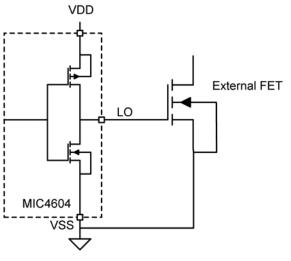

### Low-Side Driver

A block diagram of the low-side driver is shown in Figure 2. The low-side driver is designed to drive a ground (VSS pin) referenced N-channel MOSFET. Low driver impedances allow the external MOSFET to be turned on and off quickly. The rail-to-rail drive capability of the output ensures a low  $R_{D}s_{ON}$  from the external MOSFET.

A high level applied to LI pin causes the upper driver MOSFET to turn on and VDD voltage is applied to the gate of the external MOSFET. A low level on the LI pin turns off the upper driver and turns on the low side driver to ground the gate of the external MOSFET.

Figure 2. Low-Side Driver Block Diagram

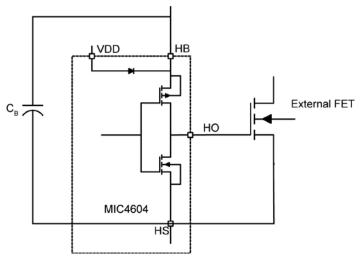

### High-Side Driver and Bootstrap Circuit

A block diagram of the high-side driver and bootstrap circuit is shown in Figure 3. This driver is designed to drive a floating N-channel MOSFET, whose source terminal is referenced to the HS pin.

Figure 3. High-Side Driver and Bootstrap Circuit Block Diagram

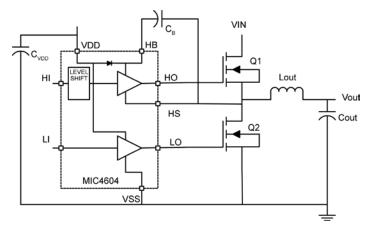

A low-power, high-speed, level-shifting circuit isolates the low side (VSS pin) referenced circuitry from the high-side (HS pin) referenced driver. Power to the high-side driver and UVLO circuit is supplied by the bootstrap circuit while the voltage level of the HS pin is shifted high. The bootstrap circuit consists of an internal diode and external capacitor,  $C_B$ . In a typical application, such as the synchronous buck converter shown in Figure 4, the HS pin is at ground potential while the low-side MOSFET is on. The internal diode allows capacitor  $C_B$  to charge up to VDD-VF during this time (where VF is the forward voltage drop of the internal diode). After the low-side MOSFET is turned off and the HO pin turns on, the voltage across capacitor  $C_B$  is applied to the gate of the upper external MOSFET. As the upper MOSFET turns on, voltage on the HS pin rises with the source of the high-side MOSFET until it reaches VIN. As the HS and HB pin rise, the internal diode is reverse biased preventing capacitor  $C_B$  from discharging.

Figure 4. High-Side Driver and Bootstrap Circuit Block Diagram

### **Programmable Gate Drive**

The MIC4604 offers programmable gate drive, which means the MOSFET gate drive (gate to source voltage) equals the VDD voltage. This feature offers designers flexibility in driving the MOSFETs. Different MOSFETs require different VGS characteristics for optimum R<sub>DSON</sub> performance. Typically, the higher the gate voltage (up to 16V), the lower the R<sub>DSON</sub> achieved. For example, a 4899 MOSFET can be driven to the ON state at 4.5V gate voltage but R<sub>DSON</sub> is 7.5mΩ. If driven to 10V gate voltage, R<sub>DSON</sub> is 4.5mΩ. In low-current applications, the losses due to R<sub>DSON</sub> are minimal, but in high-current applications such as power hand tools, the difference in R<sub>DSON</sub> can cut into the efficiency budget.

In portable hand tools and other battery-powered applications, the MIC4604 offers the ability to drive motors at a lower voltage compared to the traditional MOSFET drivers because of the wide VDD range (5.5V to 16V). Traditional MOSFET drivers typically require a VDD greater than 9V. The MIC4604 drives a motor using only two Li-ion batteries (total 7.2V) compared to traditional MOSFET drivers which will require at least three cells

(total of 10.8V) to exceed the minimal VDD range. As an additional benefit, the low 5.5V gate drive capability allows a longer run time. This is because the Li-ion battery can run down to 5.5V, which is just above its 4.8V minimum recommended discharge voltage. This is also a benefit in higher current power tools that use five or six cells. The driver can be operated up to 16V to minimize the  $R_{DSON}$  of the MOSFETs and use as much of the discharge battery pack as possible for a longer run time. For example, an 18V battery pack can be used to the lowest operating discharge voltage of 13.5V.

### **Application Information**

### **Power Dissipation Considerations**

Power dissipation in the driver can be separated into three areas:

- Internal diode dissipation in the bootstrap circuit

- Internal driver dissipation

- Quiescent current dissipation used to supply the internal logic and control functions.

### **Bootstrap Circuit Power Dissipation**

Power dissipation of the internal bootstrap diode primarily comes from the average charging current of the  $C_B$  capacitor multiplied by the forward voltage drop of the diode. Secondary sources of diode power dissipation are the reverse leakage current and reverse recovery effects of the diode.

The average current drawn by repeated charging of the high-side MOSFET is calculated by:

$$I_{F(AVE)} = Q_{gate} \times f_{S}$$

Eq. 1

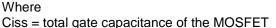

Where:

$Q_{gate}$  = total gate charge at V<sub>HB</sub> f<sub>s</sub> = gate drive switching frequency

The average power dissipated by the forward voltage drop of the diode equals:

$$\mathsf{Pdiode}_{\mathsf{fwd}} = \mathsf{I}_{\mathsf{F}(\mathsf{AVE})} \times \mathsf{V}_{\mathsf{F}} \qquad \qquad \mathsf{Eq. 2}$$

Where:

$V_F$  = diode forward voltage drop

The value of  $V_F$  should be taken at the peak current through the diode; however, this current is difficult to calculate because of differences in source impedances. The peak current can either be measured or the value of  $V_F$  at the average current can be used, which will yield a good approximation of diode power dissipation.

The reverse leakage current of the internal bootstrap diode is typically  $2\mu$ A at a reverse voltage of 85V at 125C. Power

dissipation due to reverse leakage is typically much less than 1mW and can be ignored.

Reverse recovery time is the time required for the injected minority carriers to be swept away from the depletion region during turn-off of the diode. Power dissipation due to reverse recovery can be calculated by computing the average reverse current due to reverse recovery charge times the reverse voltage across the diode. The average reverse current and power dissipation due to reverse recovery can be estimated by:

Where:

$I_{\text{RRM}} = \text{peak reverse recovery current} \\ t_{\text{rr}} = \text{reverse recovery time}$

The total diode power dissipation is:

$$Pdiode_{total} = Pdiode_{fwd} + Pdiode_{RR}$$

Eq. 4

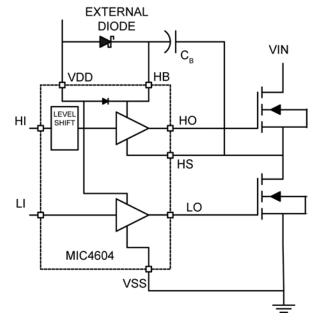

An optional external bootstrap diode may be used instead of the internal diode (Figure 5). An external diode may be useful if high gate charge MOSFETs are being driven and the power dissipation of the internal diode is contributing to excessive die temperatures. The voltage drop of the external diode must be less than the internal diode for this option to work. The reverse voltage across the diode will be equal to the input voltage minus the VDD supply voltage. The above equations can be used to calculate power dissipation in the external diode; however, if the external diode has significant reverse leakage current, the power dissipated in that diode due to reverse leakage can be calculated as:

$$Pdiode_{REV} = I_{R} \times V_{REV} \times (1 - D)$$

Eq. 5

Where:

$$\begin{split} I_{R} &= \text{reverse current flow at } V_{REV} \text{ and } T_{J} \\ V_{REV} &= \text{diode reverse voltage} \\ D &= \text{duty cycle} = t_{ON} \times f_{S} \end{split}$$

The on-time is the time the high-side switch is conducting. In most topologies, the diode is reverse biased during the switching cycle off-time.

Figure 5. Optional Bootstrap Diode

### Gate Driver Power Dissipation

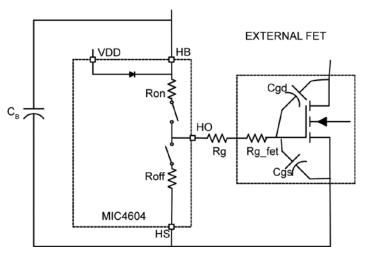

Power dissipation in the output driver stage is mainly caused by charging and discharging the gate to source and gate to drain capacitance of the external MOSFET. Figure 6 shows a simplified equivalent circuit of the MIC4604 driving an external MOSFET.

Figure 6. MIC4604 Driving an External MOSFET

### Dissipation during the External MOSFET Turn-On

Energy from capacitor  $C_B$  is used to charge up the input capacitance of the MOSFET (Cgd and Cgs). The energy delivered to the MOSFET is dissipated in the three resistive components, Ron, Rg and Rg\_fet. Ron is the on resistance of the upper driver MOSFET in the MIC4604.

Downloaded from Arrow.com.

Rg is the series resistor (if any) between the driver IC and the MOSFET. Rg\_fet is the gate resistance of the MOSFET. Rg\_fet is usually listed in the power MOSFET's specifications. The ESR of capacitor  $C_B$  and the resistance of the connecting etch can be ignored since they are much less than Ron and Rg\_fet.

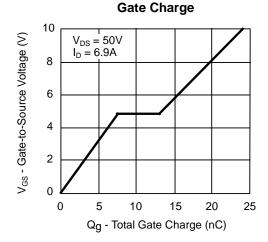

The effective capacitances of Cgd and Cgs are difficult to calculate because they vary non-linearly with Id, Vgs, and Vds. Fortunately, most power MOSFET specifications include a typical graph of total gate charge versus Vgs. Figure 7 shows a typical gate charge curve for an arbitrary power MOSFET. This chart shows that for a gate voltage of 10V, the MOSFET requires about 23.5nC of charge. The energy dissipated by the resistive components of the gate drive circuit during turn-on is calculated as:

$$\begin{split} & E = \frac{1}{2} \times Ciss \times {V_{gs}}^2 \\ & \text{but} \\ & Q = C \times V \\ & \text{Eq. 6} \\ & \text{so} \\ & E = 1/2 \times Qg \times V_{gs} \end{split}$$

The same energy is dissipated by Roff, Rg and Rg\_fet when the driver IC turns the MOSFET off. Assuming Ron is approximately equal to Roff, the total energy and power dissipated by the resistive drive elements is:

$$\begin{array}{l} \mathsf{E}_{driver} = \mathsf{Q}g \times \mathsf{V}_{gs} \\ \text{and} & \mathsf{Eq. 7} \\ \mathsf{P}_{driver} = \mathsf{Q}g \times \mathsf{V}_{gs} \times \mathsf{fs} \end{array}$$

Where:

$E_{driver}$  = energy dissipated per switching cycle  $P_{driver}$  = power dissipated per switching cycle Qg = total gate charge at Vgs Vgs = gate to source voltage on the MOSFET fs = switching frequency of the gate drive circuit

The power dissipated inside the MIC4604 is equal to the ratio of Ron and Roff to the external resistive losses in Rg and Rg\_fet. Letting Ron = Roff, the power dissipated in the MIC4604 due to driving the external MOSFET is:

$$Pdiss_{drive} = P_{driver} \frac{Ron}{Ron + Ra + Ra}$$

Eq. 8

### Supply Current Power Dissipation

Power is dissipated in the MIC4604 even if nothing is being driven. The supply current is drawn by the bias for the internal circuitry, the level shifting circuitry, and shootthrough current in the output drivers. The supply current is proportional to operating frequency and the VDD and VHB voltages. The typical characteristic graphs show how supply current varies with switching frequency and supply voltage.

The power dissipated by the MIC4604 due to supply current is

$$Pdiss_{supply} = VDD \times IDD + VHB \times IHB$$

Eq. 9

### **Total Power Dissipation and Thermal Considerations**

Total power dissipation in the MIC4604 is equal to the power dissipation caused by driving the external MOSFETs, the supply current and the internal bootstrap diode.

$$Pdiss_{total} = Pdiss_{supply} + Pdiss_{drive} + Pdiode_{total}$$

Eq. 10

The die temperature can be calculated after the total power dissipation is known.

$$T_J = T_A + Pdiss_{total} \times \theta_{JA}$$

Eq. 11

Where:

$\begin{array}{l} T_{\text{A}} = \text{maximum ambient temperature} \\ T_{\text{J}} = \text{junction temperature (°C)} \\ \text{Pdiss}_{\text{total}} = \text{power dissipation of the MIC4604} \\ \theta_{\text{JA}} = \text{thermal resistance from junction to ambient air} \end{array}$

### **Propagation Delay and Other Timing Considerations**

Propagation delay and signal timing are important considerations. Many power supply topologies use two switching MOSFETs operating 180° out of phase from each other. These MOSFETs must not be on at the same time or a short circuit will occur, causing high peak currents and higher power dissipation in the MOSFETs. The MIC4604 output gate drivers are not designed with anti-shoot-through protection circuitry. The output drive signals simply follow the inputs. The power supply design must include timing delays (dead-time) between the input signals to prevent shoot-through.

Make sure the input signal pulse width is greater than the minimum specified pulse width. An input signal that is less than the minimum pulse width may result in no output pulse or an output pulse whose width is significantly less than the input.

The maximum duty cycle (ratio of high side on-time to switching period) is controlled by the minimum pulse width of the low side and by the time required for the  $C_B$  capacitor to charge during the off-time. Adequate time must be allowed for the  $C_B$  capacitor to charge up before the high-side driver is turned on.

### **Decoupling and Bootstrap Capacitor Selection**

Decoupling capacitors are required for both the low side (VDD) and high side (HB) supply pins. These capacitors supply the charge necessary to drive the external MOSFETs and also minimize the voltage ripple on these pins. The capacitor from HB to HS has two functions: it provides decoupling for the high-side circuitry and also provides current to the high-side circuit while the high-side external MOSFET is on. Ceramic capacitors are recommended because of their low impedance and small size. Z5U type ceramic capacitor dielectrics are not recommended because of the large change in capacitance over temperature and voltage. A minimum value of 0.1µF is required for each of the capacitors, regardless of the MOSFETs being driven. Larger MOSFETs may require larger capacitance values for proper operation. The voltage rating of the capacitors depends on the supply voltage, ambient temperature and the voltage derating used for reliability. 25V rated X5R or X7R ceramic capacitors are recommended for most applications. The

minimum capacitance value should be increased if low voltage capacitors are used because even good quality dielectric capacitors, such as X5R, will lose 40% to 70% of their capacitance value at the rated voltage.

Placement of the decoupling capacitors is critical. The bypass capacitor for VDD should be placed as close as possible between the VDD and VSS pins. The bypass capacitor ( $C_B$ ) for the HB supply pin must be located as close as possible between the HB and HS pins. The etch connections must be short, wide, and direct. The use of a ground plane to minimize connection impedance is recommended. Refer to the section on Grounding, Component Placement and Circuit Layout for more information.

The voltage on the bootstrap capacitor drops each time it delivers charge to turn on the MOSFET. The voltage drop depends on the gate charge required by the MOSFET. Most MOSFET specifications specify gate charge versus Vgs voltage. Based on this information and a recommended  $\Delta V_{HB}$  of less than 0.1V, the minimum value of bootstrap capacitance is calculated as:

$$C_{B} \ge \frac{Q_{gate}}{\Delta V_{HB}}$$

Eq. 12

Where:

$Q_{gate}$  = total gate charge at V<sub>HB</sub>  $\Delta V_{HB}$  = voltage drop at the HB pin

The decoupling capacitor for the VDD input may be calculated in with the same formula; however, the two capacitors are usually equal in value.

### Grounding, Component Placement and Circuit Layout

Nanosecond switching speeds and ampere peak currents in and around the MIC4604 drivers require proper placement and trace routing of all components. Improper placement may cause degraded noise immunity, false switching, excessive ringing, or circuit latch-up.

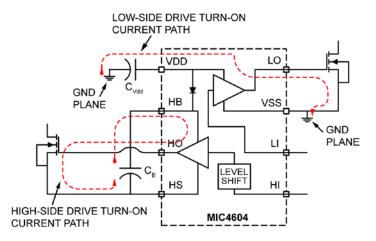

Figure 8 shows the critical current paths when the driver outputs go high and turn on the external MOSFETs. It also helps demonstrate the need for a low impedance ground plane. Charge needed to turn-on the MOSFET gates comes from the decoupling capacitors  $C_{VDD}$  and  $C_B$ . Current in the low-side gate driver flows from  $C_{VDD}$  through the internal driver, into the MOSFET gate, and out the source. The return connection back to the decoupling capacitor is made through the ground plane. Any inductance or resistance in the ground return path causes a voltage spike or ringing to appear on the source of the MOSFET. This voltage works against the gate drive voltage and can either slow down or turn off the MOSFET during the period when it should be turned on.

Current in the high-side driver is sourced from capacitor  $C_B$  and flows into the HB pin and out the HO pin, into the gate of the high side MOSFET. The return path for the current is from the source of the MOSFET and back to capacitor  $C_B$ . The high-side circuit return path usually does not have a low-impedance ground plane so the etch connections in this critical path should be short and wide to minimize parasitic inductance. As with the low-side circuit, impedance between the MOSFET source and the decoupling capacitor causes negative voltage feedback that fights the turn-on of the MOSFET.

It is important to note that capacitor  $C_B$  must be placed close to the HB and HS pins. This capacitor not only provides all the energy for turn-on but it must also keep HB pin noise and ripple low for proper operation of the high-side drive circuitry.

Figure 8. Turn-On Current Paths

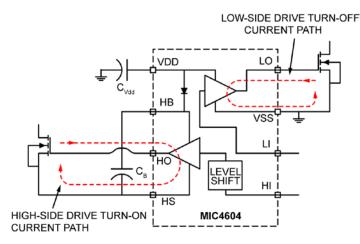

Figure 9 shows the critical current paths when the driver outputs go low and turn off the external MOSFETs. Short, low-impedance connections are important during turn-off for the same reasons given in the turn-on explanation. Current flowing through the internal diode replenishes charge in the bootstrap capacitor,  $C_B$ .

Figure 9. Turn-Off Current Paths

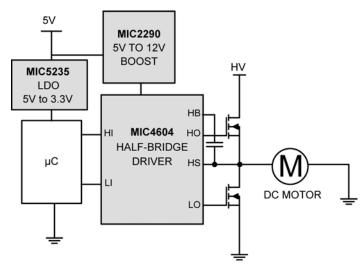

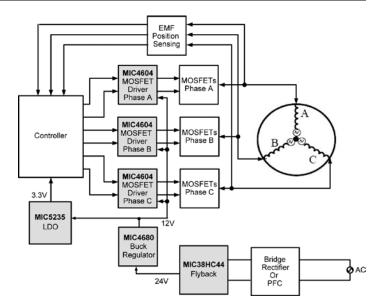

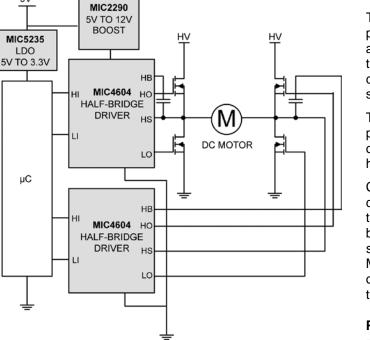

### **DC Motor Applications**

MIC4604 MOSFET drivers are widely used in DC motor applications. They address brushed motors in both halfbridge and full-bridge motor topologies as well as 3-phase brushless motors. As shown in Figure 10, Figure 11, and Figure 12, the drivers switch the MOSFETs at variable duty cycles that modulate the voltage to control motor speed. In the half-bridge topology, the motor turns in one direction only. The full-bridge topology allows for bidirectional control. 3-Phase motors are more efficient compared to the brushed motors but require three halfbridge switches and additional circuitry to sense the position of the rotor.

The MIC4604 85V operating voltage offers the engineer margin to protect against Back Electromotive Force (EMF) which is a voltage spike caused by the rotation of the rotor. The Back EMF voltage amplitude depends on the speed of the rotation. It is good practice to have at least twice the HV voltage of the motor supply. 85V is plenty of margin for 12V, 24V, and 40V motors.

5V

Figure 10. Half Bridge DC Motor

Figure 12. 3-Phase Brushless DC Motor Driver – 24V Block Diagram

Figure 11. Full Bridge DC Motor

The MIC4604 is offered in a small 2.5mm  $\times$  2.5mm TDFN package for applications that are space constrained and an SOIC-8 package for ease of manufacturing. The motor trend is to put the motor control circuit inside the motor casing, which requires small packaging because of the size of the motor.

The MIC4604 offers low UVLO threshold and programmable gate drive, which allows for longer operation time in battery operated motors such as power hand tools.

Cross conduction across the half bridge can cause catastrophic failure in a motor application. Engineers typically add dead time between states that switch between high input and low input to ensure that the lowside MOSFET completely turns off before the high-side MOSFET turns on and vice versa. The dead time depends on the MOSFET used in the application, but 200ns is typical for most motor applications.

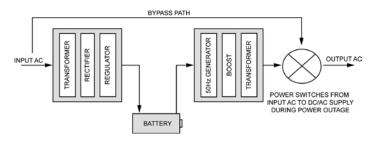

### **Power Inverter**

Power inverters are used to supply AC loads from a DC operated battery system, mainly during power failure. The battery voltage can be 12VDC, 24VDC, or up to 36VDC, depending on the power requirements. There two popular conversion methods, Type I and Type II, that convert the battery energy to AC line voltage (110VAC or 230VAC).

Figure 13. Type I Inverter Topology

As shown in Figure 13, Type I is a dual-stage topology where line voltage is converted to DC through a transformer to charge the storage batteries. When a power failure is detected, the stored DC energy is converted to AC through another transformer to drive the AC loads connected to the inverter output. This method is simplest to design but tends to be bulky and expensive because it uses two transformers.

Type II is a single-stage topology that uses only one transformer to charge the bank of batteries to store the energy. During a power outage, the same transformer is used to power the line voltage. The Type II switches at a higher frequency compared to the Type I topology to maintain a small transformer size.

Both types require a half bridge or full bridge topology to boost the DC to AC. This application can use two MIC4604s. The 85V operating voltage offers enough margin to address all of the available banks of batteries commonly used in inverter applications. The 85V operating voltage allows designers to increase the bank of batteries up to 72V, if desired. The MIC4604 can sink as much as 1A, which is enough current to overcome the MOSFET's input capacitance and switch the MOSFET up to 50kHz. This makes the MIC4604 an ideal solution for inverter applications.

As with all half bridge and full bridge topologies, cross conduction is a concern to inverter manufactures because it can cause catastrophic failure. This can be remedied by adding the appropriate dead time between transitioning from the high-side MOSFET to the low-side MOSFET and vice versa.

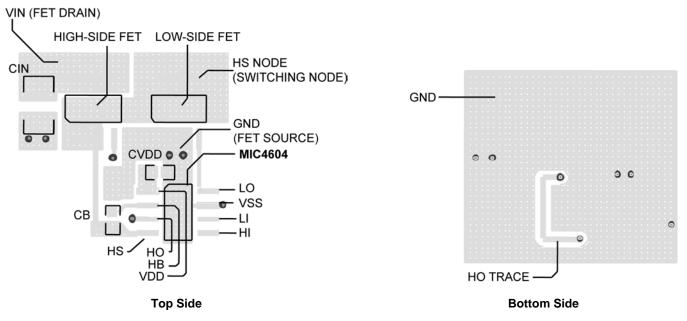

#### **Layout Guidelines**

Use the following layout guidelines for optimum circuit performance:

Place the VDD and HB bypass capacitors close to the supply and ground pins. It is critical that the etch length between the high side decoupling capacitor (C<sub>B</sub>) and the HB and HS pins be minimized to reduce lead inductance.

- Use a ground plane to minimize parasitic inductance and impedance of the return paths. The MIC4604 is capable of greater than 1A peak currents and any impedance between the MIC4604, the decoupling capacitors, and the external MOSFET will degrade the performance of the driver.

- Trace out the high di/dt and dv/dt paths, as shown in Figure 14 and Figure 15, and minimize etch length and loop area for these connections. Minimizing these parameters decreases the parasitic inductance and the radiated EMI generated by fast rise and fall times.

A typical layout of a synchronous Buck converter power stage (Figure 14) is shown in Figure 15.

Figure 14. Synchronous Buck Converter Power Stage

The high-side MOSFET drain connects to the input supply voltage (drain) and the source connects to the switching node. The low-side MOSFET drain connects to the switching node and its source is connected to ground. The buck converter output inductor (not shown) connects to the switching node. The high-side drive trace, HO, is routed on top of its return trace, HS, to minimize loop area and parasitic inductance. The low-side drive trace LO is routed over the ground plane to minimize the impedance of that current path. The decoupling capacitors,  $C_B$  and  $C_{VDD}$ , are placed to minimize etch length between the capacitors and their respective pins. This close placement is necessary to efficiently charge capacitor C<sub>B</sub> when the HS node is low. All traces are 0.025in wide or greater to reduce impedance. C<sub>IN</sub> is used to decouple the high current path through the MOSFETs.

Figure 15. Typical Layout of a Synchronous Buck Converter Power Stage

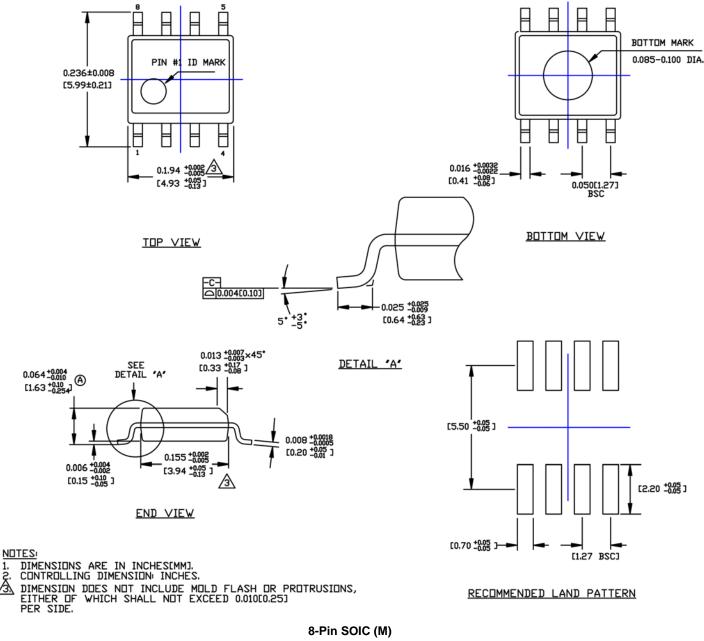

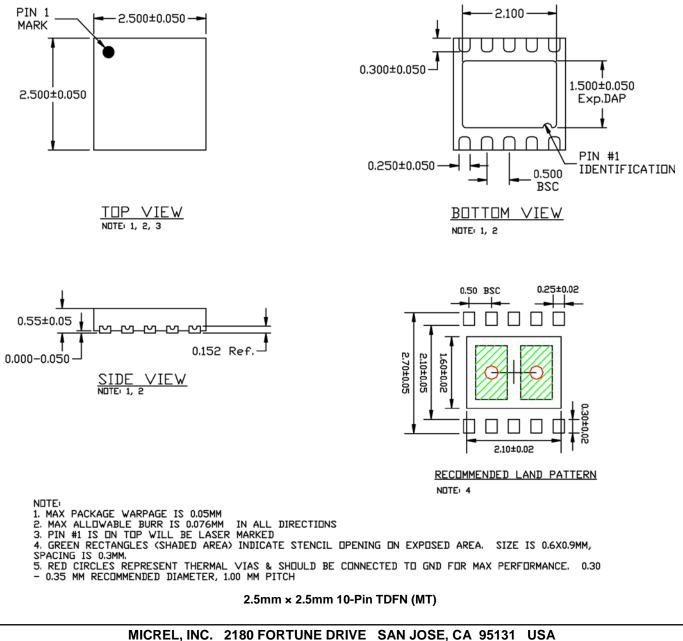

# Package Information and Recommended Land Pattern<sup>(7)</sup>

#### Note:

1. ni

7. Package information is correct as of the publication date. For updates and most current information, go to www.micrel.com.

### Package Information and Recommended Land Pattern (Continued)<sup>(7)</sup>

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB <u>http://www.micrel.com</u>

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2013 Micrel, Incorporated.