### **ABSOLUTE MAXIMUM RATINGS**

| PGND to GND<br>LXP, LXN to PGND0.3V to                |                  |

|-------------------------------------------------------|------------------|

| POUT, CLK/SEL, AIN, REF, FB,                          | ((1001 1 0.01)   |

| POKIN to GND0.3V                                      | to (Vout + 0.3V) |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                  |

| Narrow SO (derate 8.70mW/°C above +70°C)              | 696mW            |

| Operating Temperature Range         | 40°C to +85°C  |

|-------------------------------------|----------------|

| Junction Temperature                | +150°C         |

| Storage Temperature Range           | 65°C to +160°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

M/X/M

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(CLK/SEL = AIN =  $\overline{ON}$  = POKIN = FB = PGND = GND, OUT = POUT, LXP = LXN, V<sub>OUT</sub> = 5.3V (Note 1), **TA = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                        | CONDITIONS                                                                                 |                                                    | MIN   | TYP   | MAX   | UNITS |

|----------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|-------|

| DC-DC CONVERTER                  |                                                                                            |                                                    | I     |       |       |       |

| Input Supply Range               | (Note 2)                                                                                   |                                                    |       | 0.7   | 5.5   | V     |

| Minimum Start-Up Voltage         | $I_{LOAD} < 1mA, T_A = +$                                                                  | -25°C (Note 3)                                     |       | 0.9   | 1.1   | V     |

| Frequency in Start-Up Mode       | V <sub>OUT</sub> = 1.5V                                                                    |                                                    | 40    | 140   | 300   | kHz   |

| Output Voltage<br>(Note 4)       | $V_{FB} < 0.1V$ , CLK/SEL<br>$0 \le I_{LX} \le 1.1A$ , $V_{BATT}$                          |                                                    | 4.87  | 5.05  | 5.20  | V     |

| FB Regulation Voltage            | Adjustable output, C $0 \le I_{LX} \le 1.1A$ , VBATT                                       | LK/SEL = OUT,<br>- = 2.2V, V <sub>OUT</sub> = 3.3V | 1.21  | 1.24  | 1.255 | V     |

| FB Input Current                 | V <sub>FB</sub> = 1.25V                                                                    |                                                    |       | 0.1   | 20    | nA    |

| Output Voltage Adjust Range      |                                                                                            |                                                    | 2.5   |       | 5.5   | V     |

| Output Voltage Lockout Threshold | (Note 5)                                                                                   |                                                    | 2.0   | 2.15  | 2.3   | V     |

| Load Regulation (Note 6)         | CLK/SEL = OUT, no                                                                          | load to full load                                  |       | -1.6  |       | %     |

| Supply Current in Shutdown       | ON = OUT                                                                                   |                                                    |       | 0.1   | 20    | μA    |

| Supply Current in Low-Power Mode | CLK/SEL = GND (No                                                                          | CLK/SEL = GND (Note 1)                             |       | 65    | 120   | μA    |

| Supply Current in Low-Noise Mode | CLK/SEL = OUT (Note 1)                                                                     |                                                    |       | 150   | 300   | μA    |

| DC-DC SWITCHES                   |                                                                                            |                                                    |       |       |       |       |

| POUT, LXP Leakage Current        | V <sub>LXP</sub> = 0V, V <sub>OUT</sub> = V                                                | $V_{LXP} = 0V, V_{OUT} = V_{\overline{ON}} = 5.5V$ |       | 0.1   | 20    | μA    |

| LXN Leakage Current              | $V\overline{ON} = V_{LXN} = V_{OUT}$                                                       | = 5.5V                                             |       | 0.1   | 20    | μA    |

|                                  | N-channel                                                                                  | CLK/SEL = GND                                      |       | 0.14  | 0.25  |       |

| Switch On-Resistance             | N-Channel                                                                                  | CLK/SEL = OUT                                      |       | 0.075 | 0.13  | Ω     |

|                                  | P-channel                                                                                  | L                                                  |       | 0.13  | 0.25  |       |

| N-Channel Current Limit          | CLK/SEL = OUT                                                                              |                                                    | 2200  | 2700  | 3200  | mA    |

| N-Channel Current Limit          | CLK/SEL = GND                                                                              |                                                    | 500   | 800   | 1100  | mA    |

| P-Channel Turn-Off Current       | CLK/SEL = GND                                                                              |                                                    | 20    | 160   | 260   | mA    |

| POWER-GOOD COMPARATOR            |                                                                                            |                                                    |       |       |       |       |

| POKIN Trip Level                 | Rising VPOKIN                                                                              |                                                    | 1.225 | 1.250 | 1.275 | V     |

| POKIN Input Current              | VPOKIN = 0.7V                                                                              |                                                    | -20   |       | 20    | nA    |

| POK Low Voltage                  | $I_{SINK}(POK) = 1mA, V_{OUT} = 3.6V \text{ or}$<br>$I_{SINK}(POK) = 20\muA, V_{OUT} = 1V$ |                                                    |       | 0.03  | 0.4   | V     |

| POK High Leakage Current         | Vout = Vpok = 5.5V                                                                         |                                                    |       | 0.01  | 1     | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(CLK/SEL = AIN = \overline{ON} = POKIN = FB = PGND = GND, OUT = POUT, LXP = LXN, V_{OUT} = 5.3V (Note 1), T_A = 0°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                      | CONDITIONS                                      | MIN     | TYP   | MAX                 | UNITS |

|--------------------------------|-------------------------------------------------|---------|-------|---------------------|-------|

| GAIN BLOCK                     |                                                 | I       |       |                     |       |

| AIN Reference Voltage          | $I_{AO} = 20\mu A$                              | 1.237   | 1.25  | 1.263               | V     |

| AIN Input Current              | $V_{AIN} = 1.5V$                                | -30     |       | 30                  | nA    |

| Transconductance               | 10μA < Ι <sub>AO</sub> < 100μA                  | 5       | 10    | 16                  | mmho  |

| AO Output Low Voltage          | VAIN = 0.5V, IAO = 100µA                        |         | 0.1   | 0.4                 | V     |

| AO Output High Leakage         | V <sub>AIN</sub> = 1.5V, V <sub>AO</sub> = 5.5V |         | 0.01  | 1                   | μA    |

| REFERENCE                      |                                                 |         |       |                     |       |

| Reference Output Voltage       | I <sub>REF</sub> = 0μA                          | 1.237   | 1.250 | 1.263               | V     |

| REF Load Regulation            | -1μΑ < I <sub>REF</sub> < 50μΑ                  |         | 5     | 15                  | mV    |

| REF Supply Rejection           | 2.5V < V <sub>OUT</sub> < 5.5V                  |         | 0.2   | 5                   | mV    |

| LOGIC INPUTS                   |                                                 |         |       |                     |       |

|                                | ON, 1.2V < VOUT < 5.5V (Note 7)                 |         |       | 0.2V <sub>OUT</sub> | V     |

| Input Low Voltage              | CLK/SEL, V <sub>OUT</sub> = 2.5V                |         |       | 0.2V <sub>OUT</sub> | v     |

| Input High Voltage             | <del>ON</del> , 1.2V < V <sub>OUT</sub> < 5.5V  | 0.8Vout |       |                     | V     |

| Input High Voltage             | CLK/SEL, V <sub>OUT</sub> = 5.5V                | 0.8Vout |       |                     | v     |

| Logic Input Current            | ON, CLK/SEL                                     | -1      | 0.01  | 1                   | μA    |

| Internal Oscillator Frequency  | CLK/SEL = OUT, VFB = 0.5V                       | 260     | 300   | 340                 | kHz   |

| Oscillator Maximum Duty Cycle  | CLK/SEL = OUT, V <sub>FB</sub> = 0.5V           | 80      | 86    | 90                  | %     |

| External Clock Frequency Range |                                                 | 200     |       | 400                 | kHz   |

| Minimum CLK/SEL Pulse Width    |                                                 |         | 200   |                     | ns    |

| Maximum CLK/SEL Rise/Fall Time |                                                 |         | 100   |                     | ns    |

### **ELECTRICAL CHARACTERISTICS**

$(CLK/SEL = AIN = \overline{ON} = POKIN = FB = PGND = GND, OUT = POUT, LXP = LXN, V_{OUT} = 5.3V$  (Note 1),  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 8)

| PARAMETER                        | CONDITIONS                                                                                                       | MIN  | TYP | MAX  | UNITS |

|----------------------------------|------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| DC-DC CONVERTER                  |                                                                                                                  |      |     |      |       |

| Output Voltage (Note 4)          | $V_{FB} < 0.1V, CLK/SEL = OUT, \\ 0 \le I_{LX} \le 1.1A, V_{BATT} = 3.7V$                                        | 4.87 |     | 5.20 | V     |

| FB Regulation Voltage            | Adjustable output, CLK/SEL = OUT,<br>$0 \le I_{LX} \le 1.1A$ , V <sub>OUT</sub> = 3.3V, V <sub>BATT</sub> = 2.2V | 1.20 |     | 1.27 | V     |

| Output Voltage Lockout Threshold | (Note 5)                                                                                                         | 2.0  |     | 2.3  | V     |

| Supply Current in Shutdown       | ON = OUT                                                                                                         |      |     | 20   | μA    |

| Supply Current in Low-Power Mode | CLK/SEL = GND (Note 1)                                                                                           |      |     | 120  | μA    |

| Supply Current in Low-Noise Mode | CLK/SEL = OUT (Note 1)                                                                                           |      |     | 300  | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(CLK/SEL = AIN =  $\overline{ON}$  = POKIN = FB = PGND = GND, OUT = POUT, LXP = LXN, V<sub>OUT</sub> = 5.3V (Note 1), **TA = -40°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 8)

| DC-DC SWITCHES       Switch On-Resistance             | CLK/SEL = GND                  |       |       | ·    |

|-------------------------------------------------------|--------------------------------|-------|-------|------|

| Switch On-Resistance N-channel                        |                                |       |       |      |

| Switch On-Resistance                                  |                                |       | 0.25  |      |

|                                                       | CLK/SEL = OUT                  |       | 0.13  | Ω    |

| P-channel                                             |                                |       | 0.25  |      |

| N-Channel Current Limit                               |                                | 2200  | 3600  | mA   |

| CLK/SEL = GND                                         |                                | 500   | 1100  | mA   |

| POWER-GOOD COMPARATOR                                 |                                |       |       |      |

| POKIN Trip Level Rising VPOKIN                        | Rising VPOKIN                  |       | 1.275 | V    |

| GAIN BLOCK                                            |                                | ·     |       |      |

| AIN Reference Voltage $I_{AO} = 20\mu A$              | $I_{AO} = 20\mu A$             |       | 1.27  | V    |

| Transconductance $10\mu A < I_{AO} < 100\mu A$        | 10μA < Ι <sub>AO</sub> < 100μA |       | 16    | mmho |

| REFERENCE                                             |                                | ·     |       |      |

| Reference Output Voltage I <sub>REF</sub> = 0µA       | $I_{REF} = 0\mu A$             |       | 1.27  | V    |

| LOGIC INPUTS                                          |                                | · · · |       |      |

| Internal Oscillator Frequency CLK/SEL = OUT, VFB = 0. | CLK/SEL = OUT, VFB = 0.5V      |       | 340   | kHz  |

| Oscillator Maximum Duty Cycle CLK/SEL = OUT, VFB = 0. | CLK/SEL = OUT, VFB = 0.5V      |       | 92    | %    |

**Note 1:** Supply current from the 5.05V output is measured between the 5.05V output and the OUT pin. This current correlates directly to the actual battery supply current, but is reduced in value according to the step-up ratio and efficiency. Set V<sub>OUT</sub> = 5.3V to keep the internal switch open when measuring the device operating current.

Note 2: Minimum operating voltage. Since the regulator is bootstrapped to the output, once started it will operate down to a 0.7V input.

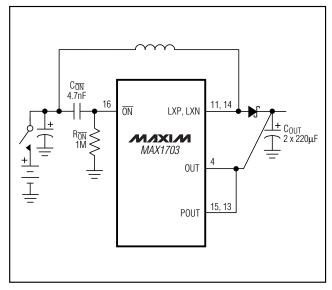

**Note 3:** Start-up is tested with the circuit of Figure 2.

Note 4: In low-power mode (CLK/SEL = GND) the output voltage regulates 1% higher than low-noise mode (CLK/SEL = OUT or synchronized).

Note 5: The regulator is in start-up mode until this voltage is reached. Do not apply full-load current below this voltage.

Note 6: Load regulation is measured from no-load to full load, where full load is determined by the N-channel switch current limit.

Note 7: The ON input has a total hysteresis of approximately 0.15 x VOUT.

**Note 8:** Specifications to -40°C are guaranteed by design and not production tested.

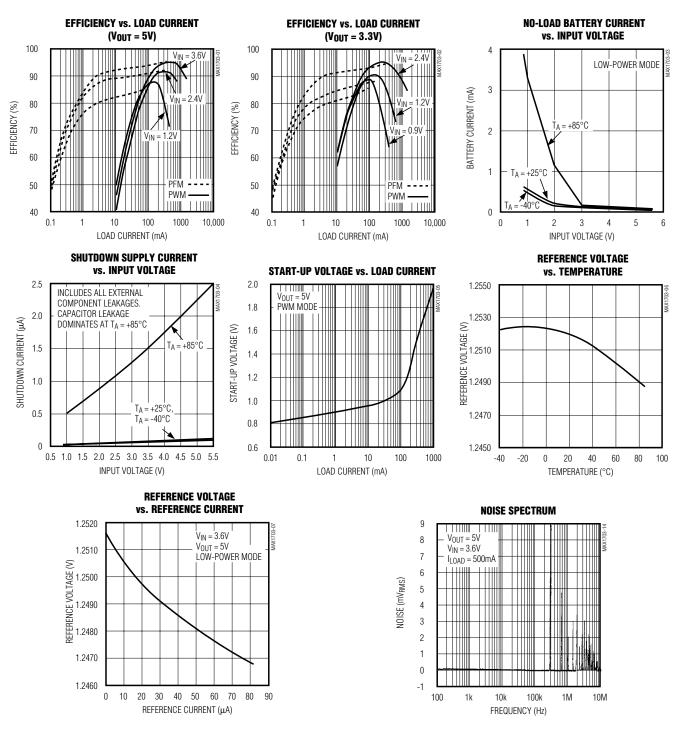

**Typical Operating Characteristics**

$(V_{IN} = +3.6V, V_{OUT} = 5V, T_A = +25^{\circ}C$ , unless otherwise noted.)

/N/IXI/N

MAX1703

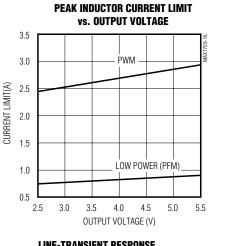

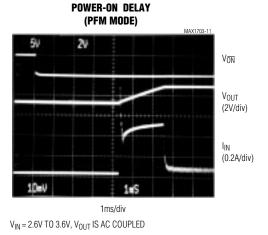

### **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.6V, V_{OUT} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

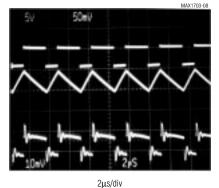

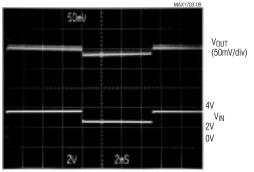

**HEAVY LOAD SWITCHING**

$I_{1 \text{ OAD}} = 1.5 \text{A}, \text{ C7} = 0.47 \mu \text{F}$

2ms/div  $V_{IN}\,{=}\,2.6V$  TO 3.6V,  $V_{OUT}\,{IS}$  AC COUPLED

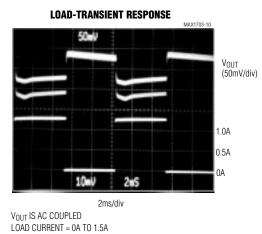

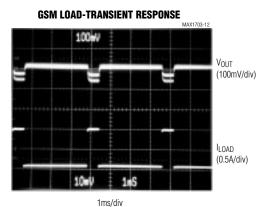

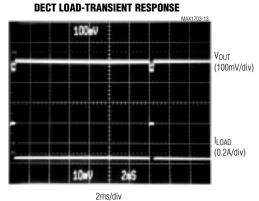

### **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.6V, V_{OUT} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

$V_{\text{IN}} = 3.6V, V_{\text{OUT}} = 5V, C_{\text{OUT}} = 470 \mu\text{F},$ PULSE WIDTH = 577 $\mu$ s, LOAD CURRENT = 100mA TO 1A

$V_{IN} = 1.2V, V_{OUT} = 3.3V, C_{OUT} = 470 \mu F,$

PULSE WIDTH = 416µs, LOAD CURRENT = 50mA TO 400mA

## Pin Description

| PIN    | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | REF     | Reference Output. Bypass with a 0.22µF bypass capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2      | FB      | Dual-Mode™ Feedback Input. Connect FB to ground to set a fixed output voltage of +5V. Connect a divider between the output voltage and GND to set the output voltage from 2.5V to 5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3      | POKIN   | Power-Good Comparator Input. Threshold is 1.250V, with 1% hysteresis on the threshold's rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4      | OUT     | DC-DC Converter Output. Power source for the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5      | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6      | AIN     | Gain-Block Input. When AIN is low, AO sinks current. The nominal transconductance from AIN to AO is 10mmhos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7      | AO      | Gain-Block Output. This open-drain output sinks current when VAIN < VREF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8      | POK     | Power-Good Comparator Output. This open-drain N-channel output is low when VPOKIN < 1.250V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9      | CLK/SEL | <ul> <li>Switch-Mode Selection and External-Clock Synchronization Input:</li> <li>CLK/SEL = Low: Low-power, low-quiescent-current PFM mode. Delivers up to 10% of full load current.</li> <li>CLK/SEL = High: High-power PWM mode. Full output power available. Operates in low-noise, constant-frequency mode.</li> <li>CLK/SEL = External Clock: High-power PWM mode with the internal oscillator synchronized to the external CLK</li> <li>Turning on with CLK/SEL = OV also serves as a soft-start function, since peak inductor current is limited to 25% of that allowed in PWM mode.</li> </ul> |

| 10, 12 | PGND    | Source of N-Channel Power MOSFET Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11     | LXN     | Drain of N-Channel Power Switch. Connect LXP to LXN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13, 15 | POUT    | Source of P-Channel Synchronous Rectifier MOSFET Switch. Connect an external Schottky diode from LXN and LXP to POUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14     | LXP     | Drain of P-Channel Synchronous Rectifier. Connect LXP to LXN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16     | ŌN      | On/Off Input. When $\overline{ON}$ is low, the IC turns on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Dual Mode is a trademark of Maxim Integrated Products.

**MAX1703**

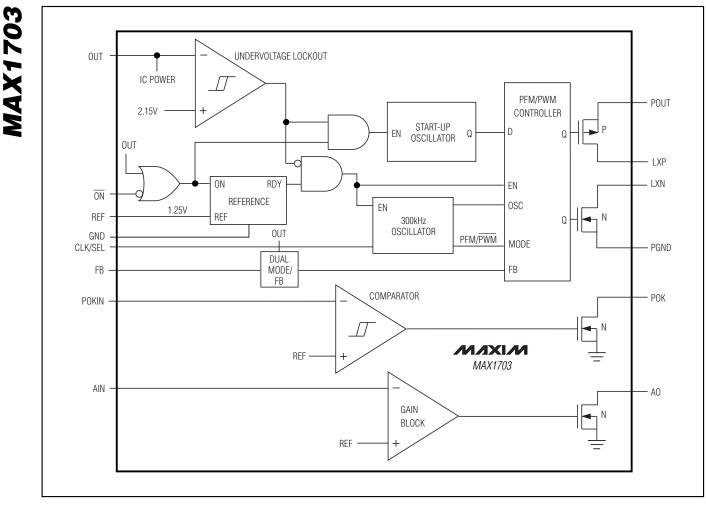

Figure 1. Functional Block Diagram

### **Detailed Description**

The MAX1703 is a highly efficient, low-noise power supply for portable RF and data-acquisition instruments. It combines a boost switching regulator, Nchannel power MOSFET, P-channel synchronous rectifier, precision reference, shutdown control, versatile gain block, and power-good (POK) comparator (Figure 1) in a 16-pin narrow SO package.

The switching DC-DC converter boosts a 1- to 3-cell input to a fixed 5V or an adjustable output between 2.5V and 5.5V. Typically the MAX1703 starts from a low, 0.9V input and remains operational down to 0.7V.

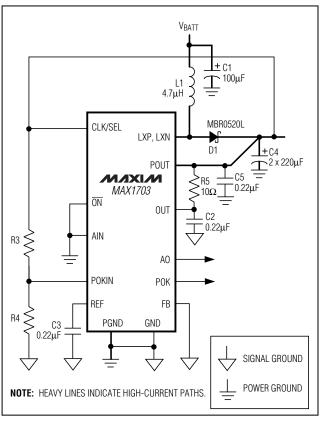

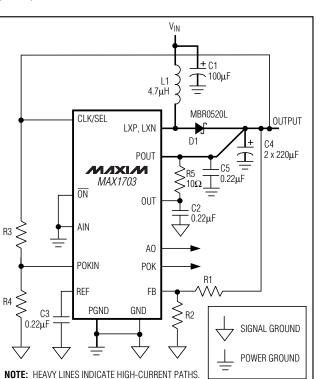

The MAX1703 is optimized for use in cellular phones and other applications requiring low noise during fullpower operation, as well as low quiescent current for maximum battery life in low-power mode and shutdown. It features constant-frequency (300kHz), lownoise PWM operation with up to 1.5A output capability. See Table 1 for typical outputs. A low-quiescent-current, low-power mode offers an output up to 150mA and reduces quiescent power consumption to 300µW. In shutdown mode, the quiescent current is further reduced to just 1µA. Figure 2 shows the standard application circuit for the MAX1703.

8

M/X/M

| <i>,</i> , , |                         |                          |                           |  |

|--------------|-------------------------|--------------------------|---------------------------|--|

| NO. OF CELLS | INPUT<br>VOLTAGE<br>(V) | OUTPUT<br>VOLTAGE<br>(V) | OUTPUT<br>CURRENT<br>(mA) |  |

| 1 NiCd/NiMH  | 1.2                     | 3.3                      | 600                       |  |

| 2 NiCd/NiMH  | 2.4                     | 3.3                      | 1400                      |  |

|              | 2.4                     | 5.0                      | 950                       |  |

| 3 NiCd/NiMH  | 3.6                     | 5.0                      | 1600                      |  |

### Table 1. Typical Available Output Current

Figure 2. MAX1703 in High-Power PWM Mode

Additional features include synchronous rectification for high efficiency and improved battery life, and an uncommitted comparator (POK) for monitoring the regulator's output or battery voltage. The MAX1703 also includes a gain block that can be used to build a linear regulator using an external P-channel MOSFET pass device; this gain block can also function as a second comparator. A CLK input allows frequency synchronization to reduce interference.

### Table 2. Selecting the Operating Mode

| CLK/SEL                              | MODE                | FEATURES                          |

|--------------------------------------|---------------------|-----------------------------------|

| 0                                    | Low power           | Low supply current                |

| 1                                    | PWM                 | Low noise,<br>high output current |

| External Clock<br>(200kHz to 400kHz) | Synchronized<br>PWM | Low noise,<br>high output current |

#### **Step-Up Converter**

The step-up switching DC-DC converter generates an adjustable output from 2.5V to 5.5V. The internal N-channel MOSFET switch is turned on during the first part of each cycle, allowing current to ramp up in the inductor and store energy in a magnetic field. During the second part of each cycle, when the MOSFET is turned off, the voltage across the inductor reverses and forces current through the diode and synchronous rectifier to the output filter capacitor and load. As the energy stored in the inductor is depleted, the current ramps down and the output diode and synchronous rectifier turn off. Depending on the CLK/SEL pin setting, voltage across the load is regulated using either low-noise PWM or low-power operation (Table 2).

#### Low-Noise PWM Operation

When CLK/SEL is pulled high, the MAX1703 operates in a high-power, low-noise PWM mode. During PWM operation, the MAX1703 switches at a constant frequency (300kHz), and modulates the MOSFET-switch pulse width to control the power transferred per cycle and regulate the voltage across the load. In PWM mode the device can output up to 1.5A. Switching harmonics generated by fixed-frequency operation are consistent and easily filtered. See the Noise Spectrum plot in the *Typical Operating Characteristics*.

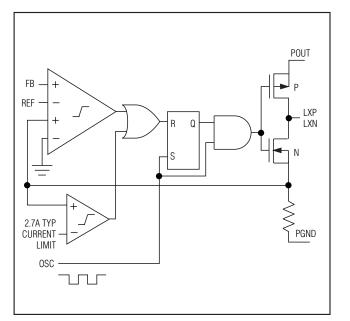

During PWM operation, each of the internal clock's rising edges sets a flip-flop, which turns on the N-channel MOSFET switch (Figure 3). The switch turns off when the sum of the voltage-error, slope-compensation, and current-feedback signals trips a multi-input comparator and resets the flip-flop; the switch remains off for the rest of the cycle. When a change occurs in the output voltage error signal, the comparator shifts the level to which the inductor current ramps during each cycle. A second comparator enforces an inductor current limit of 2.7A (typical). MAX1703

Figure 3. Simplified PWM Controller Block Diagram

#### Synchronized PWM Operation

The MAX1703 can be synchronized in PWM mode to a 200kHz to 400kHz frequency by applying an external clock to CLK/SEL. This allows the user to set the harmonics to avoid IF bands in wireless applications. The synchronous rectifier is also active during synchronized PWM operation.

#### Low-Power PFM Operation

Pulling CLK/SEL low places the MAX1703 in a lowpower mode. During low-power mode, PFM operation regulates the output voltage by transferring a fixed amount of energy during each cycle, and then modulating the pulse frequency to control the power delivered to the output. The devices switch only as needed to service the load, resulting in the highest possible efficiency at light loads. Output current capability in PFM mode is 150mA (max). The output voltage is typically 1% higher than in PWM mode.

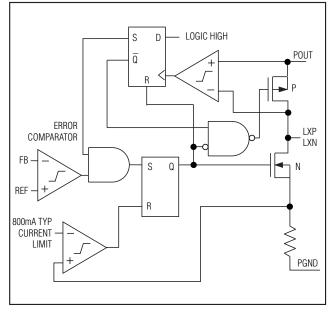

During PFM operation, the error comparator detects the output voltage falling out of regulation and sets a flipflop, which turns on the N-channel MOSFET switch (Figure 4). When the inductor current ramps to the PFM mode current limit (800mA typical) and stores a fixed amount of energy, the current-sense comparator resets a flip-flop. The flip-flop turns off the N-channel switch and turns on the P-channel synchronous rectifier. A second flip-flop, previously reset by the switch's "on" sig-

Figure 4. Controller Block Diagram in Low-Power PFM Mode

nal, inhibits the error comparator from initiating another cycle until the energy stored in the inductor is transferred to the output filter capacitor and the synchronous rectifier current has ramped down to 80mA. This forces operation with a discontinuous inductor current.

#### **Synchronous Rectifier**

The MAX1703 features an internal 140m $\Omega$ , P-channel synchronous rectifier to enhance efficiency. Synchronous rectification provides a 5% efficiency improvement over similar nonsynchronous boost regulators. In PWM mode, the synchronous rectifier is turned on during the second half of each switching cycle. In low-power mode, an internal comparator turns on the synchronous rectifier when the voltage at LX exceeds the boost regulator output, and then turns it off when the inductor current drops below 80mA.

#### Low-Voltage Start-Up Oscillator

The MAX1703 uses a CMOS, low-voltage start-up oscillator for a 1.1V guaranteed minimum start-up input voltage at +25°C. On start-up, the low-voltage oscillator switches the N-channel MOSFET until the output voltage reaches 2.15V. Above this level, the normal boostconverter feedback and control circuitry take over. Once the device is in regulation, it can operate down to a 0.7V input, since internal power for the IC is bootstrapped from the output via the OUT pin. Do not apply full load until the output exceeds 2.3V (max).

#### Shutdown

The MAX1703 shuts down to reduce quiescent current to 1µA. During shutdown ( $\overline{ON} = V_{OUT}$ ), the reference, low-battery comparator, gain block, and all feedback and control circuitry are off. The boost converter's output drops to one Schottky diode drop below the input.

#### **Power-Good (POK) Comparator**

The MAX1703 features an uncommitted POK comparator. The internal POK comparator has an open-drain output (POK) capable of sinking 1mA. When the input (POKIN) rises above the 1.25V reference, the POK open-drain output turns off. The POKIN input has 10mV of hysteresis.

To provide a power-good signal, connect the POKIN input to an external resistor-divider between OUT and GND (Figure 5). Calculate the resistor values as follows:

#### R3 = R4(VTH / VREF - 1)

where VTH is the desired input voltage trip threshold.

Since the input bias current into POKIN is less than 20nA, R4 can be a large value (such as  $270k\Omega$  or less) without sacrificing accuracy. Connect the resistor voltage-divider as close to the IC as possible, within 0.2in. (5mm) of POKIN.

#### Reference

The MAX1703 has an internal 1.250V, 1% bandgap reference. Connect a 0.22 $\mu$ F bypass capacitor to GND within 0.2in. (5mm) of the REF pin. REF can source up to 50 $\mu$ A of external load current.

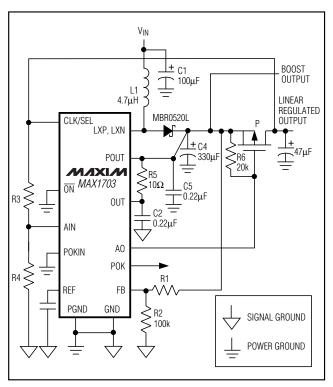

#### **Gain Block**

The MAX1703 gain block can function as a second comparator, or can be used to build a linear regulator using an external P-channel MOSFET pass device. The gain-block output is a single-stage transconductance amplifier that drives an open-drain N-channel MOSFET. The gm of the entire gain-block stage is 10mmho. Figure 6 shows the gain block used in a linear-regulator application. The output of an external P-channel pass element is compared to the internal reference. The difference is amplified and used to drive the gate of the pass element. Use a logic-level PFET, such as an NDS336P (RDS(ON) = 270m $\Omega$ ) from Fairchild. This configuration allows ripple reduction at the output. If a lower RDS(ON) PFET is used, then the linear regulator output filter capacitance may need to be increased.

To use the gain block as a comparator, refer to the *Power-Good (POK) Comparator* section.

Figure 5. Adjustable Output (PWM Mode)

M/IXI/M

Figure 6. Using the Gain Block as a Linear Regulator

| 3 |

|---|

| 0 |

| Ň |

|   |

|   |

|   |

| 2 |

| Σ |

### **Table 3. Component Selection Guide**

| PRODUCTION    | INDUCTORS                       | CAPACITORS          | DIODES            |

|---------------|---------------------------------|---------------------|-------------------|

|               | Sumida CDR125                   | Matsuo 267 series   |                   |

| Surface Mount | Sprague 595D series             | Sprague 595D series | Motorola MBR0520L |

|               | Coilcraft DO3316 AVX TPS series | AVX TPS series      | _                 |

| Through Holo  | Sumida RCH654 series            | Sanyo OS-CON series | 1N5817            |

| Through Hole  | Sumiua nomoja senes             | Nichicon PL series  | ΠΙΟΟΤΤ            |

### **Design Procedure**

#### **Setting the Output Voltages**

Set the output voltage between 2.5V and 5.5V by connecting a resistor voltage-divider to FB from OUT to GND, as shown in Figure 2. The resistor values are then as follows:

$$R1 = R2(V_{OUT} / V_{FB} - 1)$$

where V<sub>FB</sub>, the boost-regulator feedback setpoint, is 1.24V. Since the input bias current into FB is less than 20nA, R2 can have a large value (such as  $270k\Omega$  or less) without sacrificing accuracy. Connect the resistor voltage-divider as close to the IC as possible, within 0.2in. (5mm) of the FB pin.

#### **Inductor Selection**

The MAX1703's high switching frequency allows the use of a small surface-mount inductor. A 4.7µH inductor should have a saturation-current rating that exceeds the N-channel switch current limit. However, it is generally acceptable to bias the inductor current into saturation by as much as 20%, although this will slightly reduce efficiency. For high efficiency, choose an inductor with a high-frequency core material, such as ferrite, to reduce core losses. To minimize radiated noise, use a toroid, pot core, or shielded bobbin inductor. See Table 3 for suggested components and Table 4 for a list of component suppliers. Connect the inductor from the battery to the LX pins as close to the IC as possible.

#### **Output Diode**

Use a Schottky diode such as a 1N5817, MBR0520L, or equivalent. The Schottky diode carries current during both start-up and PFM mode after the synchronous rectifier turns off. Thus, its current rating only needs to be 500mA. Connect the diode between LXN/LXP and POUT, as close to the IC as possible. Do not use ordinary rectifier diodes, since slow switching speeds and long reverse recovery times will compromise efficiency and load regulation.

### Table 4. Component Suppliers

| SUPPLIER  | PHONE                                        | FAX                              |

|-----------|----------------------------------------------|----------------------------------|

| AVX       | USA: (803) 946-0690<br>(800) 282-4975        | (803) 626-3123                   |

| Coilcraft | USA: (847) 639-6400                          | (847) 639-1469                   |

| Matsuo    | USA: (714) 969-2491                          | (714) 960-6492                   |

| Motorola  | USA: (602) 303-5454                          | (602) 994-6430                   |

| Sanyo     | USA: (619) 661-6835<br>Japan: 81-7-2070-6306 | (619) 661-1055<br>81-7-2070-1174 |

| Sumida    | USA: (847) 956-0666<br>Japan: 81-3-3607-5111 | (847) 956-0702<br>81-3-3607-5144 |

#### Input and Output Filter Capacitors

Choose input and output filter capacitors that will service the input and output peak currents with acceptable voltage ripple. Choose input capacitors with working voltage ratings over the maximum input voltage, and output capacitors with working voltage ratings higher than the output.

A 330µF, 100m $\Omega$ , low-ESR tantalum capacitor is recommended for a 5V output. For full output load current, one 470µF or two 220µF, 100m $\Omega$  low-ESR tantalum capacitors are recommended for a 3.3V output. The input filter capacitor (CIN) also reduces peak currents drawn from the input source and reduces input switching noise. The input voltage source impedance determines the required size of the input capacitor.

When operating directly from one or two NiCd cells placed close to the MAX1703, use a  $100\mu F,$  low-ESR input filter capacitor.

Sanyo OS-CON and Panasonic SP/CB-series ceramic capacitors offer the lowest ESR. Low-ESR tantalum capacitors are a good choice and generally offer a good tradeoff between price and performance. Do not exceed the ripple current ratings of tantalum capacitors. Avoid most aluminum-electrolytic capacitors, because their ESR is often too high.

#### **Bypass Capacitors**

A few ceramic bypass capacitors are required for proper operation. Bypass REF with a  $0.22\mu$ F capacitor to GND. Connect a  $0.22\mu$ F ceramic capacitor from OUT to GND. Each of these should be placed as close to their respective pins as possible, within 0.2in. (5mm) of the DC-DC converter IC. See Table 4 for suggested suppliers.

### **Applications Information**

#### Intermittent Supply/Battery Connections

When boosting an input supply connected via a mechanical switch, or a battery connected via spring contacts, input power may sometimes be intermittent as a result of contact bounce. When operating in PFM mode with input voltages greater than 2.5V, restarting after such dropouts may initiate high current pulses that interfere with the MAX1703's internal MOSFET switch control. If contact or switch bounce is anticipated in the design, use one of the following solutions:

- 1) Connect a capacitor  $(\overline{C_{ON}})$  from  $\overline{ON}$  to  $V_{IN}$  and a 1M $\Omega$  resistor ( $\overline{R_{ON}}$ ) from  $\overline{ON}$  to GND, as shown in Figure 7. This resistor-capacitor network differentiates fast input edges at  $V_{IN}$  and momentarily holds the IC off until  $V_{IN}$  settles. The appropriate value of  $\overline{C_{ON}}$  is 10<sup>-5</sup> times the total output filter capacitance ( $C_{OUT}$ ), so a  $C_{OUT}$  of 440µF results in  $\overline{C_{ON}}$  = 4.7nF.

- 2) Use the system microcontroller to hold the MAX1703 in shutdown from the time when power is applied (or reapplied) until COUT has charged to at least the input voltage. Standard power-on-reset times accomplish this.

- Ensure that the IC operates, or at least powers up, in PWM mode (CLK/SEL = high). Activate PFM mode only after the output voltage has settled and all of the system's power-on-reset flags are cleared.

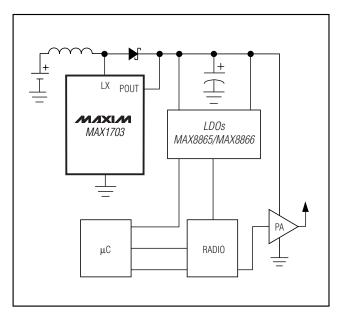

#### Use in a Typical Wireless Phone Application

The MAX1703 is ideal for use in digital cordless and PCS phones. The power amplifier (PA) is connected directly to the boost-converter output for maximum voltage swing (Figure 8). Low-dropout linear regulators are used for post-regulation to generate low-noise power for DSP, control, and RF circuitry. Typically, RF phones spend most of their life in standby mode with only short periods in transmit/receive mode. During standby, maximize battery life by setting CLK/SEL = 0; this places the IC in low-power mode (for the lowest quiescent power consumption). See *Gain Block* section for information on configuring an external MOSFET as a linear regulator.

Figure 7. Connecting  $C_{\overline{ON}}$  and  $R_{\overline{ON}}$  when Switch or Battery-Contact Bounce is Anticipated

#### **Designing a PC Board**

High switching frequencies and large peak currents make PC board layout an important part of design. Poor design can cause excessive EMI and ground bounce, both of which can cause instability or regulation errors by corrupting the voltage and current feedback signals.

Power components—such as the inductor, converter IC, filter capacitors, and output diode—should be placed as close together as possible, and their traces should be kept short, direct, and wide. A separate low-noise ground plane containing the reference and signal grounds should only connect to the power-ground plane at one point. This minimizes the effect of power-ground currents on the part.

Keep the voltage feedback network very close to the IC, within 0.2in. (5mm) of the FB pins. Keep noisy traces, such as from the LX pin, away from the voltage feedback networks and separated from them using grounded copper. Consult the MAX1703 EV kit for a full PC board example.

#### Soft-Start

To implement soft-start, set CLK/SEL low on power-up; this forces PFM operation and reduces the peak switching current to 800mA max. Once the circuit is in regulation and start-up transients have settled, CLK/SEL can be set high for full-power operation.

13

MAX1703

Chip Information

TRANSISTOR COUNT: 554 SUBSTRATE CONNECTED TO GND

Figure 8. Typical Phone Application

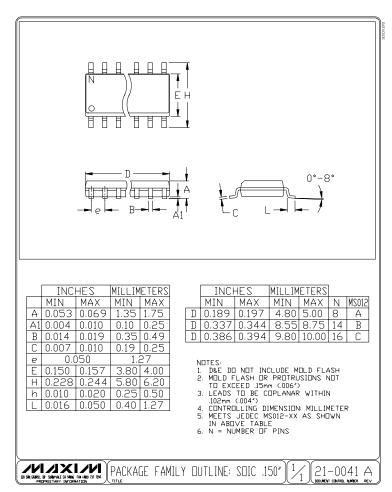

### Package Information

NOTES