# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Power Supply (V <sub>CC</sub> )<br>External NMOS Drive (NDRV)<br>NDRV to V <sub>CC</sub> | 0.3V to 20V    |

|------------------------------------------------------------------------------------------|----------------|

| Bootstrap Supply (BOOST)                                                                 | –0.3V to 115V  |

| Top Source (TS)                                                                          | 5V to 100V     |

| BOOST to TS                                                                              | 0.3V to 15V    |

| Soft-Start Fault, Feedback,                                                              |                |

| Frequency Set, Transformer                                                               |                |

| Inputs (SSFLT, FB/IN+, FS/IN-)                                                           | 0.3V to 15V    |

| All Other Pins (V <sub>SI MT</sub> , I <sub>S</sub> , UVLO)                              | 0.3V to 5V     |

| Peak Output Current <1µs (TG, BG)                                                        | 2A             |

| <b>Operating Ambient Temperature Rang</b>                                                |                |

| Operating Junction Temperature (Note                                                     | e 2)125°C      |

| Storage Temperature Range                                                                | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)                                                     |                |

|                                                                                          |                |

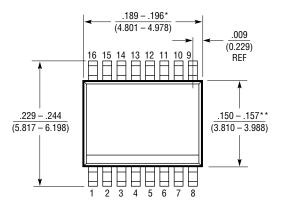

# PACKAGE/ORDER INFORMATION

| TOP VI                                                   | Is 2 15 TG  VSLMT 3 14 BOOST  UVLO 4 13 NC  SSFLT 5 12 NC  NDRV 6 11 VCC  FB/IN* 7 10 BG | ORDER PART<br>NUMBER     |  |  |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| V <sub>SLMT</sub> 3<br>UVLO 4                            |                                                                                          | LTC3705EGN<br>LTC3705IGN |  |  |  |

| NDRV 6 FB/IN <sup>+</sup> 7                              |                                                                                          | GN PART<br>MARKING       |  |  |  |

| GN PAC<br>16-LEAD NARROW<br>T <sub>JMAX</sub> = 125°C, € | PLASTIC SSOP                                                                             | 3705<br>3705I            |  |  |  |

| Order Options Tap                                        | Order Options Tape and Reel: Add #TR                                                     |                          |  |  |  |

Order Options Tape and Reel: Add #TR

Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF

Lead Free Part Marking: http://www.linear.com/leadfree/

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = V_{BOOST} = 12V$ ,  $GND = PGND = V_{TS} = 0V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| SYMBOL                  | PARAMETER                                        | CONDITIONS                                                                                                 |   | MIN                | TYP                | MAX              | UNITS       |

|-------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------|---|--------------------|--------------------|------------------|-------------|

| V <sub>CC</sub> Supply, | , Linear Regulator and Trickle Charger Shunt Reg | ulator                                                                                                     |   |                    |                    |                  |             |

| V <sub>CCOP</sub>       | Operating Voltage Range                          |                                                                                                            |   | 7                  | 12                 | 15               | V           |

| V <sub>CCLR</sub>       | Output Voltage                                   | Linear Regulator in Operation                                                                              |   |                    | 8                  |                  | V           |

| I <sub>NDRV</sub>       | Current into NDRV Pin                            | Linear Regulator in Operation                                                                              |   | 0.1                |                    | 1                | mA          |

| t <sub>r(VCC)</sub>     | Rise Time of V <sub>CC</sub>                     | Linear Regulator Charging (0.5V to 7.5V)                                                                   |   |                    | 45                 |                  | μS          |

| I <sub>NDRVTO</sub>     | Linear Regulator Time Out Current Threshold      | Primary-Side Operation                                                                                     |   |                    | 0.27               |                  | mA          |

| I <sub>CC</sub>         | Supply Current                                   | V <sub>UVLO</sub> = 1.5V, Linear Regulator in Operation (Note 3)                                           |   |                    | 1.4                | 2.1              | mA          |

| I <sub>CCM</sub>        | Maximum Supply Current                           | V <sub>UVLO</sub> = 1.5V, Trickle Charger in Operation, V <sub>CC</sub> = 13.2V (Note 3)                   |   |                    | 1.7                | 2.5              | mA          |

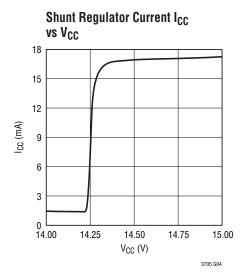

| V <sub>CCSR</sub>       | Maximum Supply Voltage                           | Trickle Charger Shunt Regulator                                                                            |   |                    | 14.25              | 15               | V           |

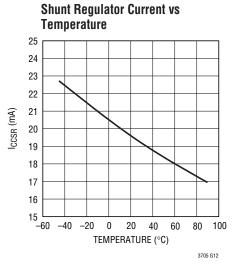

| I <sub>CCSR</sub>       | Minimum Current into NDRV/V <sub>CC</sub>        | Trickle Charger Shunt Regulator, V <sub>CC</sub> = 15V (Note 3)                                            |   | 10                 |                    |                  | mA          |

| Internal Un             | dervoltage                                       |                                                                                                            |   |                    |                    |                  |             |

| V <sub>CCUV</sub>       | Internal Undervoltage Threshold                  | V <sub>CC</sub> Rising<br>V <sub>CC</sub> Falling                                                          |   |                    | 5.3<br>4.7         |                  | V           |

| Gate Drive              | Undervoltage                                     |                                                                                                            |   |                    |                    |                  |             |

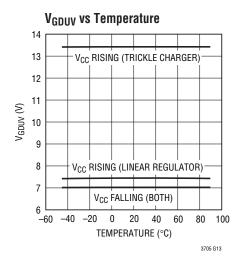

| V <sub>GDUV</sub>       | Gate Drive Undervoltage Threshold                | V <sub>CC</sub> Rising (Linear Regulator) V <sub>CC</sub> Rising (Trickle Charger) V <sub>CC</sub> Falling | • | 7.2<br>13.1<br>6.8 | 7.4<br>13.4<br>7.0 | 7.7<br>14<br>7.2 | V<br>V<br>V |

| Undervoltaç             | ge Lockout (UVLO)                                |                                                                                                            |   |                    |                    |                  |             |

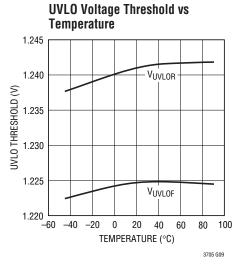

| V <sub>UVLOR</sub>      | Undervoltage Lockout Threshold Rising            | Rising                                                                                                     | • | 1.220              | 1.242              | 1.280            | V           |

| V <sub>UVLOF</sub>      | Undervoltage Lockout Threshold Falling           | Falling                                                                                                    | • | 1.205              | 1.226              | 1.265            | V           |

|                         | <u> </u>                                         |                                                                                                            |   |                    |                    |                  | 3705fb      |

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = V_{BOOST} = 12V$ , $GND = PGND = V_{TS} = 0V$ , $T_A = 25^{\circ}C$ , unless otherwise noted.

| SYMBOL                  | PARAMETER                                  | CONDITIONS                                                                    |   | MIN                     | TYP  | MAX  | UNITS |

|-------------------------|--------------------------------------------|-------------------------------------------------------------------------------|---|-------------------------|------|------|-------|

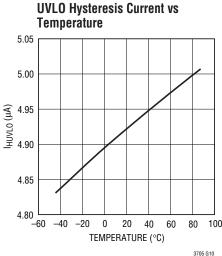

| I <sub>HUVLO</sub>      | Hysteresis Current                         | V <sub>UVLO</sub> = 1V                                                        | • | 4.2                     | 4.9  | 5.6  | μА    |

| V <sub>UVLOOP</sub>     | Voltage Feedforward Operating Range        | Primary-Side Control                                                          |   | V <sub>UVLOF(MIN)</sub> |      | 3.75 | V     |

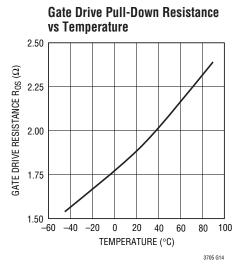

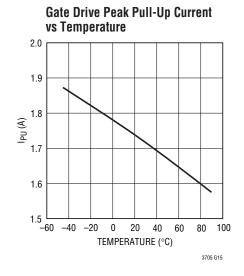

| Gate Drivers            | (TG and BG)                                |                                                                               |   |                         |      |      |       |

| R <sub>OS</sub>         | Output Pull-Down Resistance                | I <sub>OUT</sub> = 100mA                                                      |   |                         | 1.9  |      | Ω     |

| V <sub>OH</sub>         | High Output Voltage                        | $I_{OUT} = -100 \text{mA}$                                                    |   |                         | 11   |      | V     |

| I <sub>PU</sub>         | Peak Pull-Up Current                       |                                                                               |   |                         | 1.7  |      | A     |

| t <sub>r</sub>          | Output Rise Time                           | 10% to 90%, C <sub>OUT</sub> = 4.7nF                                          |   |                         | 40   |      | ns    |

| t <sub>f</sub>          | Output Fall Time                           | 10% to 90%, C <sub>OUT</sub> = 4.7nF                                          |   |                         | 70   |      | ns    |

| Rectifier               |                                            |                                                                               |   |                         |      |      |       |

| I <sub>RECT</sub>       | Maximum Rectifier DC Output Current        |                                                                               |   |                         |      | 25   | mA    |

| Oscillator              |                                            |                                                                               |   |                         |      |      |       |

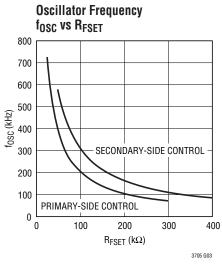

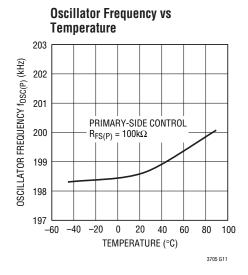

| f <sub>OSC(P)</sub>     | Oscillator Frequency                       | Primary-Side Control, $R_{FS(P)} = 100k\Omega$                                |   |                         | 200  |      | kHz   |

|                         |                                            | Primary-Side Control, $R_{FS(P)} = 25k\Omega$                                 |   |                         | 700  |      | kHz   |

|                         | Oscillator Desister Cet Assurance          | Primary-Side Control, $R_{FS(P)} = 300k\Omega$<br>Primary-Side Control        |   |                         | 70   |      | kHz   |

| $\Delta f_{RFS(P)}$     | Oscillator Resistor Set Accuracy           | 25k < R <sub>FSET</sub> < 300k                                                |   |                         | ±15  |      | %     |

| f <sub>OSC(S)</sub>     | Oscillator Frequency                       | Secondary-Side Control (During Start-Up),                                     |   |                         | 300  |      | kHz   |

| 1030(3)                 |                                            | $R_{FS(S)} = 100k\Omega$                                                      |   |                         |      |      |       |

| Soft-Start/Fa           | ult (SSFLT)                                |                                                                               |   |                         |      |      |       |

| I <sub>SS(C)</sub>      | Soft-Start Charge Current                  | Primary-Side Control, V <sub>SSFLT</sub> = 2V                                 |   |                         | -5.2 |      | μА    |

|                         |                                            | Secondary-Side Control, V <sub>UVLO</sub> = 1.3V,                             |   |                         | -4   |      | μΑ    |

|                         |                                            | V <sub>SSFLT</sub> = 2V<br>Secondary-Side Control, V <sub>UVLO</sub> = 3.75V, |   |                         | -1.6 |      | μΑ    |

|                         |                                            | V <sub>SSFLT</sub> = 2V                                                       |   |                         | 1.0  |      |       |

| V <sub>LRTO</sub>       | Linear Regulator Time Out-Threshold        |                                                                               |   |                         | 3.9  |      | V     |

| $V_{FLTH}$              | Fault Output High                          | V <sub>CC</sub> = 8V                                                          |   |                         | 6.7  |      | V     |

| I <sub>SS(D)</sub>      | Soft-Start Discharge Current               | Timing Out After Fault, V <sub>SSFLT</sub> = 2V                               |   |                         | 1    |      | μА    |

| Current Sens            | se Input (I <sub>S</sub> )                 |                                                                               |   |                         |      |      |       |

| V <sub>IS(MAX)</sub>    | Overcurrent Threshold                      |                                                                               |   |                         | 300  |      | mV    |

| Volt Second             | Limit (V <sub>SLMT</sub> )                 |                                                                               |   |                         |      |      |       |

| V <sub>VSL(MAX)</sub>   | Volt-Second Limit Threshold                |                                                                               |   |                         | 1.26 |      | V     |

| I <sub>VSLMT(MAX)</sub> | Maximum Volt-Second Limit Resistor Current |                                                                               |   |                         | 0.25 |      | mA    |

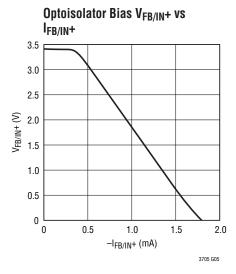

| Optoisolator            | Bias Current                               |                                                                               |   |                         |      |      |       |

| V <sub>OPTO</sub>       | Open Circuit Optoisolator Voltage          | Primary-Side Control I <sub>FB</sub> = 0V                                     |   |                         | 3.3  |      | V     |

| I <sub>OPTO</sub>       | Optoisolator Bias Current                  | Primary-Side Control V <sub>FB</sub> = 2.5V                                   |   |                         | 0.5  |      | mA    |

|                         |                                            | Primary-Side Control V <sub>FB</sub> = 0V                                     |   |                         | 1.6  |      | mA    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Operating junction temperature  $T_J$  (in °C) is calculated from the ambient temperature  $T_A$  and the average power dissipation PD (in watts) by the formula:  $T_J = T_A + \theta_{JA} \cdot PD$ . Refer to the Applications Information section for details.

Note 3:  $I_{CC}$  is the sum of current into NDRV and  $V_{CC}$ .

**Note 4:** The LTC3705EGN is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3705IGN is guaranteed and tested over the -40°C to 85°C operating temperature range.

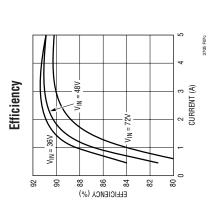

# TYPICAL PERFORMANCE CHARACTERISTICS (TA = 25°C unless otherwise specified)

# TYPICAL PERFORMANCE CHARACTERISTICS ( $T_A = 25^{\circ}C$ unless otherwise specified)

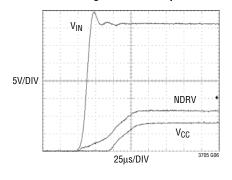

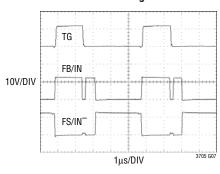

#### **Linear Regulator Start-Up**

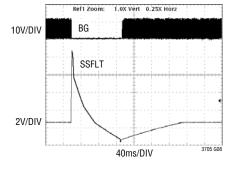

#### **Fault Operation**

### PIN FUNCTIONS

GND (Pin 1): Signal Ground.

**Is (Pin 2):** Input to the Overcurrent Comparator. Connect to the positive terminal of a current-sense resistor in series with the source of the ground-referenced bottom MOSFET.

$V_{SLMT}$  (Pin 3): Volt-Second Limit. Form an R-C integrator by connecting a resistor from  $V_{IN}$  to  $V_{SLMT}$  and a capacitor from  $V_{SLMT}$  to ground. The gate drives are turned off when the voltage on the  $V_{SLMT}$  pin exceeds 1.25V.

**UVLO (Pin 4):** Undervoltage Lockout. Connect to a resistive voltage divider to monitor input voltage  $V_{IN}$ . Enables converter operation for  $V_{UVLO} > 1.242V$ . Hysteresis is a fixed 16mV hysteresis voltage with a 4.9 $\mu$ A hysteresis current that combines with the Thevenin resistance of the divider to set the total UVLO hysteresis voltage. This input also senses  $V_{IN}$  for voltage feedforward. Finally, this pin can be used for external run/stop control.

**SSFLT (Pin 5):** Combination Soft-Start and Fault Indicator. A capacitor to GND sets the duty cycle ramp-up rate during start-up. To indicate a fault, the SSFLT pin is momentarily pulled up to within 1.3V of  $V_{CC}$ .

**NDRV (Pin 6):** Drive for the External NMOS of the Linear Regulator. Connect to the gate of the NMOS and connect a pull up resistor to the input voltage  $V_{IN}$ . Optionally, to create a trickle charger omit the NMOS device and connect NDRV to  $V_{CC}$ .

**FB/IN**<sup>+</sup> **(Pin 7):** This pin has several functions. The two terminals of one pulse transformer winding are connected to the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins. The other pulse transformer winding is connected to the LTC3706. The LTC3705 automatically detects when the LTC3706 applies a pulse-encoded signal to the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins and decodes

duty cycle information for control of the primary-side gate drives (see Operation below). In secondary-side control, primary-side gate drive bias power is also extracted from the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins using an on-chip full-wave rectifier.

For primary-side control connect this pin to an optoisolator for feedback control of converter output voltage using an internal optoisolator biasing network.

**FS/IN**<sup>-</sup> (**Pin 8**): This pin has several functions. Place a resistor from this pin to GND to set the oscillator frequency. For secondary-side control with the LTC3706, connect one winding of the pulse transformer for operation as described for the FB/IN<sup>+</sup> pin above.

**PGND (Pin 9):** Supply Return for the Bottom Gate Driver and the On-Chip Bridge Rectifier.

**BG (Pin 10):** Bottom Gate Driver. Connect to the gate of the "low side" external MOSFET.

$V_{CC}$  (Pin 11): Main  $V_{CC}$  Power for All Driver and Control Circuitry.

**NC (Pins 12, 13):** Voltage Isolation Pins. No connection. Provided to allow adequate clearance between high-voltage pins (BOOST, TG, and TS) and the remainder of the pins.

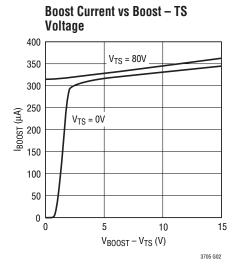

**BOOST (Pin 14):** Top Gate Driver Supply. Connect to  $V_{CC}$  with a diode to supply power to the "high side" external MOSFET and bypass with a capacitor to TS.

**TG (Pin 15):** Top Gate Driver. Connect to the gate of the "high side" external MOSFET.

**TS (Pin 16):** Supply Return for the Top Gate Driver. Connect to the source of the "high side" external MOSFET.

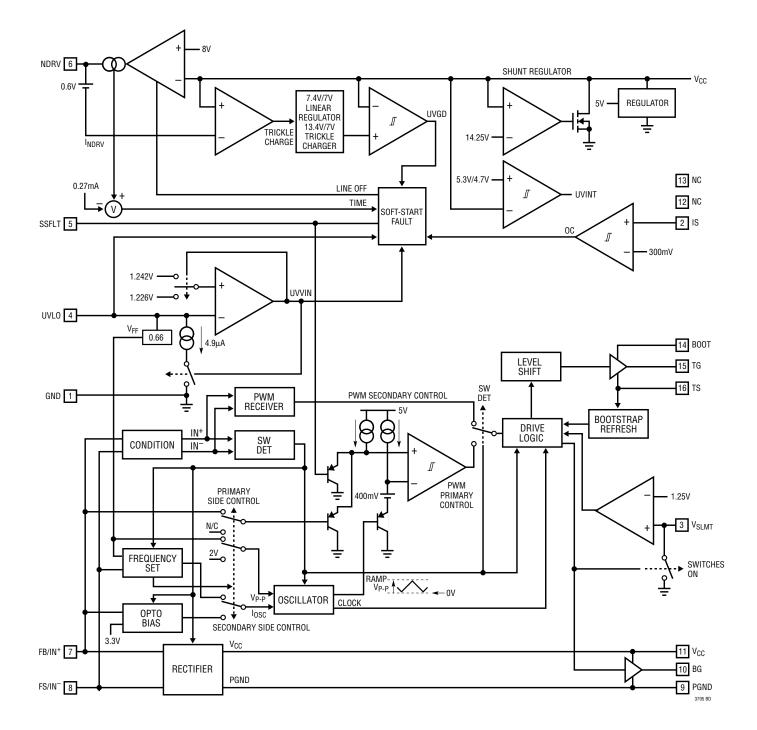

# **BLOCK DIAGRAM**

### **OPERATION**

### **Mode Setting**

The LTC3705 is a controller and gate driver designed for use in a 2-switch forward converter. When used in conjunction with the LTC3706 PolyPhase secondary-side synchronous forward controller it forms a complete 2-switch forward converter with secondary-side regulation, galvanic isolation between input and output, and synchronous rectification. In this mode, upon start-up, the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins are effectively shorted by one winding of the pulse transformer. The LTC3705 detects this short circuit to determine that it is in secondary-side control mode. Operation in this mode is confirmed when the LTC3706 begins switching the pulse transformer.

Alternately, the LTC3705 can be used as a standalone primary-side controller. In this case, the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins operate independently. The FB/IN<sup>+</sup> pin is connected to the collector of an optoisolator to provide feedback and the FS/IN<sup>-</sup> pin is connected to the frequency set resistor.

#### **Gate Drive Encoding**

In secondary-side control with the LTC3706, after a startup sequence, the LTC3706 transmits multiplexed PWM information through a pulse transformer to the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> inputs of the LTC3705. In the LTC3705, the PWM receiver extracts the duty cycle and uses it to control the top and bottom gate drivers.

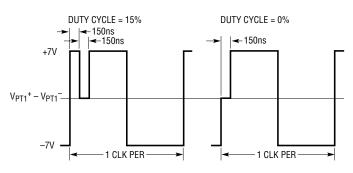

Figure 1 shows that the LTC3706 drives the pulse transformer in a complementary fashion, with a duty cycle of approximately 50%. At the appropriate time during the positive half cycle, the LTC3706 applies a short (150ns) zero-voltage pulse across the pulse transformer, indicating the end of the "on" time. Although this scheme allows

Figure 1. Gate Drive Multiplexing Scheme

the transmission of 0% to 50% duty cycle, it is necessary to establish a minimum controllable "on" time of approximately 100ns. This ensures that 0% duty cycle can be reliably distinguished from 50% duty cycle.

#### **On-Chip Rectifier**

Simultaneously with duty-cycle decoding, and through the same pulse transformer, the near-square-wave generated by the LTC3706 provides primary-side  $V_{CC}$  gate drive bias power by way of the LTC3705's on-chip full-wave bridge rectifier. No auxiliary bias supply is necessary and forward converter design and circuitry are considerably simplified.

#### **External Series Pass Linear Regulator**

The LTC3705 features an external series pass linear regulator that eliminates the long start-up time associated with the conventional trickle charger. The drain of an external NMOS is connected to the input voltage and the source is connected to V<sub>CC</sub>. The gate of the NMOS is connected to NDRV. To power the gate, an external pull-up resistor is connected from the input voltage to NDRV. The NMOS must be a standard 3V threshold type (i.e. not logic level). An on-chip circuit manages the start up and operation of the linear regulator. It takes approximately 45 us for the linear regulator to charge V<sub>CC</sub> to its target value of 8V (unless limited by a slower rise of  $V_{IN}$ ). The LTC3705 begins operating the gate drives when  $V_{CC}$  reaches 7.4V. Often, the thermal rating of the NMOS prevents it from operating continuously, and the LTC3705 "times out" the linear regulator to prevent overheating. This is accomplished using the capacitor connected to the SSFLT pin as described subsequently.

#### **Trickle Charger Shunt Regulator**

Alternately, a trickle charger can be implemented by eliminating the external NMOS and connecting NDRV to  $V_{CC}$  and using the pull-up resistor to charge  $V_{CC}$ . To allow extra headroom for starting, the LTC3705 detects this mode and increases the threshold for starting the gate drives to 13.4V. An internal shunt regulator limits the voltage on the trickle charger to 15V.

### **OPERATION**

#### **Self-Starting Architecture**

The LTC3705 is combined with the LTC3706 to form a complete self-starting DC isolated power supply. When power is first applied, and when V<sub>CC</sub> for the LTC3705 is above the appropriate threshold, the LTC3705 begins open-loop operation using its own internal oscillator. Power is supplied to the secondary by switching the gate drivers with a gradually increasing duty cycle as controlled by the rate of rise of the voltage on the SSFLT pin. A peak detector power supply for the LTC3706 allows it to begin operation even for small duty cycles. Once adequate voltage is available for the LTC3706, it provides duty cycle information and gate drive bias power using the pulse transformer as shown in Figure 1. The LTC3705 detects the appearance of this signal and transfers control of the gate drivers to the LTC3706. Simultaneously, the LTC3705 also enables the on-chip rectifier and turns off the linear regulator.

Alternately, when the LTC3705 is used as a standalone primary-side controller, the gradually increasing duty cycle powers up a secondary-side reference and optoisolator and feedback is accomplished when the output of the optoisolator begins pulling down in the FB/IN+ pin.

#### **Soft-Start and Fault**

These two functions are implemented using the SSFLT pin. (This pin is also used for linear regulator timeout as described in the following section.)

Initiating soft-start requires that: 1) the gate drive undervoltage (UVGD) goes low meaning that adequate voltage is available on the  $V_{CC}$  pin (7.4V for the linear regulator or 13.4V for the trickle charger) and 2) the input undervoltage (UVV $_{IN}$ ) goes low meaning that the voltage on the UVLO pin has reached the 1.242V rising threshold.

During soft-start, the LTC3705 gradually charges the softstart capacitor to ramp up the converter duty cycle. Softstart is over when the voltage on the SSFLT pin reaches 2.8V. In normal operation, at some point before this, the LTC3705 makes a transition to controlling duty cycle using closedloop regulation of the converter output voltage.

The SSFLT pin is also used to indicate a fault. The LTC3705 recognizes faults from four origins: 1) an overcurrent fault

caused by the current sense voltage on the IS pin exceeding the 300mV overcurrent threshold, 2) an input undervoltage fault caused by the UVLO pin falling below the 1.226V falling threshold, 3) a gate drive undervoltage fault caused by the voltage on the  $V_{CC}$  pin falling below the 7V threshold, or 4) loss of the gate drive encoding signal from the LTC3706.

Upon sensing a fault, the LTC3705 immediately turns off the top and bottom gate drives and indicates a fault by quickly pulling the voltage on the SSFLT pin to within 1.3V of the voltage on the  $V_{CC}$  pin. After indicating the fault, the LTC3705 quickly ramps down the voltage on the SSFLT pin to approximately 2.8V. Then, to allow complete discharge of the secondary-side circuit, the LTC3705 slowly ramps down the voltage on the SSFLT pin to about 200mV. The LTC3705 then attempts a restart.

#### **Linear Regulator Timeout**

The thermal rating of the linear regulator's external NMOS often cannot allow it to indefinitely supply bias current to the primary-side gate drives. The LTC3705 has a linear regulator timeout mechanism that also uses the SSFLT capacitor.

As described in the prior section, soft-start is over once the voltage on the SSFLT pin reaches 2.8V. However, the SSFLT capacitor continues to charge and the linear regulator is turned off when the voltage on the SSFLT pin reaches 3.9V. The "Applications Information" section describes linear regulator timeout in more detail.

#### **Volt-Second Limit**

The volt-second limit ensures that the power transformer core does not saturate for any combination of duty cycle and input voltage. The input of an R-C integrator is connected to  $V_{IN}$  and its output is connected to the  $V_{SLMT}$  pin. While the top and bottom gate drives are "off," the LTC3705 grounds the  $V_{SLMT}$  pin. When the gate drives are turned "on" the  $V_{SLMT}$  pin is released and the capacitor is allowed to charge in proportion to  $V_{IN}$ . If the capacitor voltage on the  $V_{SLMT}$  pin exceeds 1.25V the two gate drives are immediately turned "off." Note that this is not considered a fault condition and the LTC3705 can run indefinitely with the switch duty cycle being determined by

### **OPERATION**

the volt-second limit circuit. The duty cycle is always limited to 50% to ensure that the power transformer flux always has time to reset before the start of the next cycle.

In an alternate application, the volt-second limit can be used for open-loop regulation of the output against changes in  $V_{\text{IN}}$ .

#### **Current Limit**

Current limit for the LTC3705 is principally a safety feature to protect the converter and is not part of a control function. The current that flows in series through the top switch, the transformer primary, and the bottom switch is sensed by a resistor connected between the source of the bottom switch and GND. If the voltage across this resistor exceeds 300mV, the LTC3705 initiates a fault.

#### **Bootstrap Refresh**

The LTC3705 incorporates a unique bootstrap refresh circuit to ensure that the bootstrap supply (BOOST) for the top switch has adequate voltage for operation at low duty cycles. Therefore, the LTC3705 does not require a undervoltage lockout for the bootstrap supply and a potential source of unexpected shutdowns is eliminated.

#### **Voltage Feedforward**

The LTC3705 uses voltage feedforward to properly modulate the duty cycle as a function of the input voltage. For secondary-side control with the LTC3706, voltage feedforward is used during start-up only. The duty cycle

during start up is determined by comparison of the voltage on the SSFLT pin to a 50% duty cycle triangle wave with an amplitude of 2V. To implement voltage feedforward, the charging current for the soft-start capacitor is reduced in proportion to the input voltage. As a result, the initial rate of rise of the converter output voltage is held approximately constant regardless of the input voltage. At some point during start-up, the LTC3706 begins to switch the pulse transformer and takes over the soft-start.

For operation with standalone primary-side control and optoisolator feedback, voltage feedforward is used during both start-up and normal operation. The duty cycle is determined by using a 50% duty cycle triangle wave with an amplitude equal to 66% of the voltage on the UVLO pin which is, in turn, proportional to  $V_{IN}$ . The charging current for the soft-start capacitor is a constant 5.2 $\mu$ A. During soft-start, the duty cycle is determined by comparing the voltage on the SSFLT pin to the triangle wave. Soft-start is concluded when the voltage on the SSFLT pin exceeds the voltage on the FB/IN+ pin. After the conclusion of soft-start, the duty cycle is determined by comparison of the voltage on the FB/IN+ pin to the triangle wave.

#### **Optoisolator Bias**

When the LTC3705 is used in standalone primary-side mode, feedback is provided by an optoisolator connected to the FB/IN+ pin. The LTC3705 has a built optoisolator bias circuit which eliminates the need for external components.

# APPLICATIONS INFORMATION

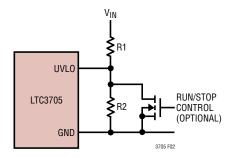

#### UVL0

The UVLO pin is connected to a resistive voltage divider connected to  $V_{IN}$  as shown in Figure 2. The voltage threshold on the UVLO pin for  $V_{IN}$  rising is 1.242V. To introduce hysteresis, the LTC3705 draws 4.9 $\mu$ A from the UVLO pin when  $V_{IN}$  is rising. The hysteresis is therefore user adjustable and depends on the value of R1. The UVLO threshold for  $V_{IN}$  rising is:

$$V_{IN(UVLO, RISING)} = (1.242V) \frac{R1 + R2}{R2} + R1(4.9\mu A)$$

The LTC3705 also has 16mV of voltage hysteresis on the UVLO pin so that the UVLO threshold for  $V_{IN}$  falling is:

$$V_{IN(UVLO, FALLING)} = (1.226V) \frac{R1 + R2}{R2}$$

To implement external Run/Stop control, connect a small NMOS to the UVLO pin as shown in Figure 2. Turning the NMOS on grounds the UVLO pin and prevents the LTC3705 from running.

Figure 2. Resistive Voltage Divider for UVLO and Optional Run/Stop Control

#### **Linear Regulator**

The linear regulator eliminates the long start-up times associated with a conventional trickle charger by using an external NMOS to quickly charge the capacitor connected to the  $V_{CC}$  pin.

Note that a trickle charger usually requires a large capacitor to provide holdup for the  $V_{CC}$  pin while the converter attempts to start. The linear regulator in the LTC3705 can both charge the capacitor connected to the  $V_{CC}$  pin and provide primary-side gate-drive bias current. Therefore, with the linear regulator, the capacitor need only be large enough to cope with the ripple current from driving the top and bottom gates and holdup need not be considered.

The external NMOS for the linear regulator should be a standard 3V threshold type (i.e. not a logic level threshold). The rate of charge of  $V_{CC}$  from 0V to 8V is controlled by the LTC3705 to be approximately 45 $\mu$ s regardless of the size of the capacitor connected to the  $V_{CC}$  pin. The charging current for this capacitor is approximately:

$$I_{\rm C} = \frac{8V}{45\mu s} {\rm C}$$

The safe operating area (SOA) for the external NMOS should be chosen so that capacitor charging does not damage the NMOS. Excessive values of capacitor are unnecessary and should be avoided.

### **Start-Up Considerations**

When used in a self-starting converter with the LTC3706, the LTC3705 initially begins the soft-start of the converter in an open-loop fashion. After bias is obtained on the secondary side, the LTC3706 assumes control and

completes the soft-start interval. In order to ensure that control is properly transferred from the LTC3705 (primary-side) to the LTC3706 (secondary-side), it is necessary to limit the rate of rise on the primary-side soft-start ramp so that the LTC3706 has adequate time to wake up and assume control before the output voltage gets too high. This condition is satisfied for many applications if the following relationship is maintained:

$$C_{SS,SEC} \leq C_{SS\_PRI}$$

However, care should be taken to ensure that soft-start transfer from primary-side to secondary-side is completed well before the output voltage reaches its target value. A good design goal is to have the transfer completed when the output voltage is less than one-half of its target value. Note that the fastest output voltage rise time during primary-side soft-start mode occurs with minimum load current.

The open-loop start-up frequency on the LTC3705 is set by placing a resistor  $R_{FS(S)}$  from the FS/IN $^-$  pin to GND. Although the exact start-up frequency on the primary side is not critical, it is generally a good practice to set it approximately equal to the operating frequency on the secondary side.

In this mode the start-up frequency of the LTC3705 is approximately:

$$f_{PRI} = \frac{34 \cdot 109}{R_{FS(S)} + 10,000}$$

In the event that the LTC3706 fails to start up properly and assume control of switching, there are several fail-safe mechanisms to help avoid overvoltage conditions. First, the LTC3705 implements a volt-second clamp that may be used to keep the primary-side duty cycle at a level that does not produce an excessive output voltage. Second, the timeout of the linear regulator (described in the following section) means that, unless the LTC3706 starts and supports the LTC3705's gate drives through the pulse transformer and on-chip rectifier, the LTC3705 eventually suffers a gate drive undervoltage fault. Finally, the LTC3706 has an independent overvoltage detection circuit that crowbars the output of the DC/DC converter using the synchronous secondary-side MOSFET switch.

In the event that a short-circuit is applied to the output of the converter prior to start-up, the LTC3706 generally does not receive enough bias voltage to operate. In this case, the LTC3705 detects a FAULT for one of two reasons: 1) since the LTC3706 never sends pulse encoding to the LTC3705, the linear regulator times out resulting in a gate drive undervoltage fault, or 2) the primary-side overcurrent circuit is tripped because of current buildup in the output inductor. In either case, the LTC3705 initiates a shutdown followed by a soft-start retry.

#### **Linear Regulator Timeout**

After start-up, the LTC3705 times out the linear regulator to prevent overheating of the external NMOS. The timeout interval is set by further charging the soft-start capacitor  $C_{SSFLT}$  from the end-of-soft-start voltage of approximately 2.8V to the timeout threshold of 3.9V. Linear regulator timeout behaves differently depending on mode.

In primary-side standalone mode, the LTC3705 generally requires that an auxiliary gate drive bias supply take over from the linear regulator. (See the subsequent section for more detail on the auxiliary supply.) During linear regulator timeout, the rate of rise of the soft-start capacitor voltage depends on the current into the NDRV pin as controlled by the pull-up resistor  $R_{PULLUP},$  the value of  $V_{IN}$  and the value of  $V_{NDRV}.$

$$I_{NDRV} = \frac{V_{IN} - V_{NDRV}}{R_{PULLUP}}$$

The value of  $V_{NDRV}$  is  $V_{CC}$  = 8V plus the value of the gate-to-source voltage ( $V_{NDRV} - V_{CC}$ ) of the external NMOS in the linear regulator. The gate-to-source voltage depends on the actual device but is approximately the threshold voltage of the external NMOS.

For  $I_{NDRV} > 0.27 mA$ , the capacitor on the SSFLT pin is charged in proportion to  $(I_{NDRV} - 0.27 mA)$  until the linear regulator times out. Thus, since  $V_{NDRV}$  is very nearly constant, the timeout interval for the linear regulator is inversely proportional to the input voltage and a higher input voltage produces a shorter timeout.

$$t_{TIMEOUT} = \frac{66C_{SSFLT}(3.9V - 2.8V)}{\left[\frac{V_{IN} - V_{NDRV}}{R_{PULLUP}} - 0.27\text{mA}\right]}$$

Since the power dissipation of the linear regulator is proportional to the input voltage, this strategy of making the timeout inversely proportional to the input voltage produces an approximately constant temperature excursion for the external NMOS of the linear regulator regardless of the input voltage.

In situations for which the continuous operation of the linear regulator does not exceed the thermal limitations of the external NMOS (i.e. converters with low  $V_{\text{IN}}$  or with minimal gate drive bias requirements), the auxiliary supply can be omitted and the linear regulator allowed to operate continuously. If  $I_{\text{NDRV}}$  is less than 0.27mA the linear regulator never times out and the voltage on the SSFLT pin stays at approximately 2.8V after start-up is completed. To accomplish this set:

$$R_{PULLUP} > \frac{V_{IN(MAX)} - V_{NDRV}}{0.27mA}$$

where  $V_{IN(MAX)}$  is the maximum expected continuous input voltage. Note that once the linear regulator is turned off it locks out. Therefore when using this strategy, care should be taken to ensure that a transient higher than  $V_{IN(MAX)}$  does not persist longer than  $t_{TIMEOUT}$ .

In secondary-side operation with the LTC3706, there is never any need for continuous operation of the linear regulator since gate drive bias power is provided by the LTC3706 through the pulse transformer and on-chip rectifier. The LTC3705 shuts down the linear regulator once the LTC3706 begins switching the pulse transformer. If the LTC3706 fails to start, the LTC3705 quickly times out the linear regulator once the voltage on the SSFLT pin reaches 2.8V.

#### **Fault Lockout**

The LTC3705 indicates a fault by pulling the SSFLT pin to within 1V of  $V_{CC}$ . The LTC3705 subsequently attempts a restart. Optionally, the user can prevent restart and "lock out" the converter by clamping the voltage on the SSFLT pin with a 4.3V Zener diode. Once the converter has locked out it can only be restarted by the removal of the input voltage or by release of the Zener diode clamp.

#### **Pulse Transformer**

The pulse transformer that connects the LTC3706 to the LTC3705 performs the dual functions of gate drive duty cycle encoding and gate drive bias supply for the LTC3705 by way of the on-chip full-wave rectifier. The designs of the LTC3705 and LTC3706 have been coordinated so that the transformer turn ratio is:

$$N_{LTC3705} = 2N_{LTC3706}$$

where  $N_{LTC3705}$  is the number of turns in the winding connected to the FB/IN<sup>+</sup> and FS/IN<sup>-</sup> pins of the LTC3705 and  $N_{LTC3706}$  is the number of turns in the winding connected to the PT<sup>+</sup> and PT<sup>-</sup> pins of the LTC3706. The winding connected to the LTC3706 must be able to withstand volt-seconds equal to:

$$(V-s)_{MAX} = \frac{V_{CC}}{2f}$$

where  $V_{CC}$  is the maximum supply voltage for the LTC3706 and f is the operating frequency of the LTC3706.

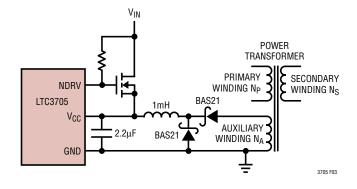

### **Auxiliary Supply**

When used with the LTC3706, the LTC3705 does not require an auxiliary supply to provide primary-side gatedrive bias current. After start-up, primary-side gate drive current is provided by the LTC3706 through a small pulse transformer and the LTC3705's on-chip rectifier.

However, when used as a standalone primary-side controller, the LTC3705 may require a conventional gate-drive bias supply as shown in Figure 3. The bias supply must be

Figure. 3. Auxiliary Supply for Primary-Side Control

designed to keep the voltage on the  $V_{CC}$  pin between the absolute maximum of 15V and the gate-drive undervoltage lockout of 7V.

The auxiliary supply is connected in parallel with  $V_{CC}$ . The linear regulator maintains  $V_{CC}$  at 8V. If the auxiliary supply produces more than 8V, it turns off the external NMOS before the LTC3705 can time out the linear regulator. If the auxiliary supply produces less than 8V, the linear regulator times out and then the voltage on the  $V_{CC}$  pin declines to the voltage produced by the auxiliary supply.

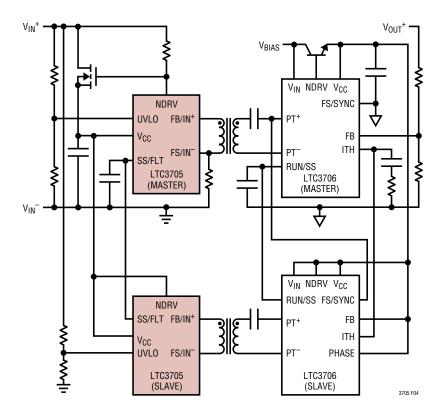

#### **Slave Mode Operation**

When the LTC3705 is paired with the LTC3706, multiple pairs can be used to form a PolyPhase converter. In PolyPhase operation, one LTC3705 becomes the "master" while the remainder become "slaves." The master controls start-up in the same manner as for the single-phase converter, while the slaves do not begin switching until receiving PWM information through their own pulse transformer from their corresponding LTC3706. To synchronize operation, the SSFLT and  $V_{CC}$  pins of the master are connected to the corresponding pins of all the slaves. The master is designated by connection of the frequency set resistor to the FS/IN $^-$ pin while this resistor is omitted from the slaves. For the slaves the NDRV pin is connected to the  $V_{CC}$  pin. See the following section on PolyPhase Applications for more detail.

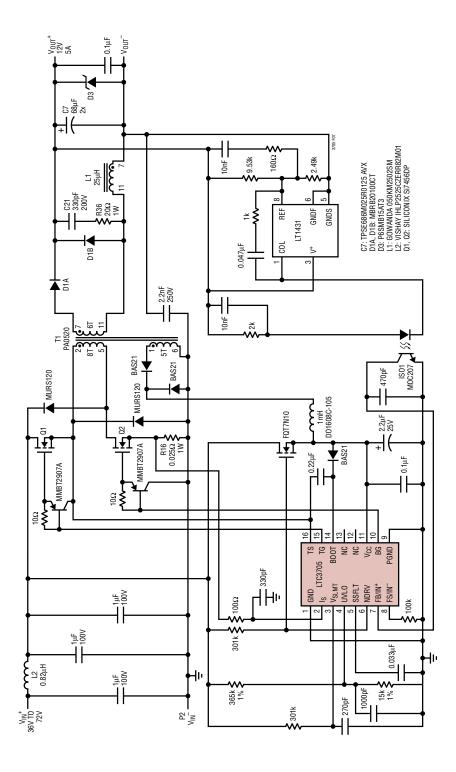

#### PolyPhase Applications

Figure 4 shows the basic connections for using the LTC3705 and LTC3706 in PolyPhase applications. One of the phases is always identified as the "master," while all other phases are "slaves." For the LTC3705 (primary side), the master performs the open-loop start-up and supplies the initial  $V_{\rm CC}$  voltage for the master and all slaves. The LTC3705 slaves are put into that mode by omitting the resistor on FS/IN—. The LTC3705 slaves simply stand by and wait for PWM signals from their respective pulse transformers. Since the SSFLT pins of master and slave LTC3705s are interconnected, a FAULT (overcurrent, etc.) on any one of the phases will perform a shutdown/restart on all phases together.

For the LTC3706, the master performs soft-start and voltage-loop regulation by driving all slaves to the same current as the master using the  $I_{TH}$  pins. Faults and shutdowns are communicated via the interconnection of the RUN/SS pins. The LTC3706 is put into slave mode by tying the FB pin to  $V_{CC}$ .

#### Standalone Primary-Side Operation

The LTC3705 can be used to implement a standalone forward converter using optoisolator feedback and a secondary-side voltage reference. Alternately the LTC3705 can be used to implement an open-loop forward converter using the VSLMT pin to regulate against changes in  $V_{IN}$ . In either case, the LTC3705 oscillator determines the frequency as found from:

$$f_{OSC} = \frac{21 \cdot 10^9}{R_{FS(P)} + 4200}$$

Note that polyphase operation is not possible in the standalone configuration.

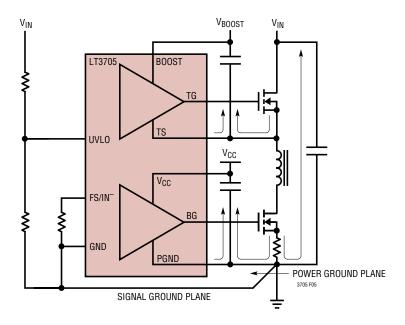

#### **Grounding Considerations**

The LT3705 is typically used in high current converter designs that involve substantial switching transients. Figure 5 illustrates these currents. The switch drivers on the IC are designed to drive large capacitances and, as such, generate significant transient currents. Careful consideration must be made regarding input and local power supply bypassing to avoid corrupting the ground references used by the UVLO and frequency set circuitry.

Typically, high current paths and transients from the input supply and any local drive supplies must be kept isolated from GND. By virtue of the topologies used in LT3705 applications, the large currents from the primary switches, as well as the switch drive transients, pass through the sense resistor to ground. This defines the ground connection of the sense resistor as the reference point for both GND and PGND.

Effective grounding can be achieved by considering the return current paths from the sense resistor to each respective bypass capacitor. Don't be tempted to run small traces to separate the grounds. A power ground plane is important as always in high power converters, but care must be taken to keep high current paths away from the GND reference. An effective approach is to use a 2-layer ground plane, reserving an entire layer for GND and an entire layer for PGND. The UVLO and frequency set resistors can then be directly connected to the GND plane.

Figure 4. Connections for PolyPhase

Figure 5. High-Current Transient Return Paths

# TYPICAL APPLICATIONS

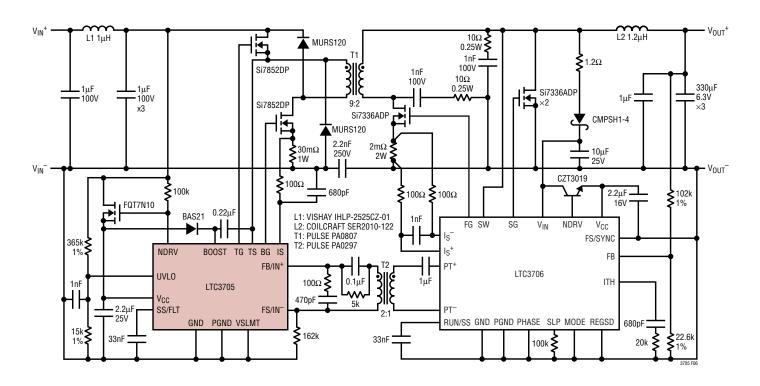

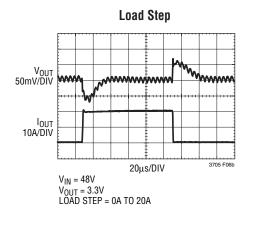

Figure 6. 36V-72V to 3.3V/20A Isolated Forward Converter Using LTC3706

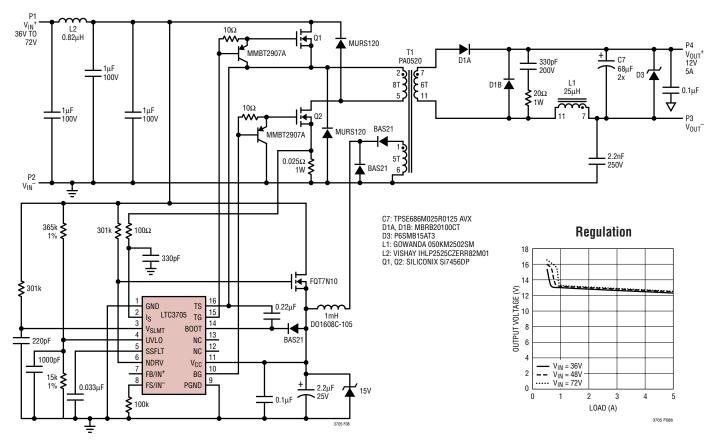

# TYPICAL APPLICATIONS

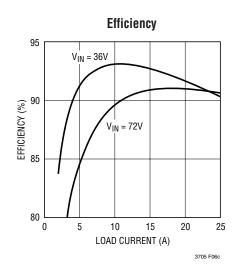

Figure 7. 36V-72V to 12V/5A Isolated Forward Converter Using Optoisolator

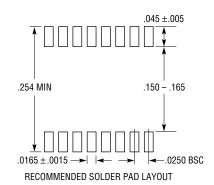

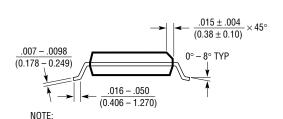

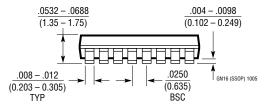

# PACKAGE DESCRIPTION

#### GN Package 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

- 1. CONTROLLING DIMENSION: INCHES

- 2. DIMENSIONS ARE IN  $\frac{\text{INCHES}}{\text{(MILLIMETERS)}}$

- 3. DRAWING NOT TO SCALE

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

# TYPICAL APPLICATION

Figure 8. 36V-72V to 12V/5A Open-Loop Regulated Isolated Forward Converter Using VSLMT

# **RELATED PARTS**

| PART NUMBER       | NUMBER DESCRIPTION COMMENTS                                                  |                                                                                                               |

|-------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| LTC1693           | High Speed Single/Dual N-Channel MOSFET Drivers                              | CMOS Compatible Input, V <sub>CC</sub> Range: 4.5V to 12V                                                     |

| LTC1698           | Secondary Synchronous Rectifier Controller                                   | Use with the LT1681, Optocoupler Driver, Pulse Transformer Synchronization                                    |

| LT1950            | Single Switch Controller                                                     | Used for 20W to 500W Forward Converters                                                                       |

| LTC3706           | Polyphase Secondary-Side Synchronous<br>Forward Controller                   | Fast Transient Response, Self-Starting Architecture, Current Mode Control                                     |

| LT3710            | Secondary-Side Synchronous Post Regulator                                    | For Regulated Auxiliary Output in Isolated DC/DC Converters                                                   |

| LT3781            | "Bootstrap" Start Dual Transistor Synchronous<br>Forward Controller          | 72V Operation, Synchronous Switch Output                                                                      |

| LT3804            | Secondary Side Dual Output Controller with Opto Driver                       | Regulates Two Secondary Outputs, Optocoupler Feedback Driver and Second Output Synchronous Driver Controller  |

| LTC3901           | Secondary-Side Synchronous Driver for<br>Push-Pull and Full-Bridge Converter | Similar Function to LTC3900, Used in Full-Bridge and Push-Pull Converter                                      |

| LTC4440/LTC4440-5 | High Speed, High Voltage and High Side<br>Gate Drivers                       | High Side Source Up to 100V, Up to 15V Gate Drive Supply, 6-Lead ThinSOT™ or 8-Lead Exposed Pad MSOP Packages |

| LTC4441           | 6A MOSFET Driver                                                             | Adjustable Gate Drive from 5V to 8V, 5V to 28V V <sub>IN</sub> Range                                          |

ThinSOT is a trademark of Linear Technology Corporation.