# Contents

| 1 | Bloc | k diagram                                                   | 6    |

|---|------|-------------------------------------------------------------|------|

| 2 | Pins | description                                                 | 7    |

|   | 2.1  | PowerSO-20                                                  | 7    |

|   | 2.2  | PowerSO16                                                   | 8    |

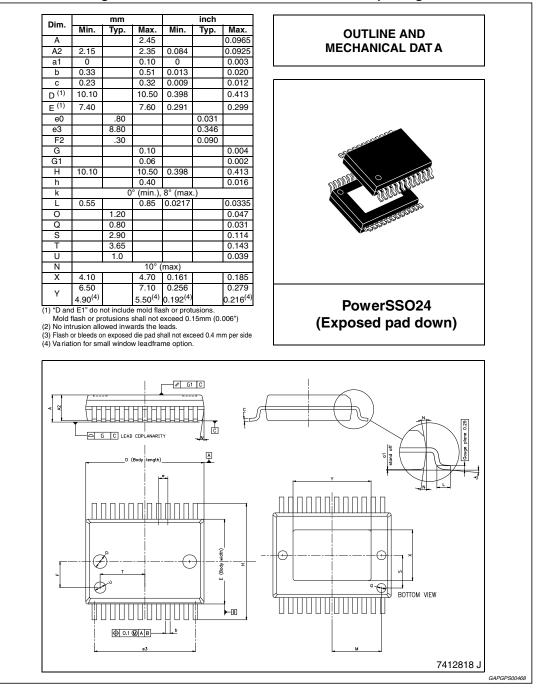

|   | 2.3  | PowerSSO24                                                  | 9    |

| 3 | Devi | ce description                                              | . 10 |

|   | 3.1  | Supply range                                                | . 10 |

|   | 3.2  | Control inputs                                              | . 10 |

|   |      | 3.2.1 DI and EN inputs                                      | . 10 |

|   |      | 3.2.2 DIR and PWM inputs                                    | . 11 |

|   | 3.3  | Serial peripheral interface (SPI)                           | . 12 |

|   |      | 3.3.1 Daisy chain operation                                 | . 14 |

|   | 3.4  | SPI timing                                                  | . 14 |

|   | 3.5  | SPI communication failure                                   | . 15 |

|   | 3.6  | 5 V and 3.3 V output compatibility                          | . 15 |

| 4 | Curr | ent regulation                                              | . 16 |

|   | 4.1  | Temperature-dependent current regulation                    | . 16 |

|   | 4.2  | Current regulation with low-inductive loads                 | . 17 |

|   | 4.3  | Slew rate control in case of current limitation on low-side | . 17 |

| 5 | Diag | nostics and protections                                     | . 19 |

|   | 5.1  | Diagnosis reset strategy                                    | . 19 |

|   |      | 5.1.1 Reset requests                                        | . 19 |

|   |      | 5.1.2 Diagnosis reset bit                                   | . 19 |

|   | 5.2  | Protection and on state diagnostics                         | . 20 |

|   |      | 5.2.1 Over-current on high-side - short to ground           | . 20 |

|   |      | 5.2.2 Over-current on low-side - short to Vs                | . 20 |

|   |      | 5.2.3 Short circuit over-load                               | . 20 |

|   |      | 5.2.4 Open load in on state                                 | . 20 |

|   |      | 5.2.5 Over-temperature                                      | . 21 |

|   |      |                                                             |      |

2/38

|   |      | 5.2.6     | Vs under-voltage shutdown21                      |

|---|------|-----------|--------------------------------------------------|

|   |      | 5.2.7     | Vdd over-voltage detection                       |

|   |      | 5.2.8     | Vdd under-voltage detection                      |

|   |      | 5.2.9     | Output short protection                          |

|   | 5.3  | Off-sta   | te diagnosis                                     |

|   |      | 5.3.1     | Off-state detection scheme                       |

|   |      | 5.3.2     | Open load detection                              |

|   | 5.4  | H-Brido   | ge functional status                             |

| 6 | Elec | trical sp | ecifications                                     |

|   | 6.1  | Absolu    | te maximum ratings 25                            |

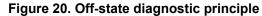

|   | 6.2  | Therma    | al data                                          |

|   | 6.3  | Range     | of functionality                                 |

|   | 6.4  | Electric  | al characteristics                               |

|   |      | 6.4.1     | Device supply                                    |

|   |      | 6.4.2     | Device supply monitoring                         |

|   |      | 6.4.3     | SPI                                              |

|   |      | 6.4.4     | Digital inputs: TTL // 3.3V / 5V CMOS compatible |

|   |      | 6.4.5     | Bridge output drivers                            |

|   |      | 6.4.6     | Over-temperature monitoring                      |

|   |      | 6.4.7     | Current limitation and over-current detection    |

|   |      | 6.4.8     | Diagnostic of open-load in on-state              |

|   |      | 6.4.9     | Off-state diagnostic                             |

|   |      | 6.4.10    | Timing characteristics                           |

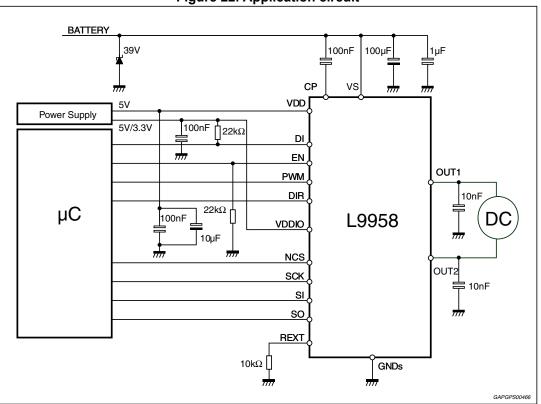

| 7 | Appl | ication   | circuit                                          |

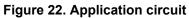

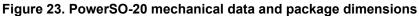

| 8 | Pack | age info  | ormation                                         |

| 9 | Revi | sion his  | tory                                             |

# List of tables

| Table 1.  | Device summary                                   | 1    |

|-----------|--------------------------------------------------|------|

| Table 2.  | PowerSO-20 pin function                          | 7    |

| Table 3.  | PowerSO16 pin function                           | 8    |

| Table 4.  | PowerSSO24 pin function.                         | 9    |

| Table 5.  | Control pins EN, DI                              | . 10 |

| Table 6.  | Control pins DIR, PWM                            | . 11 |

| Table 7.  | Configuration protocol (CFG_REG)                 | . 13 |

| Table 8.  | Diagnosis protocol (DIA_REG)                     | . 13 |

| Table 9.  | Current limitation programmability               | . 16 |

| Table 10. | Slew rate control on low side MOS                | . 18 |

| Table 11. | Diagnosis reset strategy                         | . 19 |

| Table 12. | Over-temperature                                 | . 21 |

| Table 13. | Vs under-voltage                                 | . 22 |

| Table 14. | Vdd over-voltage detection                       | . 22 |

| Table 15. | Absolute maximum ratings                         | . 25 |

| Table 16. | Thermal data                                     |      |

| Table 17. | Range of functionality                           | . 26 |

| Table 18. | Device supply                                    | . 27 |

| Table 19. | Device supply monitoring                         |      |

| Table 20. | SPI                                              |      |

| Table 21. | Digital inputs: TTL // 3.3V / 5V CMOS compatible | . 29 |

| Table 22. | Bridge output drivers                            |      |

| Table 23. | Over-temperature monitoring                      | . 30 |

| Table 24. | Current limitation and over-current detection    |      |

| Table 25. | Diagnostic of open-load in on-state              | . 31 |

| Table 26. | Off-state diagnostic                             | . 31 |

| Table 27. | Timing characteristics                           | . 32 |

| Table 28. | Document revision history.                       | . 37 |

|           |                                                  |      |

# List of figures

| Figure 1.  | Block diagram                                          | . 6 |

|------------|--------------------------------------------------------|-----|

| Figure 2.  | PowerSO-20 pin connection (top view).                  | . 7 |

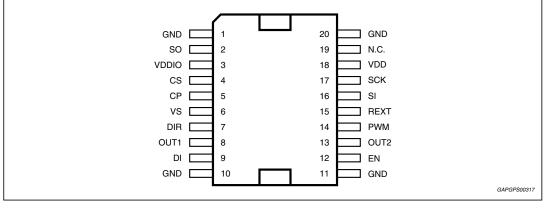

| Figure 3.  | PowerSO16 pin connection (top view)                    | . 8 |

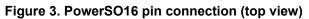

| Figure 4.  | PowerSSO24 pin connection (top view)                   | . 9 |

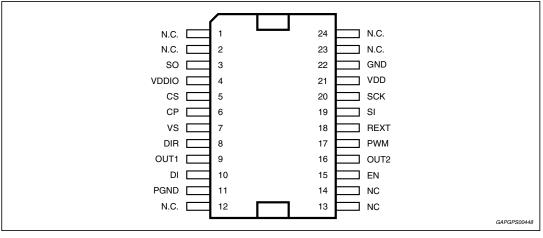

| Figure 5.  | H-Bridge configurations                                | 11  |

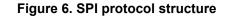

| Figure 6.  | SPI protocol structure                                 | 12  |

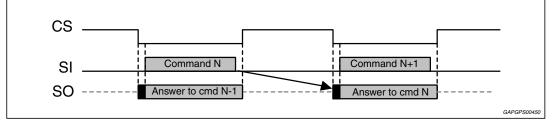

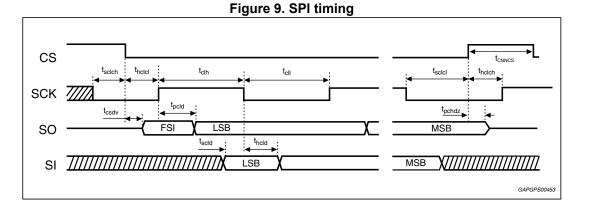

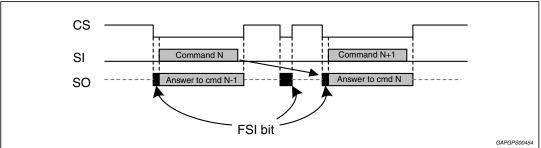

| Figure 7.  | FSI bit                                                | 12  |

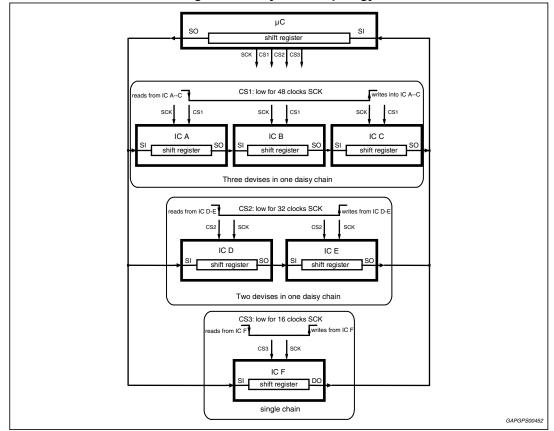

| Figure 8.  | Daisy chain topology.                                  | 14  |

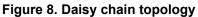

| Figure 9.  | SPI timing                                             | 14  |

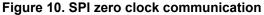

| Figure 10. | SPI zero clock communication                           |     |

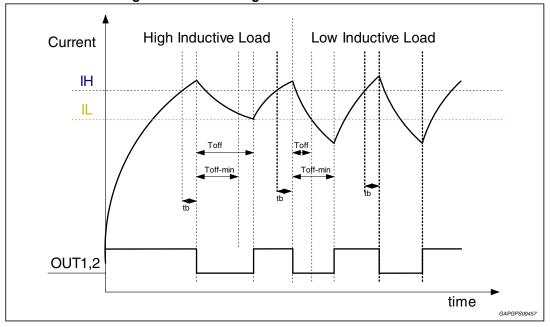

| Figure 11. | Current limitation.                                    |     |

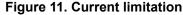

| Figure 12. | Temperature dependent current regulation               | 17  |

| Figure 13. | Current regulation with different loads                | 17  |

| Figure 14. | Slew rate switching strategy                           | 18  |

| Figure 15. | Diagnostics for SCB / SCOL                             |     |

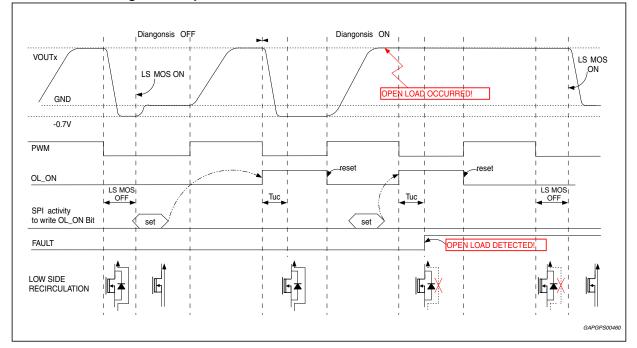

| Figure 16. | Open load in on state - Low-side current recirculation | 21  |

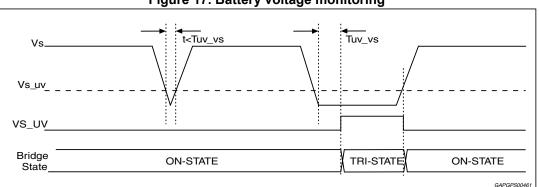

| Figure 17. | Battery voltage monitoring                             | 22  |

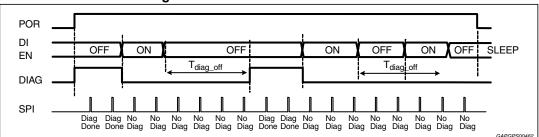

| Figure 18. | Off-state detection scheme                             | 23  |

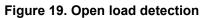

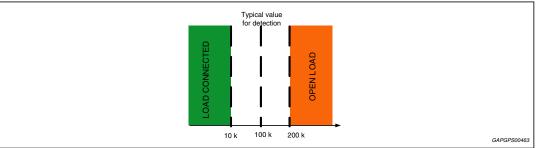

| Figure 19. | Open load detection                                    | 23  |

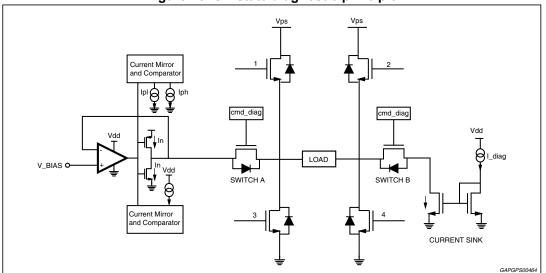

| Figure 20. | Off-state diagnostic principle                         | 24  |

| Figure 21. | Thermal impedance (junction-ambient) of power packages | 26  |

| Figure 22. | Application circuit                                    | 33  |

| Figure 23. | PowerSO-20 mechanical data and package dimensions      | 34  |

| Figure 24. | PowerSO16 mechanical data and package dimensions.      | 35  |

| Figure 25. | PowerSSO24 mechanical data and package dimensions      | 36  |

# 1 Block diagram

Figure 1. Block diagram

# 2 Pins description

## 2.1 PowerSO-20

The exposed slug must be soldered on the PCB and connected to GND.

| Pin N° Name Description |       |                                                   |  |  |  |  |

|-------------------------|-------|---------------------------------------------------|--|--|--|--|

| 1                       | GND   | Ground                                            |  |  |  |  |

| 2                       | SO    | Serial out                                        |  |  |  |  |

| 3                       | VDDIO | Supply voltage for SPI                            |  |  |  |  |

| 4                       | CS    | Chip select                                       |  |  |  |  |

| 5                       | СР    | Charge pump                                       |  |  |  |  |

| 6                       | VS    | Supply voltage                                    |  |  |  |  |

| 7                       | DIR   | Direction input                                   |  |  |  |  |

| 8                       | OUT1  | Output 1                                          |  |  |  |  |

| 9                       | DI    | Disable                                           |  |  |  |  |

| 10                      | GND   | Ground                                            |  |  |  |  |

| 11                      | GND   | Ground                                            |  |  |  |  |

| 12                      | EN    | Enable                                            |  |  |  |  |

| 13                      | OUT2  | Output 2                                          |  |  |  |  |

| 14                      | PWM   | PWM input                                         |  |  |  |  |

| 15                      | REXT  | External reference resistor                       |  |  |  |  |

| 16                      | SI    | Serial in                                         |  |  |  |  |

| 17                      | SCK   | SPI clock                                         |  |  |  |  |

| 18                      | VDD   | Supply voltage                                    |  |  |  |  |

| 19                      | N.C.  | Not connected (To be connected to GND on the PCB) |  |  |  |  |

| 20                      | GND   | Ground                                            |  |  |  |  |

Table 2. PowerSO-20 pin function

| Figure 2. PowerSO-20 pin connection (top vie | w) |

|----------------------------------------------|----|

|----------------------------------------------|----|

## 2.2 PowerSO16

The exposed slug must be soldered on the PCB and connected to GND

| Pin N° Name Description |      |                             |  |  |  |  |  |

|-------------------------|------|-----------------------------|--|--|--|--|--|

| 1                       | GND  | Ground                      |  |  |  |  |  |

| 2                       | SO   | Serial Out                  |  |  |  |  |  |

| 3                       | CS   | Chip Select                 |  |  |  |  |  |

| 4                       | СР   | Charge pump                 |  |  |  |  |  |

| 5                       | DIR  | Direction Input             |  |  |  |  |  |

| 6                       | OUT1 | Output 1                    |  |  |  |  |  |

| 7                       | DI   | Disable                     |  |  |  |  |  |

| 8                       | PGND | Power Ground                |  |  |  |  |  |

| 9                       | EN   | Enable                      |  |  |  |  |  |

| 10                      | OUT2 | Output 2                    |  |  |  |  |  |

| 11                      | PWM  | PWM Input                   |  |  |  |  |  |

| 12                      | REXT | External Reference Resistor |  |  |  |  |  |

| 13                      | VS   | Supply Voltage              |  |  |  |  |  |

| 14                      | SI   | Serial In                   |  |  |  |  |  |

| 15                      | SCK  | SPI Clock                   |  |  |  |  |  |

| 16                      | VDD  | Supply Voltage              |  |  |  |  |  |

Table 3. PowerSO16 pin function

|      |   | - |          |             |

|------|---|---|----------|-------------|

|      |   |   |          |             |

|      |   |   |          |             |

| GND  | 1 |   | 16 🛄 VDD |             |

| SO   | 2 |   | 15 SCK   |             |

| CS [ | 3 |   | 14 🛄 SI  |             |

| CP [ | 4 |   | 13 🔜 VS  |             |

| DIR  | 5 |   | 12 REXT  |             |

| OUT1 | 6 |   | 11 PWM   |             |

| DI   | 7 |   | 10 OUT2  |             |

| PGND | 8 |   | 9 🔜 EN   |             |

|      |   | • |          | GAPGPS00447 |

## 2.3 PowerSSO24

Although this package has two separate pins for the ground (pin 11 = PGND = Power Ground and pin 22 = GND = Logic Ground), the device is designed to work with shortening ground and is mandatory that the two pins have to be connected nearby the IC on the PCB.

The exposed slug must be soldered on the PCB and connected to GND.

| Pin Nº                      | Pin Nº Name Description |                             |  |  |  |  |  |

|-----------------------------|-------------------------|-----------------------------|--|--|--|--|--|

| 1, 2, 12, 13,<br>14, 23, 24 | N.C.                    | Not Connected               |  |  |  |  |  |

| 3                           | SO                      | Serial Out                  |  |  |  |  |  |

| 4                           | VDDIO                   | Supply Voltage for SPI      |  |  |  |  |  |

| 5                           | CS                      | Chip Select                 |  |  |  |  |  |

| 6                           | CP                      | Supply Voltage for SPI      |  |  |  |  |  |

| 7                           | VS                      | Supply Voltage              |  |  |  |  |  |

| 8                           | DIR                     | Direction Input             |  |  |  |  |  |

| 9                           | OUT1                    | Output 1                    |  |  |  |  |  |

| 10                          | DI                      | Disable                     |  |  |  |  |  |

| 11                          | PGND                    | Power Ground                |  |  |  |  |  |

| 15                          | EN                      | Enable                      |  |  |  |  |  |

| 16                          | OUT2                    | Output 2                    |  |  |  |  |  |

| 17                          | PWM                     | PWM Input                   |  |  |  |  |  |

| 18                          | REXT                    | External Reference Resistor |  |  |  |  |  |

| 19                          | SI                      | Serial In                   |  |  |  |  |  |

| 20                          | SCK                     | SPI Clock                   |  |  |  |  |  |

| 21                          | VDD                     | Supply Voltage              |  |  |  |  |  |

| 22                          | GND                     | Ground                      |  |  |  |  |  |

Table 4. PowerSSO24 pin function

## 3 Device description

## 3.1 Supply range

The L9958 has an operating supply range from "Vs\_uv" (battery monitoring) up to 28 V. However, the device is tested until 16 V; the functionality of the device is guaranteed until 28 V. The absolute maximum rating is defined to 40 V DC.

## 3.2 Control inputs

The bridge is controlled by the Inputs PWM, DIR, EN and DI.

All the digital inputs and outputs of the L9958 are compatible with 3.3 V and 5 V CMOS. The power stages output OUT1 and OUT2 are controlled by the direct inputs DIR and PWM as given in *Table 5*. The DIR input gives the direction of output current, while the PWM input controls whether the current is increased or reduced.

### 3.2.1 DI and EN inputs

The pin DI is internally pulled-up and high active. When DI is active (set to HIGH), the bridge is set to tristate, whatever the state of the DIR and PWM inputs. All the data stored in SPI registers are not reset and SPI communication with the MCU is still possible. When DI is inactive (set to LOW), the bridge is controlled by the DIR and PWM inputs.

The pin EN is internally pulled down and high active. When EN is inactive (set to LOW), the bridge is set to tri-state, whatever the state of the DIR and PWM inputs. All the data stored in SPI registers are not reset and SPI communication with the MCU is still possible. When EN is active (set to HIGH), the bridge is controlled by the DIR and PWM inputs. The coding is performed as shown in the next table. The state of the bridge is transferred in the diagnostic register in a bit called "ACT".

| EN | DI | Bit "ACT"   | Bridge status |

|----|----|-------------|---------------|

| 0  | 0  | 0 Tri-state |               |

| 0  | 1  | 0           | Tri-state     |

| 1  | 0  | 1           | On-state      |

| 1  | 1  | 0           | Tri-state     |

Table 5. Control pins EN, DI

### 3.2.2 DIR and PWM inputs

The pins DIR and PWM are internally pulled down. The bridge is controlled by these two inputs according to the table below.

Table 6. Control pins DIR, PWM

| ,   |     |      |      |                  |  |  |

|-----|-----|------|------|------------------|--|--|

| DIR | PWM | OUT1 | OUT2 | Bridge Status    |  |  |

| Н   | Н   | Н    | L    | Forward          |  |  |

| L   | L   | L    | L    | Freewheeling Low |  |  |

| L   | Н   | L    | Н    | Reverse          |  |  |

| Н   | L   | L    | L    | Freewheeling low |  |  |

Figure 5. H-Bridge configurations

The outputs can be disabled (set to tri-state) by the Disable and Enable inputs DI and EN. Input DI has an internal pull-up. Input EN has an internal pull-down. During freewheeling phase, an active freewheeling on the Low-Side MOS is automatically set, switching ON the power transistor in parallel to the internal freewheeling diode.

## 3.3 Serial peripheral interface (SPI)

The SPI is used for bidirectional communication with a control unit, allowing IC configuration, diagnosis and identification. L9958 can also be used in daisy-chain configuration (number of device in the daisy chain is not limited).

The SPI interface of L9958 is a slave SPI interface: the master is the  $\mu$ C which provides CS and SCK to L9958.

Transfer format uses 16 bits word in case of single device configuration and multiple of 16 bits word in case of daisy chain configuration.

The first answer after Power-ON-Reset is the IC identifier.

A command sent by the  $\mu$ C during transfer N is answered during transfer N+1. SO is clocked on SCK rising edge. SI is sampled on falling edge. When CS = '1' and during power-ON reset, SO is in tri-state. Otherwise, the SPI interface is always active.

Settings made by the SPI control word become active at the end of the SPI transmission and remain valid until a different control word is transmitted or a power on reset occurs.

At each SPI transmission, the diagnosis bits as currently valid in the error logic are transmitted. Details on diagnosis are described in *Section 5*.

Between CS falling edge and SCK rising edge, an internal signal called "FSI bit" is set asynchronously on SO output. This can be useful to have internal information on the device without stimulating the SCK clock. The definition of the FSI bit is presented in the diagnostics chapter.

Except the Enable / Disable bit ("ACT" pin), all the bits of diagnosis register are latched and can be released by:

- Diagnosis register read by SPI

- Power-On-Reset condition.

The coding for the Configuration and Diagnosis Registers is reported in the table below.

| Bit     | Name    | Description                       | Config. value<br>after reset |

|---------|---------|-----------------------------------|------------------------------|

| 0 - LSB | RES     | Reserved                          | —                            |

| 1       | DR      | Diagnostic Reset Bit              | 0                            |

| 2       | CL_1    | Bit1 for Regulation Current Level | 0                            |

| 3       | CL_2    | Bit2 for Regulation Current Level | 1                            |

| 4       | RES     | Reserved                          | —                            |

| 5       | RES     | Reserved                          | _                            |

| 6       | RES     | Reserved                          | _                            |

| 7       | RES     | Reserved                          | —                            |

| 8       | VSR     | Voltage Slew Rate Control Value   | 0                            |

| 9       | ISR     | Current Slew Rate Control Value   | 0                            |

| 10      | ISR_DIS | Current Slew Rate Control Disable | 0                            |

| 11      | OL_ON   | Open Load in ON state Enable      | 0                            |

| 12      | RES     | Reserved                          | —                            |

| 13      | RES     | Reserved                          |                              |

| 14      | 0       | "0" to be written                 | _                            |

| 15-MSB  | 0       | "0" to be written                 | —                            |

Table 7. Configuration protocol (CFG\_REG)

## Table 8. Diagnosis protocol (DIA\_REG)

| Bit    | Name     | Description                       | Status after reset | Bit state   | DR impact | H-bridge<br>status |

|--------|----------|-----------------------------------|--------------------|-------------|-----------|--------------------|

| 0-LSB  | OL_OFF   | Open Load in OFF condition        | 0                  | Latched     | -         | -                  |

| 1      | OL_ON    | Open Load in ON condition         | 0                  | Latched     | _         | _                  |

| 2      | VS_UV    | Vs undervoltage                   | 0                  | Not latched | _         | Hi-Z if "1"        |

| 3      | VDD_OV   | Vdd overvoltage                   | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 4      | ILIM     | Current Limitation reached        | 0                  | Latched     | _         | _                  |

| 5      | TWARN    | Temperature warning               | 0                  | Latched     | _         | _                  |

| 6      | TSD      | Over-temperature Shutdown         | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 7      | ACT      | Bridge enable                     | 1                  | Not latched | _         | Hi-Z if "0"        |

| 8      | OC_LS1   | Over-Current on Low Side 1        | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 9      | OC_LS2   | Over-Current on Low Side 2        | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 10     | OC_HS1   | Over-Current on High Side 1       | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 11     | OC_HS2   | Over-Current on High Side 2       | 0                  | Latched     | Х         | Hi-Z if "1"        |

| 12     | Null     | Not Used                          | -                  | -           | -         | -                  |

| 13     | Null     | Not Used                          | _                  | _           | _         | _                  |

| 14     | SGND_OFF | Short to GND in OFF condition     | 0                  | Latched     | _         | _                  |

| 15-MSB | SBAT_OFF | Short to Battery in OFF condition | 0                  | Latched     | -         | _                  |

### 3.3.1 Daisy chain operation

Several L9958 can be connected to one SPI connection in daisy chain operation to save  $\mu$ C interface pins. The number of devices connected in daisy chain is unlimited.

## 3.4 SPI timing

## 3.5 SPI communication failure

In case of "no SCK edge" when CS = '0', the transfer is considered as valid: no error is returned to the  $\mu$ C. The answer of last command is sent during next transfer.

When the number of SCK period is different from 0 or multiple of 16, next SPI answer is all zero.

## 3.6 5 V and 3.3 V output compatibility

In order to ensure a full compatibility with 5V and 3.3V MCU peripherals, the pin VDDIO is dedicated to supply the output buffer of SO. The overall current consumption on Vddio is "Ivddio". A parasitic current from the pin SO could flow through the pin VDDIO in case of over-voltage on SO pin vs. VDDIO pin.

## 4 Current regulation

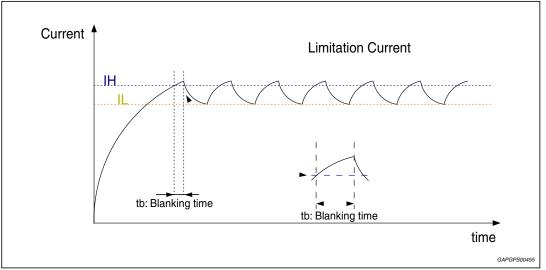

To protect the actuator and limit power dissipation, a two-level chopper current limitation is integrated as shown in figure below. The current is measured by sense cells integrated in the low-side switches. As soon the upper current limit "IH" is reached, both low-side drivers are switched on to allow free-wheeling recirculation, until the lower current limit "IL" is reached. During the current regulation, all the slew rate controls are disabled in order to minimize the power dissipation. Four current limit levels can be set by the SPI control bits 0 and 1. In order to achieve very precise current threshold and ripple, an external resistance is required (1 % accuracy on all temp range/lifetime) to generate a current reference. Detailed values for current thresholds and ripple are reported in *Table 9*.

| CL_2 | CL_1 | Current limit (typical values) |

|------|------|--------------------------------|

| 0    | 0    | 2.5 A                          |

| 0    | 1    | 4 A                            |

| 1    | 0    | 6.6 A (default value)          |

| 1    | 1    | 8.6 A                          |

## 4.1 Temperature-dependent current regulation

In order to reduce power dissipation and thus the junction temperature, above a temperature **Twarn** = 160 °C, current regulation high limit linearly decreases with temperature, to reach about 2.5 A at **Tsd** = 175 °C (shutdown temperature).

When this thermal threshold is reached during a current limitation phase, the information is stored and latched in a coding of bits called "**Twarn**". This bit can be reset only if the settings conditions ( $T_j > T$ warn and  $I_{LIM} = 0$ ) are not present anymore. This feature is mainly used to reduce the power dissipation and thus the junction temperature.

## 4.2 Current regulation with low-inductive loads

Each time output stages are turned off, an internal timing starts for duration **Toff-min**. Whenever turn-on is reached in a time Toff that is shorter than **Toff-min**, output stages are kept OFF, until **Toff-min** is reached.

In such case the ripple control could be not so precise as specified.

Figure 13. Current regulation with different loads

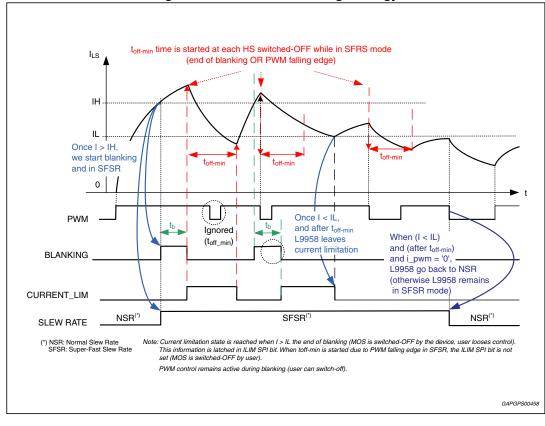

## 4.3 Slew rate control in case of current limitation on low-side

The slew rate control can be done on voltage and current or only on voltage. This can be selected by SPI through the bit ISR\_DIS.

The slew rate of each high-side power transistor of the bridge is controlled either during turn-on and turn-off (current AND voltage slew rate). The same setting is applied for both switching. Moreover, this slew rate is configurable by SPI in order to get the best trade-off between conducted/radiated EMI and power dissipation during switching. The slew rate

selection can be done "on the fly" by SPI. The corresponding bits are called "**VSR**" and "**ISR**". No external component is needed to select the slew rate range. Only the power transistors not used for freewheeling can be adjusted, the two others can be controlled with a preset slew rate.

The couples of value defined to fulfill most of the application requirements are described in the table below. The required accuracy is  $\pm 50$  % for an output current from 1A to 8A and with output voltage up to 19 V. The overall delay implemented between high-side and low-side transistor switching must be adjusted automatically to avoid any cross-conduction through one half-bridge in all conditions.

| Range             | VSR    | ISR      | dV/dt (V/µs) | dl/dt (A/µs) |

|-------------------|--------|----------|--------------|--------------|

| 1 (default value) | 0      | 0        | 4            | 3            |

| 2                 | 0      | 1        | 4            | 0.3          |

| 3                 | 1      | 0        | 2            | 3            |

| 4                 | 1      | 1        | 2            | 0.3          |

| No SR control     | Not se | lectable | 14           | 14           |

Table 10. Slew rate control on low side MOS

In case of current limitation and any detection that put the bridge in tri-state, the slew rate is not related anymore to the preset bits "**VSR**"; "**ISR**" but to a dedicated faster slew rate control named "SUPER FAST" mode. The automatic change from SPI selectable to SUPER FAST slew rate is described hereafter.

Figure 14. Slew rate switching strategy

18/38

# 5 Diagnostics and protections

A detailed diagnostic of the H-bridge is available through SPI communication. The 16 bits diagnostic word is sent back to the MCU in return of a command word. The diagnostic word is used to report two kinds of information:

- H-Bridge failures:

- Over-current on each transistor in on-state,

- Vps under-voltage,

- Vdd over-voltage,

- Over-temperature,

- Open-load in on-state,

- Off-state diagnostic.

- H-bridge functional status:

- Current limitation condition,

- Current limitation decreasing condition,

- Disable / Enable status.

## 5.1 Diagnosis reset strategy

### 5.1.1 Reset requests

Except "ACT" and "VS\_UV" bits, all the others are latched and can only be released by:

- Transition from "Disable" to "Enable" on DI / EN pins,

- Diagnostic register read by SPI (see details on each failure release) depending on bit "DR",

- Power-On-Reset condition.

When the diagnostic register is reset, the bridge is switched back to normal mode driven by DIR and PWM. All the settings are kept as before the failure. In case of SPI read, no additional action on DI / EN is needed.

### 5.1.2 Diagnosis reset bit

In case of "DR" set to LOW (default value), all the bits of the diagnostic register can be reset by the three possibilities described in previous section.

In case of "DR" set to HIGH, the over-current, Vdd over-voltage and over-temperature diagnostic bits can NOT be reset by SPI read and therefore, the bridge is kept in tri-state until a transition from "Disable" to "Enable" on DI/EN pins or Power-on-Reset condition.

| DR | Diagnosis reset strategy                                                                         |  |

|----|--------------------------------------------------------------------------------------------------|--|

| 0  | All diagnostic bits reset at each SPI reading (Default)                                          |  |

| 1  | Over current bits (811) + Temp. shutdown TSD bit (6) + Vdd over voltage bit (3) NOT reset by SPI |  |

## 5.2 **Protection and on state diagnostics**

L9958 is protected against short circuits, overload and invalid supply voltage by the following measures.

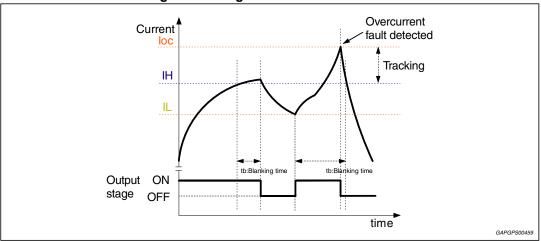

### 5.2.1 Over-current on high-side - short to ground

The high-side switches are protected against a short of the output to ground by an overcurrent shutdown. If a high-side switch is turned on and the current rises above the short circuit detection current **loc** all output transistors are turned off after a filter time **Toc\_Is** and the error bits "overcurrent on high side 1 (2)", **OC\_HS1** (**OC\_HS2**) are stored in the internal status register.

### 5.2.2 Over-current on low-side - short to Vs

Due to the chopper current regulation, the low-side switches are already protected against a short to the supply voltage. To be able to distinguish a short circuit from normal current limit operation, the current limitation is deactivated for the blanking time  $t_b$  after the current has exceeded the current limit threshold IH. If the short circuit detection current  $I_{oc}$  is reached within this blanking time, a short circuit is detected. All output transistors are turned OFF and the according error bit "Over-Current on Low Side 1 (2)", OC\_LS1 (OC\_LS2) is set.

### 5.2.3 Short circuit over-load

If, during the Blanking time  $(t_b)$  of the current regulation mode, the current reaches the  $l_{oc}$  threshold; after a filtering time, the output MOS are switched OFF and the "Short circuit over load" can be checked by the reading of the overcurrent bits of the DIA\_REG (please refer to *Table 8* bit 8, 9,10 and 11).

### 5.2.4 Open load in on state

To perform the Open Load diagnosis in ON state, the flag OL\_ON has to be set high through SPI. After every open load diagnosis in ON state, the OL\_ON flag is resetted, to perform a new open load diagnosis in ON state the OL\_ON flag has to be set again.

This disable the turning on of the low-side drivers during current recirculation. The current flows through the body diode of the low-side MOS for a fixed time. At the end of this fixed time the Vout voltage is sampled and the possible open load condition detected (see *Figure 16*).

Figure 16. Open load in on state - Low-side current recirculation

### 5.2.5 Over-temperature

When **Twarn** is reached, thermal current reduction is activated, and the information is stored and latched. When **Tsd** is reached, the "**TSD**" bit is set and all output transistors are put in tri-state conditions as long as a reset is applied.

| Table | 12. | <b>Over-temperature</b> |

|-------|-----|-------------------------|

|-------|-----|-------------------------|

| TSD         | Comments | Bridge state | FSI |

|-------------|----------|--------------|-----|

| 1           | Tj > TSD | Tri-state-   | 1   |

| 0 (default) | Tj < TSD | -            | 0   |

### 5.2.6 Vs under-voltage shutdown

If the supply-voltage at the V<sub>S</sub> pins falls below the under-voltage detection threshold **Vs\_uv\_off**, the outputs are set to tri-state and the error bit "Undervoltage at V<sub>S</sub>" is set. A filtering time "**Tuv\_Vs**" is implemented to avoid unwanted detection due to parasitic glitches. The information is transferred into the SPI register in a bit called "**VS\_UV**". This bit is NOT latched. As soon as the voltage rises again above the Vs under-voltage threshold (hysteresis implemented), the bridge is switched back to normal mode driven by DIR and PWM. All the settings are kept as before the under-voltage event.

Figure 17. Battery voltage monitoring

### Table 13. Vs under-voltage

| vs_uv       | Comments       | Bridge state | FSI             |

|-------------|----------------|--------------|-----------------|

| 1           | Vs < Vs_uv_off | Hi Z         | 1 (not latched) |

| 0 (default) | Vs > Vs_uv_on  | -            | 0               |

#### 5.2.7 Vdd over-voltage detection

Although the Vdd input pin and all I/O's are able to withstand up to 19 V, an over-voltage circuitry is implemented to ensure that the bridge is kept in tri-state when the Vdd voltage is higher than the Vdd overvoltage threshold "Vdd\_ov\_off" for duration longer than "Tov Vdd". The information is detected and stored into the SPI register in a bit called "VDD OV". The bridge is kept in tri-state as long as an appropriate reset is not requested (see Section 5.1).

| Table 14. Vdd over-volt | age detection |  |

|-------------------------|---------------|--|

|                         |               |  |

| VDD_OV Comments |                  | Bridge state | FSI         |

|-----------------|------------------|--------------|-------------|

| 1               | Vdd > Vdd_ov_off | Hi-Z         | 1 (latched) |

| 0 (default)     | Vdd < Vdd_ov_on  | -            | 0           |

#### 5.2.8 Vdd under-voltage detection

When the Vdd voltage falls below the under-voltage detection threshold "Vdd\_uv\_off" for duration longer than "Tuv\_vdd", the bridge is switched to tri-state. In such a condition, the L9958 is going in sleep mode. When the voltage increases above the threshold (hysteresis implemented), the L9958 starts with all the settings reset to their default values (Power On Reset).

#### 5.2.9 **Output short protection**

The L9958 can sustain short on the outputs. In case of short to GND, short to battery or short between outputs the battery voltage cannot exceed 18 V. The connection of a 100 µF plus a 1µF decoupling capacitors as close as possible to V<sub>s</sub> pin and the GND connection of the slug or of the exposed pad is mandatory to improve the robustness.

57/

## 5.3 Off-state diagnosis

This diagnostic is performed in any off-state condition, just after ignition key-on or during an off-state phase occurring after an on-state phase of the bridge.

### 5.3.1 Off-state detection scheme

In order to avoid any wrong diagnostic, a filtering time "**Tdiag\_off**" is applied before performing the detection if the bridge was in on-state before. This filtering time is not applied in case of detection after key on.

Figure 18. Off-state detection scheme

### 5.3.2 Open load detection

An equivalent resistor of 100 k $\Omega$  (typ.) is targeted for open-load detection.

In order to avoid any unwanted supply of the bridge through the high-side transistor body diode during off-state measurement, the current source is connected only if Vs is higher than the Vs under-voltage threshold.

The diagnostic is based on a closed loop voltage control on OUT1 and associated current measurement.

A voltage amplifier forces a constant voltage on OUT1 through two current sources (highside source and low-side current sink). The OUT2 is pulled-down through a constant current sink. Based on the current flowing out of the amplifier (Ip - In) compared to several current thresholds, open-load as well as short-circuit to ground and battery can be detected.

## 5.4 H-Bridge functional status

Three bits in the diagnosis register are used to give a feedback about the state of the H-Bridge. Status are Current Limitation (bit 4 "C\_LIM"), Temperature Warning (bit 5 "T\_WRN") and Bridge Enable Status (bit 7 "ACT"). Those bits do not report a failure but only a functional state of the H-bridge that could be useful to change the control strategy mainly in term of power dissipation.

# 6 Electrical specifications

## 6.1 Absolute maximum ratings

The component must withstand the overall following stimulus without any damage or latchup. Beyond these values, damage to the component may occur.

| Symbol                    | Parameter            | Test condition                                               | Min.     | Max.      | Unit |

|---------------------------|----------------------|--------------------------------------------------------------|----------|-----------|------|

| V <sub>ps</sub>           | Supply voltage       | Continuous<br>Transient (0.5 s; $I \le 10 A$ )               | -1<br>-2 | 40<br>40  | V    |

| V <sub>dd</sub>           | Logic supply voltage | 0 V < V <sub>ps</sub> < 40 V                                 | -0.3     | 19        | V    |

| V <sub>ddio</sub>         | SDO supply voltage   | 0 V < V <sub>ps</sub> < 40 V                                 | -0.3     | 19        | V    |

| Vi                        | Logic input voltage  | 0 V < V <sub>ps</sub> < 40 V<br>0 V < V <sub>dd</sub> < 19 V | -0.3     | 19        | V    |

| Vo                        | Logic output voltage | $0 V < V_{ps} < 40 V$<br>$0 V < V_{dd} < 18.7V$              | -0.3     | Vddio+0.3 | V    |

| Output pins<br>OUTx, VPS) | ESD Compliance       | EIA/JESD22-A114-B                                            | ±4       | -         | kV   |

| Input pins                |                      |                                                              | ±2       | -         |      |

| -                         | ISO 7637 pulses      | Cf. standards                                                | -        | -         | -    |

| -                         | Latch-up immunity    | Jedec standard                                               | -100     | +100      | mA   |

| Table | 15. | Absolute | maximum | ratings |

|-------|-----|----------|---------|---------|

|-------|-----|----------|---------|---------|

Note: In case of load dump condition, status of device outputs is kept unchanged.

## 6.2 Thermal data

### Table 16. Thermal data

| Symbol                | Parameter                                          | Test condition               | Min. | Max. | Unit |

|-----------------------|----------------------------------------------------|------------------------------|------|------|------|

| т                     | Junction temperature                               | Failure condition            | -40  | OTsd | °C   |

| Тj                    |                                                    | Lifetime                     | -40  | 150  | C    |

| T <sub>stg</sub>      | Storage temperature                                | -                            | -55  | 150  | °C   |

| T <sub>amb</sub>      | Ambient temperature                                | 0 V < V <sub>ps</sub> < 40 V | -40  | 125  | °C   |

|                       | Thermal resistance junction to case <sup>(1)</sup> | Package PowerSO-20           | -    | 1    |      |

| R <sub>thj-case</sub> |                                                    | Package PowerSO16            | -    | 1    | °C/W |

|                       |                                                    | Package PowerSSO24           | -    | 2    |      |

1. Guaranteed by design and package characterization.

Figure 21. Thermal impedance (junction-ambient) of power packages

## 6.3 Range of functionality

Within the range of functionality, all L9958 functionalities have to be guaranteed. All voltages refers to GND. Currents are positive into and negative out of the specified pin.

| Pos. | Symbol                           | Parameter                                                    | Test condition                                    | Min.       | Тур. | Max.                 | Unit |

|------|----------------------------------|--------------------------------------------------------------|---------------------------------------------------|------------|------|----------------------|------|

| FR1  | V <sub>ps</sub>                  | Supply voltage                                               | -                                                 | Vps_uv_off | 14   | 28 <sup>(1)</sup>    | V    |

| FR2  | dV <sub>ps</sub> /d <sub>t</sub> | Supply voltage slew rate                                     | -                                                 | -20        | -    | 20                   | V/µs |

| FR3  | V <sub>dd</sub>                  | Logic supply voltage                                         | -                                                 | Vdd_uv_off | 5    | Vdd_ov_off           | V    |

| FR4  | dV <sub>dd</sub> /d <sub>t</sub> | Logic supply voltage slew rate                               | -                                                 | -          | -    | 0.025 <sup>(2)</sup> | V/µs |

| FR5  | Vi                               | Logic input voltage (SDI,<br>SCLK, NCS, DI, EN, DIR,<br>PWM) | See alsoTable 15:<br>Absolute maximum<br>ratings. | -0.3       | -    | Vdd_ov_off           | V    |

| FR6  | V <sub>ddio</sub>                | SDO output voltage                                           | -                                                 | 3          | -    | 5.5                  | V    |

| FR7  | f <sub>spi</sub>                 | SPI clock frequency                                          | -                                                 | -          | -    | 5                    | MHz  |

Table 17. Range of functionality

1. In load dump conditions V<sub>ps</sub> ranges between 28V and 40V. During load dump, status of device outputs is kept unchanged,

2. To VDD pin are connected  $10\mu F$  and 10nF (close to the pin) capacitors.

## 6.4 Electrical characteristics

$T_{case}$  = -40 °C to 125 °C unless otherwise specified,

$V_{dd}$  = 4.5 V to 5.5 V unless otherwise specified

$V_{ps}$  = 4 V to 28 V unless otherwise specified

All voltages refer to GND. Currents are positive into and negative out of the specified pin.

## 6.4.1 Device supply

| Pos. | Symbol           | Parameter                 | Test condition                                                          | Min. | Тур. | Max. | Unit |

|------|------------------|---------------------------|-------------------------------------------------------------------------|------|------|------|------|

|      |                  |                           | V <sub>dd</sub> < 0.7 V; V <sub>ps</sub> = 16 V<br>from -40 °C to 25 °C | -    | -    | 20   | μA   |

| 1.1  | I <sub>ps</sub>  | Power supply current      | V <sub>dd</sub> < 0.7 V; V <sub>ps</sub> = 16 V<br>at 125 °C            | -    | -    | 35   | μA   |

|      |                  |                           | $F_{pwm} = 0, I_{out} = 0$                                              | -    | -    | 20   | mA   |

| 1.2  | I <sub>out</sub> | Leakage current on output | Bridge in tri-state                                                     | -    | -    | 100  | μA   |

| 1.3  | 1                | Logic-supply current      | V <sub>dd</sub> >V <sub>dd_uv_on</sub><br>F <sub>PWM</sub> = 0          | -    | -    | 5    | mA   |

| 1.5  | I <sub>CC</sub>  |                           | F <sub>PWM</sub> = 20 kHz<br>(Average value)                            | -    | -    | 5    | mA   |

| Table 18. Device supply | Table | 18. | Device | supply |

|-------------------------|-------|-----|--------|--------|

|-------------------------|-------|-----|--------|--------|

## 6.4.2 Device supply monitoring

### Table 19. Device supply monitoring

| Pos. | Symbol                  | Parameter                                    | Test condition             | Min. | Тур. | Max. | Unit |

|------|-------------------------|----------------------------------------------|----------------------------|------|------|------|------|

| 2.1  | V <sub>ps_uv_off</sub>  | V <sub>ps</sub> under-voltage threshold      | V <sub>ps</sub> decreasing | -    | -    | 4    | V    |

| 2.2  | V <sub>ps_uv_on</sub>   | V <sub>ps</sub> under-voltage threshold      | V <sub>ps</sub> increasing | -    | -    | 4.5  | V    |

| 2.3  | V <sub>ps_uv_hyst</sub> | V <sub>ps</sub> under-voltage hysteresis     | -                          | 0.1  | -    | -    | V    |

| 2.4  | T <sub>uv_vps</sub>     | V <sub>ps</sub> under-voltage filtering time | V <sub>ps</sub> decreasing | 1    | -    | 3    | μs   |

| 2.5  | V <sub>dd_uv_off</sub>  | V <sub>dd</sub> under-voltage threshold      | V <sub>dd</sub> decreasing | 3    | -    | 3.7  | V    |

| 2.6  | V <sub>dd_uv_on</sub>   | V <sub>dd</sub> under-voltage threshold      | V <sub>dd</sub> increasing | 3.3  | -    | 4    | V    |

| 2.7  | V <sub>dd_uv_hyst</sub> | V <sub>dd</sub> under-voltage hysteresis     | -                          | 0.1  | -    | -    | V    |

| 2.8  | T <sub>uv_Vdd</sub>     | V <sub>dd</sub> under-voltage filtering time | V <sub>dd</sub> decreasing | 1    | -    | 4    | μs   |

| 2.9  | V <sub>dd_ov_off</sub>  | V <sub>dd</sub> over-voltage threshold       | V <sub>dd</sub> increasing | 5.8  | -    | 6.8  | V    |

| 2.10 | V <sub>dd-ov_on</sub>   | V <sub>dd</sub> over-voltage threshold       | V <sub>dd</sub> decreasing | 5.5  | -    | 6.5  | V    |

| 2.11 | V <sub>dd_ov_hyst</sub> | V <sub>dd</sub> over-voltage hysteresis      | -                          | 0.1  | -    | -    | V    |

| 2.12 | T <sub>ov_Vdd</sub>     | V <sub>dd</sub> over-voltage filtering time  | V <sub>dd</sub> increasing | 60   | 100  | 140  | μs   |

### 6.4.3 SPI

Table 20. SPI

| Pos. | Symbol                 | Parameter                                                                   | Test condition                                     | Min.                       | Тур. | Max. | Unit |

|------|------------------------|-----------------------------------------------------------------------------|----------------------------------------------------|----------------------------|------|------|------|

| 3.1  | f <sub>spi</sub>       | Clock frequency (50 % duty cycle)                                           | -                                                  | -                          | -    | 5    | MHz  |

| 3.2  | т                      | SDO transition speed, 20-80 %                                               | $V_{sdo}$ = 5V, $C_{load}$ = 50 pF <sup>(1)</sup>  | 5                          | -    | 30   | ns   |

| 5.2  | T <sub>sdo_trans</sub> | SDO transition speed, 20-60 %                                               | V <sub>sdo</sub> = 5 V, C <sub>load</sub> = 150 pF | 5                          | -    | 50   | ns   |

| 3.3  | T <sub>clh</sub>       | Minimum time SCLK = HIGH                                                    | -                                                  | 75                         | -    |      | ns   |

| 3.4  | T <sub>cll</sub>       | Minimum time SCLK = LOW                                                     | -                                                  | 75                         | -    |      | ns   |

| 3.5  | T <sub>pcld</sub>      | Propagation delay (SCLK to data at 10% of SDO rising edge)                  | -                                                  | -                          | -    | 40   | ns   |

| 3.6  | T <sub>csdv</sub>      | NCS = LOW to data at SDO<br>active                                          | -                                                  | -                          | -    | 85   | ns   |

| 3.7  | T <sub>sclch</sub>     | SCLK low before NCS low<br>(setup time SCLK to NCS<br>change H/L)           | -                                                  | 75                         | -    | -    | ns   |

| 3.8  | T <sub>hclcl</sub>     | SCLK change L/H after NCS =<br>low                                          | -                                                  | 75                         | -    | -    | ns   |

| 3.9  | T <sub>scld</sub>      | SDI input setup time (SCLK change H/L after SDI data valid)                 | -                                                  | 40                         | -    | -    | ns   |

| 3.10 | T <sub>hcld</sub>      | SDI input hold time (SDI data hold after SCLK change H/L)                   | -                                                  | 40                         | -    | -    | ns   |

| 3.11 | T <sub>sclcl</sub>     | SCLK low before NCS high                                                    | -                                                  | 100                        | -    | -    | ns   |

| 3.12 | T <sub>hclch</sub>     | SCLK high after NCS high                                                    | -                                                  | 100                        | -    | -    | ns   |

| 3.13 | T <sub>pchdz</sub>     | NCS L/H to SDO @ high impedance                                             | -                                                  | -                          | -    | 75   | ns   |

| 3.14 | Tonncs                 | NCS min. high time                                                          | -                                                  | 300                        | -    |      | ns   |

| 3.15 | -                      | Capacitance at SDI, SCLK; NCS                                               | -                                                  | -                          | -    | 14   | pF   |

| 5.15 | -                      | Capacitance at SDO                                                          | -                                                  | -                          | -    | 19   | pF   |

| 3.16 | T <sub>fncs</sub>      | NCS Filter time will be ignored)<br>Guaranteed by design<br>(Pulses = TfNCS | Guaranteed by design                               | 10                         | -    | 40   | ns   |

| 3.17 | V <sub>ddio</sub>      | Supply voltage for SDO output buffer                                        | -                                                  | 3                          | -    | 5.5  | V    |

| 3.18 | I <sub>vddio</sub>     | Current consumption on Vddio                                                | (2)                                                | -                          | -    | 1    | mA   |

| 3.19 | sdo_H                  | High output level on SDO                                                    | I <sub>sdo</sub> = 1.5 mA                          | V <sub>ddio</sub> -<br>0.4 | -    | -    | v    |

| 3.20 | sdo_L                  | Low output level on SDO                                                     | I <sub>sdo</sub> = 2 mA                            | -                          | -    | 0.4  | V    |

| 3.21 | I <sub>sdo</sub>       | Tri state leakage current                                                   | NCS = HIGH V <sub>DDIO</sub> = 5 V                 | -5                         | -    | 5    | μA   |

1. Not tested – guaranteed by  $C_{load}$  = 150 pF measurement

2. Measured for PSO16 at wafer sort level only.

## 6.4.4 Digital inputs: TTL // 3.3V / 5V CMOS compatible

| Pos.                 | Symbol                                             | Parameter                                       | Test condition                          | Min. | Тур. | Max.    | Unit |

|----------------------|----------------------------------------------------|-------------------------------------------------|-----------------------------------------|------|------|---------|------|

| 4.1                  | V <sub>ih</sub>                                    | Input voltage HIGH                              | -                                       | 2    | -    | Vdd+0.3 | V    |

| 4.2                  | V <sub>il</sub>                                    | Input voltage LOW                               | -                                       | -0.3 | -    | 0.8     | V    |

| 4.3                  |                                                    | Hysteresis of input voltage                     | -                                       | 200  | -    | -       | mV   |

| 4.4 I <sub>inl</sub> | Input current source for: DI /<br>NCS / SCLK / SDI | V <sub>in</sub> = 0 V                           | -100                                    | -    | -30  |         |      |

|                      |                                                    | V <sub>in</sub> = 5 V No back<br>supply allowed | -                                       | -    | 5    | μA      |      |

| 4.5                  | I                                                  | Input current sink for: EN / DIR /              | V <sub>in</sub> = 5 V                   | 30   | -    | 100     | μA   |

| 4.5                  | l <sub>inh</sub>                                   | PWM                                             | V <sub>in</sub> = 0 V                   | -5   | -    | -       | μΑ   |

|                      | V <sub>rext</sub>                                  |                                                 | -                                       | -    | 1.24 | -       | V    |

| 4.6                  | External resistor                                  | -                                               | -                                       | 10   | -    | kΩ      |      |

|                      | R <sub>ext</sub>                                   |                                                 | Overall tolerance can be taken as 3.5 % | -    | 1    | -       | %    |

### Table 21. Digital inputs: TTL // 3.3V / 5V CMOS compatible

## 6.4.5 Bridge output drivers

### Table 22. Bridge output drivers

| Pos.                    | Symbol                 | Parameter                                                                      | Test condition                                                                 | Min. | Тур. | Max. | Unit  |

|-------------------------|------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|-------|

| 5.1 R <sub>dson_h</sub> | High-side transistor R | T <sub>j</sub> = 150 °C, I <sub>out</sub> = 3 A<br>4 V < V <sub>ps</sub> < 5 V | -                                                                              | -    | 300  | mΩ   |       |

|                         | ™dson_h                |                                                                                | T <sub>j</sub> = 150 °C, I <sub>out</sub> = 3 A<br>V <sub>ps</sub> > 5 V       | -    | -    | 150  | 11152 |

| 5.2 R <sub>dson_l</sub> | Ρ                      | Low-side transistor R <sub>dson</sub>                                          | T <sub>j</sub> = 150 °C, I <sub>out</sub> = 3 A<br>4 V < V <sub>ps</sub> < 5 V | -    | -    | 300  | mΩ    |

|                         | '\dson_l               |                                                                                | T <sub>j</sub> = 150 °C, I <sub>out</sub> = 3 A<br>V <sub>ps</sub> > 5 V       | -    | -    | 150  | 11152 |

| 5.3                     | V <sub>bd_h</sub>      | Body diode forward voltage drop high-side transistor                           | I <sub>diode</sub> = 3 A                                                       | -    | 1.2  | 2    | V     |

| 5.4                     | V <sub>bd_I</sub>      | Body diode forward voltage drop low-side transistor                            | I <sub>diode</sub> = 3 A                                                       | -    | 1.2  | 2    | V     |

## 6.4.6 Over-temperature monitoring

| Pos. | Symbol           | Parameter                       | Test condition                  | Min. | Тур. | Max. | Unit |

|------|------------------|---------------------------------|---------------------------------|------|------|------|------|

| 6.1  | OTwarn           | Over-temperature warning        | -                               | 150  | -    | 170  | °C   |

| 6.2  | OTsd             | Over-temperature shut-down      | -                               | 170  | -    | 200  | °C   |

| 6.3  | OThyst           | Over-temperature hysteresis     | -                               | 10   | -    | -    | °C   |

| 6.4  | T <sub>TSD</sub> | Over-temperature filtering time | Guaranteed by clock measurement | -    | 36   | -    | μs   |

## 6.4.7 Current limitation and over-current detection

| Pos. | Symbol              | Parameter                                              | Test condition                               | Min.                       | Тур.                         | Max.                                                                                                                                                                                                                                    | Unit |

|------|---------------------|--------------------------------------------------------|----------------------------------------------|----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      |                     |                                                        | CL1:0 = 00; -40 °C ≤ T <sub>j</sub> ≤ 150 °C | 2                          | 2.5                          | 3.1                                                                                                                                                                                                                                     | A    |

| 7.1  |                     |                                                        | CL1:0 = 01; -40 °C ≤ T <sub>j</sub> ≤ 150 °C | 3.5                        | 4                            | 4.85                                                                                                                                                                                                                                    |      |

|      |                     |                                                        | CL1:0 = 10; -40 °C ≤ T <sub>j</sub> < 25 °C  | 5.5                        | 6.75                         | 8                                                                                                                                                                                                                                       |      |

|      | I <sub>lim_H</sub>  | Current limitation high threshold                      | CL1:0 = 10; 25 °C ≤ T <sub>j</sub> ≤ 150 °C  | 5.5                        | 6.6                          | 7.7                                                                                                                                                                                                                                     |      |

|      |                     |                                                        | CL1:0 = 11; -40 °C ≤ T <sub>j</sub> < 25 °C  | 7.8                        | 9.1                          | 10.4                                                                                                                                                                                                                                    |      |

|      |                     |                                                        | CL1:0 = 11; 25 °C ≤ T <sub>j</sub> ≤ 150°C   | 7.6                        | 8.6                          | 9.6                                                                                                                                                                                                                                     |      |

|      |                     |                                                        | CL1:0 = XX, T <sub>j</sub> = OTsd            | 2                          | 2.5                          | 3                                                                                                                                                                                                                                       |      |

|      |                     |                                                        | CL1:0 = 0X; -40 °C ≤ T <sub>j</sub> ≤ 150 °C | I <sub>lim_H</sub> –0.2    | I <sub>lim_H</sub> −<br>0.5  | I <sub>lim_H</sub> -<br>0.8                                                                                                                                                                                                             |      |

|      | I <sub>lim_L</sub>  | Current limitation low<br>I <sub>lim_L</sub> threshold | CL1:0 = 10; -40°C ≤ T <sub>j</sub> < 25 °C   | I <sub>lim_Н</sub><br>0.35 | l <sub>lim_H</sub> -<br>0.65 | l <sub>lim_H</sub> -<br>0.95                                                                                                                                                                                                            | А    |

| 7.2  |                     |                                                        | CL1:0 = 10; 25 °C ≤ T <sub>j</sub> ≤ 150°C   | I <sub>lim_H</sub><br>0.35 | l <sub>lim_H</sub> -<br>0.55 | I <sub>lim_H</sub> -<br>0.85                                                                                                                                                                                                            |      |

|      |                     |                                                        | CL1:0 = 11; -40°C ≤ T <sub>j</sub> < 25°C    | I <sub>lim_H</sub> –0.4    | I <sub>lim_H</sub> -<br>0.7  | I <sub>lim_H</sub> -1                                                                                                                                                                                                                   |      |

|      |                     |                                                        | CL1:0 = 11; 25 °C ≤ T <sub>j</sub> ≤ 150°C   | I <sub>lim_H</sub> –0.4    | l <sub>lim_H</sub> -<br>0.55 | 10.4         9.6         3         I <sub>lim_H</sub> <sup>-</sup> 0.8         I <sub>lim_H</sub> <sup>-</sup> 0.95         I <sub>lim_H</sub> <sup>-1</sup> 0.85         I <sub>lim_H</sub> -1         I <sub>lim_H</sub> -1         3 |      |

| 7.3  | T <sub>limh</sub>   | High current limitation threshold filtering time       | can be included in T <sub>blanck</sub>       | 0.1                        | -                            | 1                                                                                                                                                                                                                                       | μs   |

| 7.4  | T <sub>liml</sub>   | Low current limitation threshold filtering time        | -                                            | 1                          | -                            | 3                                                                                                                                                                                                                                       | μs   |

| 7.5  | T <sub>offmin</sub> | Current limitation delay time                          | -                                            | 30                         | -                            | 45                                                                                                                                                                                                                                      | μs   |

| 7.6  | Т <sub>b</sub>      | Blanking time                                          | -                                            | 4.9                        | -                            | 8.7                                                                                                                                                                                                                                     | μs   |

### Table 24. Current limitation and over-current detection

L9958

| Pos. | Symbol           | Parameter                                                            | Test condition                                              | Min.                    | Тур. | Max. | Unit |

|------|------------------|----------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|------|------|------|

|      | loc_ls<br>loc-hs | loc_ls<br>loc-hs<br>threshold<br>High-side over-current<br>threshold | CL1:0 = 0X; -40 °C ≤ T <sub>j</sub> ≤ 150 °C                | 5.5                     | 7.7  | 11   |      |

|      |                  |                                                                      | CL1:0 = 1X; -40°C ≤ T <sub>j</sub> < 25 °C                  | 9.3                     | 12   | 16.5 |      |

| 7.7  |                  |                                                                      | CL1:0 = 1X; 25 °C ≤ T <sub>j</sub> ≤ 150°C                  | 9.3                     | 11.5 | 14   | A    |

|      | Tracking         |                                                                      | CL1:0 = 0X; CL1:0 = 10;<br>-40 °C ≤ T <sub>j</sub> ≤ 150 °C | I <sub>lim_h</sub> +2   | -    | -    |      |

|      |                  |                                                                      | CL1:0 = 11; -40 °C ≤ T <sub>j</sub> ≤ 150 °C                | I <sub>lim_h</sub> +1.3 | -    | -    |      |

| 7.8  | Toc_ls<br>Toc_hs | Low-side & high-side<br>over-current detection<br>filtering time     | -                                                           | 0.8                     | -    | 2.5  | μs   |

Table 24. Current limitation and over-current detection (continued)

## 6.4.8 Diagnostic of open-load in on-state

| Pos. | Symbol   | Parameter                      | Test condition                                                    | Min. | Тур. | Max. | Unit |

|------|----------|--------------------------------|-------------------------------------------------------------------|------|------|------|------|

|      |          |                                | T <sub>j</sub> = -40 °C (go-no-go<br>functional test)             | 50   | -    | 120  |      |

| 8.1  | ls_OL-on | Current source                 | T <sub>j</sub> = 25 °C to 150 °C<br>(go-no-go functional<br>test) | 50   | -    | 100  | μA   |

| 8.2  | Tmeas_on | Detection time (settling time) | -                                                                 | -    | 3    | 5    | μs   |

### Table 25. Diagnostic of open-load in on-state

## 6.4.9 Off-state diagnostic

| Pos. | Symbol                  | Parameter                                                                             | Test condition                                                                                                               | Min. | Тур. | Max. | Unit |

|------|-------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 9.1  | R <sub>OL</sub>         | Load detection threshold                                                              |                                                                                                                              | 10   | 60   | 200  | kΩ   |

| 9.2  | Tdiag_off               | Delay time before enabling off-<br>state diagnostic structure diagnostic structure    |                                                                                                                              | 100  | 125  | 150  | ms   |

| 9.3  | T <sub>diag-off_1</sub> | Off-state diag filtering time<br>when OUT 1 and/or 2 decrease<br>from V <sub>ps</sub> | used each time OUT<br>pins are released from<br>Vps (after release of<br>SCB, after Tdiag_off)<br>Guaranteed through<br>SCAN | 2.4  | 3    | 3.6  | ms   |

| 9.4  | T <sub>diag_off_2</sub> | Off-state diagnostic filtering time on failure detection                              | One symmetric filter for<br>each failure type (OL,<br>SCG, SCB) Guaranteed<br>through SCAN                                   | 200  | 250  | 300  | μs   |

| 9.5  | T <sub>clock</sub>      | Oscillator frequency                                                                  | -                                                                                                                            | 4    | -    | 6    | MHz  |

Table 26. Off-state diagnostic

## 6.4.10 Timing characteristics

| Pos.  | Symbol                            | Parameter Test condition                                                           |                                                                                                                                                                                       | Min. | Тур. | Max. | Unit     |

|-------|-----------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| 10.1  | f <sub>pwm</sub>                  | PWM frequency -                                                                    |                                                                                                                                                                                       | -    | -    | 20   | kHz      |

|       | T <sub>don</sub>                  | Delay time for switch-on                                                           | $ \begin{array}{l} R_{load} @ \ I_{out} = 3 \ A \\ PWM \rightarrow 90\% \ V_{out} \ (or \\ 10 \ \% \ I_{out}) \end{array} $                                                           | -    | -    | 10   | μs       |

| 10.2  | T <sub>doff</sub>                 | Delay time for switch-off                                                          | $ \begin{array}{l} R_{\text{load}} @ \ I_{\text{out}} = 3 \ A \\ PWM \rightarrow 10 \ \% \ V_{\text{out}} \ (\text{or} \\ 90\% \ lout) \end{array} $                                  | -    | -    | 10   | μs       |

|       | $\Delta T_d$                      | Delay time: symmetry                                                               | PWM accuracy = 1% @<br>2kHz                                                                                                                                                           | -    | -    | 5    | μs       |

| 10.3  | T <sub>d_dis</sub>                | Disable delay time                                                                 | DI / EN $\rightarrow$ 90% OUTx<br>@ I <sub>out</sub> = 3 A                                                                                                                            | -    | -    | 6    | μs       |

| 10.4  | T <sub>d_en</sub>                 | Enable delay time                                                                  | DI / EN $\rightarrow$ 10 % OUT                                                                                                                                                        | -    | -    | 6    | μs       |

| 10.5  | T <sub>d_pow</sub>                | Power-on delay time                                                                | $\begin{array}{l} \text{DIR= PWM=EN=1 /} \\ \text{DI=0 no load / } V_{PS} = \\ V_{dd} \text{ increasing} \\ V_{ps} = V_{dd} \rightarrow 10 \ \% \ V_{out1} \\ (= V_{ps}) \end{array}$ | -    | -    | 200  | μs       |

| 10.6  | T <sub>d_filter</sub>             | DI / EN digital filter time                                                        | -                                                                                                                                                                                     | 1    | -    | 3    | μs       |

| 10.7  | T <sub>rise_H</sub>               | Low-side transistor rise time                                                      | Non selectable by SPI                                                                                                                                                                 | 0.04 | -    | 0.2  | μs       |

| 10.8  | T <sub>fall_H</sub>               | Low-side transistor fall time                                                      | Non selectable by SPI                                                                                                                                                                 | 1    | -    | 3    | μs       |

|       |                                   | Voltage slew rate for high-side                                                    | super fast mode                                                                                                                                                                       | 7    | 14   | 24   |          |