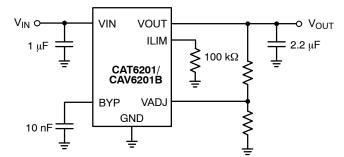

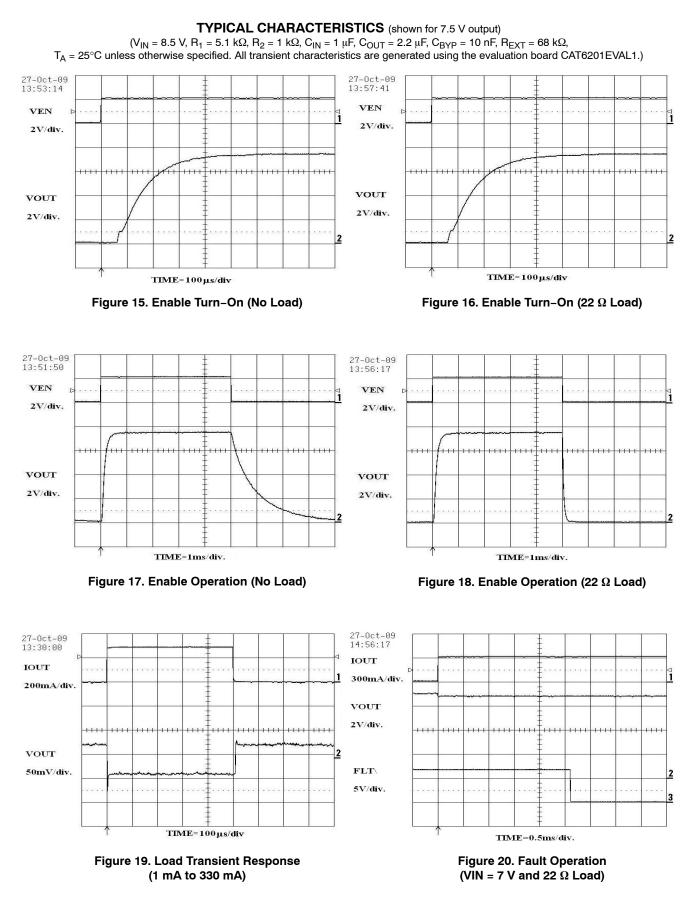

Figure 1. CAT6201/CAV6201B Typical Application

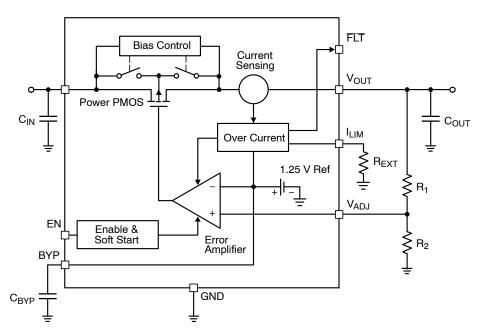

Figure 2. CAT6201/CAV6201B Functional Block Diagram

### Table 1. PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name | Description                                                                                                                                                                                                                                                  |  |  |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | VIN      | Supply voltage input                                                                                                                                                                                                                                         |  |  |  |

| 2       | FLT      | Fault indicator (active low)                                                                                                                                                                                                                                 |  |  |  |

| 3       | EN       | Enable input (active high)                                                                                                                                                                                                                                   |  |  |  |

| 4       | BYP      | A capacitor between BYP and GND controls the regulator's turn-on speed and improves PSRR                                                                                                                                                                     |  |  |  |

| 5       | GND      | Ground reference                                                                                                                                                                                                                                             |  |  |  |

| 6       | ILIM     | Current limit control pin                                                                                                                                                                                                                                    |  |  |  |

| 7       | VADJ     | Output voltage adjustment                                                                                                                                                                                                                                    |  |  |  |

| 8       | VOUT     | LDO Output Voltage                                                                                                                                                                                                                                           |  |  |  |

| Pad     | -        | Backside pad in center of package provides thermal contact for cooling, typically via the PCB ground plane. This pad is electrically active and connected to GND internally. An external Ground connection is not required and the pad may be left floating. |  |  |  |

### Table 2. ABSOLUTE MAXIMUM RATINGS

| Rating                                    | Value                       | Unit |

|-------------------------------------------|-----------------------------|------|

| V <sub>IN</sub> , V <sub>OUT</sub> , EN   | 0 to 16                     | V    |

| All other pins                            | -0.3 to +6.0                | V    |

| Junction Temperature, T <sub>J</sub>      | +150                        | °C   |

| Power Dissipation, P <sub>D</sub>         | Internally Limited (Note 1) | mW   |

| Storage Temperature Range, T <sub>S</sub> | -65 to +150                 | °C   |

| Lead Temperature (soldering, 5 sec.)      | 260                         | °C   |

| ESD Rating (Human Body Model)             | 1000                        | V    |

| ESD Rating (Machine Model)                | 200                         | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. The maximum allowable power dissipation at any  $T_A$  (ambient temperature) is  $P_{Dmax} = (T_{Jmax} - T_A) / \theta_{JA}$ . Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

#### Table 3. RECOMMENDED OPERATING CONDITIONS (Note 2)

| Parameter                                        | Range       | Unit |

|--------------------------------------------------|-------------|------|

| V <sub>IN</sub> , V <sub>OUT</sub> , EN          | 3.3 to 13.5 | V    |

| All other pins                                   | 0 to 6.0    | V    |

| Junction Temperature Range, T <sub>J</sub>       | -40 to +125 | °C   |

| Package Thermal Resistance (SOIC), $\theta_{JA}$ | 235         | °C/W |

| Package Thermal Resistance (TDFN), $\theta_{JA}$ | 92          | °C/W |

2. The device is not guaranteed to work outside its operating rating.

### **Pin Function**

**VIN** is the supply pin for both the LDO's operation and the load the LDO is driving. It is recommended that a 1  $\mu$ F ceramic bypass capacitor be placed between the V<sub>IN</sub> pin and ground in close proximity to the device. When using longer connections to the power supply, C<sub>IN</sub> value can be increased without limit. The operating input voltage range is from 3.3 V to 13.5 V.

**FLT** is an active low open-drain output indicating one of 3 fault conditions:

- 1. Input under-voltage: input is below the intended output voltage

- 2. Over-current. Brief over-current events are masked by a 3 ms time delay.

CAT6201/CAV6201B will limit current anytime the load tries to draw more than the maximum allowed, however reporting of this event will occur only if the event lasts longer than the delay timer. Events terminating before the timer reaches its full count are ignored and the timer is reset.

3. Over-temperature shutdown has occurred.

**EN** is an active HIGH logic level input for switching the regulator's output between ON and OFF. A weak internal pull down assures that if EN pin is left open, the circuit is disabled.

**BYP** controls the soft-start feature for the regulator. When large capacitive loads are present at the regulator's output, enabling the regulator will produce large current surges on the  $V_{IN}$  supply line. To reduce these surges the regulator can be turned on gently by connecting a capacitor between the BYP pin and ground. The larger the capacitance value the more slowly  $V_{OUT}$  approaches its programmed value. The table below gives a list of common capacitor values and their resulting turn-on times. If the soft-start feature is not desired, this pin should be left floating.

| Capacitance [nF] | t <sub>ON</sub> [ms] |

|------------------|----------------------|

| 0                | 0.2                  |

| 10               | 1                    |

| 100              | 10                   |

**GND** is the ground reference for the LDO in the TDFN package, center metal pad is internally connected to GND. If electrical contact is made with this pad, it should be to GND and/or the ground plane of the PCB. Connection to the ground plane enhances thermal conductivity drawing heat out of the package and into the surrounding PCB.

**ILIM** stands for Current Limit and is the control input for setting the point at which the current limit is invoked.  $I_{LIM}$  is defined as the current at which  $V_{OUT}$  is still within 80% of its nominal value and should not be confused with  $I_{SC}$ , the

short circuit current, measured at  $V_{OUT} = 0$  V, which is typically 100 mA greater than  $I_{LIM}$ .

A resistor  $R_{EXT}$  placed between  $I_{LIM}$  and GND selects the trip current according to a formula:

$$I_{LIM} = I_{LIM0} + \frac{Current\_Limit\_Factor(CLF)}{R_{EXT}}$$

(eq. 1)

$I_{LIM0}$  is the built–in minimum current limit (typically 150 mA), and CLF is a numerical value (typical 30,000 Volts) which relates the allowable load current to a resistance value. The value of this resistor is determined by the following equation:

$$\mathsf{R}_{\mathsf{EXT}}(\Omega) = \frac{\mathsf{CLF}(\mathsf{V})}{\mathsf{I}_{\mathsf{LIM}}(\mathsf{A}) - \mathsf{I}_{\mathsf{LIM0}}(\mathsf{A})} \tag{eq. 2}$$

It is recommended that  $I_{LIM}$  be set to at least 50% higher than the maximum intended continuous  $I_{OUT}$ .

Example: Set  $I_{\text{LIMIT}} = 600 \text{ mA}$

$$\mathsf{R}_{\mathsf{EXT}}(\Omega) = \frac{30,000 \text{ V}}{0.6 \text{ A} - 0.15 \text{ A}} = 68 \text{ K}\Omega \tag{eq. 3}$$

**VADJ** is the output voltage control pin. A resistor divider placed between VOUT and GND whose center point connects to VADJ sets the LDO regulator's output voltage. Typical VADJ value is 1.25 V. The current through the resistor divider can be anywhere between 10  $\mu$ A and 1 mA. The higher this current is, the lower the noise.

For best performance R1 and R2 should have similar temperature coefficients, otherwise output voltage accuracy will be compromised.

$$V_{OUT} = V_{ADJ} \left( 1 + \frac{R_1}{R_2} \right)$$

(eq. 4)

**VOUT** is the LDO regulator output. A small 2.2  $\mu$ F ceramic bypass capacitor is required between VOUT and ground. For better transient response, its value can be increased to 4.7  $\mu$ F. This capacitor should be located near the device.

VOUT is protected against short circuits and over-temp operation by internal circuitry. In the event of an over-current, the LDO behaves like a current source, limiting current at the output. The maximum current allowed is set by  $R_{EXT}$ , the resistor between  $I_{LIM}$  and GND. If the load attempts to draw more than the allowed current, VOUT and IOUT decrease together and thus limit the total power delivered.

VOUT is protected against the application of voltages greater than VIN. For example, in automotive applications, if CAT6201/CAV6201B is powering a remote load and damage occurs to a wiring harness shorting a powered line, Battery + for instance, to VOUT, CAT6201/CAV6201B will not be damaged by this higher voltage being applied to VOUT.

### Table 4. ELECTRICAL CHARACTERISTICS

$(V_{IN} = V_{OUT} + 1 V, V_{EN} = High, I_{OUT} = 1 mA, C_{IN} = 1 \mu F, C_{OUT} = 2.2 \mu F, R_{EXT} = 68 k\Omega$ , ambient temperature of 25°C (over recommended operating conditions unless specified otherwise). **Bold numbers** apply for the entire junction temperature range.)

| Symbol               | Parameter                                     | Conditions                                                                                                      | Min              | Тур   | Max   | Unit   |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|-------|-------|--------|

| V <sub>IN</sub>      | Input Voltage                                 |                                                                                                                 | 3.3              |       | 13.5  | V      |

| V <sub>OUT</sub>     | Output Voltage                                |                                                                                                                 | V <sub>ADJ</sub> |       | 12.5  |        |

| V <sub>ADJ</sub>     | ADJ Voltage                                   |                                                                                                                 | 1.232            | 1.250 | 1.268 | V      |

| I <sub>ADJ</sub>     | ADJ Input Current                             |                                                                                                                 |                  | 0.5   | 2.0   | μA     |

| TC <sub>OUT</sub>    | Output Voltage<br>Temp. Coefficient           | l <sub>OUT</sub> = 10 mA                                                                                        |                  | 100   |       | ppm/°C |

| $V_{R-LINE}$         | Line Regulation                               | V <sub>OUT</sub> + 1 V < V <sub>IN</sub> < 13.5 V                                                               | -0.2             | ±0.1  | +0.2  | %/V    |

|                      |                                               | The second se | -0.4             |       | +0.4  |        |

| V <sub>R-LOAD</sub>  | Load Regulation                               | I <sub>OUT</sub> = 1 mA to 300 mA                                                                               |                  | 0.7   | 2     | %      |

| V <sub>DROP</sub>    | Dropout Voltage (Note 3)                      | I <sub>OUT</sub> = 300 mA                                                                                       |                  | 250   | 350   | mV     |

| I <sub>GND</sub>     | Ground Current                                | I <sub>OUT</sub> = 0 mA                                                                                         |                  | 100   | 150   | μA     |

|                      |                                               | I <sub>OUT</sub> = 300 mA                                                                                       |                  | 160   | 300   |        |

| I <sub>GND-SD</sub>  | Shutdown Ground<br>Current                    | V <sub>EN</sub> < 0.4 V                                                                                         |                  | 0.5   | 2     | μA     |

| PSRR                 | Power Supply<br>Rejection Ratio               | f = 1 kHz, C <sub>BYP</sub> = 10 nF                                                                             |                  | 62    |       | dB     |

|                      |                                               | f = 20 kHz, C <sub>BYP</sub> = 10 nF                                                                            |                  | 52    |       |        |

| T <sub>ON</sub>      | Turn-On Time                                  | C <sub>BYP</sub> = 10 nF<br>V <sub>OUT</sub> = 0% – 100%                                                        |                  | 700   |       | μs     |

| I <sub>SC</sub>      | Output short circuit<br>current               | V <sub>OUT</sub> < 0.8 V<br>R <sub>EXT</sub> = 68 K                                                             | 500              | 650   | 800   | mA     |

|                      |                                               | V <sub>OUT</sub> < 0.8 V<br>I <sub>LIM</sub> = OPEN                                                             |                  | 200   |       |        |

| I <sub>LIM</sub>     | Output current limit                          | V <sub>OUT</sub> = 80% of V <sub>OUT</sub> measured<br>at a load of 1 mA<br>R <sub>EXT</sub> = 68 K             | 400              | 450   | 600   | mA     |

|                      |                                               | $V_{OUT}$ = 80% of $V_{OUT}$ measured<br>at a load of 1 mA<br>I <sub>LIM</sub> = OPEN                           | 120              | 150   | 180   |        |

| CLF                  | Current Limit Factor                          | V <sub>OUT</sub> < 0.8 V                                                                                        | 24               | 30    | 36    | KV     |

| t <sub>FD</sub>      | Fault Delay                                   |                                                                                                                 | 1.5              | 3     | 6     | ms     |

| V <sub>IN-UVLO</sub> | Under voltage<br>lockout threshold            |                                                                                                                 | 2.85             | 3.1   | 3.25  | V      |

| ESR                  | R <sub>OUT</sub> equivalent series resistance |                                                                                                                 | 5                |       | 500   | mΩ     |

#### ENABLE INPUT

| V <sub>HI</sub> | Logic High Level     | V <sub>IN</sub> = 3.3 to 13.5 V | 2 |      |     | V  |

|-----------------|----------------------|---------------------------------|---|------|-----|----|

| V <sub>LO</sub> | Logic Low Level      | V <sub>IN</sub> = 3.3 to 13.5 V |   |      | 0.4 | V  |

| I <sub>EN</sub> | Enable Input Current | V <sub>EN</sub> = 0.4 V         |   | 0.15 | 1   | μΑ |

|                 |                      | $V_{EN} = V_{IN}$               |   | 3    | 5   |    |

#### THERMAL PROTECTION

| T <sub>SD</sub>  | Thermal Shutdown   |  | 140 | °C |

|------------------|--------------------|--|-----|----|

| T <sub>HYS</sub> | Thermal Hysteresis |  | 10  | °C |

3. Dropout voltage is defined as the input-to-output differential at which the output voltage drops 2% below its nominal value. During test, the input voltage stays always above the minimum 3.3 V. The given values are for V<sub>OUT</sub> = 7.5 V.

http://onsemi.com 7

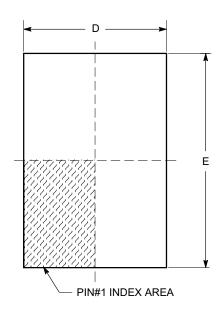

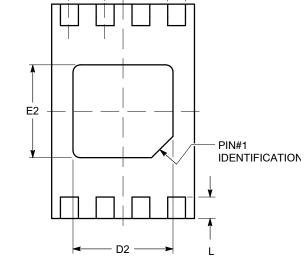

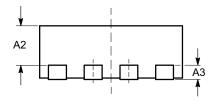

### PACKAGE DIMENSIONS

TDFN8, 2x3 CASE 511AK-01 ISSUE A

b

е

TOP VIEW

SIDE VIEW

| SYMBOL | MIN            | NOM       | MAX  |  |

|--------|----------------|-----------|------|--|

| А      | 0.70           | 0.75      | 0.80 |  |

| A1     | 0.00           | 0.02      | 0.05 |  |

| A2     | 0.45           | 0.55      | 0.65 |  |

| A3     | 0.20 REF       |           |      |  |

| b      | 0.20           | 0.25      | 0.30 |  |

| D      | 1.90           | 1.90 2.00 |      |  |

| D2     | 1.30           | 1.30 1.40 |      |  |

| E      | 2.90 3.00      |           | 3.10 |  |

| E2     | 1.20 1.30      |           | 1.40 |  |

| e      | 0.50 TYP       |           |      |  |

| L      | 0.20 0.30 0.40 |           |      |  |

Notes:

All dimensions are in millimeters.

Complies with JEDEC MO-229.

**BOTTOM VIEW**

FRONT VIEW

#### **ORDERING INFORMATION**

| Device Order Number | Specific<br>Device Marking | Package Type | Lead Finish | Shipping (Note 5)   |

|---------------------|----------------------------|--------------|-------------|---------------------|

| CAT6201VP2-GT3      | НКВ                        | TDFN-8       | NiPdAu      | 3,000 / Tape & Reel |

| CAV6201BVP2-GT3     | НКВ                        | TDFN-8       | NiPdAu      | 3,000 / Tape & Reel |

4. For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

5. For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

For detailed information and a breakdown of device nomenclature and numbering systems, please see the ON Semiconductor Device Nomenclature document, TND310/D, available at <u>www.onsemi.com</u>.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products herein. SCILLC may produce nor use of any product or circuit, and specifically disclaims any and all liability, including without further notice to any product of the application or use of any product or circuit, and specifically disclaims any and all liability, including without services and consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended to surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the desi

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative