### **Absolute Maximum Ratings**

Stresses beyond the limits listed below may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

| Supply Voltage±18\                                                          |

|-----------------------------------------------------------------------------|

| Input Voltage Range ±V <sub>S</sub> \                                       |

| Differential Input Voltage (G = 1 to 10)                                    |

| Differential Input Voltage (G > 10) $\leq$ 0.05 (R <sub>G</sub> + 800) +1 \ |

| Load Resistance (min)                                                       |

# **Operating Conditions**

| Supply Voltage Range               | $\pm 2.3V$ to $\pm 18V$ (4.6V to 36V) |

|------------------------------------|---------------------------------------|

| Gain Range                         | 1 to 10,000                           |

| Operating Temperature Range        | 40°C to 85°C                          |

| Junction Temperature               | 150°C                                 |

| Storage Temperature Range          | 65°C to 150°C                         |

| Lead Temperature (Soldering, 10s). | 260°C                                 |

# **Package Thermal Resistance**

| θ <sub>JA</sub> (DIP-8)100°C/W                                                                                  |

|-----------------------------------------------------------------------------------------------------------------|

| θ <sub>JA</sub> (SOIC-8)150°C/W                                                                                 |

| Package thermal resistance ( $\theta_{\text{JA}}),\ \text{JEDEC}$ standard, multi-layer test boards, still air. |

### **ESD Protection**

| SOIC-8 (HBM) 1.5i                      | κV |

|----------------------------------------|----|

| ESD Rating for HBM (Human Body Model). |    |

# **Electrical Characteristics**

$T_A = 25^{\circ}\text{C}, \ V_S = \pm 15\text{V}, \ R_L = 2\text{k}\Omega \ \text{to GND}; \ \text{unless otherwise noted}. \ \text{Gain} = 1 + (49.4\text{k/R}_{\text{G}}); \ \text{Total RTI Error} = V_{OSI} + (V_{OSO}/G)$

| Symbol                     | Parameter                               | Conditions                                                   | Min                   | Тур   | Max                   | Units  |

|----------------------------|-----------------------------------------|--------------------------------------------------------------|-----------------------|-------|-----------------------|--------|

| Gain                       |                                         |                                                              |                       |       |                       |        |

|                            | Gain Range                              |                                                              | 1                     |       | 10,000                |        |

|                            |                                         | G = 1, V <sub>OUT</sub> = ±10V                               | -0.1                  |       | 0.1                   | %      |

|                            | Coin Favor (1)                          | G = 10, V <sub>OUT</sub> = ±10V                              | -0.375                |       | 0.375                 | %      |

|                            | Gain Error (1)                          | G = 100, V <sub>OUT</sub> = ±10V                             | -0.375                |       | 0.375                 | %      |

|                            |                                         | G = 1,000, V <sub>OUT</sub> = ±10V                           | -0.8                  |       | 0.8                   | %      |

|                            | Cain Nanlinearity                       | $G = 1 - 100$ , $V_{OUT} = -10V$ to 10V, $R_L = 10kΩ$        |                       | 10    | 50                    | ppm    |

|                            | Gain Nonlinearity                       | $G = 1 - 100$ , $V_{OUT} = -10V$ to $10V$ , $R_L = 2k\Omega$ |                       | 10    | 95                    | ppm    |

|                            | Gain vs. Temperature                    | G = 1                                                        |                       | <10   |                       | ppm/°C |

|                            | Gain vs. remperature                    | G > 1                                                        |                       | <-50  |                       | ppm/°C |

|                            | Reference Gain Error <sup>(1)</sup>     | $V_S = \pm 16.5V$                                            | -0.03                 |       | 0.03                  | %      |

| Voltage Off                | set                                     |                                                              |                       |       |                       |        |

| V <sub>OSI</sub>           | Input Offset Voltage                    | $V_S = \pm 4.5 V \text{ to } \pm 16.5 V$                     | -125                  |       | 125                   | μV     |

|                            | Average Temperature Coefficient         | $V_S = \pm 4.5 V \text{ to } \pm 16.5 V$                     |                       | 0.1   |                       | μV/°C  |

| V <sub>OSO</sub>           | Output Offset Voltage                   | $V_S = \pm 4.5 V$ to $\pm 16.5 V$ , $G = 1$                  | -1500                 | 200   | 1500                  | μV     |

|                            | Average Temperature Coefficient         | $V_S = \pm 4.5 V \text{ to } \pm 16.5 V$                     |                       | 2.5   |                       | μV/°C  |

|                            |                                         | $G = 1, V_S = \pm 2.3V \text{ to } \pm 18V$                  | 80                    | 100   |                       | dB     |

| PSR                        | Offset Referred to the Input vs. Supply | $G = 10, V_S = \pm 2.3V \text{ to } \pm 18V$                 | 95                    | 120   |                       | dB     |

| 1 011                      | Chact reletted to the input vs. Supply  | $G = 100, V_S = \pm 2.3V \text{ to } \pm 18V$                | 110                   | 140   |                       | dB     |

|                            |                                         | $G = 1000, V_S = \pm 2.3V \text{ to } \pm 18V$               | 110                   | 140   |                       | dB     |

| Input Curre                | nt                                      |                                                              |                       |       | ,                     |        |

| $I_{B}$                    | Input Bias Current                      | $V_{S} = \pm 16.5 V$                                         | -2                    | 0.5   | 2                     | nA     |

|                            | Average Temperature Coefficient         | $V_S = \pm 16.5V$                                            |                       | 3     |                       | pA/°C  |

| I <sub>OS</sub>            | Input Offset Current                    | $V_S = \pm 16.5V$                                            | -1                    |       | 1                     | nA     |

| Input                      |                                         |                                                              |                       |       |                       |        |

|                            | Input Impedance                         | Differential                                                 |                       | 10, 2 |                       | GΩ, pF |

|                            | mpat impodance                          | Common-Mode                                                  |                       | 10, 2 |                       | GΩ, pF |

| IVR                        | Input Voltage Range (2)                 | $V_S = \pm 4.5V, G = 1$                                      | -V <sub>S</sub> + 1.9 |       | +V <sub>S</sub> - 1.2 | V      |

|                            | input voltage Harrige                   | $V_S = \pm 16.5V, G = 1$                                     | -V <sub>S</sub> + 1.9 |       | +V <sub>S</sub> - 1.4 | V      |

|                            |                                         | $G = 1, V_S = \pm 16.5V$                                     | 70                    | 90    |                       | dB     |

| CMRR                       | Common-Mode Rejection Ratio             | $G = 10, V_S = \pm 16.5V$                                    | 90                    | 110   |                       | dB     |

|                            |                                         | $G = 100, V_S = \pm 16.5V$                                   | 108                   | 130   |                       | dB     |

|                            |                                         | $G = 1000, V_S = \pm 16.5V$                                  | 108                   | 130   |                       | dB     |

| Output                     |                                         |                                                              |                       |       | 1                     |        |

| V <sub>OUT</sub>           | Output Swing                            | V <sub>S</sub> = ±2.3V to ±4.5V                              | -V <sub>S</sub> + 1.1 |       | +V <sub>S</sub> - 1.2 | V      |

|                            |                                         | V <sub>S</sub> = ±18V, G = 1                                 | -V <sub>S</sub> + 1.4 |       | +V <sub>S</sub> - 1.2 | V      |

| I <sub>SC</sub>            | Short Circuit Current                   |                                                              |                       | ±20   |                       | mA     |

| Dynamic Pe                 | erformance                              |                                                              |                       |       | T                     |        |

| BW <sub>-3dB</sub> Small S |                                         | G = 1                                                        |                       | 700   |                       | kHz    |

|                            | Small Signal -3dB Bandwidth             | G = 10                                                       |                       | 400   |                       | kHz    |

|                            |                                         | G = 100                                                      |                       | 100   |                       | kHz    |

|                            |                                         | G = 1000                                                     |                       | 12    |                       | kHz    |

| SR                         | Slew Rate                               | $G = 10, V_S = \pm 15V$                                      | 0.6                   | 1.2   |                       | V/µs   |

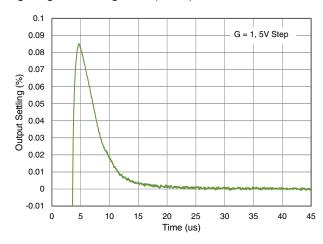

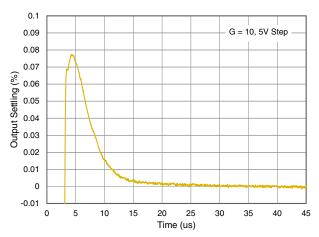

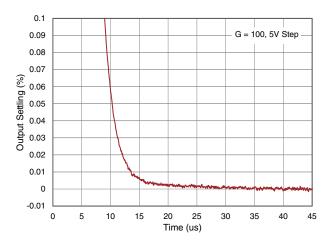

| t <sub>S</sub>             | Settling Time to 0.01%                  | 5V step, G = 1 to 100                                        |                       | 13    |                       | μs     |

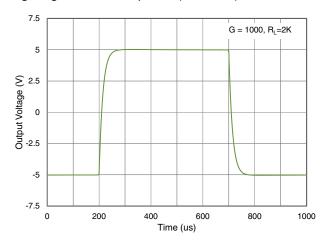

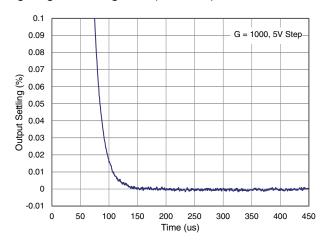

| ıs s                       |                                         | 5V step, G = 1000                                            |                       | 110   |                       | μs     |

# **Electrical Characteristics continued**

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $R_L = 2k\Omega$  to GND; unless otherwise noted. Gain = 1 + (49.4k/R<sub>G</sub>); Total RTI Error =  $V_{OSO}/G$ )

| Symbol           | Parameter                  | Conditions                              | Min                   | Тур      | Max                   | Units            |

|------------------|----------------------------|-----------------------------------------|-----------------------|----------|-----------------------|------------------|

| Noise            |                            |                                         |                       |          |                       |                  |

| e <sub>ni</sub>  | Input Voltage Noise        | 1kHz, G = 1000, V <sub>S</sub> = ±15V   |                       | 6.6      | 13                    | nV/√Hz           |

| e <sub>no</sub>  | Output Voltage Noise       | $1kHz, G = 1, V_S = \pm 15V$            |                       | 70       | 100                   | nV/√Hz           |

|                  |                            | G = 1, 0.1Hz to 10Hz                    |                       | 5        |                       | μV <sub>pp</sub> |

| e <sub>npp</sub> | Peak-to-Peak Noise (RTI)   | G = 10, 0.1Hz to 10Hz, $V_S = \pm 15V$  |                       |          | 0.8                   | μV <sub>pp</sub> |

|                  |                            | G = 100, 0.1Hz to 10Hz, $V_S = \pm 15V$ |                       | 0.2      | 0.4                   | μV <sub>pp</sub> |

| i <sub>n</sub>   | Current Noise              | f = 1kHz                                |                       | 100      |                       | fA/√Hz           |

| i <sub>npp</sub> | Peak-to-Peak Current Noise | 0.1Hz to 10Hz                           |                       | 10       |                       | pA <sub>pp</sub> |

| Reference        | Input                      |                                         |                       |          |                       |                  |

| R <sub>IN</sub>  | Input Resistance           |                                         |                       | 20       |                       | kΩ               |

| I <sub>IN</sub>  | Input Current              | V <sub>S</sub> = ±16.5V                 |                       | 50       | 60                    | μΑ               |

|                  | Voltage Range              |                                         | -V <sub>S</sub> + 1.6 |          | +V <sub>S</sub> - 1.6 | V                |

|                  | Gain to Output             |                                         |                       | 1±0.0001 |                       |                  |

| Power Sup        | ply                        |                                         |                       |          |                       |                  |

| Vs               | Operating Range            |                                         | ±2.3                  |          | ±18                   | V                |

| I <sub>S</sub>   | Supply Current             | V <sub>S</sub> = ±16.5V                 |                       | 1.3      | 2.2                   | mA               |

#### Notes:

- 1. Nominal reference voltage gain is 1.0

- 2. Input voltage range =  $CMV + (G V_{DIFF})/2$

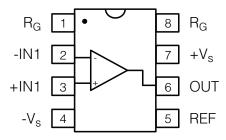

# **CLC1200 Pin Configurations** SOIC-8, DIP-8

# **CLC1200 Pin Assignments**

SOIC-8, DIP-8

| Pin No. | Pin Name        | Description                                 |

|---------|-----------------|---------------------------------------------|

| 1, 8    | R <sub>G</sub>  | R <sub>G</sub> sets gain                    |

| 2       | -IN             | Negative input                              |

| 3       | +IN             | Positive input                              |

| 4       | -V <sub>S</sub> | Negative supply                             |

| 5       | REF             | Output is referred to the REF pin potential |

| 6       | OUT             | Output                                      |

| 7       | +V <sub>S</sub> | Positive supply                             |

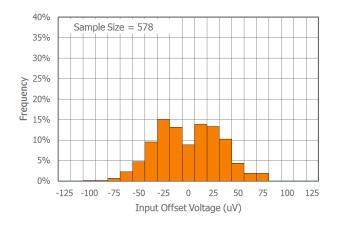

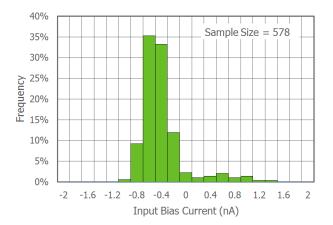

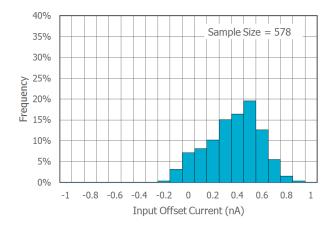

$T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$  to GND; unless otherwise noted.

### Input Offset Distribution (typical)

### Input Bias Current Distribution (typical)

### Input Offset Current Distribution (typical)

$T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$  to GND; unless otherwise noted.

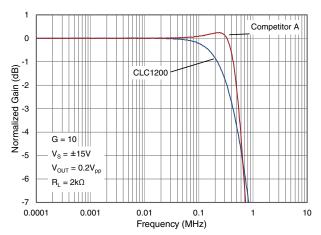

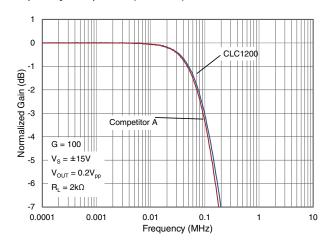

### Gain vs. Frequency

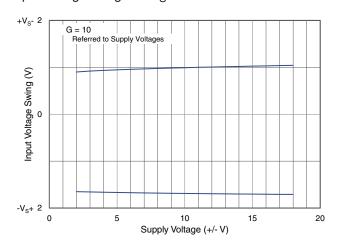

# Input Voltage Range vs. V<sub>S</sub>

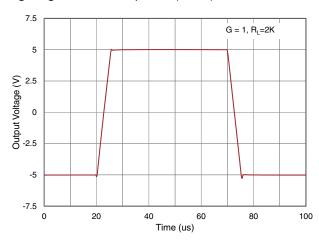

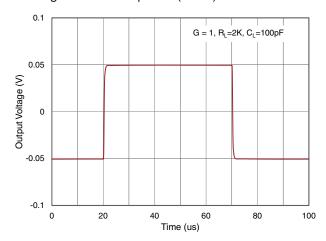

### Large Signal Pulse Response (G = 1)

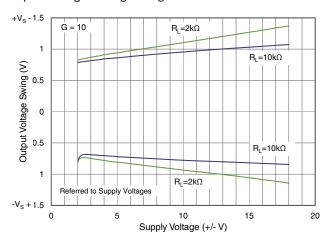

### Output Voltage Swing vs. V<sub>S</sub>

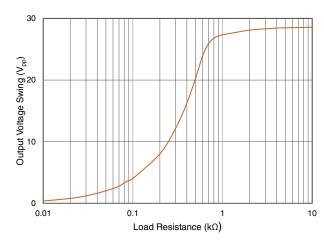

### Output Voltage Swing vs. RL

### Large Signal Settling Time (G = 1)

$T_A$  = 25°C,  $V_S$  = ±15V,  $R_L$  = 2k $\Omega$  to GND; unless otherwise noted.

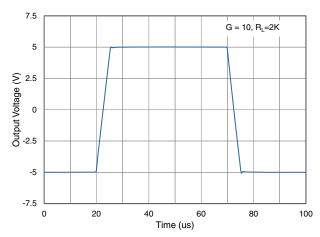

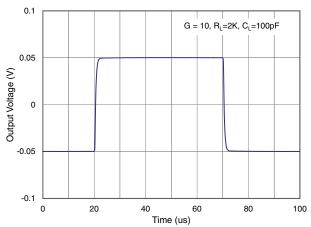

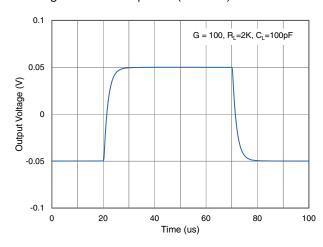

### Large Signal Pulse Response (G = 10)

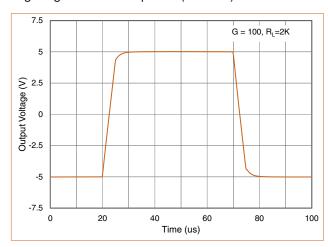

### Large Signal Pulse Response (G = 100)

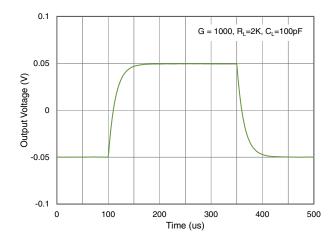

### Large Signal Pulse Response (G = 1000)

### Large Signal Settling Time (G = 10)

Large Signal Settling Time (G = 100)

### Large Signal Settling Time (G = 1000)

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $R_L = 2k\Omega$  to GND; unless otherwise noted.

### Small Signal Pulse Response (G = 1)

# Small Signal Pulse Response (G = 10)

### Small Signal Pulse Response (G = 100)

Small Signal Pulse Response (G = 1000)

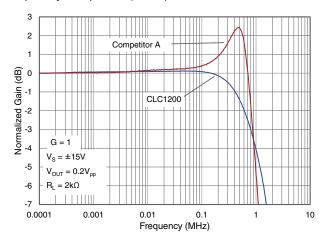

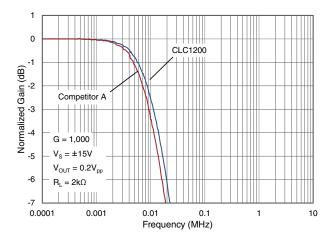

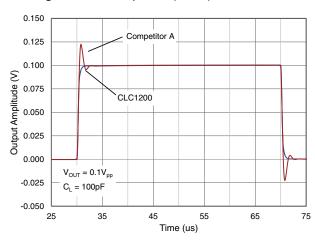

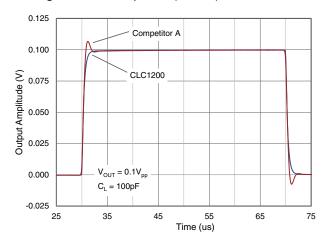

# **Typical Competitive Comparison Plots**

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $R_L = 2k\Omega$ , Resurgent evaluation board; unless otherwise noted.

# Frequency Response (G = 1)

### Frequency Response (G = 10)

### Frequency Response (G = 100)

Frequency Response (G = 1000)

### Small Signal Pulse Response (G = 1)

Small Signal Pulse Response (G = 10)

### **Application Information**

### **Basic Information**

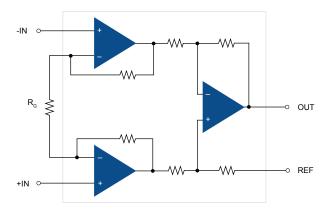

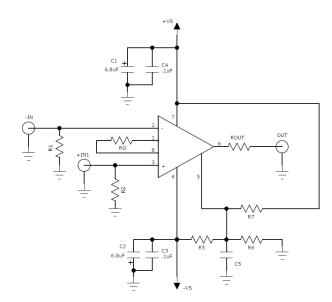

The CLC1200 is a monolithic instrumentation amplifier based on the classic three op amp solution, refer to the Functional Block Diagram shown in Figure 1. The CLC1200 produces a single-ended output referred to the REF pin potential.

Figure 1: Functional Block Diagram

The internal resistors are trimmed which allows the gain to be accurately adjusted with one external resistor  $R_{\rm G}$ .

$$G = \frac{49.4k}{R_G} + 1$$

;  $R_G = \frac{49.4k}{G - 1}$

$R_G$  also determines the transconductance of the preamp stage. As  $R_G$  is reduced for larger gains, the transconductance increases to that of the input transistors. Producing the following advantages:

- Open-loop gain increases as the gain is increased, reducing gain related errors

- Gain-bandwidth increases as the gain is increased, optimizing frequency response

- Reduced input voltage noise which is determined by the collector current and base resistance of the input devices

### **Gain Selection**

The impedance between pins 1 and 8,  $R_G$ , sets the gain of the CLC1200. Table 1 shows the required standard table values of  $R_G$  for various calculated gains. For G = 1,  $R_G = \infty$ .

| 1% R <sub>G</sub> (Ω) | Caclulated<br>Gain | 0.1% R <sub>G</sub> (Ω) | Calculated<br>Gain |

|-----------------------|--------------------|-------------------------|--------------------|

| 49.9k                 | 1.990              | 49.3k                   | 2.002              |

| 12.4k                 | 4.984              | 12.4k                   | 4.984              |

| 5.49k                 | 9.998              | 5.49k                   | 9.998              |

| 2.61k                 | 19.93              | 2.61k                   | 19.93              |

| 1.00k                 | 50.40              | 1.01k                   | 49.91              |

| 499                   | 100.0              | 499                     | 100.0              |

| 249                   | 199.4              | 249                     | 199.4              |

| 100                   | 495.0              | 98.8                    | 501.0              |

| 49.9                  | 991.0              | 49.3                    | 1,003.0            |

Table 1: Recommended R<sub>G</sub> Values

Follow these guidelines for improved performance:

- To maintain gain accuracy, use 0.1% to 1% resistors

- To minimize gain error, avoid high parasitic resistance in series with R<sub>G</sub>

- To minimize gain drift, use low TC resistors (<10ppm/°C)

### **Common Mode Rejection**

The CLC1200 offers high CMRR. To achieve optimal CMRR performance:

- Connect the reference terminal (pin 5) to a low impedance source

- Minimize capacitive and resistive differences between the inputs

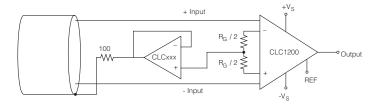

In many applications, shielded cables are used to minimize noise. Properly drive the shield for best CMRR performance over frequency. Figures 1 and 2 show active data guards that are configured to improve AC common-mode rejections. the capacitances of input cable shields are "bootstrapped" to minimize the capacitance mismatch between the inputs.

Figure 2: Common-mode Shield Driver

Figure 3: Differential Shield Driver

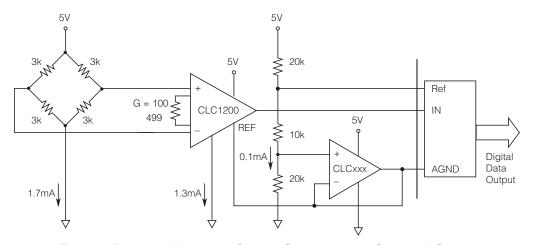

### **Pressure Measurement Applications**

The CLC1200 is especially suitable for higher resistance pressure sensors powered at lower voltages where small size and low power become more significant.

Figure 3 shows a  $3k\Omega$  pressure transducer bridge powered from 5V. In such a circuit, the bridge consumes only 1.7mA. Adding the CLC1200 and a buffered voltage divider allows the signal to be conditioned for only 3.8mA of total supply current.

Small size and low cost make the CLC1200 especially attractive for voltage output pressure transducers. Since it delivers low noise and drift, it will also serve applications such as diagnostic noninvasive blood pressure measurement.

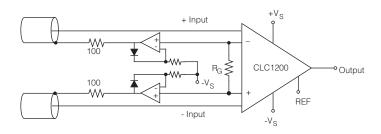

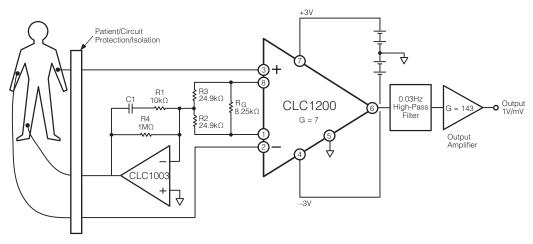

### **Medical ECG**

The CLC1200 is perfect for ECG monitors because of its low current noise. A typical application is shown in Figure 4. The CLC1200's low power, low supply voltage requirements, and space-saving 8-lead SOIC package offerings make it an excellent choice for battery-powered data recorders.

Furthermore, the low bias currents and low current noise, coupled with the low voltage noise of the CLC1200, improve the dynamic range for better performance.

The value of capacitor C1 is chosen to maintain stability of the right leg drive loop. Proper safeguards, such as isolation, must be added to this circuit to protect the patient from possible harm.

Figure 4: Pressure Monitoring Circuits Operating on a Single 5V Supply

Figure 5: Typical Circuit for ECG Monitor Applications

### Grounding

The output voltage of the CLC1200 is developed with respect to the potential on the reference terminal (pin 8). Simply tie the REF pin to the appropriate "local ground" to resolve many grounding problems.

To isolate low level analog signals from a noisy digital environment, many data acquisition components have separate analog and digital ground pins. Use separate ground lines (analog and digital) to minimize current flow from sensitive areas to system ground. These ground returns must be tied together at some point, usually best at the ADC.

### **Layout Considerations**

General layout and supply bypassing play major roles in high frequency performance. Resurgent has evaluation boards to use as a guide for high frequency layout and as an aid in device testing and characterization. Follow the steps below as a basis for high frequency layout:

- Include 6.8µF and 0.1µF ceramic capacitors for power supply decoupling

- Place the 6.8µF capacitor within 0.75 inches of the power pin

- Place the 0.1µF capacitor within 0.1 inches of the power pin

- Remove the ground plane under and around the part, especially near the input and output pins to reduce parasitic capacitance

- Minimize all trace lengths to reduce series inductances

Refer to the evaluation board layouts below for more information.

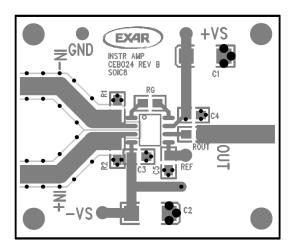

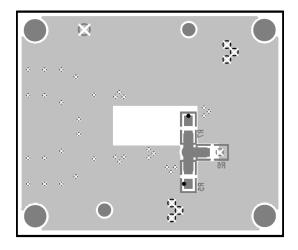

### **Evaluation Board Information**

The following evaluation boards are available to aid in the testing and layout of these devices:

| Evaluation Board # | Products          |

|--------------------|-------------------|

| CEB024             | CLC1200 in SOIC-8 |

### **Evaluation Board Schematics**

Evaluation board schematics and layouts are shown in Figures 6-8. These evaluation boards are built for dual-supply operation. Follow these steps to use the board in a single-supply application:

- 1. Short -V<sub>S</sub> to ground.

- 2. Use C3 and C4, if the -V<sub>S</sub> pin of the amplifier is not directly connected to the ground plane.

Figure 6. CEB024 Schematic

Figure 7. CEB024 Top View

Figure 8. CEB024 Bottom View

Variation AA

0.193 BSC

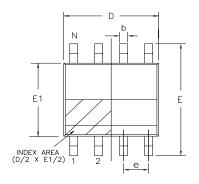

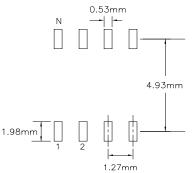

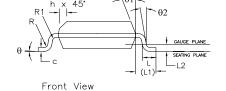

### **Mechanical Dimensions**

### **SOIC-8 Package**

RECOMMENDED PCB LAND PATTERN

DIMENSIONS IN MM (Control Unit) DIMENSIONS IN INCH (Reference Unit) SYMBOLS MIN NOM MAX MIN NOM 1.75 0.069 1.35 Α1 0.10 0.25 0.004 0.010 A2 1.25 1.65 0.049 0.065 0.31 0.51 0.012 0.020 b 0.17 0.25 0.007 0.010 6.00 BSC 0.236 BSC Ε 3.90 BSC 0.154 BSC E1 0.050 BSC 1.27 BSC 0.25 0.010 0.020 h 0.50 0.016 L1 L2 1.04 REF 0.041 REF 0.25 BS 0.010 BSC R 0.07 0.003 0.07 0.003 R1 8° θ 0. 0, 15° θ1 5° 5° 15° θ2 0,

4.90 BSC

JEDEC MS-012

8 Pin SOICN

D

Side View

Top View

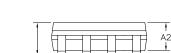

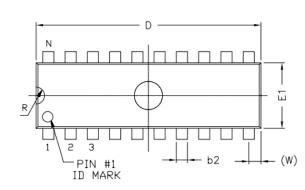

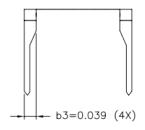

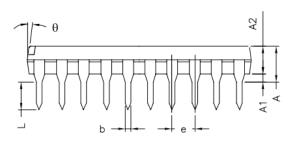

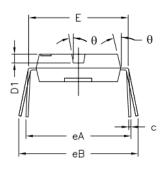

### **DIP-8 Package**

REMARKS: FOR 8LD AND 16LD ALL END LEADS (4X) ARE HALF LEAD TYPES

Top View

Side View

Front View

| 8 Pin PDIP JEDEC MS-001 Variation BA |                    |                                      |       |      |        |       |

|--------------------------------------|--------------------|--------------------------------------|-------|------|--------|-------|

| SYMBOLS                              | 4 -                | DIMENSIONS IN INCH<br>(Control Unit) |       |      |        |       |

|                                      | MIN                | NOM                                  | MAX   | MIN  | NOM    | MAX   |

| Α                                    | _                  | _                                    | 0.210 | _    | _      | 5.33  |

| A1                                   | 0.015              | _                                    | _     | 0.38 | _      | _     |

| A2                                   | 0.115              | 0.130                                | 0.195 | 2.92 | 3.30   | 4.95  |

| b                                    | 0.014              | 0.018                                | 0.022 | 0.36 | 0.46   | 0.56  |

| b2                                   | 0.045              | 0.060                                | 0.070 | 1.14 | 1.52   | 1.78  |

| С                                    | 0.008              | 0.010                                | 0.014 | 0.20 | 0.25   | 0.36  |

| D1                                   | 0.030              | _                                    | 0.060 | 0.76 | _      | 1.52  |

| E                                    | 0.300              | 0.310                                | 0.325 | 7.62 | 7.87   | 8.26  |

| E1                                   | 0.240              | 0.250                                | 0.280 | 6.10 | 6.35   | 7.11  |

| е                                    | C                  | ).100 E                              | SC    | 2    | .54 BS | C     |

| eA                                   | 0                  | 0.300 E                              | SC    | 7    | .62 BS | C     |

| eB                                   | _                  | _                                    | 0.430 | -    | _      | 10.92 |

| L                                    | 0.115              | 0.130                                | 0.150 | 2.92 | 3.30   | 3.81  |

| W                                    | 0.075 REF 1.91 REF |                                      |       | -    |        |       |

| R                                    | 0.030 BSC          |                                      |       | C    | .76 BS | iC    |

| θ                                    | 4°                 | 7*                                   | 10°   | 4*   | 7*     | 10°   |

| D                                    | 0.355              | 0.365                                | 0.400 | 9.02 | 9.27   | 10.16 |

| N                                    | 8 8                |                                      |       |      |        |       |

### **Ordering Information**

| Part Number    | Package              | Green | Operating Temperature Range | Packaging        |

|----------------|----------------------|-------|-----------------------------|------------------|

| CLC1200ISO8X   | SOIC-8               | Yes   | -40°C to +85°C              | Tape & Reel      |

| CLC1200ISO8MTR | SOIC-8 Yes           |       | -40°C to +85°C              | Mini Tape & Reel |

| CLC1200ISO8EVB | Evaluation Board N/A |       | N/A                         | N/A              |

| CLC1200IDP8    | DIP-8 Yes            |       | -40°C to +85°C              | Rail             |

| CLC1200ICF     | Die                  | Yes   | -40°C to +85°C              | Wafer            |

Moisture sensitivity level for all parts is MSL-1. Mini Tape and Reel contains 250 pieces.

### **Revision History**

| Revision         | Date       | Description                                                                                                                                                                                                                                                      |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2E (ECN 1513-02) | March 2015 | Reformat into Exar data sheet template. Updated PODs and thermal resistance numbers. Updated ordering information table to include MTR and EVB part numbers. Updated evaluation board top and bottom views to Rev b. Added schematic used for evaluation boards. |

| 2E.R             | July 2018  | Updated to Resurgent Semiconductor.                                                                                                                                                                                                                              |

### For Further Assistance:

www.resurgentsemi.net

#### NOTICE

Resurgent Semiconductor reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. Resurgent Semiconductor assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

Resurgent Semiconductor does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Resurgent Semiconductor receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of Resurgent Semiconductor is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of Resurgent Semiconductor is prohibited.