### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage ( $V_{CC}$ to $V_{EE}$ )                                             |

|-------------------------------------------------------------------------------------|

| (SENSE <sup>+</sup> , SENSE <sup>-</sup> , FILTER) V <sup>-</sup> to V <sup>+</sup> |

| Logic Outputs (ISRC, ISNK, TSD) COMMON to V <sub>CC</sub>                           |

| Input Voltage (–IN, +IN) $V_{EE} - 0.3V$ to $V_{EE} + 36V$                          |

| Input Current 10mA                                                                  |

| Current Control Inputs                                                              |

| (VC <sub>SRC</sub> , VC <sub>SNK</sub> )COMMON to COMMON + 7V                       |

| Enable Logic Input COMMON to V <sub>CC</sub>                                        |

| COMMON V <sub>FF</sub> to V <sub>CC</sub>                                           |

| Output Short-Circuit Duration Indefinite                                            |

| Operating Temperature Range (Note 2)–40°C to 85°C                                   |

| Specified Temperature Range (Note 3) –40°C to 85°C                                  |

| Maximum Junction Temperature 150°C                                                  |

| Storage Temperature Range–65°C to 150°C                                             |

| Lead Temperature (Soldering, 10 sec)                                                |

|                                                                                     |

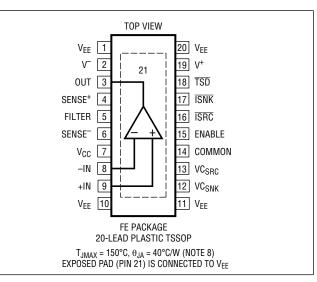

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION   | SPECIFIED TEMPERATURE RANGE |

|------------------|-----------------|---------------|-----------------------|-----------------------------|

| LT1970CFE#PBF    | LT1970CFE#TRPBF | LT1970CFE     | 20-Lead Plastic TSSOP | 0°C to 70°C                 |

| LT1970IFE#PBF    | LT1970IFE#TRPBF | LT1970IFE     | 20-Lead Plastic TSSOP | –40°C to 85°C               |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. See Test Circuit for standard test conditions.

| SYMBOL                       | PARAMETER                           | CONDITIONS                                                   |   | MIN  | ТҮР  | MAX                 | UNITS             |

|------------------------------|-------------------------------------|--------------------------------------------------------------|---|------|------|---------------------|-------------------|

| Power Op Amp Characteristics |                                     |                                                              |   |      |      |                     |                   |

| V <sub>0S</sub>              | Input Offset Voltage                | 0°C < T <sub>A</sub> < 70°C<br>-40°C < T <sub>A</sub> < 85°C | • |      | 200  | 600<br>1000<br>1300 | μV<br>μV<br>μV    |

|                              | Input Offset Voltage Drift (Note 4) |                                                              | • | -10  | -4   | 10                  | μV/°C             |

| l <sub>os</sub>              | Input Offset Current                | $V_{CM} = 0V$                                                | • | -100 |      | 100                 | nA                |

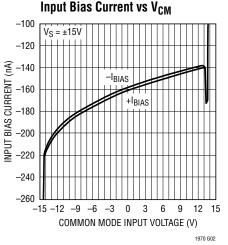

| I <sub>B</sub>               | Input Bias Current                  | $V_{CM} = 0V$                                                | • | -600 | -160 |                     | nA                |

|                              | Input Noise Voltage                 | 0.1Hz to 10Hz                                                |   |      | 3    |                     | μV <sub>P-P</sub> |

| e <sub>n</sub>               | Input Noise Voltage Density         | 1kHz                                                         |   |      | 15   |                     | nV/√Hz            |

| i <sub>n</sub>               | Input Noise Current Density         | 1kHz                                                         |   |      | 3    |                     | pA/√Hz            |

|                              |                                     | 1                                                            |   |      |      |                     | 1970fe            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. See Test Circuit for standard test conditions.

| SYMBOL                  | PARAMETER                                | CONDITIONS                                                                                                                                                                                                                                                                                       |             | MIN                        | ТҮР                              | MAX                      | UNITS                |

|-------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------|----------------------------------|--------------------------|----------------------|

| R <sub>IN</sub>         | Input Resistance                         | Common Mode<br>Differential Mode                                                                                                                                                                                                                                                                 |             |                            | 500<br>100                       |                          | kΩ<br>kΩ             |

| CIN                     | Input Capacitance                        | Pin 8 and Pin 9 to Ground                                                                                                                                                                                                                                                                        |             |                            | 6                                |                          | pF                   |

| V <sub>CM</sub>         | Input Voltage Range                      | Typical<br>Guaranteed by CMRR Test                                                                                                                                                                                                                                                               | •           | -14.5<br>-12.0             |                                  | 13.6<br>12.0             | V<br>V               |

| CMRR                    | Common Mode Rejection Ratio              | -12V < V <sub>CM</sub> < 12V                                                                                                                                                                                                                                                                     | •           | 92                         | 105                              |                          | dB                   |

| PSRR                    | Power Supply Rejection Ratio             | $ \begin{array}{l} V_{EE} = V^- = -5V,  V_{CC} = V^+ = 3V \ \text{to} \ 30V \\ V_{EE} = V^- = -5V,  V_{CC} = 30V,  V^+ = 2.5V \ \text{to} \ 30V \\ V_{EE} = V^- = -3V \ \text{to} \ -30V,  V_{CC} = V^+ = 5V \\ V_{EE} = -30V,  V^- = -2.5V \ \text{to} \ -30V,  V_{CC} = V^+ = 5V \end{array} $ | •<br>•<br>• | 90<br>110<br>90<br>110     | 100<br>130<br>100<br>130         |                          | dB<br>dB<br>dB<br>dB |

| A <sub>VOL</sub>        | Large-Signal Voltage Gain                | R <sub>L</sub> = 1k, -12.5V < V <sub>OUT</sub> < 12.5V                                                                                                                                                                                                                                           | •           | 100<br>75                  | 150                              |                          | V/mV<br>V/mV         |

|                         |                                          | $R_L = 100\Omega, -12.5V < V_{OUT} < 12.5V$                                                                                                                                                                                                                                                      | •           | 80<br>40                   | 120                              |                          | V/mV<br>V/mV         |

|                         |                                          | $R_L = 10\Omega$ , $-5V < V_{OUT} < 5V$ , $V^+ = -V^- = 8V$                                                                                                                                                                                                                                      | •           | 20<br>5                    | 45                               |                          | V/mV<br>V/mV         |

| V <sub>OL</sub>         | Output Sat Voltage Low                   |                                                                                                                                                                                                                                                                                                  | •           |                            | 1.9<br>0.8                       | 2.5                      | V<br>V               |

| V <sub>OH</sub>         | Output Sat Voltage High                  |                                                                                                                                                                                                                                                                                                  | •           |                            | 1.7<br>1.0                       | 2.3                      | V<br>V               |

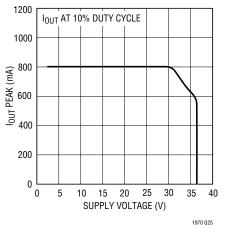

| I <sub>SC</sub>         | Output Short-Circuit Current             | Output Low, R <sub>SENSE</sub> = 0Ω<br>Output High, R <sub>SENSE</sub> = 0Ω                                                                                                                                                                                                                      |             | 500<br>-1000               | 800<br>800                       | 1200<br>500              | mA<br>mA             |

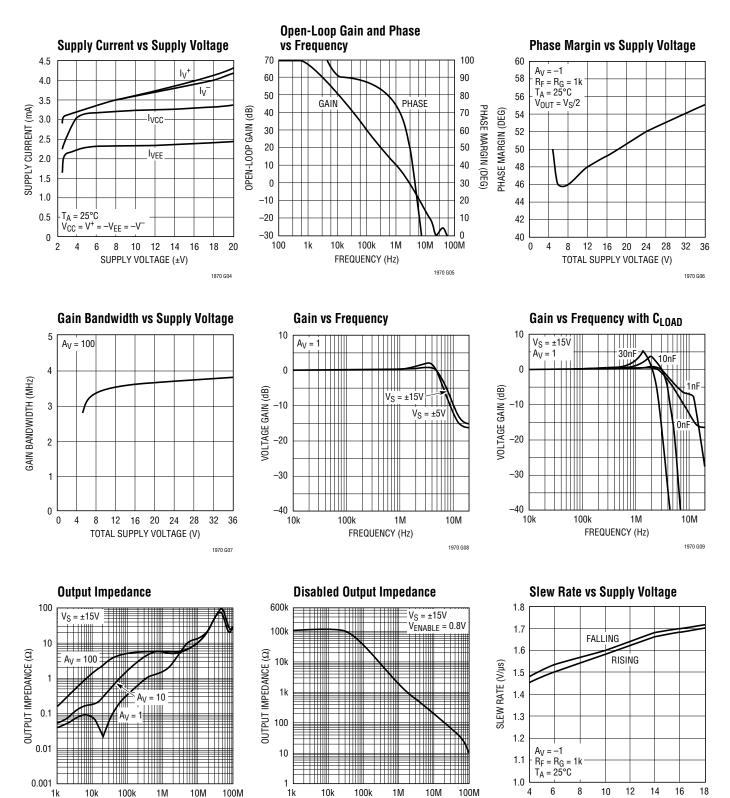

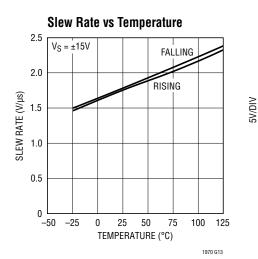

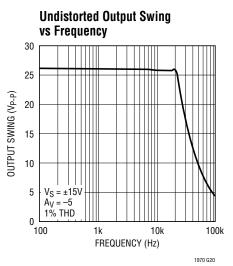

| SR                      | Slew Rate                                | $-10V < V_{OUT} < 10V, R_{L} = 1k$                                                                                                                                                                                                                                                               |             | 0.7                        | 1.6                              |                          | V/µs                 |

| FPBW                    | Full Power Bandwidth                     | V <sub>OUT</sub> = 10V <sub>PEAK</sub> (Note 5)                                                                                                                                                                                                                                                  |             | 11                         |                                  |                          | kHz                  |

| GBW                     | Gain Bandwidth Product                   | f = 10kHz                                                                                                                                                                                                                                                                                        |             |                            | 3.6                              |                          | MHz                  |

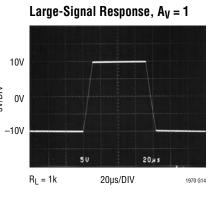

| t <sub>S</sub>          | Settling Time                            | 0.01%, V <sub>OUT</sub> = 0V to 10V, A <sub>V</sub> = -1, R <sub>L</sub> = 1k                                                                                                                                                                                                                    |             |                            | 8                                |                          | μs                   |

| Current Sen             | se Characteristics                       |                                                                                                                                                                                                                                                                                                  |             |                            |                                  |                          |                      |

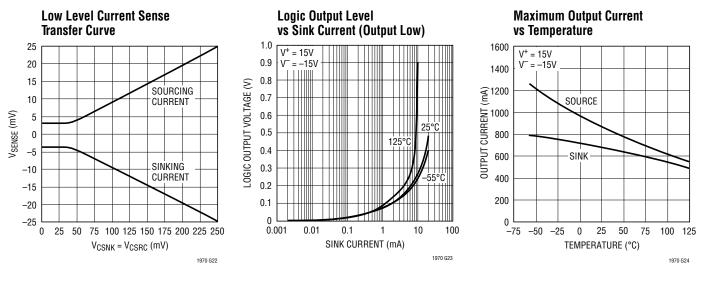

| V <sub>SENSE(MIN)</sub> | Minimum Current Sense Voltage            | $VC_{SRC} = VC_{SNK} = 0V$                                                                                                                                                                                                                                                                       | •           | 0.1<br>0.1                 | 4                                | 7<br>10                  | mV<br>mV             |

| V <sub>SENSE(4%)</sub>  | Current Sense Voltage 4% of Full Scale   | $VC_{SRC} = VC_{SNK} = 0.2V$                                                                                                                                                                                                                                                                     |             | 15                         | 20                               | 25                       | mV                   |

| V <sub>SENSE(10%)</sub> | Current Sense Voltage 10% of Full Scale  | $VC_{SRC} = VC_{SNK} = 0.5V$                                                                                                                                                                                                                                                                     | •           | 45                         | 50                               | 55                       | mV                   |

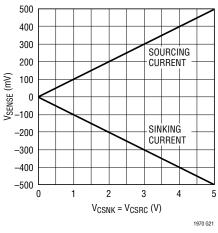

| V <sub>SENSE(FS)</sub>  | Current Sense Voltage 100% of Full Scale | VC <sub>SRC</sub> = VC <sub>SNK</sub> = 5V                                                                                                                                                                                                                                                       | •           | 490<br>480                 | 500<br>500                       | 510<br>520               | mV<br>mV             |

| I <sub>BI</sub>         | Current Limit Control Input Bias Current | VC <sub>SRC</sub> , VC <sub>SNK</sub> Pins                                                                                                                                                                                                                                                       | ٠           | -1                         | -0.2                             | 0.1                      | μA                   |

| I <sub>SENSE</sub> -    | SENSE <sup>-</sup> Input Current         | 0V < (VC <sub>SRC</sub> , VC <sub>SNK</sub> ) < 5V                                                                                                                                                                                                                                               | •           | -500                       |                                  | 500                      | nA                   |

| I <sub>FILTER</sub>     | FILTER Input Current                     | 0V < (VC <sub>SRC</sub> , VC <sub>SNK</sub> ) < 5V                                                                                                                                                                                                                                               | •           | -500                       |                                  | 500                      | nA                   |

| I <sub>SENSE</sub> +    | SENSE <sup>+</sup> Input Current         | $\label{eq:VC_SRC} \begin{array}{l} VC_{SRC} = VC_{SNK} = 0V \\ VC_{SRC} = 5V,  VC_{SNK} = 0V \\ VC_{SRC} = 0V,  VC_{SNK} = 5V \\ VC_{SRC} = VC_{SNK} = 5V \end{array}$                                                                                                                          | •<br>•<br>• | -500<br>200<br>-300<br>-25 | 250<br>250                       | 500<br>300<br>–200<br>25 | nA<br>nA<br>nA<br>nA |

|                         | Current Sense Change with Output Voltage | VC <sub>SRC</sub> = VC <sub>SNK</sub> = 5V, -12.5V < V <sub>OUT</sub> < 12.5V                                                                                                                                                                                                                    |             |                            | ±0.1                             |                          | %                    |

|                         | Current Sense Change with Supply Voltage | $ \begin{array}{l} VC_{SRC} = VC_{SNK} = 5V,  6V < (V_{CC},  V^{+}) < 18V \\ 2.5V < V^{+} < 18V,  V_{CC} = 18V \\ -18V < (V_{EE},  V^{-}) < -2.5V \\ -18V < V^{-} < -2.5V,  V_{EE} = -18V \end{array} $                                                                                          |             |                            | ±0.05<br>±0.01<br>±0.05<br>±0.01 |                          | %<br>%<br>%          |

### **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. See Test Circuit for standard test conditions. The • denotes the specifications which apply over the full operating

| SYMBOL                | PARAMETER                               | CONDITIONS                                                                                      |   | MIN | ТҮР  | MAX  | UNITS |

|-----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|---|-----|------|------|-------|

|                       | Current Sense Bandwidth                 |                                                                                                 |   |     | 2    |      | MHz   |

| R <sub>CSF</sub>      | Resistance FILTER to SENSE <sup>-</sup> |                                                                                                 |   | 750 | 1000 | 1250 | Ω     |

| Logic I/O C           | Characteristics                         |                                                                                                 |   |     |      |      |       |

|                       | Logic Output Leakage ISRC, ISNK, TSD    | V = 15V                                                                                         | • |     |      | 1    | μA    |

|                       | Logic Low Output Level                  | I = 5mA (Note 6)                                                                                | ٠ |     | 0.2  | 0.4  | V     |

|                       | Logic Output Current Limit              |                                                                                                 |   |     | 25   |      | mA    |

| V <sub>ENABLE</sub>   | Enable Logic Threshold                  |                                                                                                 | ٠ | 0.8 | 1.9  | 2.5  | V     |

| IENABLE               | Enable Pin Bias Current                 |                                                                                                 | ٠ | -1  |      | 1    | μA    |

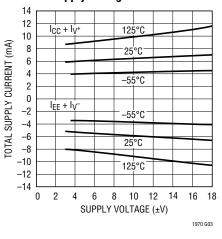

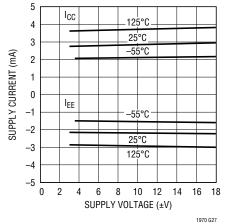

| I <sub>SUPPLY</sub>   | Total Supply Current                    | V <sub>CC</sub> , V <sup>+</sup> and V <sup>-</sup> , V <sub>EE</sub> Connected                 |   |     | 7    | 13   | mA    |

| I <sub>CC</sub>       | V <sub>CC</sub> Supply Current          | V <sub>CC</sub> , V <sup>+</sup> and V <sup>-</sup> , V <sub>EE</sub> Separate                  | ٠ |     | 3    | 7    | mA    |

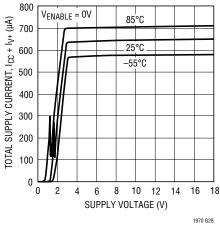

| I <sub>CC(STBY)</sub> | Supply Current Disabled                 | $V_{CC}$ , V <sup>+</sup> and V <sup>-</sup> , V <sub>EE</sub> Connected, $V_{ENABLE} \le 0.8V$ | ٠ |     | 0.6  | 1.5  | mA    |

| t <sub>ON</sub>       | Turn-On Delay                           | (Note 7)                                                                                        |   |     | 10   |      | μs    |

| t <sub>OFF</sub>      | Turn-Off Delay                          | (Note 7)                                                                                        |   |     | 10   |      | μs    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LT1970C is guaranteed functional over the operating temperature range of -40°C and 85°C.

**Note 3:** The LT1970C is guaranteed to meet specified performance from 0°C to 70°C. The LT1970C is designed, characterized and expected to meet specified performance from -40°C to 85°C but is not tested or QA sampled at these temperatures. The LT1970I is guaranteed to meet specified performance from -40°C to 85°C.

Note 4: This parameter is not 100% tested.

Note 5: Full power bandwidth is calculated from slew rate measurements: FPBW = SR/( $2 \cdot \pi \cdot V_P$ )

Note 6: The logic low output level of pin TSD is guaranteed by correlating the output level of pin ISRC and pin ISNK over temperature.

Note 7: Turn-on and turn-off delay are measured from VENABLE crossing 1.6V to the OUT pin at 90% of normal output voltage.

Note 8: Thermal resistance varies depending upon the amount of PC board metal attached to the device. If the maximum dissipation of the package is exceeded, the device will go into thermal shutdown and be protected.

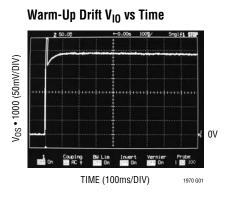

# TYPICAL PERFORMANCE CHARACTERISTICS

### **Total Supply Current** vs Supply Voltage

### **TYPICAL PERFORMANCE CHARACTERISTICS**

<sup>1970</sup> G12

SUPPLY VOLTAGE (±V)

1970fe

FREQUENCY (Hz)

1970 G10

FREQUENCY (Hz)

1970 G11

# **TYPICAL PERFORMANCE CHARACTERISTICS**

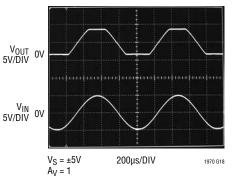

Large-Signal Response,  $A_V = -1$

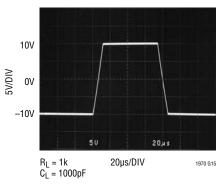

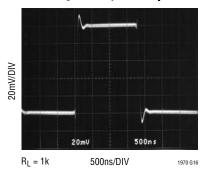

Small-Signal Response,  $A_V = 1$

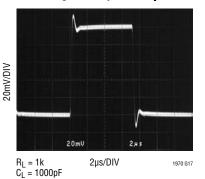

Small-Signal Response,  $A_V = -1$

**Output Overdriven**

### Full Range Current Sense Transfer Curve

For more information www.linear.com/LT1970

6

### **TYPICAL PERFORMANCE CHARACTERISTICS**

**Safe Operating Area**

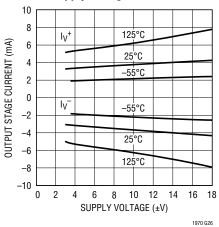

Output Stage Quiescent Current vs Supply Voltage

# PIN FUNCTIONS

**V<sub>EE</sub> (Pins 1, 10, 11, 20, Package Base):** Minus Supply Voltage. V<sub>EE</sub> connects to the substrate of the integrated circuit die, and therefore must always be the most negative voltage applied to the part. Decouple V<sub>EE</sub> to ground with a low ESR capacitor. V<sub>EE</sub> may be a negative voltage or it may equal ground potential. Any or all of the V<sub>EE</sub> pins may be used. Unused V<sub>EE</sub> pins must remain open.

**V**<sup>-</sup> (**Pin 2**): Output Stage Negative Supply. V<sup>-</sup> may equal  $V_{EE}$  or may be smaller in magnitude. Only output stage current flows out of V<sup>-</sup>, all other current flows out of V<sub>EE</sub>. V<sup>-</sup> may be used to drive the base/gate of an external power device to boost the amplifier's output current to levels above the rated 500mA of the on-chip output devices. Unless used to drive boost transistors, V<sup>-</sup> should be decoupled to ground with a low ESR capacitor.

**OUT (Pin 3):** Amplifier Output. The OUT pin provides the force function as part of a Kelvin sensed load connection. OUT is normally connected directly to an external load current sense resistor and the SENSE<sup>+</sup> pin. Amplifier feedback is directly connected to the load and the other end of the current sense resistor. The load connection is also wired directly to the SENSE<sup>-</sup> pin to monitor the load current.

The OUT pin is current limited to  $\pm 800$ mA typical. This current limit protects the output transistor in the event that connections to the external sense resistor are opened or shorted which disables the precision current limit function.

**SENSE<sup>+</sup>** (Pin 4): Positive Current Sense Pin. This lead is normally connected to the driven end of the external sense resistor. Sourcing current limit operation is activated when the voltage  $V_{SENSE}$  ( $V_{SENSE+} - V_{SENSE-}$ ) equals 1/10 of the programming control voltage at VC<sub>SRC</sub> (Pin 13). Sinking current limit operation is activated when the voltage  $V_{SENSE}$  equals -1/10 of the programming control voltage at VC<sub>SNK</sub> (Pin 12). **FILTER (Pin 5):** Current Sense Filter Pin. This pin is normally not used and should be left open or shorted to the SENSE<sup>-</sup> pin. The FILTER pin can be used to adapt the response time of the current sense amplifiers with a 1nF to 100nF capacitor connected to the SENSE<sup>-</sup> input. An internal 1k resistor sets the filter time constant.

**SENSE<sup>-</sup> (Pin 6):** Negative Current Sense Pin. This pin is normally connected to the load end of the external sense resistor. Sourcing current limit operation is activated when the voltage  $V_{SENSE}$  ( $V_{SENSE+} - V_{SENSE-}$ ) equals 1/10 of the programming control voltage at VC<sub>SRC</sub> (Pin 13). Sinking current limit operation is activated when the voltage  $V_{SENSE}$  equals -1/10 of the programming control voltage at VC<sub>SNK</sub> (Pin 12).

$V_{CC}$  (Pin 7): Positive Supply Voltage. All circuitry except the output transistors draw power from V<sub>CC</sub>. Total supply voltage from V<sub>CC</sub> to V<sub>EE</sub> must be between 3.5V and 36V. V<sub>CC</sub> must always be greater than or equal to V<sup>+</sup>. V<sub>CC</sub> should always be decoupled to ground with a low ESR capacitor.

**–IN (Pin 8):** Inverting Input of Amplifier. –IN may be any voltage from  $V_{EE} - 0.3V$  to  $V_{EE} + 36V$ . –IN and +IN remain high impedance at all times to prevent current flow into the inputs when current limit mode is active. Care must be taken to insure that –IN or +IN can never go to a voltage below  $V_{EE} - 0.3V$  even during transient conditions or damage to the circuit may result. A Schottky diode from  $V_{EE}$  to –IN can provide clamping if other elements in the circuit can allow –IN to go below  $V_{EE}$ .

**+IN (Pin 9):** Noninverting Input of Amplifier. +IN may be any voltage from  $V_{EE} - 0.3V$  to  $V_{EE} + 36V$ . –IN and +IN remain high impedance at all times to prevent current flow into the inputs when current limit mode is active. Care must be taken to insure that –IN or +IN can never go to a voltage below  $V_{EE} - 0.3V$  even during transient conditions or damage to the circuit may result. A Schottky diode from  $V_{EE}$  to +IN can provide clamping if other elements in the circuit can allow +IN to go below  $V_{EE}$ .

### PIN FUNCTIONS

**VC**<sub>SNK</sub> (Pin 12): Sink Current Limit Control Voltage Input. The current sink limit amplifier will activate when the sense voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> equals  $-1.0 \cdot V_{VCSNK}/10$ . VC<sub>SNK</sub> may be set between V<sub>COMMON</sub> and V<sub>COMMON</sub> + 6V. The transfer function between VC<sub>SNK</sub> and V<sub>SENSE</sub> is linear except for very small input voltages at VC<sub>SNK</sub> < 60mV. V<sub>SENSE</sub> limits at a minimum set point of 4mV typical to insure that the sink and source limit amplifiers do not try to operate simultaneously. To force zero output current, the ENABLE pin can be taken low.

**VC<sub>SRC</sub> (Pin 13):** Source Current Limit Control Voltage Input. The current source limit amplifier will activate when the sense voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> equals V<sub>VCSRC</sub>/10. VC<sub>SRC</sub> may be set between V<sub>COMMON</sub> and V<sub>COMMON</sub> + 6V. The transfer function between VC<sub>SRC</sub> and V<sub>SENSE</sub> is linear except for very small input voltages at VC<sub>SRC</sub> < 60mV. V<sub>SENSE</sub> limits at a minimum set point of 4mV typical to insure that the sink and source limit amplifiers do not try to operate simultaneously. To force zero output current, the ENABLE pin can be taken low.

**COMMON (Pin 14):** Control and ENABLE inputs and flag outputs are referenced to the COMMON pin. COMMON may be at any potential between  $V_{EE}$  and  $V_{CC}$  – 3V. In typical applications, COMMON is connected to ground.

**ENABLE (Pin 15):** ENABLE Digital Input Control. When taken low this TTL-level digital input turns off the amplifier output and drops supply current to less than 1mA. Use the ENABLE pin to force zero output current. Setting  $VC_{SNK} = VC_{SRC} = 0V$  allows  $I_{OUT} = \pm 4mV/R_{SENSE}$  to flow in or out of  $V_{OUT}$ .

**ISRC** (Pin 16): Sourcing Current Limit Digital Output Flag. ISRC is an open collector digital output. ISRC pulls low whenever the sourcing current limit amplifier assumes control of the output. This pin can sink up to 10mA of current. The current limit flag is off when the source current limit is not active.  $\overline{ISRC}$ ,  $\overline{ISNK}$  and  $\overline{TSD}$  may be wired "OR" together if desired.  $\overline{ISRC}$  may be left open if this function is not monitored.

**ISNK** (Pin 17): Sinking Current Limit Digital Output Flag. ISNK is an open collector digital output. ISNK pulls low whenever the sinking current limit amplifier assumes control of the output. This pin can sink up to 10mA of current. The current limit flag is off when the source current limit is not active. ISRC, ISNK and TSD may be wired "OR" together if desired. ISNK may be left open if this function is not monitored.

**TSD** (Pin 18): Thermal Shutdown Digital Output Flag. TSD is an open collector digital output. TSD pulls low whenever the internal thermal shutdown circuit activates, typically at a die temperature of 160°C. This pin can sink up to 10mA of output current. The TSD flag is off when the die temperature is within normal operating temperatures. ISRC, ISNK and TSD may be wired "OR" together if desired. TSD may be left open if this function is not monitored. Thermal shutdown activation should prompt the user to evaluate electrical loading or thermal environmental conditions.

**V**<sup>+</sup> (**Pin 19**): Output Stage Positive Supply. V<sup>+</sup> may equal V<sub>CC</sub> or may be smaller in magnitude. Only output stage current flows through V<sup>+</sup>, all other current flows into V<sub>CC</sub>. V<sup>+</sup> may be used to drive the base/gate of an external power device to boost the amplifier's output current to levels above the rated 500mA of the on-chip output devices. Unless used to drive boost transistors, V<sup>+</sup> should be decoupled to ground with a low ESR capacitor.

**Package Base:** The exposed backside of the package is electrically connected to the  $V_{EE}$  pins on the IC die. The package base should be soldered to a heat spreading pad on the PC board that is electrically connected to  $V_{EE}$ .

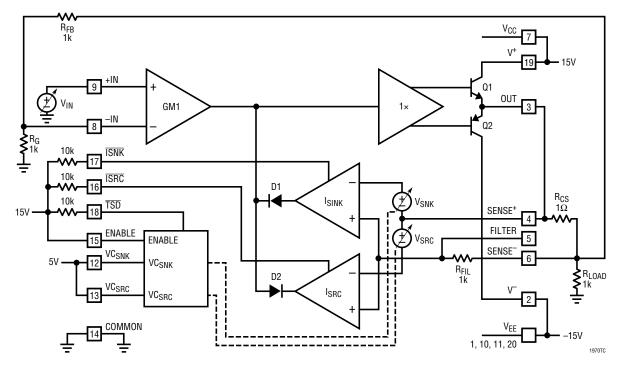

# **BLOCK DIAGRAM AND TEST CIRCUIT**

# **APPLICATIONS INFORMATION**

The LT1970 power op amp with precision controllable current limit is a flexible voltage and current source module. The drawing on the front page of this data sheet is representative of the basic application of the circuit, however many alternate uses are possible with proper understanding of the sub circuit capabilities.

### **CIRCUIT DESCRIPTION**

### Main Operational Amplifier

Sub circuit block GM1, the 1X unity-gain current buffer and output transistors Q1 and Q2 form a standard operational amplifier. This amplifier has  $\pm$  500mA current output capability and a 3.6MHz gain bandwidth product. Most applications of the LT1970 will use this op amp in the main signal path. All conventional op amp circuit configurations are supported. Inverting, noninverting, filter, summation or nonlinear circuits may be implemented in a conventional manner. The output stage includes current limiting at  $\pm$ 800mA to protect against fault conditions. The input stage has high differential breakdown of 36V minimum between –IN and +IN. No current will flow at the inputs when differential input voltage is present. This feature is important when the precision current sense amplifiers " $I_{SINK}$ " and " $I_{SRC}$ " become active.

### **Current Limit Amplifiers**

Amplifier stages "ISINK" and "ISRC" are very high transconductance amplifier stages with independently controlled offset voltages. These amplifiers monitor the voltage between input pins SENSE<sup>+</sup> and SENSE<sup>-</sup> which usually sense the voltage across a small external current sense resistor. The transconductance amplifiers outputs connect to the same high impedance node as the main input stage GM1 amplifier. Small voltage differences between SENSE<sup>+</sup> and SENSE<sup>-</sup>, smaller than the user set VC<sub>SNK</sub>/10 and VC<sub>SRC</sub>/10 in magnitude, cause the current limit amplifiers to decouple from the signal path. This is functionally indicated by diodes D1 and D2 in the Block Diagram. When the voltage V<sub>SENSE</sub> increases in magnitude sufficient to equal or overcome one of the offset voltages VC<sub>SNK</sub>/10 or VC<sub>SRC</sub>/10, the appropriate current limit amplifier becomes active and because of 1970fe

its very high transconductance, takes control from the input stage, GM1. The output current is regulated to a value of  $I_{OUT} = V_{SENSE}/R_{SENSE} = (VC_{SRC} \text{ or } VC_{SNK})/(10 \bullet R_{SENSE})$ . The time required for the current limit amplifiers to take control of the output is typically 4µs.

Linear operation of the current limit sense amplifier occurs with the inputs SENSE<sup>+</sup> and SENSE<sup>-</sup> ranging between  $V_{CC}$ – 1.5V and  $V_{EE}$  + 1.5V. Most applications will connect pins SENSE<sup>+</sup> and OUT together, with the load on the opposite side of the external sense resistor and pin SENSE<sup>-</sup>. Feedback to the inverting input of GM1 should be connected from SENSE<sup>-</sup> to – IN. Ground side sensing of load current may be employed by connecting the load between pins OUT and SENSE<sup>+</sup>. Pin SENSE<sup>-</sup> would be connected to ground in this instance. Load current would be regulated in exactly the same way as the conventional connection. However, voltage mode accuracy would be degraded in this case due to the voltage across R<sub>SENSE</sub>.

Creative applications are possible where pins SENSE<sup>+</sup> and SENSE<sup>-</sup> monitor a parameter other than load current. The operating principle that at most one of the current limit stages may be active at one time, and that when active, the current limit stages take control of the output from GM1, can be used for many different signals.

### **Current Limit Threshold Control Buffers**

Input pins VC<sub>SNK</sub> and VC<sub>SRC</sub> are used to set the response thresholds of current limit amplifiers "I<sub>SINK</sub>" and "I<sub>SRC</sub>". Each of these inputs may be independently driven by a voltage of 0V to 5V above the COMMON reference pin. The 0V to 5V input voltage is attenuated by a factor of 10 and applied as an offset to the appropriate current limit amplifier. AC signals may be applied to these pins. The AC bandwidth from a V<sub>C</sub> pin to the output is typically 2MHz. For proper operation of the LT1970, these control inputs cannot be left floating.

For low  $V_{CC}$  supply applications it is important to keep the maximum input control voltages,  $VC_{SRC}$  and  $VC_{SNK}$ , at least 2.5V below the  $V_{CC}$  potential. This ensures linear control of the current limit threshold. Reducing the current limit sense resistor value allows high output current from a smaller control voltage which may be necessary if the  $V_{CC}$  supply is only 5V. The transfer function from  $V_C$  to the associated  $V_{OS}$  is linear from about 0.1V to 5V in, or 10mV to 500mV at the current limit amplifier inputs. An intentional nonlinearity is built into the transfer functions at low levels. This nonlinearity insures that both the sink and source limit amplifiers cannot become active simultaneously. Simultaneous activation of the limit amplifiers could result in uncontrolled outputs. As shown in the Typical Performance Characteristics curves, the control inputs have a "hockey stick" shape, to keep the minimum limit threshold at 4mV for each limit amplifier.

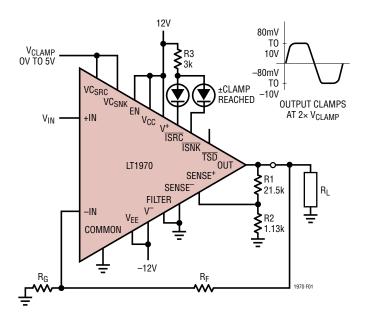

Figure 1 illustrates an interesting use of the current sense input pins. Here the current limit control amplifiers are used to produce a symmetrically limited output voltage swing. Instead of monitoring the output current, the output voltage is divided down by a factor of 20 and applied to the SENSE<sup>+</sup> input, with the SENSE<sup>-</sup> input grounded. When the threshold voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> (V<sub>CLAMP</sub>/10) is reached, the current limit stage takes control of the output and clamps it a level of  $\pm 2 \cdot V_{CLAMP}$ . With control inputs V<sub>CSRC</sub> and V<sub>CSNK</sub> tied together, a single polarity input voltage sets the same + and – output limit voltage for symmetrical limiting. In this circuit the output will current limit at the built-in fail-safe level of typically 800mA.

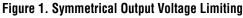

### **ENABLE Control**

The ENABLE input pin puts the LT1970 into a low supply current, high impedance output state. The ENABLE pin responds to TTL threshold levels with respect to the COMMON pin. Pulling the ENABLE pin low is the best way to force zero current at the output. Setting VC<sub>SNK</sub> = VC<sub>SRC</sub> = 0V allows the output current to remain as high as  $\pm 4$ mV/R<sub>SENSE</sub>.

In applications such as circuit testers (ATE), it may be preferable to apply a predetermined test voltage with a preset current limit to a test node simultaneously. The ENABLE pin can be used to provide this gating action as shown in Figure 2. While the LT1970 is disabled, the load is essentially floating and the input voltage and current limit control voltages can be set to produce the load test levels. Enabling the LT1970 then drives the load. The LT1970 enables and disables in just a few microseconds. The actual enable and disable times at the load are a function of the load reactance.

### **Operating Status Flags**

The LT1970 has three digital output indicators; TSD, ISRC and ISNK. These outputs are open collector drivers referred to the COMMON pin. The outputs have 36V capabilities and can sink in excess of 10mA. ISRC and ISNK indicate

activation of the associated current limit amplifier. The  $\overline{\text{TSD}}$  output indicates excessive die temperature has caused the circuit to enter thermal shutdown. The three digital outputs may be wire "OR'd" together, monitored individually or left open. These outputs do not affect circuit operation, but provide an indication of the present operational status of the chip.

For slow varying output signals, the assertion of a low level at the current limit output flags occurs when the current limit threshold is reached. For fast moving signals where the LT1970 output is moving at the slew limit, typically  $1.6V/\mu$ s, the flag assertion can be somewhat premature at typically 75% of the actual current limit value.

The operating status flags are designed to drive LEDs to provide a visual indication of current limit and thermal conditions. As such, the transition edges to and from the active low state are not particularly sharp and may exhibit some uncertainty. Adding some positive feedback to the current limit control inputs helps to sharpen these transitions.

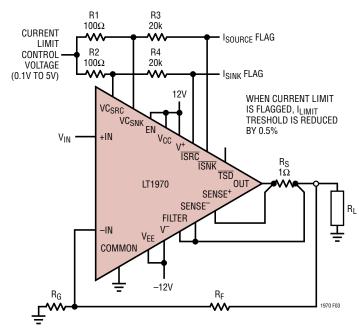

With the values shown in Figure 3, the current limit threshold is reduced by approximately 0.5% when either current limit status flag goes low. With sharp logic transitions, the status outputs can be used in a system control loop to

Figure 2. Using the ENABLE pin

take protective measures when a current limit condition is detected automatically.

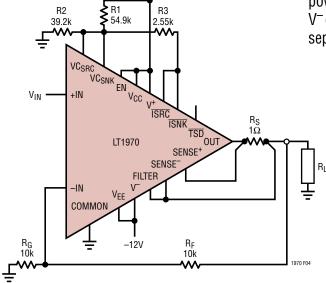

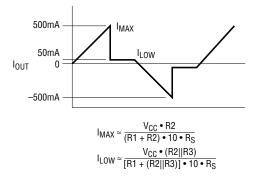

The current limit status flag can also be used to produce a dramatic change in the current limit value of the amplifier. Figure 4 illustrates a "snap-back" current limiting characteristic. In this circuit, a simple resistor network

Figure 3. Adding Positive Feedback to Sharpen the Transition **Edges of the Current Limit Status Flags**

R2

12V

R3

initially sets a high value of current limit (500mA). The circuit operates normally until the signal is large enough to enter current limit. When either current limit flag goes low, the current limit control voltage is reduced by a factor of 10. This then forces a low level of output current (50mA) until the signal is reduced in magnitude. When the load current drops below the lower level, the current limit is then restored to the higher value. This action is similar to a self resettable fuse that trips at dangerously high current levels and resets only when conditions are safe to do so.

### THERMAL MANAGEMENT

### Minimizing Power Dissipation

The LT1970 can operate with up to 36V total supply voltage with output currents up to  $\pm 500$  mA. The amount of power dissipated in the chip could approach 18W under worst-case conditions. This amount of power will cause die temperature to rise until the circuit enters thermal shutdown. While the thermal shutdown feature prevents damage to the circuit, normal operation is impaired. Thermal design of the LT1970 operating environment is essential to getting maximum utility from the circuit.

The first concern for thermal management is minimizing the heat which must be dissipated. The separate power pins V<sup>+</sup> and V<sup>-</sup> can be a great aid in minimizing on-chip power. The output pin can swing to within 1.0V of V<sup>+</sup> or V<sup>-</sup> even under maximum output current conditions. Using separate power supplies, or voltage regulators, to set V<sup>+</sup>

and V<sup>-</sup> to their minimum values for the required output swing will minimize power dissipation. The supplies V<sub>CC</sub> and V<sub>EE</sub> may also be reduced to a minimal value, but these supply pins do not carry high currents, and the power saving is much less. V<sub>CC</sub> and V<sub>EE</sub> must be greater than the maximum output swing by 1.5V or more.

When V<sup>-</sup> and V<sup>+</sup> are provided separately from V<sub>CC</sub> and V<sub>EE</sub>, care must be taken to insure that V<sup>-</sup> and V<sup>+</sup> are always less than or equal to the main supplies in magnitude. Protection Schottky diodes may be required to insure this in all cases, including power on/off transients.

Operation with reduced V<sup>+</sup> and V<sup>-</sup> supplies does not affect any performance parameters except maximum output swing. All DC accuracy and AC performance specifications guaranteed with  $V_{CC} = V^+$  and  $V_{EE} = V^-$  are still valid with the reduced output signal swing range.

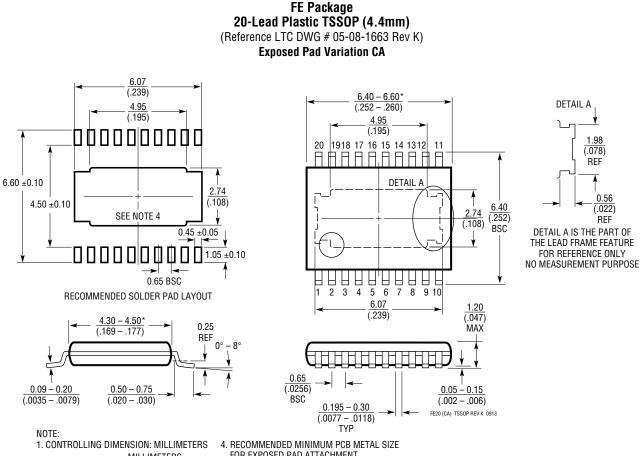

### Heat Sinking

The power dissipated in the LT1970 die must have a path to the environment. With 100°C/W thermal resistance in free air with no heat sink, the package power dissipation is limited to only 1W. The 20-pin TSSOP package with exposed copper underside is an efficient heat conductor if it is effectively mounted on a PC board. Thermal resistances as low as 40°C/W can be obtained by soldering the bottom of the package to a large copper pattern on the PC board. For operation at 85°C, this allows up to 1.625W of power to be dissipated on the LT1970. At 25°C operation, up to 3.125W of power dissipation can be achieved. The PC board heat spreading copper area must be connected to V<sub>EE</sub>.

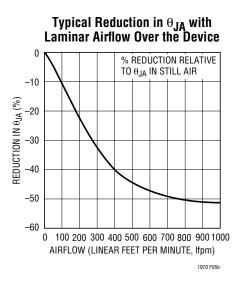

Figure 5 shows examples of PCB metal being used for heat spreading. These are provided as a reference for what might be expected when using different combinations of metal area on different layers of a PCB. These examples are with a 4-layer board using 1oz copper on each layer. The most effective layers for spreading heat are those closest to the LT1970 junction. Soldering the exposed thermal pad of the TSSOP package to the board produces a thermal resistance from junction-to-case of approximately 3°C/W.

As a minimum, the area directly beneath the package on all PCB layers can be used for heat spreading. However, limiting the area to that of the metal heat sinking pad is not very effective. Expanding the area on various layers significantly reduces the overall thermal resistance. The addition of vias (small 13 mil holes which fill during PCB plating) connecting all layers of metal also helps reduce the operating temperature of the LT1970. These are also shown in Figure 5.

It is important to note that the metal planes used for heat sinking are connecting electrically to  $V_{EE}$ . These planes must be isolated from any other power planes used in the PCB design.

Another effective way to control the power amplifier operating temperature is to use airflow over the board. Airflow can significantly reduce the total thermal resistance as also shown in Figure 5.

### **DRIVING REACTIVE LOADS**

### **Capacitive Loads**

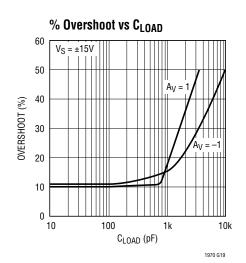

The LT1970 is much more tolerant of capacitive loading than most operational amplifiers. In a worst-case configuration as a voltage follower, the circuit is stable for capacitive loads less than 2.5nF. Higher gain configurations improve the  $C_{LOAD}$  handling. If very large capacitive loads are to be driven, a resistive decoupling of the amplifier from the capacitive load is effective in maintaining stability and reducing peaking. The current sense resistor, usually connected between the output pin and the load can serve as a part of the decoupling resistance.

### **Inductive Loads**

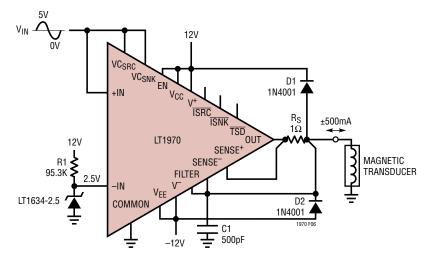

Load inductance is usually not a problem at the outputs of operational amplifiers, but the LT1970 can be used as a high output impedance current source. This condition may be the main operating mode, or when the circuit enters a protective current limit mode. Just as load capacitance degrades the phase margin of normal op amps, load inductance causes a peaking in the loop response of the feedback controlled current source. The inductive load may be caused by long lead lengths at the amplifier output. If the amplifier will be driving inductive loads or long lead lengths (greater than 4 inches) a 500pF capacitor from the SENSE<sup>-</sup> pin to the ground plane will cancel the inductive load and ensure stability.

| STILL AIR <sub>bja</sub> | PACKAGE | TOP LAYER | 2ND LAYER | 3RD LAYER | BOTTOM LAYER |

|--------------------------|---------|-----------|-----------|-----------|--------------|

| TSSOP<br>100°C/W         |         | • •       | • •       | • •       |              |

| TSSOP<br>50°C/W          |         |           | •••       | •••       |              |

| TSSOP<br>45°C/W          |         |           |           |           | 1970 F05a    |

Figure 5. Examples of PCB Metal Used for Heat Dissipation. Driver Package Mounted on Top Layer. Heat Sink Pad Soldered to Top Layer Metal. Metal Areas Drawn to Scale of Package Size

Figure 6 shows the LT1970 driving an inductive load with a controlled amount of current. This load is shown as a generic magnetic transducer, which could be used to create and modulate a magnetic field. Driving the current limit control inputs directly forces a current through the load that could range up to 2MHz in modulation. Biasing the input stage to the midpoint of the modulation signal allows symmetrical bidirectional current flow through the load. Clamp diodes are added to protect the LT1970 output from large inductive flyback potentials caused by rapid di/dt changes.

### Abrupt Load Short Protection

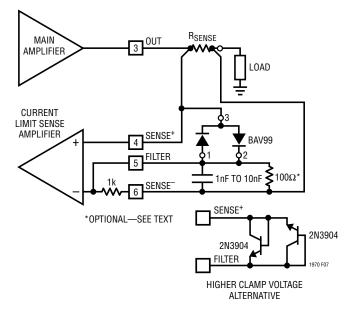

An abrupt short-circuit connection, often referred to as screwdriver or crowbar short, to ground or other supply potentials is the worst-case load condition for the LT1970. The current limit sense amplifier normally operates with an input voltage differential equal to the voltage across the sense resistor, which is only 500mV maximum in a typical application. During an abrupt load short to ground, the load end of the sense resistor is immediately connected to ground while the amplifier output remains at the normal output voltage. This can impose a large differential voltage to the sense amplifier inputs for a brief period. If this delta V can be greater than  $\pm 2V$ , it is beneficial to add clamps between the current limit sense amplifier inputs. These clamps ensure a smooth transition from the main amplifier control to the current limit amplifier control under all load short conditions that may arise.

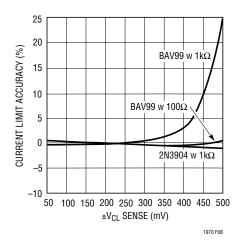

Figure 7 shows the connection of these back-to-back clamp diodes between the FILTER pin and the SENSE<sup>+</sup> pin. With this connection, the internal 1k resistor between the SENSE<sup>-</sup> pin and the FILTER pin limits the diode current. The BAV99 diodes are small SOT-23 packaged general purpose silicon diodes. The maximum current limit sense voltage is now the diode voltage drop, determined by the voltage across the sense resistor and the 1k internal resistor. As the diode begins to conduct current, with a voltage drop of around 300mV, an error in the expected current limit level at the high end of the control becomes apparent, as

Figure 7. Adding Protection for Abrupt Load Shorts

Figure 6. Current Modulation of a Magnetic Transducer

$V_{DIODE}$  is less than the voltage across  $R_{SENSE}$ . Adding an optional external 100 $\Omega$  resistor in parallel with the internal 1k resistor forces the diode voltage closer to the sensed current limit voltage and reduces the current limit error.

Alternatively, the base-emitter junctions of back-to-back 2N3904 NPN transistors can provide this clamping action. These diodes begin to conduct at a higher voltage level nearer to 600mV. With a 500mV maximum current limit threshold very little error will be noticed. Comparisons of typical current limit error with three ways of adding clamping protection are shown in Figure 8. Scaling the current sense resistor and the current limit control voltage down so that a 0V to 300mV current limit sense voltage range also prevents these accuracy errors caused by the abrupt-short clamping diodes.

Also shown in Figure 7 is a small filtering capacitor. This too provides an extra measure of control under abrupt load shorting conditions. A fast short-circuit makes apparent all parasitic interconnect lead inductances between the LT1970 and the load. These distributed parasitic elements can cause significant transient voltage spikes in the short time after the application or removal of a short circuit. These uncontrolled voltage transients could actually couple back to the current limit amplifier and cause polarity reversal from sourcing current limit to sinking or vice versa. This can act as positive feedback and cause

Figure 8. Current Limit Accuracy with Different Clamps

the current limit amplifier to go to the incorrect current limit direction and hang up. Adding a small filter capacitor between the SENSE<sup>-</sup> and FILTER pins, 1nF to 10nF is fairly typical, which charges through the clamp diodes forces the correct current limit polarity at the instant of the load short. This holds the amplifier in current limit until the capacitor discharges through the internal 1k resistor, eliminating transient induced behavior and creating a smooth transition into current limit.

### **Supply Bypassing**

The LT1970 can supply large currents from the power supplies to a load at frequencies up to 4MHz. Power supply impedance must be kept low enough to deliver these currents without causing supply rails to droop. Low ESR capacitors, such as  $0.1\mu$ F or  $1\mu$ F ceramics, located close to the pins are essential in all applications. When large, high speed transient currents are present additional capacitance may be needed near the chip. Check supply rails with a scope and if signal related ripple is seen on the supply rail, increase the decoupling capacitor as needed.

To ensure proper start-up biasing of the LT1970, it is recommended that the rate of change of the supply voltages at turn-on be limited to be no faster than  $6V/\mu s$ .

### **Application Circuit Ideas**

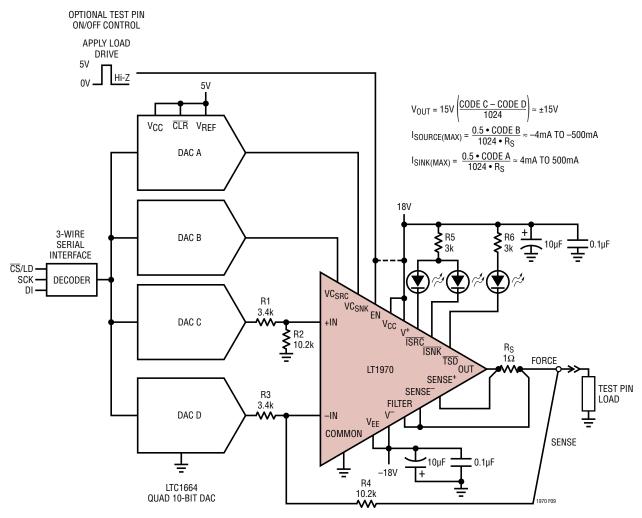

The digitally controlled analog pin driver is shown in Figure 9. All of the control signals are provided by an LTC®1664 quad, 10-bit DAC by way of a 3-wire serial interface. The LT1970 is configured as a simple difference amplifier with a gain of 3. This gain is required to produce  $\pm 15V$  from the 0V to 5V outputs from DACs C and D. To provide voltage headroom, the supplies for the LT1970 are set to the maximum value of  $\pm 18V$ . As  $\pm 18V$  is the absolute maximum rating of supply voltage for the LT1970, care must be taken to not allow the supply voltage to increase. DACs A and B separately control the sinking and sourcing current limit to the load over the range of  $\pm 4$ mA to  $\pm 500$ mA. An optional ON/OFF control for the pin driver using the ENABLE input is shown. If always enabled the ENABLE pin should be tied to V<sub>CC</sub>.

Figure 9. Digitally Controlled Analog Pin Driver

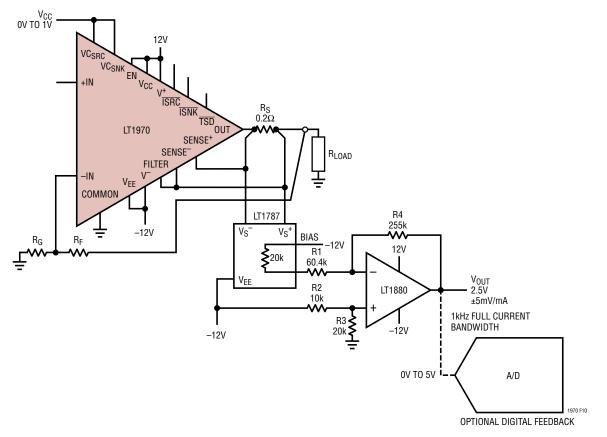

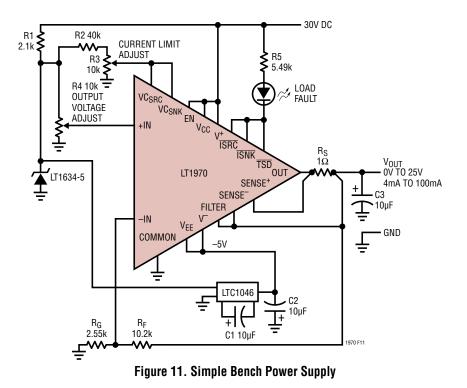

In some applications it may be necessary to know what the current into the load is at any time. Figure 10 shows an LT1787 high side current sense amplifier monitoring the current through sense resistor  $R_S$ . The LT1787 is biased from the V<sub>EE</sub> supply to accommodate the common mode input range of ±10V. The sense resistor is scaled down to provide a 100mV maximum differential signal to the current sense amplifier to preserve linearity. The LT1880 amplifier provides gain and level shifting to produce a 0V to 5V output signal (2.5V DC ±5mV/mA) with up to 1kHz full-scale bandwidth. An A/D converter could then digitize this instantaneous current reading to provide digital feedback from the circuit. The LT1970 is just as easy to use as a standard operational amplifier. Basic amplification of a precision reference voltage creates a very simple bench DC power supply as shown in Figure 11. The built-in power stage produces an adjustable OV to 25V at 4mA to 100mA of output current. Voltage and current adjustments are derived from the LT1634-5 5V reference. The output current capability is 500mA, but this supply is restricted to 100mA for power dissipation reasons. The worst-case output voltage for maximum power dissipated in the LT1970 output stage occurs if the output is shorted to ground or set to a voltage near zero. Limiting the output current to 100mA sets the maximum power dissipation to 3W. To allow the output to

Figure 10. Sensing Output Current

Figure 12. Dual Tracking Bench Power Supply

range all the way to 0V, an LTC1046 charge pump inverter is used to develop a -5V supply. This produces a negative rail for the LT1970 which has to sink only the quiescent current of the amplifier, typically 7mA.

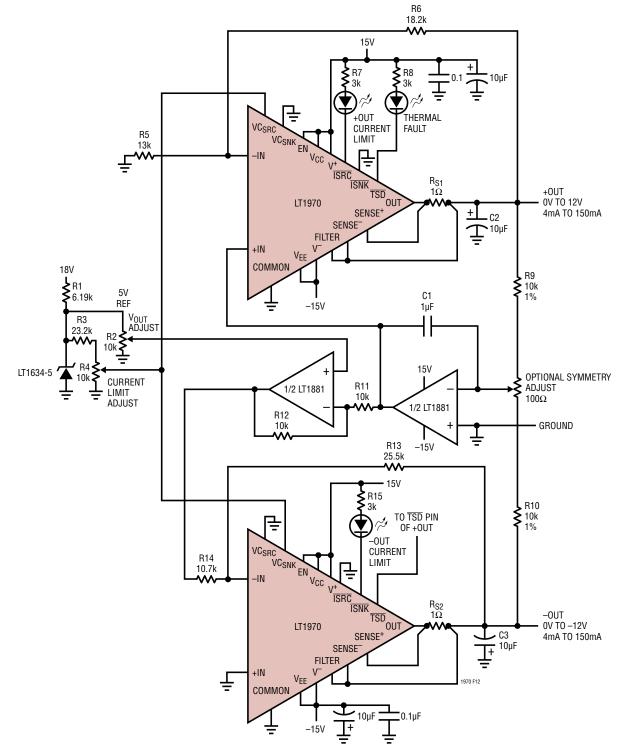

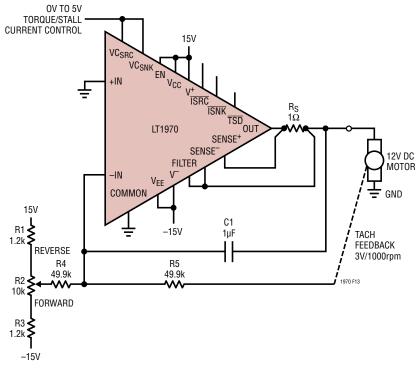

Using a second LT1970, a OV to  $\pm$ 12V dual tracking power supply is shown in Figure 12. The midpoint of two 10k resistors connected between the + and – outputs is held at OV by the LT1881 dual op amp servo feedback loop. To maintain OV, both outputs must be equal and opposite in polarity, thus they track each other. If one output reaches current limit and drops in voltage, the other output follows to maintain a symmetrical + and – voltage across a common load. Again, the output current limit is less than the full capability of the LT1970 due to thermal reasons. Separate current limit indicators are used on each LT1970 because one output only sources current and the other only sinks current. Both devices can share the same thermal shutdown indicator, as the output flags can be ORed together. Another simple linear power amplifier circuit is shown in Figure 13. This uses the LT1970 as a linear driver of a DC motor with speed control. The ability to source and sink the same amount of output current provides for bidirectional rotation of the motor. Speed control is managed by sensing the output of a tachometer built on to the motor. A typical feedback signal of 3V/1000rpm is compared with the desired speed-set input voltage. Because the LT1970 is unity-gain stable, it can be configured as an integrator to force whatever voltage across the motor as necessary to match the feedback speed signal with the set input signal.

Additionally, the current limit of the amplifier can be adjusted to control the torque and stall current of the motor. For reliability, a feedback scheme similar to that shown in Figure 4 can be used. Assuming that a stalled rotor will generate a current limit condition, the stall current limit can be significantly reduced to prevent excessive power dissipation in the motor windings.

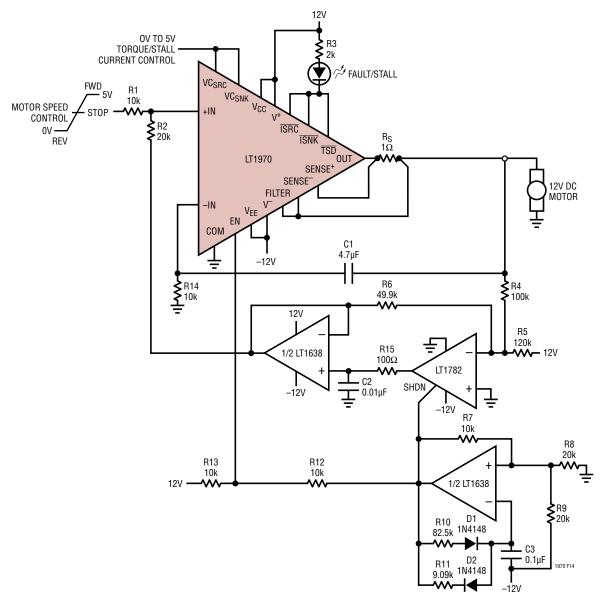

Figure 13. Simple Bidirectional DC Motor Speed Controller

For motor speed control without using a tachometer, the circuit in Figure 14 shows an approach. Using the enable feature of the LT1970, the drive to the motor can be removed periodically. With no drive applied, the spinning motor presents a back EMF voltage proportional to its rotational speed. The LT1782 is a tiny rail-to-rail amplifier with a shutdown pin. The amplifier is enabled during this interval to sample the back EMF voltage across the motor. This voltage is then buffered by one-half of an LT1638 dual op amp and used to provide the feedback to the LT1970 integrator. When re-enabled the LT1970 will adjust the drive to the motor until the speed feedback voltage, compared to the speed-set input voltage, settles the output to a fixed value. A OV to 5V signal for the motor speed input controls both rotational speed and direction.

The other half of the LT1638 is used as a simple pulse oscillator to control the periodic sampling of the motor back EMF.

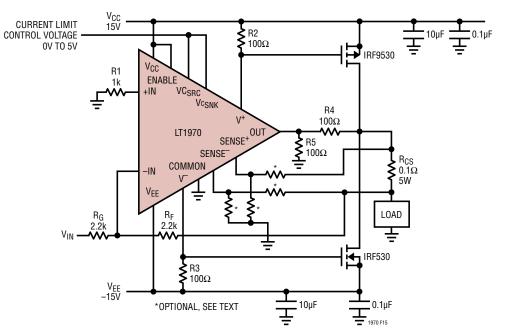

Figure 15 shows how easy it is to boost the output current of the LT1970. This  $\pm 5A$  power stage uses complementary

external N- and P-channel MOSFETs to provide the additional current. The output stage power supply inputs, V<sup>+</sup> and V<sup>-</sup>, are used to provide gate drive as needed. With higher output currents, the sense resistor R<sub>CS</sub>, is reduced in value to maintain the same easy current limit control.

This Class B power stage is intended for DC and low frequency, <1kHz, applications as crossover distortion becomes evident at higher frequencies.

Figure 15 shows some optional resistor dividers between the output connections and the current sense inputs. They are required only if the load of this power stage is removed or at a very low current level. Large power devices with no load on them can saturate and pull the output voltage very close to the power supply rails. The current sense amplifiers operate properly with input voltages at least 1V away from the V<sub>CC</sub> and V<sub>EE</sub> supply rails. In boosted current applications, it may be necessary to attenuate the maximum output voltage levels by 1V before connecting to the sense input pins. This only slightly deceases the current limit thresholds.

Figure 14. Simple Bidirectional DC Motor Speed Controller Without a Tachometer

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LT1970#packaging for the most recent package drawings.

2. DIMENSIONS ARE IN MILLIMETERS (INCHES)

3. DRAWING NOT TO SCALE

FOR EXPOSED PAD ATTACHMENT \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE

### **REVISION HISTORY** (Revision history begins at Rev C)

| REV | DATE  | DESCRIPTION                                    | PAGE NUMBER |

|-----|-------|------------------------------------------------|-------------|

| С   | 07/12 | Corrected Block Diagram                        | 10          |

|     |       | Changed supply voltage, added R6 in figure 14. | 23          |

| D   | 09/14 | Corrected Order Information table              | 2           |

|     |       | Corrected TSD pin description.                 | 9           |

| E   | 11/15 | Update Package Drawing                         | 24          |

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                            | COMMENTS                                 |

|-------------|----------------------------------------|------------------------------------------|

| LT1010      | Fast ±150mA Power Buffer               | 20MHz Bandwidth, 75V/µs Slew Rate        |

| LT1206      | 250mA/60MHz Current Feedback Amplifier | Shutdown Mode, Adjustable Supply Current |

| LT1210      | 1.1A/35MHz Current Feedback Amplifier  | Stable with C <sub>L</sub> = 10,000pF    |