### **DEVICE OVERVIEW**

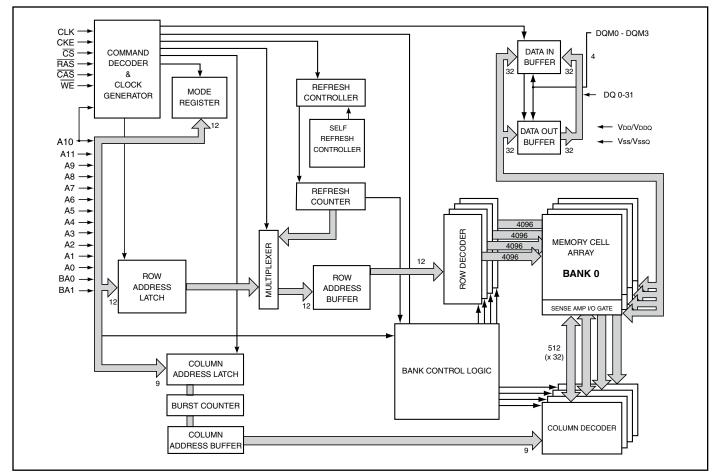

The 256Mb SDRAM is a high speed CMOS, dynamic random-access memory designed to operate in 3.3V VDD and 3.3V VDDQ memory systems containing 268,435,456 bits. Internally configured as a quad-bank DRAM with a synchronous interface. Each 67,108,864-bit bank is organized as 4,096 rows by 512 columns by 32 bits.

The 256Mb SDRAM includes an AUTO REFRESH MODE, and a power-saving, power-down mode. All signals are registered on the positive edge of the clock signal, CLK. All inputs and outputs are LVTTL compatible.

The 256Mb SDRAM has the ability to synchronously burst data at a high data rate with automatic column-address generation, the ability to interleave between internal banks to hide precharge time and the capability to randomly change column addresses on each clock cycle during burst access. A self-timed row precharge initiated at the end of the burst sequence is available with the AUTO PRECHARGE function enabled. Precharge one bank while accessing one of the other three banks will hide the precharge cycles and provide seamless, high-speed, random-access operation.

SDRAM read and write accesses are burst oriented starting at a selected location and continuing for a programmed number of locations in a programmed sequence. The registration of an ACTIVE command begins accesses, followed by a READ or WRITE command. The ACTIVE command in conjunction with address bits registered are used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A11 select the row). The READ or WRITE commands in conjunction with address bits registered are used to select the starting column location for the burst access.

Programmable READ or WRITE burst lengths consist of 1, 2, 4 and 8 locations or full page, with a burst terminate option.

## FUNCTIONAL BLOCK DIAGRAM (FOR 2Mx32x4 BANKS)

### PIN CONFIGURATIONS 86 pin TSOP - Type II for x32

|         |       | Vss        |

|---------|-------|------------|

|         |       | DQ15       |

|         | 3 84  | 🛛 VssQ     |

| DQ1 🚺   | 4 83  | DQ14       |

| DQ2     | 5 82  | DQ13       |

| VssQ 🚺  | 6 81  |            |

| DQ3 [   | 7 80  | DQ12       |

| DQ4     | 8 79  | DQ11       |

|         | 9 78  | VssQ       |

| DQ5 🔳   | 10 77 | DQ10       |

|         | 11 76 |            |

| VssQ    | 12 75 |            |

| DQ7     |       |            |

|         | 14 73 |            |

|         |       | T Vss      |

|         |       | DQM1       |

|         |       |            |

|         |       |            |

|         |       |            |

|         |       |            |

| A11 [[  |       | □ A9       |

| ВАО П   |       | A8         |

| BA1     |       | □ A7       |

| A10 [[  |       | □ A6       |

| AO [    |       | A5         |

| A1 [[   |       | A4         |

| A2 T    |       | аз<br>П Аз |

|         |       |            |

|         |       | Vss        |

|         |       |            |

| DQ16    |       |            |

| VssQ T  |       |            |

| DQ17    |       |            |

| DQ18    |       | DQ29       |

|         |       | VssQ       |

| DQ19    |       | DQ28       |

|         |       | DQ27       |

| VssQ [[ |       |            |

| DQ21    |       | DQ26       |

|         |       |            |

|         |       | VssQ       |

| DQ23    |       | DQ24       |

|         |       | Vss        |

|         |       |            |

|         |       |            |

### **PIN DESCRIPTIONS**

| A0-A11      | Row Address Input             |

|-------------|-------------------------------|

| A0-A8       | Column Address Input          |

| BA0, BA1    | Bank Select Address           |

| DQ0 to DQ31 | Data I/O                      |

| CLK         | System Clock Input            |

| CKE         | Clock Enable                  |

| CS          | Chip Select                   |

| RAS         | Row Address Strobe Command    |

| CAS         | Column Address Strobe Command |

|             |                               |

| WE        | Write Enable             |

|-----------|--------------------------|

| DQM0-DQM3 | x32 Input/Output Mask    |

| Vdd       | Power                    |

| Vss       | Ground                   |

| Vddq      | Power Supply for I/O Pin |

| Vssq      | Ground for I/O Pin       |

| NC        | No Connection            |

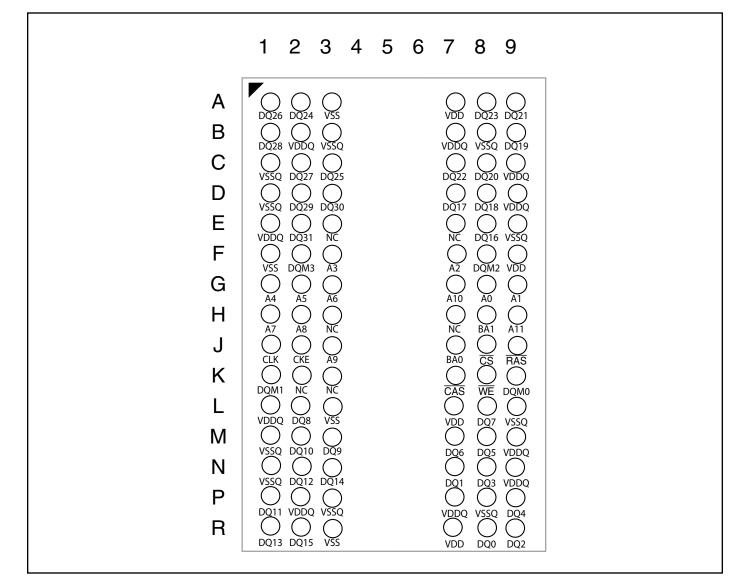

### **PIN CONFIGURATION**

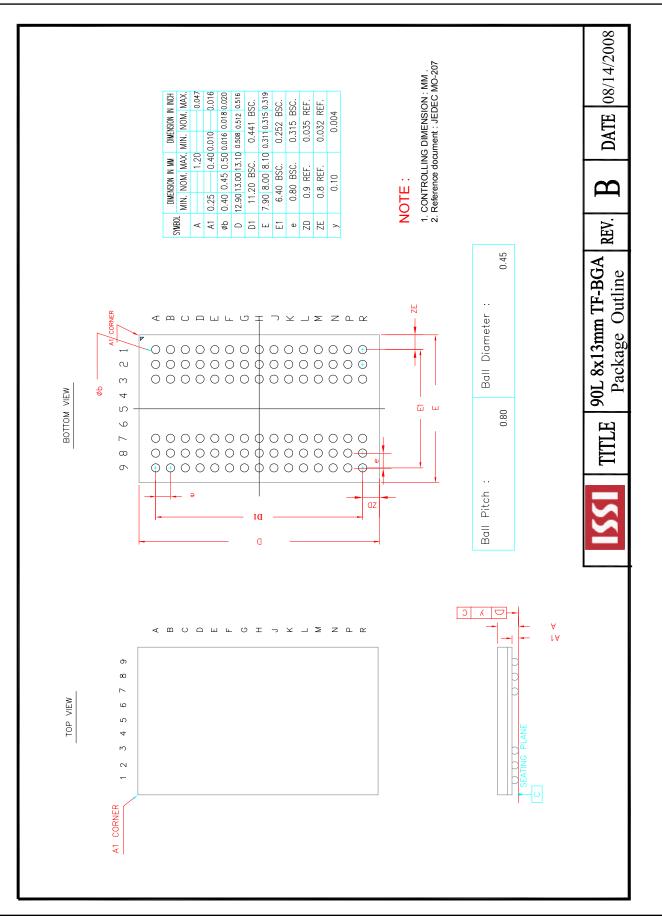

PACKAGE CODE: B 90 BALL TF-BGA (Top View) (8.00 mm x 13.00 mm Body, 0.8 mm Ball Pitch)

#### **PIN DESCRIPTIONS**

| A0-A11      | Row Address Input             |

|-------------|-------------------------------|

| A0-A8       | Column Address Input          |

| BA0, BA1    | Bank Select Address           |

| DQ0 to DQ31 | Data I/O                      |

| CLK         | System Clock Input            |

| CKE         | Clock Enable                  |

| CS          | Chip Select                   |

| RAS         | Row Address Strobe Command    |

| CAS         | Column Address Strobe Command |

|             |                               |

| WE        | Write Enable             |

|-----------|--------------------------|

| DQM0-DQM3 | x32 Input/Output Mask    |

| Vdd       | Power                    |

| Vss       | Ground                   |

| Vddq      | Power Supply for I/O Pin |

| Vssq      | Ground for I/O Pin       |

| NC        | No Connection            |

### **PIN FUNCTIONS**

| Symbol    | Туре             | Function (In Detail)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A11    | Input Pin        | Address Inputs: A0-A11 are sampled during the ACTIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |                  | command (row-address A0-A11) and READ/WRITE command (column address A0-A8), with A10 defining auto precharge) to select one location out of the memory array in the respective bank. A10 is sampled during a PRECHARGE command to determine if all banks are to be precharged (A10 HIGH) or bank selected by BA0, BA1 (LOW). The address inputs also provide the op-code during a LOAD MODE REGISTER command.                                                                                                |

| BA0, BA1  | Input Pin        | Bank Select Address: BA0 and BA1 defines which bank the ACTIVE, READ, WRITE or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                           |

| CAS       | Input Pin        | $\overline{CAS}$ , in conjunction with the $\overline{RAS}$ and $\overline{WE}$ , forms the device command. See the "Command Truth Table" for details on device commands.                                                                                                                                                                                                                                                                                                                                    |

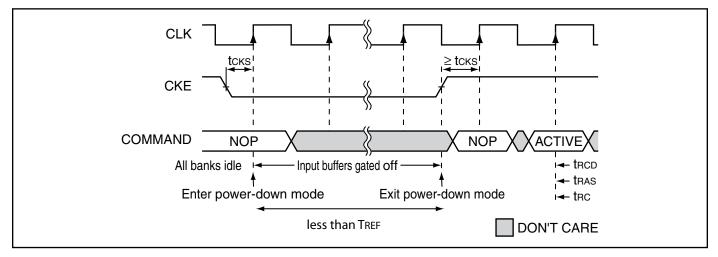

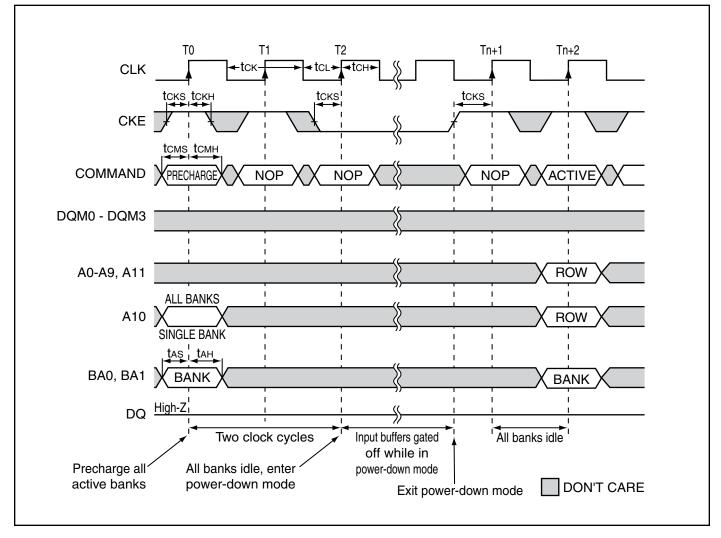

| CKE       | Input Pin        | The CKE input determines whether the CLK input is enabled. The next rising edge of the CLK signal will be valid when is CKE HIGH and invalid when LOW. When CKE is LOW, the device will be in either power-down mode, clock suspend mode, or self refresh mode. CKE is an asynchronous input.                                                                                                                                                                                                                |

| CLK       | Input Pin        | CLK is the master clock input for this device. Except for CKE, all inputs to this device are acquired in synchronization with the rising edge of this pin.                                                                                                                                                                                                                                                                                                                                                   |

| CS        | Input Pin        | The $\overline{\text{CS}}$ input determines whether command input is enabled within the device.<br>Command input is enabled when $\overline{\text{CS}}$ is LOW, and disabled with $\overline{\text{CS}}$ is HIGH. The device remains in the previous state when $\overline{\text{CS}}$ is HIGH.                                                                                                                                                                                                              |

| DQM0-DQM3 | Input Pin        | DQM0 - DQM3 control the four bytes of the I/O buffers (DQ0-DQ31). In read                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |                  | mode, DQMn control the output buffer. When DQMn is LOW, the corresponding buf-<br>fer byte is enabled, and when HIGH, disabled. The outputs go to the HIGH imped-<br>ance state whenDQMn is HIGH. This function corresponds to $\overline{OE}$ in conventional<br>DRAMs. In write mode, DQMn control the input buffer. When DQMn is LOW, the<br>corresponding buffer byte is enabled, and data can be written to the device. When<br>DQMn is HIGH, input data is masked and cannot be written to the device. |

| DQ0-DQ31  | Input/Output Pin | Data on the Data Bus is latched on these pins during Write commands, and buffered after Read commands.                                                                                                                                                                                                                                                                                                                                                                                                       |

| RAS       | Input Pin        | $\overline{\text{RAS}}$ , in conjunction with $\overline{\text{CAS}}$ and $\overline{\text{WE}}$ , forms the device command. See the "Command Truth Table" item for details on device commands.                                                                                                                                                                                                                                                                                                              |

| WE        | Input Pin        | $\overline{\text{WE}}$ , in conjunction with $\overline{\text{RAS}}$ and $\overline{\text{CAS}}$ , forms the device command. See the "Command Truth Table" item for details on device commands.                                                                                                                                                                                                                                                                                                              |

| VDDQ      | Power Supply Pin | VDDQ is the output buffer power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Vdd       | Power Supply Pin | VDD is the device internal power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Vssq      | Power Supply Pin | Vssa is the output buffer ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vss       | Power Supply Pin | Vss is the device internal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **GENERAL DESCRIPTION**

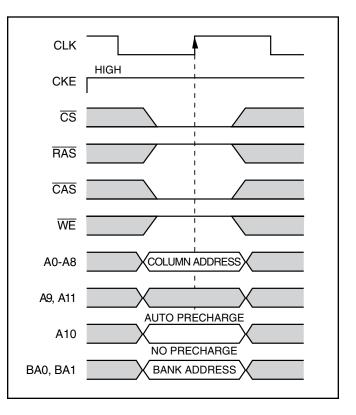

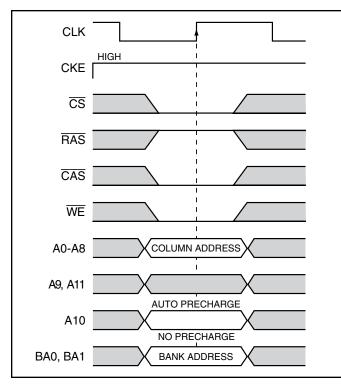

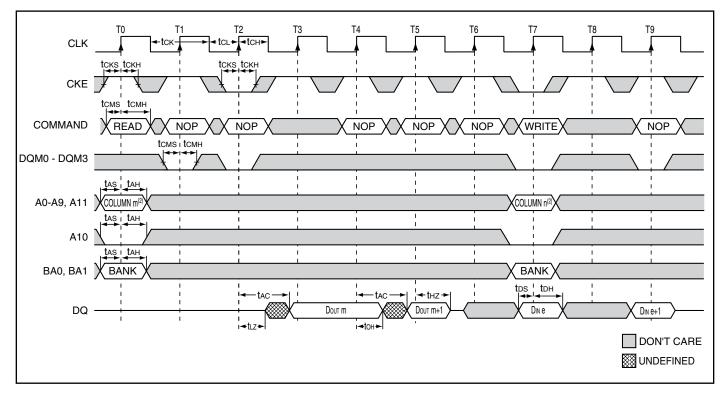

## READ

The READ command selects the bank from BA0, BA1 inputs and starts a burst read access to an active row. Inputs A0-A8 provides the starting column location. When A10 is HIGH, this command functions as an AUTO PRECHARGE command. When the auto precharge is selected, the row being accessed will be precharged at the end of the READ burst. The row will remain open for subsequent accesses when AUTO PRECHARGE is not selected. DQ's read data is subject to the logic level on the DQM inputs two clocks earlier. When a given DQM signal was registered HIGH, the corresponding DQ's will be High-Z two clocks later. DQ's will provide valid data when the DQM signal was registered LOW.

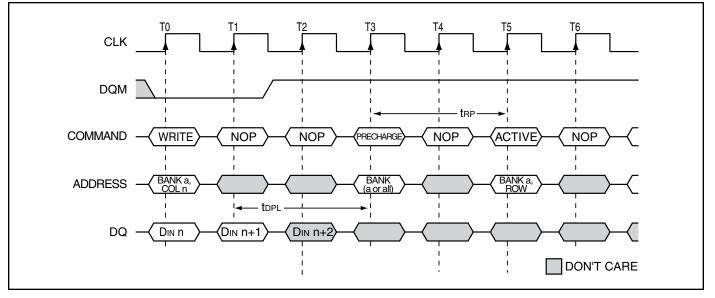

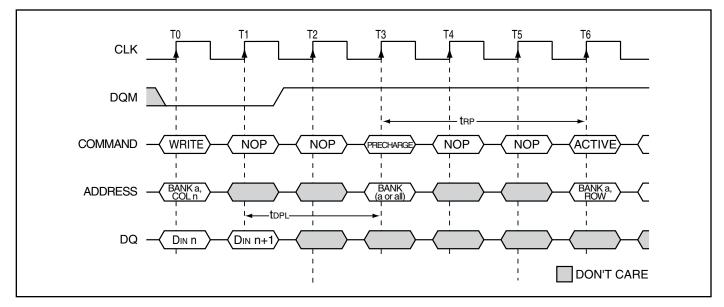

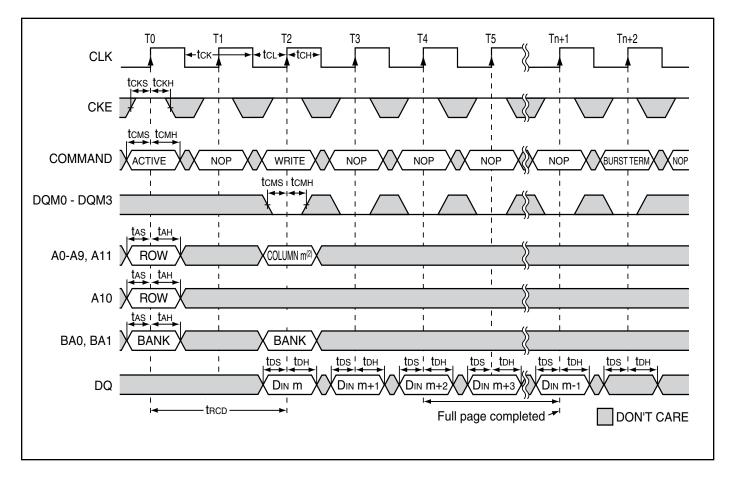

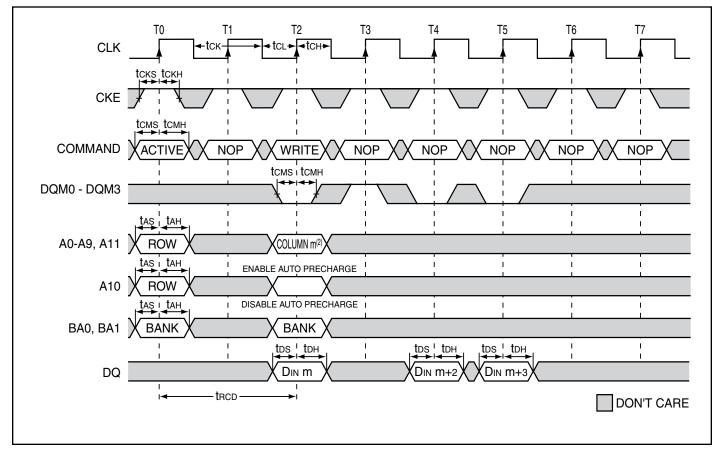

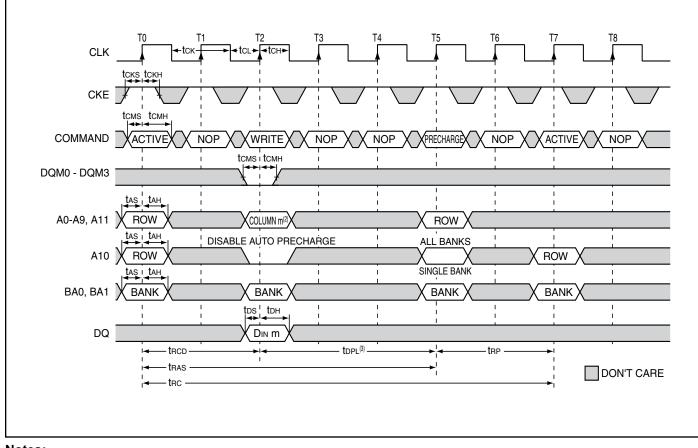

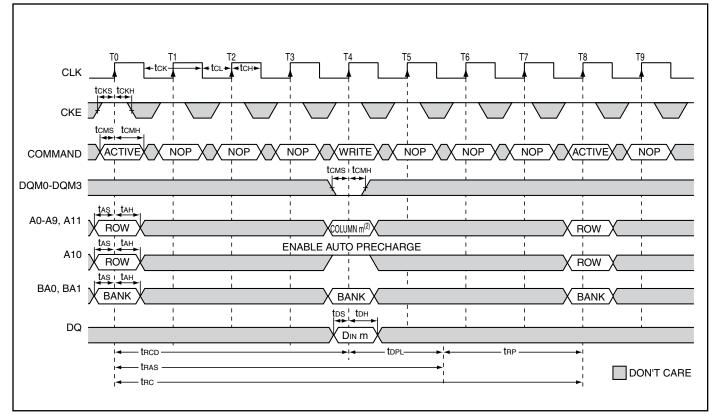

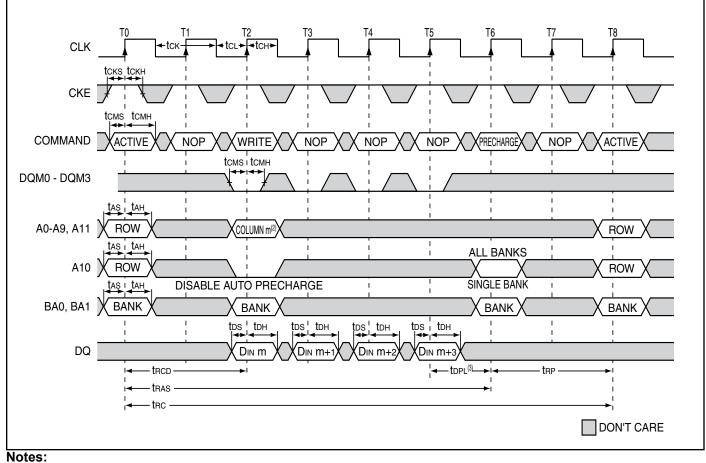

### WRITE

A burst write access to an active row is initiated with the WRITE command. BA0, BA1 inputs selects the bank, and the starting column location is provided by inputs A0-A8. Whether or not AUTO-PRECHARGE is used is determined by A10.

The row being accessed will be precharged at the end of the WRITE burst, if AUTO PRECHARGE is selected. If AUTO PRECHARGE is not selected, the row will remain open for subsequent accesses.

A memory array is written with corresponding input data on DQ's and DQM input logic level appearing at the same time. Data will be written to memory when DQM signal is LOW. When DQM is HIGH, the corresponding data inputs will be ignored, and a WRITE will not be executed to that byte/column location.

# PRECHARGE

The PRECHARGE command is used to deactivate the open row in a particular bank or the open row in all banks. BA0, BA1 can be used to select which bank is precharged or they are treated as "Don't Care". A10 determined whether one or all banks are precharged. After executing this command, the next command for the selected bank(s) is executed after passage of the period  $t_{RP}$  which is the period required for bank precharging. Once a bank has been precharged, it is in the idle state and must be activated prior to any READ or WRITE commands being issued to that bank.

# AUTO PRECHARGE

The AUTO PRECHARGE function ensures that the precharge is initiated at the earliest valid stage within a burst. This function allows for individual-bank precharge without requiring an explicit command. A10 to enable the AUTO PRECHARGE function in conjunction with a specific READ or WRITE command. For each individual READ or WRITE command, auto precharge is either enabled or disabled. AUTO PRECHARGE does not apply except in full-page burst mode. Upon completion of the READ or WRITE burst, a precharge of the bank/row that is addressed is automatically performed.

# **AUTO REFRESH COMMAND**

This command executes the AUTO REFRESH operation. The row address and bank to be refreshed are automatically generated during this operation. The stipulated period (tRc) is required for a single refresh operation, and no other commands can be executed during this period. This command is executed at least 4096 times for every TREF. During an AUTO REFRESH command, address bits are "Don't Care". This command corresponds to CBR Auto-refresh.

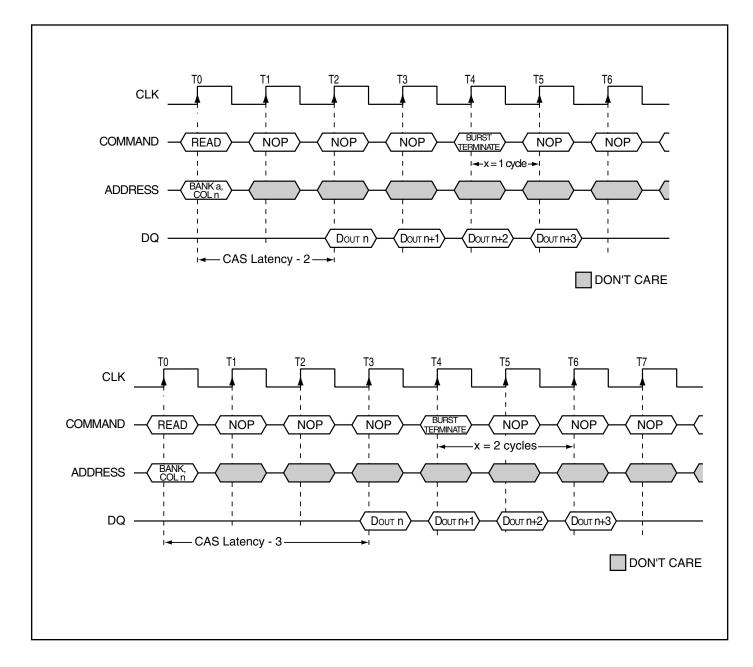

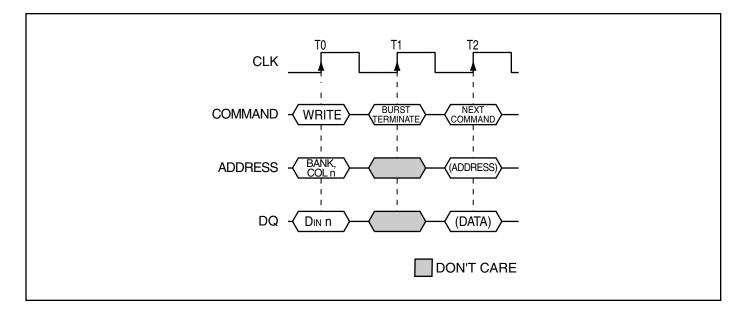

### **BURST TERMINATE**

The BURST TERMINATE command forcibly terminates the burst read and write operations by truncating either fixed-length or full-page bursts and the most recently registered READ or WRITE command prior to the BURST TERMINATE.

### **COMMAND INHIBIT**

COMMAND INHIBIT prevents new commands from being executed. Operations in progress are not affected, apart from whether the CLK signal is enabled

### **NO OPERATION**

When  $\overline{\text{CS}}$  is low, the NOP command prevents unwanted commands from being registered during idle or wait states.

# LOAD MODE REGISTER

During the LOAD MODE REGISTER command the mode register is loaded from A0-A11. This command can only be issued when all banks are idle.

### **ACTIVE COMMAND**

When the ACTIVE COMMAND is activated, BA0, BA1 inputs selects a bank to be accessed, and the address inputs on A0-A11 selects the row. Until a PRECHARGE command is issued to the bank, the row remains open for accesses.

### COMMAND TRUTH TABLE

|                             | СКЕ   |   |    |     |     |    |     |     |     | A11     |

|-----------------------------|-------|---|----|-----|-----|----|-----|-----|-----|---------|

| Function                    | n – 1 | n | CS | RAS | CAS | WE | BA1 | BA0 | A10 | A9 - A0 |

| Device deselect (DESL)      | Н     | × | Н  | ×   | ×   | ×  | ×   | ×   | ×   | ×       |

| No operation (NOP)          | Н     | × | L  | Н   | Н   | Н  | ×   | ×   | ×   | ×       |

| Burst stop (BST)            | Н     | × | L  | Н   | Н   | L  | ×   | ×   | ×   | ×       |

| Read                        | Н     | × | L  | Н   | L   | Н  | V   | V   | L   | V       |

| Read with auto precharge    | Н     | × | L  | Н   | L   | Н  | V   | V   | Н   | V       |

| Write                       | Н     | × | L  | Н   | L   | L  | V   | V   | L   | V       |

| Write with auto precharge   | Н     | × | L  | Н   | L   | L  | V   | V   | Н   | V       |

| Bank activate (ACT)         | Н     | × | L  | L   | Н   | Н  | V   | V   | V   | V       |

| Precharge select bank (PRE) | ) H   | × | L  | L   | Н   | L  | V   | V   | L   | ×       |

| Precharge all banks (PALL)  | Н     | × | L  | L   | Н   | L  | ×   | ×   | Н   | ×       |

| CBR Auto-Refresh (REF)      | Н     | Н | L  | L   | L   | Н  | ×   | ×   | ×   | ×       |

| Self-Refresh (SELF)         | Н     | L | L  | L   | L   | Н  | ×   | ×   | ×   | ×       |

| Mode register set (MRS)     | Н     | × | L  | L   | L   | L  | L   | L   | L   | V       |

Note:  $H=V_{IH}$ ,  $L=V_{IL} x=V_{IH}$  or  $V_{IL}$ , V = Valid Data.

#### DQM TRUTH TABLE

|     |   | DQM |       |

|-----|---|-----|-------|

| n-1 | n | U   | L     |

| Н   | x | L   | L     |

| Н   | × | Н   | Н     |

| Н   | × | L   | ×     |

| Н   | × | ×   | L     |

| Н   | × | Н   | ×     |

| Н   | × | ×   | Н     |

|     | H | H x | H x L |

Note:  $H=V_{IH}$ ,  $L=V_{IL} x=V_{IH}$  or  $V_{IL}$ , V = Valid Data.

### **CKE TRUTH TABLE**

|                                     | CKE   |   |    |     |     |    |         |

|-------------------------------------|-------|---|----|-----|-----|----|---------|

| Current State /Function             | n – 1 | n | CS | RAS | CAS | WE | Address |

| Activating Clock suspend mode entry | Н     | L | ×  | ×   | ×   | ×  | ×       |

| Any Clock suspend mode              | L     | L | ×  | ×   | ×   | ×  | ×       |

| Clock suspend mode exit             | L     | Н | ×  | ×   | ×   | ×  | ×       |

| Auto refresh command Idle (REF)     | Н     | Н | L  | L   | L   | Н  | ×       |

| Self refresh entry Idle (SELF)      | Н     | L | L  | L   | L   | Н  | ×       |

| Power down entry Idle               | Н     | L | ×  | ×   | ×   | ×  | ×       |

| Self refresh exit                   | L     | Н | L  | Н   | Н   | Н  | ×       |

|                                     | L     | Н | Н  | ×   | x   | ×  | ×       |

| Power down exit                     | Ĺ     | Н | ×  | ×   | ×   | ×  | ×       |

Note:  $H=V_{IH}$ ,  $L=V_{IL} \times V_{IH}$  or  $V_{IL}$ , V = Valid Data.

#### FUNCTIONAL TRUTH TABLE

| Current State | CS    | RAS | CAS | WE            | Address     | Command     | Action                                                      |

|---------------|-------|-----|-----|---------------|-------------|-------------|-------------------------------------------------------------|

| dle           | Н     | Х   | Х   | Х             | Х           | DESL        | Nop or Power Down <sup>(2)</sup>                            |

|               | L     | Н   | Н   | Н             | Х           | NOP         | Nop or Power Down <sup>(2)</sup>                            |

|               | L     | Н   | Н   | L             | Х           | BST         | Nop or Power Down                                           |

|               | L     | Н   | L   | Н             | BA, CA, A10 | READ/READA  | ILLEGAL <sup>(3)</sup>                                      |

|               | L     | Н   | L   | L             | A, CA, A10  | WRIT/ WRITA | ILLEGAL <sup>(3)</sup>                                      |

|               | L     | L   | Н   | Н             | BA, RA      | ACT         | Row activating                                              |

|               | L     | L   | Н   | L             | BA, A10     | PRE/PALL    | Nop                                                         |

|               | L     | L   | L   | Н             | Х           | REF/SELF    | Auto refresh or Self-refresh <sup>(4)</sup>                 |

|               | L     | L   | L   | L             | OC, BA1=L   | MRS         | Mode register set                                           |

| Row Active    | Н     | Х   | Х   | Х             | Х           | DESL        | Nop                                                         |

|               | _L    | Н   | Н   | Н             | Х           | NOP         | Nop                                                         |

|               | L     | Н   | Н   | L             | Х           | BST         | Nop                                                         |

|               | L     | Н   | L   | Н             | BA, CA, A10 | READ/READA  | Begin read <sup>(5)</sup>                                   |

|               | L     | Н   | L   | L             | BA, CA, A10 | WRIT/ WRITA | Begin write (5)                                             |

|               | L     | L   | Н   | Н             | BA, RA      | ACT         | ILLEGAL <sup>(3)</sup>                                      |

|               | L     | L   | Н   | L             | BA, A10     | PRE/PALL    | Precharge<br>Precharge all banks <sup>(6)</sup>             |

|               | L     | L   | L   | н             | Х           | REF/SELF    | ILLEGAL                                                     |

|               | L     | L   | L   | L             | OC, BA      | MRS         | ILLEGAL                                                     |

| Read          | Н     | Х   | Х   | х             | Х           | DESL        | Continue burst to end to Row active                         |

|               | L     | Н   | Н   | Н             | Х           | NOP         | Continue burst to end Row<br>Row active                     |

|               | L     | Н   | Н   | L             | Х           | BST         | Burst stop, Row active                                      |

|               | L     | Н   | L   | Н             | BA, CA, A10 | READ/READA  | Terminate burst,<br>begin new read <sup>(7)</sup>           |

|               | L     | Н   | L   | L             | BA, CA, A10 | WRIT/WRITA  | Terminate burst,<br>begin write <sup>(7,8)</sup>            |

|               | L     | L   | Н   | Н             | BA, RA      | ACT         | ILLEGAL <sup>(3)</sup>                                      |

|               | L     | L   | Н   | L             | BA, A10     | PRE/PALL    | Terminate burst<br>Precharging                              |

|               | L     | L   | L   | Н             | Х           | REF/SELF    | ILLEGAL                                                     |

|               | L     | L   | L   | L             | OC, BA      | MRS         | ILLEGAL                                                     |

| Write         | Н     | Х   | Х   | х             | X           | DESL        | Continue burst to end<br>Write recovering                   |

|               | L     | Н   | Н   | Н             | Х           | NOP         | Continue burst to end<br>Write recovering                   |

|               |       | Н   | Н   | L             | Х           | BST         | Burst stop, Row active                                      |

|               | L     | Н   | L   | Н             | BA, CA, A10 | READ/READA  | Terminate burst, start read :<br>Determine AP (7,8)         |

|               | L     | Н   | L   | L             | BA, CA, A10 | WRIT/WRITA  | Terminate burst, new write :<br>Determine AP <sup>(7)</sup> |

|               |       | L   | Н   | Н             | BA, RA      | RA ACT      | ILLEGAL <sup>(3)</sup>                                      |

|               | <br>L |     | H   | L             | BA, A10     | PRE/PALL    | Terminate burst Precharging (9                              |

|               | <br>L |     |     | <u>-</u><br>Н | X           | REF/SELF    | ILLEGAL                                                     |

|               | <br>L |     |     |               | OC, BA      | MRS         | ILLEGAL                                                     |

Note: H=VIH, L=VIL x= VIH or VIL, V = Valid Data, BA= Bank Address, CA+Column Address, RA=Row Address, OC= Op-Code

### FUNCTIONAL TRUTH TABLE Continued:

| Current State                 | $\overline{\text{CS}}$ | RAS | CAS | WE | Address     | Command     | Action                                                      |

|-------------------------------|------------------------|-----|-----|----|-------------|-------------|-------------------------------------------------------------|

| Read with auto<br>Precharging | H                      | ×   | ×   | ×  | ×           | DESL        | Continue burst to end, Precharge                            |

|                               | L                      | Н   | Н   | Н  | х           | NOP         | Continue burst to end, Precharge                            |

|                               | L                      | Н   | Н   | L  | ×           | BST         | ILLEGAL                                                     |

|                               | L                      | Н   | L   | Н  | BA, CA, A10 | READ/READA  | ILLEGAL (11)                                                |

|                               | L                      | Н   | L   | L  | BA, CA, A10 | WRIT/ WRITA | ILLEGAL (11)                                                |

|                               | L                      | L   | Н   | Н  | BA, RA      | ACT         | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | L   | Н   | L  | BA, A10     | PRE/PALL    | ILLEGAL (11)                                                |

|                               | L                      | L   | L   | Н  | ×           | REF/SELF    | ILLEGAL                                                     |

|                               | L                      | L   | L   | L  | OC, BA      | MRS         | ILLEGAL                                                     |

| Write with Auto<br>Precharge  | Н                      | ×   | ×   | ×  | ×           | DESL        | Continue burst to end, Write recovering with auto precharge |

|                               | L                      | Н   | Н   | Н  | ×           | NOP         | Continue burst to end, Write recovering with auto precharge |

|                               | L                      | Н   | Н   | L  | ×           | BST         | ILLEGAL                                                     |

|                               | L                      | Н   | L   | Н  | BA, CA, A10 | READ/READA  | ILLEGAL <sup>(11)</sup>                                     |

|                               | L                      | Н   | L   | L  | BA, CA, A10 | WRIT/ WRITA | ILLEGAL (11)                                                |

|                               | L                      | L   | Н   | Н  | BA, RA      | ACT         | ILLEGAL <sup>(3,11)</sup>                                   |

|                               | L                      | L   | Н   | L  | BA, A10     | PRE/PALL    | ILLEGAL <sup>(3,11)</sup>                                   |

|                               | L                      | L   | L   | Н  | ×           | REF/SELF    | ILLEGAL                                                     |

|                               | L                      | L   | L   | L  | OC, BA      | MRS         | ILLEGAL                                                     |

| Precharging                   | Н                      | ×   | ×   | ×  | ×           | DESL        | Nop, Enter idle after tRP                                   |

|                               | L                      | Н   | Н   | Н  | ×           | NOP         | Nop, Enter idle after tRP                                   |

|                               | L                      | Н   | Н   | L  | ×           | BST         | Nop, Enter idle after tRP                                   |

|                               | L                      | Н   | L   | Н  | BA, CA, A10 | READ/READA  | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA  | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | L   | Н   | Н  | BA, RA      | ACT         | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | L   | Н   | L  | BA, A10     | PRE/PALL    | Nop Enter idle after tRP                                    |

|                               | L                      | L   | L   | Н  | ×           | REF/SELF    | ILLEGAL                                                     |

|                               | L                      | L   | L   | L  | OC, BA      | MRS         | ILLEGAL                                                     |

| Row Activating                | Н                      | ×   | ×   | ×  | ×           | DESL        | Nop, Enter bank active after tRCD                           |

|                               | L                      | Н   | Н   | Н  | ×           | NOP         | Nop, Enter bank active after tRCD                           |

|                               | L                      | Н   | Н   | L  | ×           | BST         | Nop, Enter bank active after tRCD                           |

|                               | L                      | Н   | L   | Н  | BA, CA, A10 | READ/READA  | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA  | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | L   | Н   | Н  | BA, RA      | ACT         | ILLEGAL <sup>(3,9)</sup>                                    |

|                               | L                      | L   | Н   | L  | BA, A10     | PRE/PALL    | ILLEGAL <sup>(3)</sup>                                      |

|                               | L                      | L   | L   | Н  | ×           | REF/SELF    | ILLEGAL                                                     |

|                               | L                      | L   | L   | L  | OC, BA      | MRS         | ILLEGAL                                                     |

Note: H=VIH, L=VIL x= VIH or VIL, V = Valid Data, BA= Bank Address, CA+Column Address, RA=Row Address, OC= Op-Code

#### FUNCTIONAL TRUTH TABLE Continued:

| Current State    | $\overline{CS}$ | RAS | CAS | WE | Address     | Command                 | Action                           |

|------------------|-----------------|-----|-----|----|-------------|-------------------------|----------------------------------|

| Write Recovering | Н               | ×   | ×   | ×  | ×           | DESL                    | Nop, Enter row active after tDPL |

|                  | L               | Н   | Н   | Н  | ×           | NOP                     | Nop, Enter row active after tDPL |

|                  | L               | Н   | Н   | L  | ×           | BST                     | Nop, Enter row active after tDPL |

|                  | L               | Н   | L   | Н  | BA, CA, A10 | READ/READA              | Begin read <sup>(8)</sup>        |

|                  | L               | Н   | L   | L  | BA, CA, A10 | WRIT/ WRITA             | Begin new write                  |

|                  | L               | L   | Н   | Н  | BA, RA      | ACT                     | ILLEGAL <sup>(3)</sup>           |

|                  | L               | L   | Н   | L  | BA, A10     | PRE/PALL                | ILLEGAL <sup>(3)</sup>           |

|                  | L               | L   | L   | Н  | ×           | <b>REF/SELF</b>         | ILLEGAL                          |

|                  | L               | L   | L   | L  | OC, BA      | MRS                     | ILLEGAL                          |

| Write Recovering | Н               | ×   | ×   | ×  | ×           | DESL                    | Nop, Enter precharge after tDPL  |

| with Auto        | L               | Н   | Н   | Н  | ×           | NOP                     | Nop, Enter precharge after tDPL  |

| Precharge        | L               | Н   | Н   | L  | ×           | BST                     | Nop, Enter row active after tDPL |

|                  | L               | Н   | L   | Н  | BA, CA, A10 | READ/READA              | ILLEGAL <sup>(3,8,11)</sup>      |

|                  | L               | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA              | ILLEGAL <sup>(3,11)</sup>        |

|                  | L               | L   | Н   | Н  | BA, RA      | ACT                     | ILLEGAL <sup>(3,11)</sup>        |

|                  | L               | L   | Н   | L  | BA, A10     | PRE/PALL                | ILLEGAL <sup>(3,11)</sup>        |

|                  | L               | L   | L   | Н  | ×           | REF/SELF                | ILLEGAL                          |

|                  | L               | L   | L   | L  | OC, BA      | MRS                     | ILLEGAL                          |

| Refresh          | Н               | ×   | ×   | ×  | ×           | DESL                    | Nop, Enter idle after tRC        |

|                  | L               | Н   | Н   | ×  | ×           | NOP/BST                 | Nop, Enter idle after tRC        |

|                  | L               | Н   | L   | Н  | BA, CA, A10 | READ/READA              | ILLEGAL                          |

|                  | L               | Н   | L   | L  | BA, CA, A10 | WRIT/WRITA              | ILLEGAL                          |

|                  | L               | L   | Н   | Н  | BA, RA      | ACT                     | ILLEGAL                          |

|                  | L               | L   | Н   | L  | BA, A10     | PRE/PALL                | ILLEGAL                          |

|                  | L               | L   | L   | Н  | ×           | REF/SELF                | ILLEGAL                          |

|                  | L               | L   | L   | L  | OC, BA      | MRS                     | ILLEGAL                          |

| Mode Register    | Н               | ×   | ×   | ×  | ×           | DESL                    | Nop, Enter idle after 2 clocks   |

| Accessing        | L               | Н   | Н   | Н  | ×           | NOP                     | Nop, Enter idle after 2 clocks   |

|                  | L               | Н   | Н   | L  | ×           | BST                     | ILLEGAL                          |

|                  | L               | Н   | L   | ×  | BA, CA, A10 | <b>READ/WRITE</b>       | ILLEGAL                          |

|                  | L               | L   | ×   | ×  | BA, RA      | ACT/PRE/PALL<br>REF/MRS | ILLEGAL                          |

Note: H=VIH, L=VIL x= VIH or VIL, V = Valid Data, BA= Bank Address, CA+Column Address, RA=Row Address, OC= Op-Code

Notes:

- 1. All entries assume that CKE is active (CKEn-1=CKEn=H).

- 2. If both banks are idle, and CKE is inactive (Low), the device will enter Power Down mode. All input buffers except CKE will be disabled.

- 3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

- 4. If both banks are idle, and CKE is inactive (Low), the device will enter Self-Refresh mode. All input buffers except CKE will be disabled.

- 5. Illegal if tRCD is not satisfied.

- 6. Illegal if tRAS is not satisfied.

- 7. Must satisfy burst interrupt condition.

- 8. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 9. Must mask preceding data which don't satisfy tDPL.

- 10. Illegal if tRRD is not satisfied.

- 11. Illegal for single bank, but legal for other banks.

#### CKE RELATED COMMAND TRUTH TABLE<sup>(1)</sup>

|                     |                                                | CKE |   |    |     |     |    |           |

|---------------------|------------------------------------------------|-----|---|----|-----|-----|----|-----------|

| Current State       | Operation                                      | n-1 | n | CS | RAS | CAS | WE | Address   |

| Self-Refresh (S.R.) | INVALID, CLK (n - 1) would exit S.R.           | Н   | Х | Х  | Х   | Х   | Х  | Х         |

|                     | Self-Refresh Recovery <sup>(2)</sup>           | L   | Н | Н  | Х   | Х   | Х  | Х         |

|                     | Self-Refresh Recovery <sup>(2)</sup>           | L   | Н | L  | Н   | Н   | Х  | Х         |

|                     | Illegal                                        | L   | Н | L  | Н   | L   | Х  | Х         |

|                     | Illegal                                        | L   | Н | L  | L   | Х   | Х  | Х         |

|                     | Maintain S.R.                                  | L   | L | Х  | Х   | Х   | Х  | Х         |

| Self-Refresh Recove | ry Idle After tRC                              | Н   | Н | Н  | Х   | Х   | Х  | Х         |

|                     | Idle After tRC                                 | Н   | Н | L  | Н   | Н   | Х  | Х         |

|                     | Illegal                                        | Н   | Н | L  | Н   | L   | Х  | Х         |

|                     | Illegal                                        | Н   | н | L  | L   | Х   | Х  | Х         |

|                     | Begin clock suspend next cycle <sup>(5)</sup>  | Н   | L | Н  | Х   | Х   | Х  | Х         |

|                     | Begin clock suspend next cycle <sup>(5)</sup>  | Н   | L | L  | Н   | Н   | Х  | Х         |

|                     | Illegal                                        | Н   | L | L  | Н   | L   | Х  | Х         |

|                     | Illegal                                        | Н   | L | L  | L   | Х   | Х  | Х         |

|                     | Exit clock suspend next cycle <sup>(2)</sup>   | L   | Н | Х  | Х   | Х   | Х  | Х         |

|                     | Maintain clock suspend                         | L   | L | Х  | Х   | Х   | Х  | Х         |

| Power-Down (P.D.)   | INVALID, CLK (n - 1) would exit P.D.           | Н   | Х | Х  | Х   | Х   | Х  | —         |

|                     | EXIT P.D> Idle <sup>(2)</sup>                  | L   | Н | Х  | Х   | Х   | Х  | Х         |

|                     | Maintain power down mode                       | L   | L | Х  | Х   | Х   | Х  | Х         |

| Both Banks Idle     | Refer to operations in Operative Command Table | Н   | Н | Н  | Х   | Х   | Х  | _         |

|                     | Refer to operations in Operative Command Table | Н   | Н | L  | Н   | Х   | Х  | —         |

|                     | Refer to operations in Operative Command Table | Н   | Н | L  | L   | Н   | Х  | _         |

|                     | Auto-Refresh                                   | Н   | Н | L  | L   | L   | Н  | Х         |

|                     | Refer to operations in Operative Command Table | Н   | Н | L  | L   | L   | L  | Op - Code |

|                     | Refer to operations in Operative Command Table | Н   | L | Н  | Х   | Х   | Х  | —         |

|                     | Refer to operations in Operative Command Table | Н   | L | L  | Н   | Х   | Х  | —         |

|                     | Refer to operations in Operative Command Table | Н   | L | L  | L   | Н   | Х  | —         |

|                     | Self-Refresh <sup>(3)</sup>                    | Н   | L | L  | L   | L   | Н  | Х         |

|                     | Refer to operations in Operative Command Table | Н   | L | L  | L   | L   | L  | Op - Code |

|                     | Power-Down <sup>(3)</sup>                      | L   | Х | Х  | Х   | Х   | Х  | Х         |

| Any state           | Refer to operations in Operative Command Table | Н   | Н | Х  | Х   | Х   | Х  | Х         |

| other than          | Begin clock suspend next cycle <sup>(4)</sup>  | Н   | L | Х  | Х   | Х   | Х  | Х         |

| listed above        | Exit clock suspend next cycle                  | L   | Н | Х  | Х   | Х   | Х  | Х         |

|                     | Maintain clock suspend                         | L   | L | Х  | Х   | Х   | Х  | Х         |

#### Notes:

- H : High level, L : low level, X : High or low level (Don't care).

CKE Low to High transition will re-enable CLK and other inputs asynchronously. A minimum setup time must be satisfied

- before any command other than EXIT.

- 3. Power down and Self refresh can be entered only from the both banks idle state.

- 4. Must be legal command as defined in Operative Command Table.

- 5. Illegal if txsR is not satisfied.

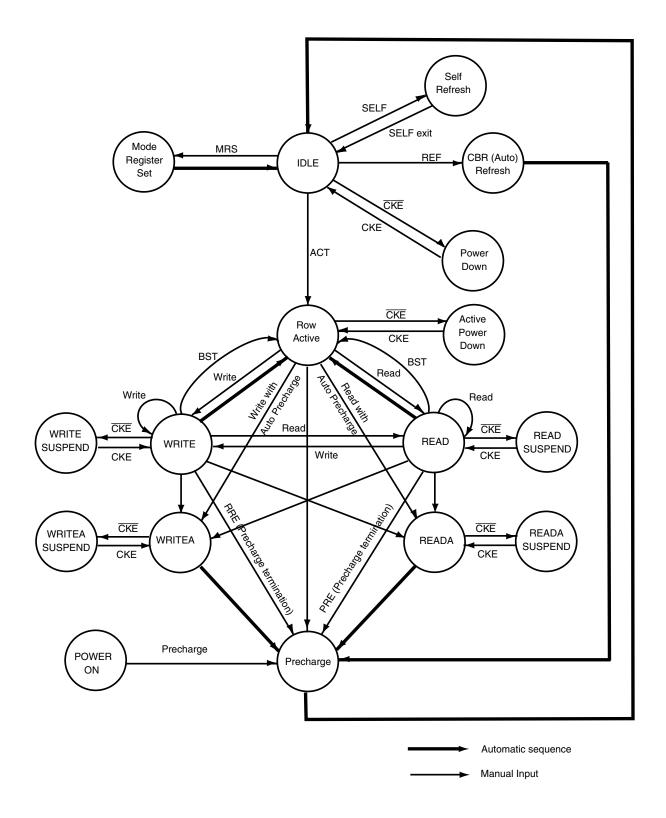

### STATE DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol   | Parameters                        |        | Rating             | Unit |

|----------|-----------------------------------|--------|--------------------|------|

| VDD MAX  | Maximum Supply Voltage            |        | -0.5 to +4.6       | V    |

| VDDQ MAX | Maximum Supply Voltage for Output | Buffer | -0.5 to +4.6       | V    |

| VIN      | Input Voltage                     |        | -0.5 to VDD + 0.5  | V    |

| Vout     | Output Voltage                    |        | -1.0 to VDDQ + 0.5 | V    |

| Pd max   | Allowable Power Dissipation       |        | 1                  | W    |

| lcs      | Output Shorted Current            |        | 50                 | mA   |

| Topr     | Operating Temperature             | Com.   | 0 to +70           | ۵°   |

|          |                                   | Ind.   | -40 to +85         |      |

|          |                                   | A1     | -40 to +85         |      |

|          |                                   | A2     | -40 to +105        |      |

| Тѕтс     | Storage Temperature               |        | -65 to +150        | °C   |

#### Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. All voltages are referenced to Vss.

# DC RECOMMENDED OPERATING CONDITIONS

(TA = 0°C to +70°C for Commercial grade. TA = -40°C to +85°C for Industrial and A1 grade. TA = -40°C to +105°C for A2 grade.)

| Symbol         | Parameter          | Min. | Тур. | Max.       | Unit |

|----------------|--------------------|------|------|------------|------|

| Vdd            | Supply Voltage     | 3.0  | 3.3  | 3.6        | V    |

| Vddq           | I/O Supply Voltage | 3.0  | 3.3  | 3.6        | V    |

| $V_{IH^{(1)}}$ | Input High Voltage | 2.0  | —    | VDDQ + 0.3 | V    |

| $VIL^{(2)}$    | Input Low Voltage  | -0.3 | —    | +0.8       | V    |

#### Note:

1. VIH (max) = VDDQ +1.2V (PULSE WIDTH  $\leq$  3NS).

2. VIL (min) = -1.2V (PULSE WIDTH  $\leq$  3NS).

3. All voltages are referenced to Vss.

#### **CAPACITANCE CHARACTERISTICS** (At $T_A = 0$ to $+25^{\circ}C$ , $V_{DD} = V_{DDQ} = 3.3 \pm 0.3V$ )

| Symbol | Parameter Min.                         |     | Ма  | Unit |    |

|--------|----------------------------------------|-----|-----|------|----|

|        |                                        |     | -6  | -7   |    |

| CIN1   | Input Capacitance: CLK                 | 2.5 | 3.5 | 4.0  | pF |

| CIN2   | Input Capacitance:All other input pins | 2.5 | 3.8 | 5.0  | pF |

| Cı/o   | Data Input/Output Capacitance:I/Os     | 4.0 | 6.5 | 6.5  | pF |

| Symbol              | Parameter                                         | Test Condition                                                                                      | -6  | -7  | -75E | Unit |

|---------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| DD1 <sup>(1)</sup>  | Operating Current                                 | One bank active, $CL = 3$ , $BL = 1$ ,                                                              | 135 | 125 | 135  | mA   |

|                     |                                                   | tclκ = tclκ (min), trc = trc (min)                                                                  |     |     |      |      |

| DD2P                | Precharge Standby Current<br>(In Power-Down Mode) | $CKE \leq V\text{il} \   (\text{max}), \ tck = 15ns$                                                | 3   | 3   | 3    | mA   |

| DD2PS               | Precharge Standby Current<br>(In Power-Down Mode) | $CKE \leq V\text{il} \text{ (max), } CLK \leq V\text{il} \text{ (max)}$                             | 3   | 3   | 3    | mA   |

| DD2N (2)            | Precharge Standby Current                         | $\overline{\text{CS}} \ge \text{V}_{\text{DD}}$ - 0.2V, $\text{CKE} \ge \text{V}_{\text{IH}}$ (MIN) | 45  | 45  | 45   | mA   |

|                     | (In Non Power-Down Mode)                          | tcκ = 15ns                                                                                          |     |     |      |      |

| DD2NS               | Precharge Standby Current                         | $\overline{CS} \ge V_{DD}$ - 0.2V, $CKE \ge V_{IH}$ (MIN) or                                        | 30  | 30  | 30   | mA   |

|                     | (In Non Power-Down Mode)                          | $CKE \le V_{IL}$ (MAX), All inputs stable                                                           |     |     |      |      |

| IDD3P               | Active Standby Current                            | $CKE \le V_{IL}$ (MAX), tck = 15ns                                                                  | 4   | 4   | 4    | mA   |

|                     | (Power-Down Mode)                                 |                                                                                                     |     |     |      |      |

| DD3PS               | Active Standby Current                            | $CKE \leq VIL (MAX), CLK \leq VIL (MAX)$                                                            | 3   | 3   | 3    | mA   |

|                     | (Power-Down Mode)                                 |                                                                                                     |     |     |      |      |

| DD3N <sup>(2)</sup> | Active Standby Current                            | $\overline{\text{CS}} \ge \text{V}_{\text{DD}}$ - 0.2V, $\text{CKE} \ge \text{V}_{\text{IH}}$ (MIN) | 55  | 55  | 55   | mA   |

|                     | (In Non Power-Down Mode)                          | tcκ = 15ns                                                                                          |     |     |      |      |

| DD3NS               | Active Standby Current                            | $\overline{CS} \ge V_{DD}$ - 0.2V, $CKE \ge V_{IH}$ (MIN) or                                        | 30  | 30  | 30   | mA   |

|                     | (In Non Power-Down Mode)                          | $CKE \le V_{IL}$ (MAX), All inputs stable                                                           |     |     |      |      |

| DD4                 | Operating Current                                 | All banks active, $BL = 4$ , $CL = 3$ ,                                                             | 180 | 150 | 180  | mA   |

|                     |                                                   | tск = tск (min)                                                                                     |     |     |      |      |

| DD5                 | Auto-Refresh Current                              | trc = trc (min), tclk = tclk (min)                                                                  | 350 | 270 | 285  | mA   |

| DD6                 | Self-Refresh Current                              | $CKE \le 0.2V$                                                                                      | 3   | 3   | 3    | mA   |

#### DC ELECTRICAL CHARACTERISTICS 1 (Recommended Operation Conditions unless otherwise noted.)

Notes:

1. IDD (MAX) is specified at the output open condition.

2. Input signals are changed one time during 30ns.

### DC ELECTRICAL CHARACTERISTICS 2 (Recommended Operation Conditions unless otherwise noted.)

| Symbol | Parameter                 | Test Condition                                                                  | Min | Max | Unit |

|--------|---------------------------|---------------------------------------------------------------------------------|-----|-----|------|

| lı∟    | Input Leakage Current     | but Leakage Current $0V \le V \text{in} \le V \text{DD}$ , with pins other than |     | 10  | μA   |

|        |                           | the tested pin at 0V                                                            |     |     |      |

| Iol    | Output Leakage Current    | Output is disabled, $0V \le Vout \le VDD$ ,                                     | -10 | 10  | μA   |

| Vон    | Output High Voltage Level | Іон = -2mA                                                                      | 2.4 | _   | V    |

| Vol    | Output Low Voltage Level  | Iol = 2mA                                                                       | _   | 0.4 | V    |

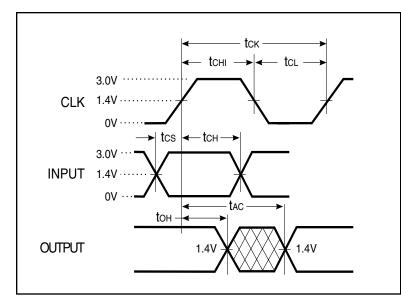

### **AC ELECTRICAL CHARACTERISTICS** (1,2,3,4)

|        |                                                                                                                   |      | -6   |      | -7   |      | -75E |       |

|--------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| Symbol | Parameter                                                                                                         | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| tскз   | Clock Cycle Time CAS Latency = 3                                                                                  | 6    | _    | 7    | _    | _    | _    | ns    |

| tск2   | CAS Latency = 2                                                                                                   | 10   | —    | 10   | —    | 7.5  | —    | ns    |

| tac3   | Access Time From CLK CAS Latency = 3                                                                              | —    | 5.4  | _    | 5.4  | _    | —    | ns    |

| tAC2   | CAS Latency = 2                                                                                                   |      | 6.5  |      | 6.5  | _    | 5.5  | ns    |

| tсні   | CLK HIGH Level Width                                                                                              | 2.5  | —    | 2.5  | —    | 2.5  | —    | ns    |

| tc∟    | CLK LOW Level Width                                                                                               | 2.5  | —    | 2.5  | —    | 2.5  | _    | ns    |

| tонз   | Output Data Hold Time $\overline{CAS}$ Latency = 3                                                                | 2.7  | —    | 2.7  | —    | —    | —    | ns    |

| toh2   | CAS Latency = 2                                                                                                   | 2.7  | _    | 2.7  | —    | 2.7  | —    | ns    |

| t∟z    | Output LOW Impedance Time                                                                                         | 0    | —    | 0    | —    | 0    | —    | ns    |

| tHZ    | Output HIGH Impedance Time                                                                                        | 2.7  | 5.4  | 2.7  | 5.4  | 2.7  | 5.4  | ns    |

| tos    | Input Data Setup Time <sup>(2)</sup>                                                                              | 1.5  | —    | 1.5  | —    | 1.5  | —    | ns    |

| tdн    | Input Data Hold Time <sup>(2)</sup>                                                                               | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| tas    | Address Setup Time <sup>(2)</sup>                                                                                 | 1.5  | _    | 1.5  | _    | 1.5  | _    | ns    |

| tан    | Address Hold Time <sup>(2)</sup>                                                                                  | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| tcĸs   | CKE Setup Time <sup>(2)</sup>                                                                                     | 1.5  | _    | 1.5  | —    | 1.5  | —    | ns    |

| tскн   | CKE Hold Time <sup>(2)</sup>                                                                                      | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| tcs    | Command Setup Time (CS, RAS, CAS, WE, DQM) <sup>(2)</sup>                                                         | 1.5  | _    | 1.5  | —    | 1.5  | _    | ns    |

| tсн    | Command Hold Time ( $\overline{CS}$ , $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ , DQM) <sup>(2)</sup> | 1.0  | _    | 1.0  | —    | 1.0  | _    | ns    |

| trc    | Command Period (REF to REF / ACT to ACT)                                                                          | 60   | _    | 67.5 | _    | 67.5 | _    | ns    |

| tras   | Command Period (ACT to PRE)                                                                                       | 42   | 100K | 45   | 100K | 45   | 100K | ns    |

| trp    | Command Period (PRE to ACT)                                                                                       | 18   | _    | 20   | _    | 15   | _    | ns    |

| trcd   | Active Command To Read / Write Command Delay Time                                                                 | 18   | _    | 20   | _    | 15   | _    | ns    |

| trrd   | Command Period (ACT [0] to ACT[1])                                                                                | 12   | _    | 14   | _    | 15   | _    | ns    |

| tdpl   | Input Data To Precharge<br>Command Delay time                                                                     | 12   | -    | 14   | _    | 15   | _    | ns    |

| tdal   | Input Data To Active / Refresh<br>Command Delay time (During Auto-Precharge)                                      | 30   | _    | 35   | _    | 30   | —    | ns    |

| tmrd   | Mode Register Program Time                                                                                        | 12   | _    | 14   | _    | 15   | _    | ns    |

| tdde   | Power Down Exit Setup Time                                                                                        | 6    | _    | 7    | _    | 7.5  | _    | ns    |

| txsr   | Self-Refresh Exit Time <sup>(5)</sup>                                                                             | 70   | _    | 70   | _    | 70   | _    | ns    |

| tτ     | Transition Time                                                                                                   | 0.3  | 1.2  | 0.3  | 1.2  | 0.3  | 1.2  | ns    |

| tref   | Refresh Cycle Time (4096) TA $\leq$ 70°C Com., Ind., A1, A2                                                       | _    | 64   | _    | 64   | _    | 64   | ms    |

|        | $T_A \leq 85^{\circ}C$ Ind., A1, A2                                                                               | —    | 64   | —    | 64   | —    | 64   | ms    |

|        | $T_{A} > 85^{\circ}C$ A2                                                                                          | —    | —    | —    | 16   | —    | —    | ms    |

#### Notes:

1. The power-on sequence must be executed before starting memory operation.

2. Measured with  $t\tau = 1$  ns. If clock rising time is longer than 1ns, (tr /2 - 0.5) ns should be added to the parameter.

3. The reference level is 1.4V when measuring input signal timing. Rise and fall times are measured between VIH(min.) and VIL (max).

4. Use recommended operation conditions.

5. Self-Refresh Mode is not supported for A2 grade with  $T_A > +85^{\circ}C$ .

# **OPERATING FREQUENCY / LATENCY RELATIONSHIPS**

| SYMBOL       | . PARAMETER                                                                |                                                              |     |     |        |          | UNITS |

|--------------|----------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|--------|----------|-------|

| _            | Clock Cycle Time                                                           |                                                              | 6   | 7   | 75     | 10       | ns    |

|              | Operating Frequency                                                        |                                                              | 166 | 143 | 133    | 100      | MHz   |

| tcac         | CAS Latency                                                                |                                                              | 3   | 3   | 2      | 2/3      | cycle |

| trcd         | Active Command To Read/Write Command Delay                                 | Time                                                         | 3   | 3   | 2      | 2        | cycle |

| <b>t</b> RAC | RAS Latency (tRCD + tCAC)                                                  | 6                                                            | 6   | 4   | 5<br>4 | cycle    |       |

| trc          | Command Period (REF to REF / ACT to ACT)                                   |                                                              | 10  | 10  | 9      | 7        | cycle |

| tras         | Command Period (ACT to PRE)                                                |                                                              | 7   | 7   | 6      | 5        | cycle |

| trp          | Command Period (PRE to ACT)                                                |                                                              | 3   | 3   | 2      | 2        | cycle |

| trrd         | Command Period (ACT[0] to ACT [1])                                         |                                                              | 2   | 2   | 2      | 2        | cycle |

| tccD         | Column Command Delay Time<br>(READ, READA, WRIT, WRITA)                    |                                                              | 1   | 1   | 1      | 1        | cycle |

| <b>İ</b> DPL | Input Data To Precharge Command Delay Time                                 |                                                              |     | 2   | 2      | 2        | cycle |

| tdal         | Input Data To Active/Refresh Command Delay Tirr<br>(During Auto-Precharge) | le                                                           | 5   | 5   | 4      | 4        | cycle |

| IRBD         | Burst Stop Command To Output in HIGH-Z Delay Time (Read)                   | $\overline{CAS}$ Latency = 3<br>$\overline{CAS}$ Latency = 2 | 3   | 3   | 2      | 3<br>2   | cycle |

| twвd         | Burst Stop Command To Input in Invalid Delay Tirr<br>(Write)               | le                                                           | 0   | 0   | 0      | 0        | cycle |

| trql         | Precharge Command To Output in HIGH-Z Delay Time (Read)                    | $\overline{CAS}$ Latency = 3<br>$\overline{CAS}$ Latency = 2 | 3   | 3   | 2      | 3<br>2   | cycle |

| WDL          | Precharge Command To Input in Invalid Delay Tim<br>(Write)                 | e                                                            | 0   | 0   | 0      | 0        | cycle |

| PQL          | Last Output To Auto-Precharge Start Time (Read)                            | $\overline{CAS}$ Latency = 3<br>$\overline{CAS}$ Latency = 2 | -2  | -2  | <br>-1 | -2<br>-1 | cycle |

| tqмd         | DQM To Output Delay Time (Read)                                            |                                                              | 2   | 2   | 2      | 2        | cycle |

| tomd         | DQM To Input Delay Time (Write)                                            |                                                              | 0   | 0   | 0      | 0        | cycle |

| tmrd         | Mode Register Set To Command Delay Time                                    |                                                              | 2   | 2   | 2      | 2        | cycle |

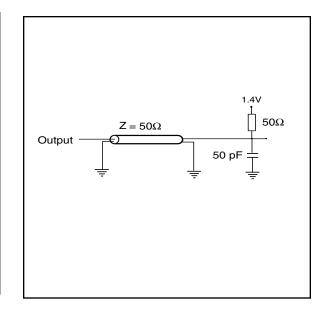

### ACTEST CONDITIONS

### Input Load

Output Load

## **ACTEST CONDITIONS**

| Parameter                                 | Rating     |

|-------------------------------------------|------------|

| AC Input Levels                           | 0V to 3.0V |

| Input Rise and Fall Times                 | 1 ns       |

| Input Timing Reference Level              | 1.4V       |

| Output Timing Measurement Reference Level | 1.4V       |

### FUNCTIONAL DESCRIPTION

Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an AC-TIVE command which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BA0 and BA1 select the bank, A0-A11 select the row). The address bits A0-A8 registered coincident with the READ or WRITE command are used to select the starting column location for the burst access.

Prior to normal operation, the SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

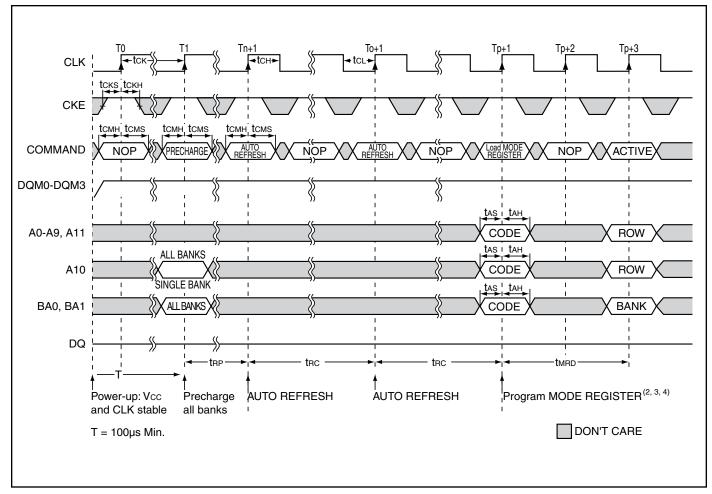

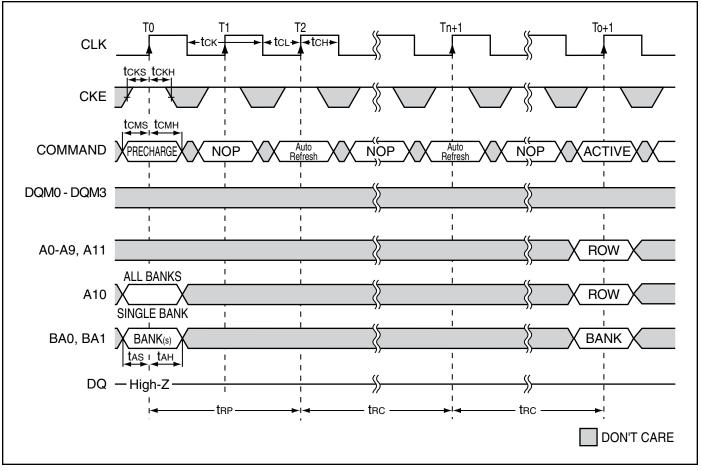

### Initialization

SDRAMs must be powered up and initialized in a predefined manner.

The 256M SDRAM is initialized after the power is applied to VDD and VDDQ (simultaneously) and the clock is stable with DQM High and CKE High.

A 100µs delay is required prior to issuing any command other than a COMMAND INHIBIT or a NOP. The COMMAND INHIBIT or NOP may be applied during the 100µs period and should continue at least through the end of the period.

With at least one COMMAND INHIBIT or NOP command having been applied, a PRECHARGE command should be applied once the 100µs delay has been satisfied. All banks must be precharged. This will leave all banks in an idle state after which at least two AUTO REFRESH cycles must be performed. After the AUTO REFRESH cycles are complete, the SDRAM is then ready for mode register programming.

The mode register should be loaded prior to applying any operational command because it will power up in an unknown state.

### INITIALIZE AND LOAD MODE REGISTER<sup>(1)</sup>

#### Notes:

- If CS is High at clock High time, all commands applied are NOP.

The Mode register may be loaded prior to the Auto-Refresh cycles if desired.

- JEDEC and PC100 specify three clocks.

Outputs are guaranteed High-Z after the command is issued.

# AUTO-REFRESH CYCLE

Notes:

1.  $\overline{CAS}$  latency = 2, 3

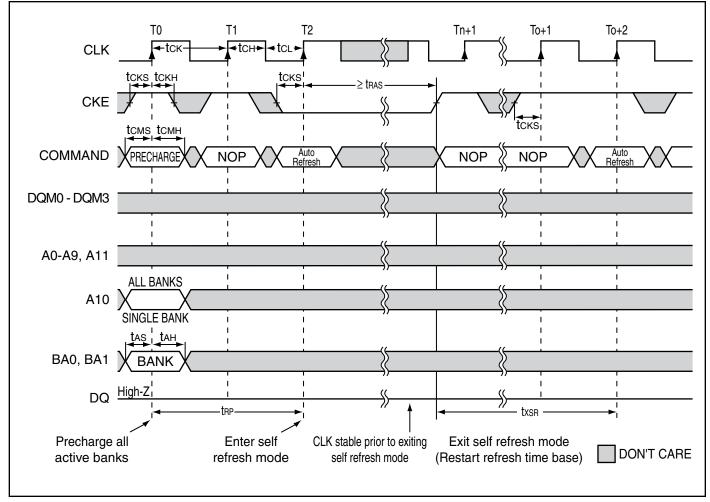

## SELF-REFRESH CYCLE

Note:

1. Self-Refresh Mode is not supported for A2 grade with  $T_A > +85^{\circ}C$ .

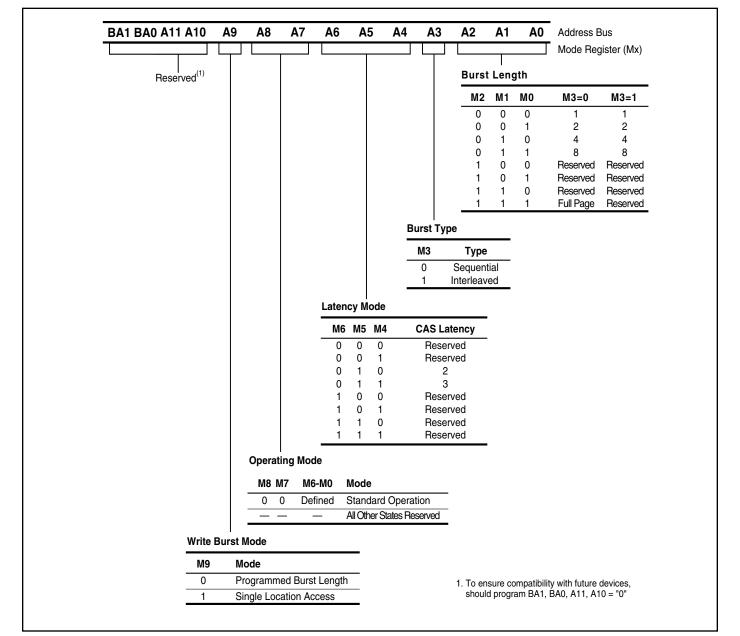

### **REGISTER DEFINITION**

#### **Mode Register**

The mode register is used to define the specific mode of operation of the SDRAM. This definition includes the selection of a burst length, a burst type, a CAS latency, an operating mode and a write burst mode, as shown in MODE REGISTER DEFINITION.

The mode register is programmed via the LOAD MODE REGISTER command and will retain the stored information until it is programmed again or the device loses power.

Mode register bits M0-M2 specify the burst length, M3 specifies the type of burst (sequential or interleaved), M4- M6 specify the CAS latency, M7 and M8 specify the operating mode, M9 specifies the WRITE burst mode, and M10 and M11 are reserved for future use.

The mode register must be loaded when all banks are idle, and the controller must wait the specified time before initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.

## MODE REGISTER DEFINITION

Integrated Silicon Solution, Inc. - www.issi.com Rev. C 12/01/09

### **BURST LENGTH**

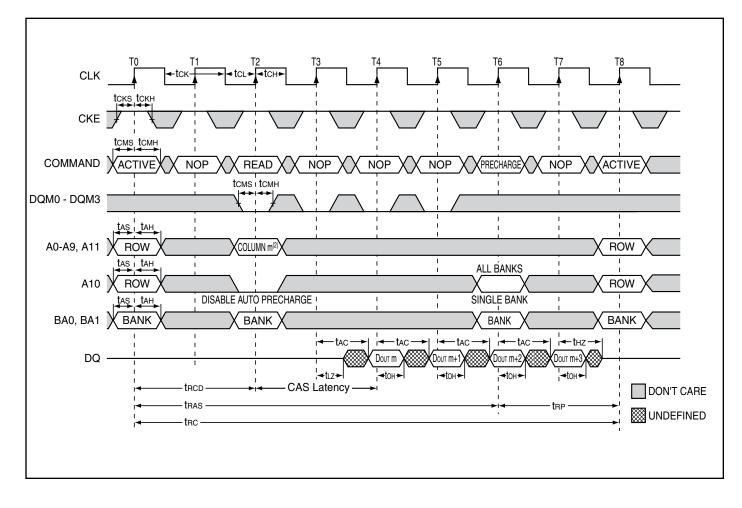

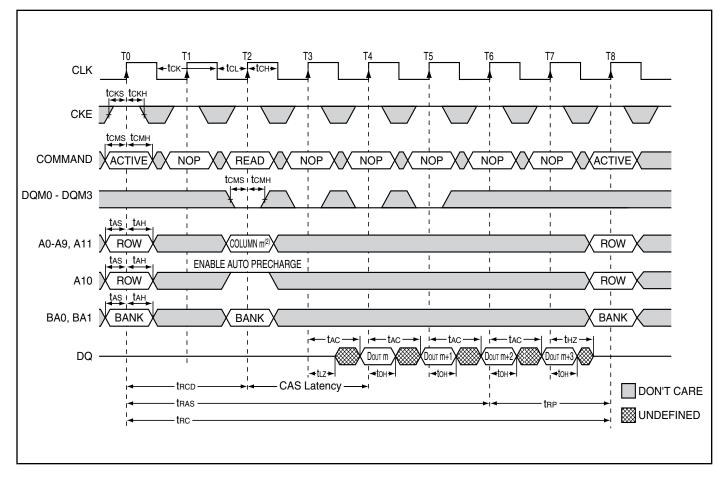

Read and write accesses to the SDRAM are burst oriented, with the burst length being programmable, as shown in MODE REGISTER DEFINITION. The burst length determines the maximum number of column locations that can be accessed for a given READ or WRITE command. Burst lengths of 1, 2, 4 or 8 locations are available for both the sequential and the interleaved burst types, and a full-page burst is available for the sequential type. The full-page burst is used in conjunction with the BURST TERMINATE command to generate arbitrary burst lengths.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively selected. All accesses for that burst take place within this block, mean-

ing that the burst will wrap within the block if a boundary is reached. The block is uniquely selected by A1-A8 (x32) when the burst length is set to two; by A2-A8 (x32) when the burst length is set to four; and by A3-A8 (x32) when the burst length is set to eight. The remaining (least significant) address bit(s) is (are) used to select the starting location within the block. Full-page bursts wrap within the page if the boundary is reached.

#### **Burst Type**

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column address, as shown in BURST DEFINITION table.

### **BURST DEFINITION**

| Burst        | Starting Column |         |     | Order of Acce                        | esses Within a Burst |

|--------------|-----------------|---------|-----|--------------------------------------|----------------------|

| Length       |                 | Address |     | Type = Sequential                    | Type = Interleaved   |

|              |                 |         | A 0 |                                      |                      |

| 2            |                 |         | 0   | 0-1                                  | 0-1                  |

|              |                 |         | 1   | 1-0                                  | 1-0                  |

|              |                 | A 1     | A 0 |                                      |                      |

|              |                 | 0       | 0   | 0-1-2-3                              | 0-1-2-3              |

| 4            |                 | 0       | 1   | 1-2-3-0                              | 1-0-3-2              |

|              |                 | 1       | 0   | 2-3-0-1                              | 2-3-0-1              |

|              |                 | 1       | 1   | 3-0-1-2                              | 3-2-1-0              |

|              | A 2             | A 1     | A 0 |                                      |                      |

|              | 0               | 0       | 0   | 0-1-2-3-4-5-6-7                      | 0-1-2-3-4-5-6-7      |

|              | 0               | 0       | 1   | 1-2-3-4-5-6-7-0                      | 1-0-3-2-5-4-7-6      |

|              | 0               | 1       | 0   | 2-3-4-5-6-7-0-1                      | 2-3-0-1-6-7-4-5      |

| 8            | 0               | 1       | 1   | 3-4-5-6-7-0-1-2                      | 3-2-1-0-7-6-5-4      |

|              | 1               | 0       | 0   | 4-5-6-7-0-1-2-3                      | 4-5-6-7-0-1-2-3      |

|              | 1               | 0       | 1   | 5-6-7-0-1-2-3-4                      | 5-4-7-6-1-0-3-2      |

|              | 1               | 1       | 0   | 6-7-0-1-2-3-4-5                      | 6-7-4-5-2-3-0-1      |

|              | 1               | 1       | 1   | 7-0-1-2-3-4-5-6                      | 7-6-5-4-3-2-1-0      |

| Full<br>Page | n = A0-A        | 8       |     | Cn, Cn + 1, Cn + 2<br>Cn + 3, Cn + 4 | Not Supported        |

| (y)          | (location 0     | -у)     |     | Ćn - 1,<br>Cn                        |                      |

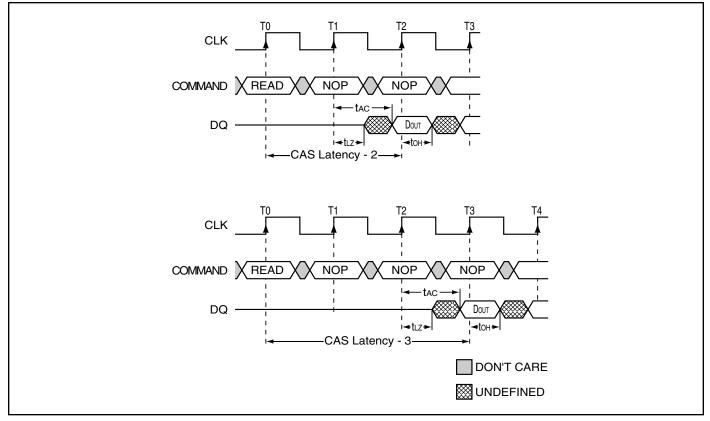

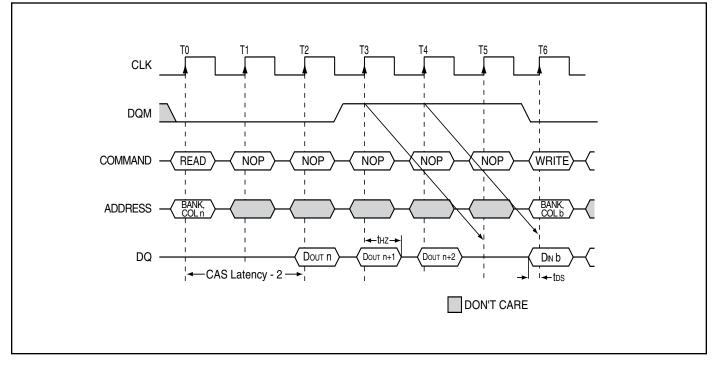

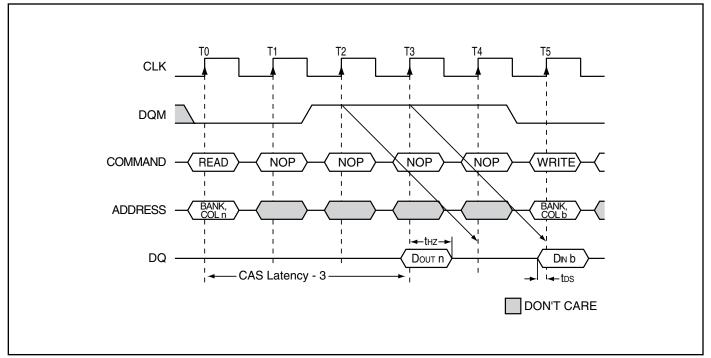

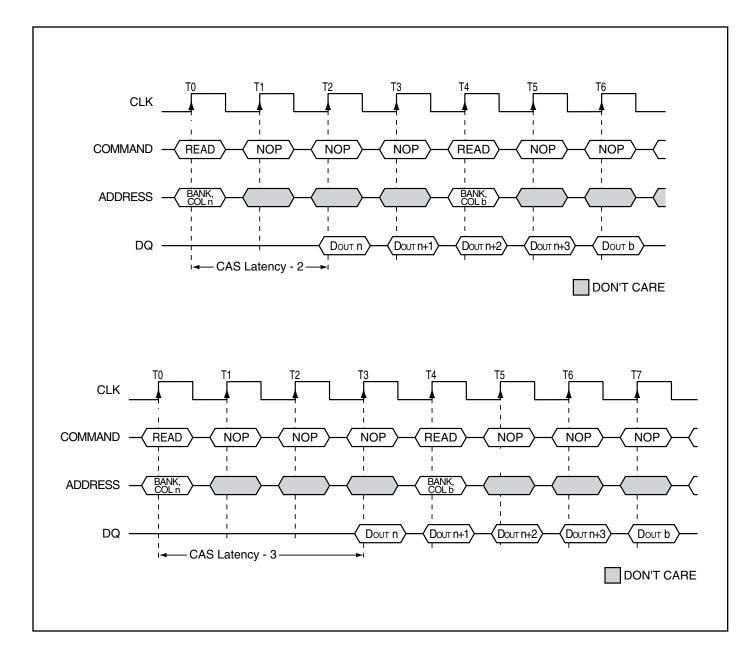

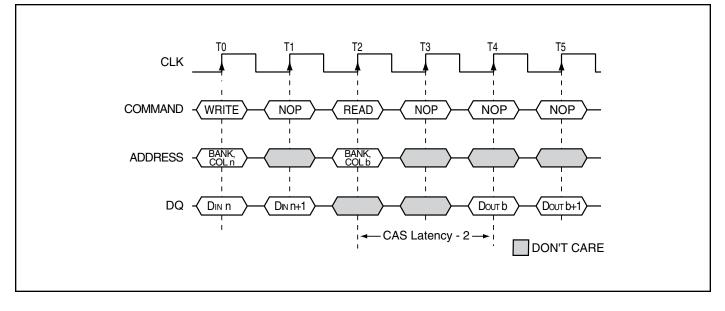

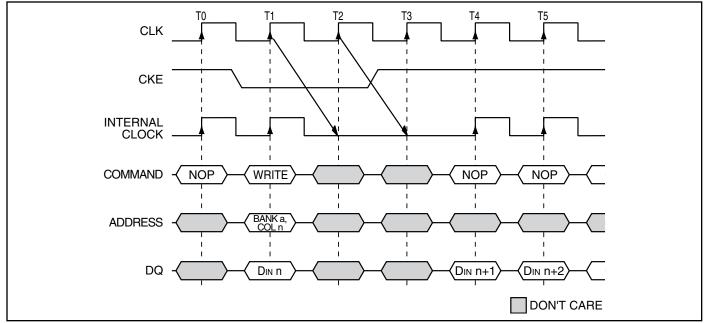

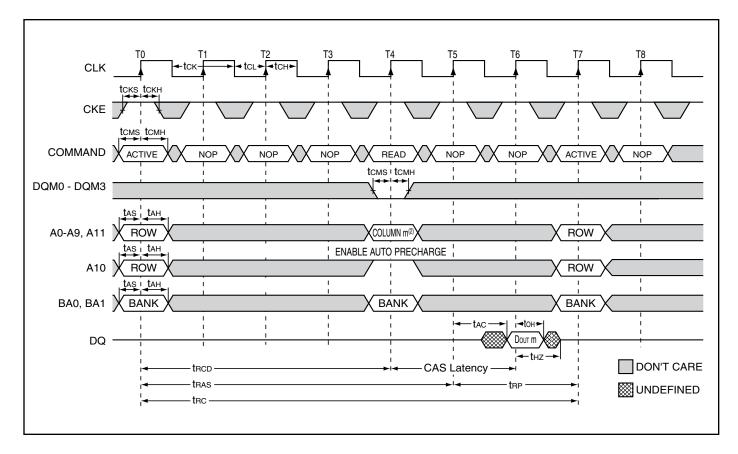

### **CAS Latency**

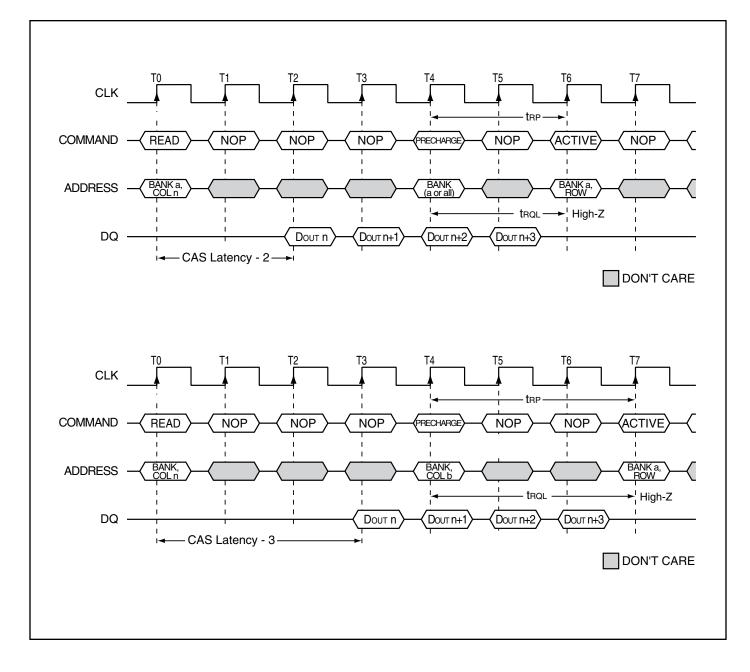

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first piece of output data. The latency can be set to two or three clocks.

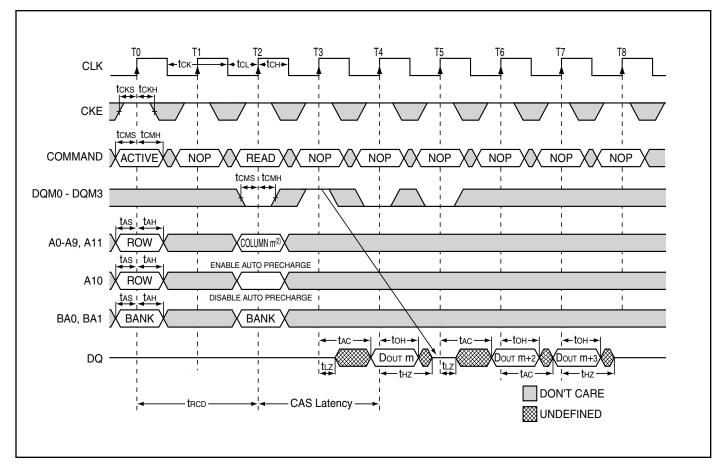

If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available by clock edge n + m. The DQs will start driving as a result of the clock edge one cycle earlier (n + m - 1), and provided that the relevant access times are met, the data will be valid by clock edge n + m. For example, assuming that the clock cycle time is such that all relevant access times are met, if a READ command is registered at T0 and the latency is programmed to two clocks, the DQs will start driving after T1 and the data will be valid by T2, as shown in CAS Latency diagrams. The Allowable Operating Frequency table indicates the operating frequencies at which each CAS latency setting can be used.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

# **Operating Mode**

The normal operating mode is selected by setting M7 and M8 to zero; the other combinations of values for M7 and M8 are reserved for future use and/or test modes. The programmed burst length applies to both READ and WRITE bursts.

Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

#### Write Burst Mode

When M9 = 0, the burst length programmed via M0-M2 applies to both READ and WRITE bursts; when M9 = 1, the programmed burst length applies to READ bursts, but write accesses are single-location (nonburst) accesses.

### CAS Latency

#### Allowable Operating Frequency (MHz)

| Speed | CAS Latency = 2 | CAS Latency = 3 |

|-------|-----------------|-----------------|

| -6    | 100             | 166             |

| -7    | 100             | 143             |

| -75E  | 133             | _               |

### CAS LATENCY

Integrated Silicon Solution, Inc. - www.issi.com Rev. C 12/01/09

#### **CHIP OPERATION**

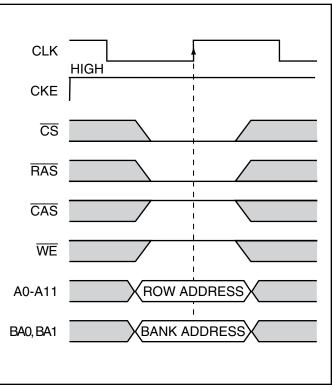

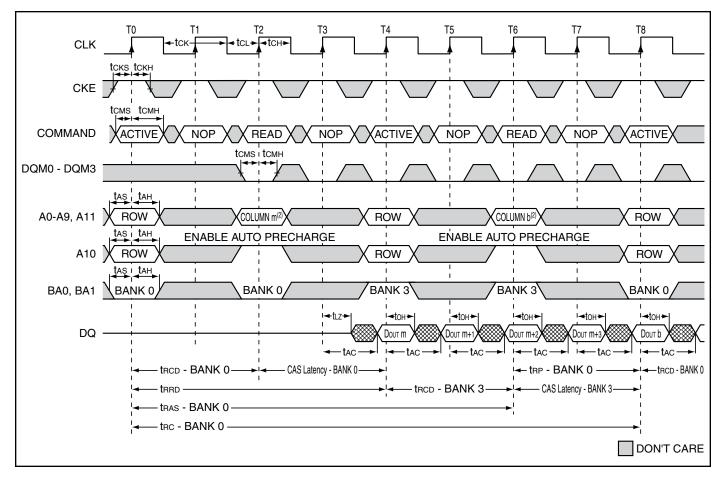

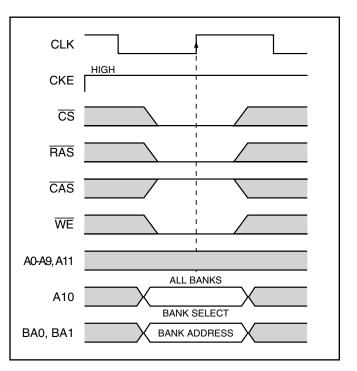

### **BANK/ROW ACTIVATION**

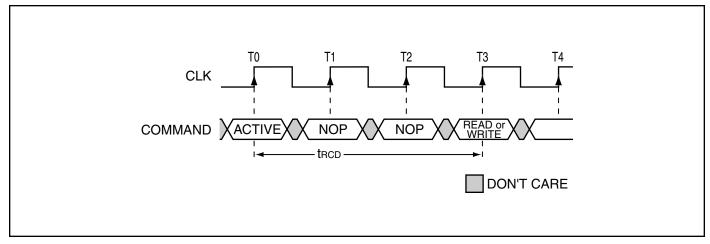

Before any READ or WRITE commands can be issued to a bank within the SDRAM, a row in that bank must be "opened." This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated (see Activating Specific Row Within Specific Bank).

After opening a row (issuing an ACTIVE command), a READ or WRITE command may be issued to that row, subject to the tRCD specification. Minimum tRCD should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVE command on which a READ or WRITE command can be entered. For example, a tRCD specification of 18ns with a 125 MHz clock (8ns period) results in 2.25 clocks, rounded to 3. This is reflected in the following example, which covers any case where  $2 < [tRCD (MIN)/tcK] \le 3$ . (The same procedure is used to convert other specification limits from time units to clock cycles).

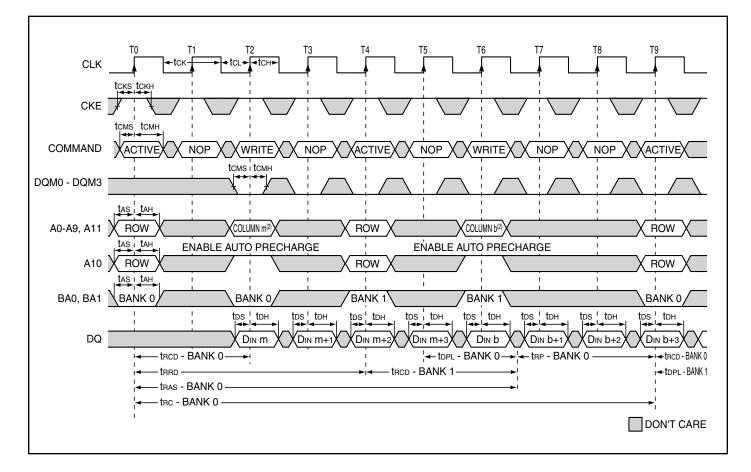

A subsequent ACTIVE command to a different row in the same bank can only be issued after the previous active row has been "closed" (precharged). The minimum time interval between successive ACTIVE commands to the same bank is defined by tRc.

A subsequent ACTIVE command to another bank can be issued while the first bank is being accessed, which results in a reduction of total row-access overhead. The minimum time interval between successive ACTIVE commands to different banks is defined by tRRD.

### ACTIVATING SPECIFIC ROW WITHIN SPE-CIFIC BANK

# **EXAMPLE:** MEETING TRCD (MIN) WHEN 2 < [TRCD (MIN)/TCK] $\leq$ 3

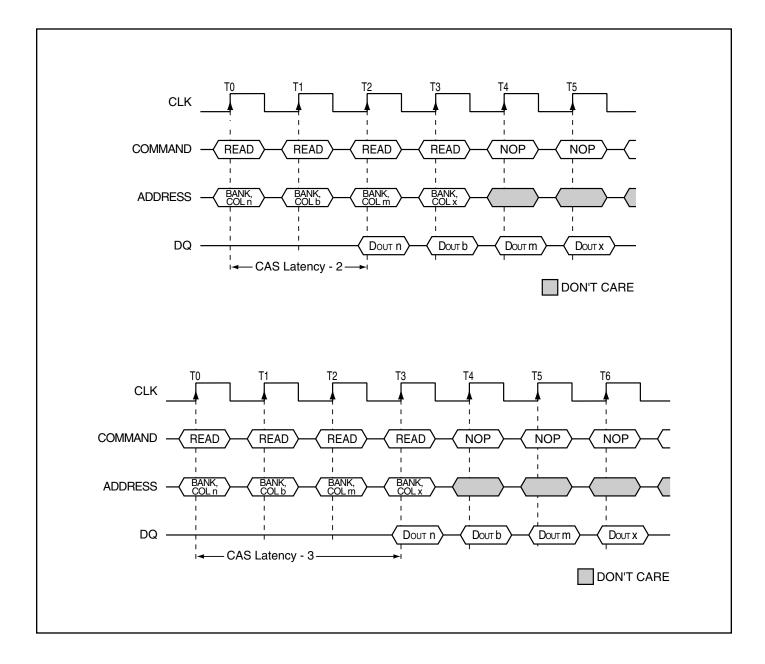

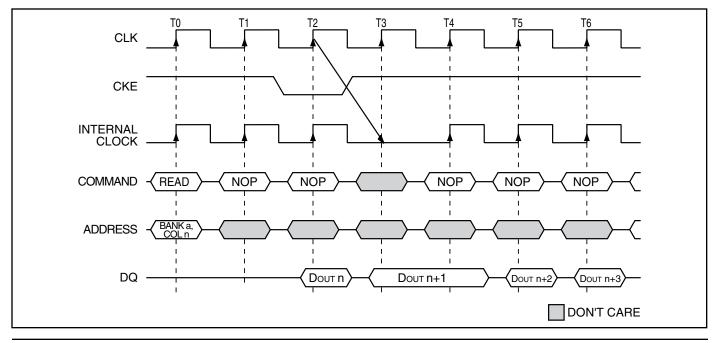

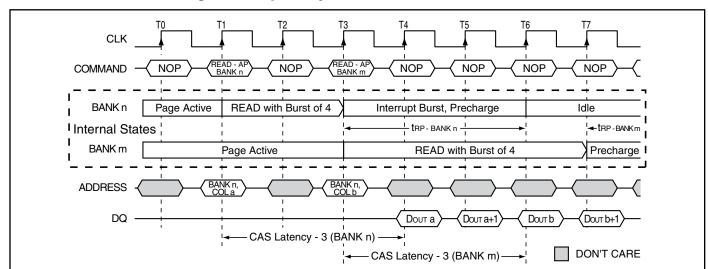

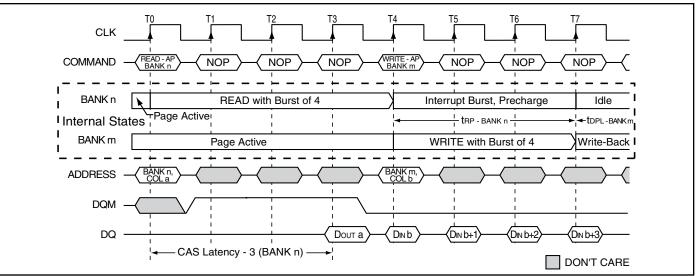

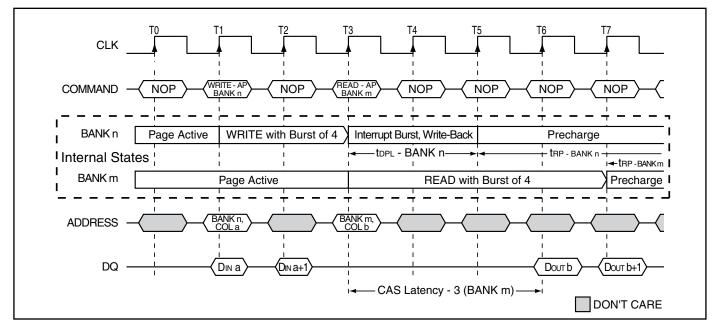

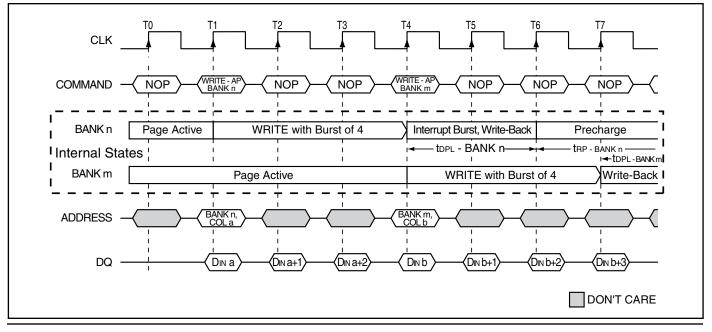

# READS

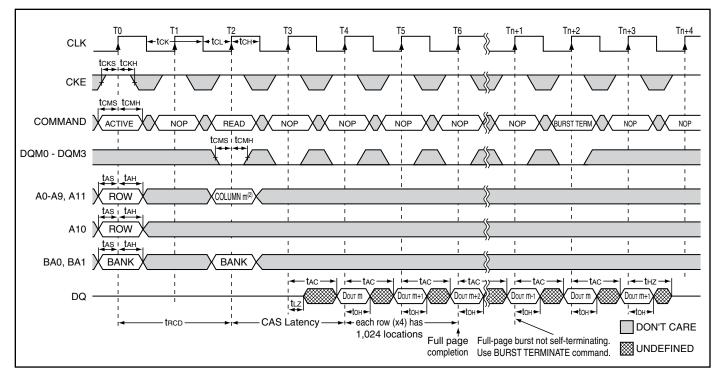

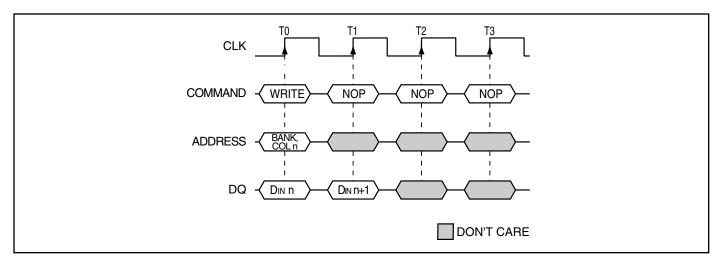

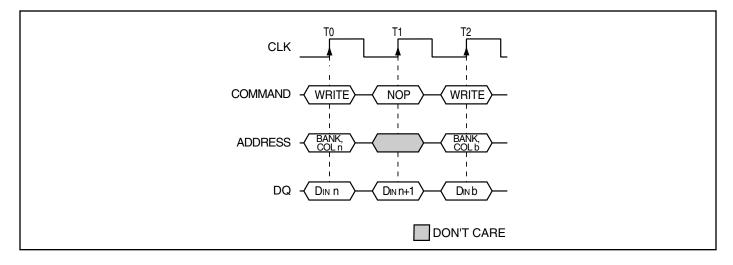

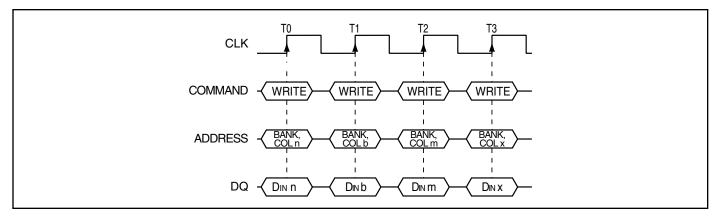

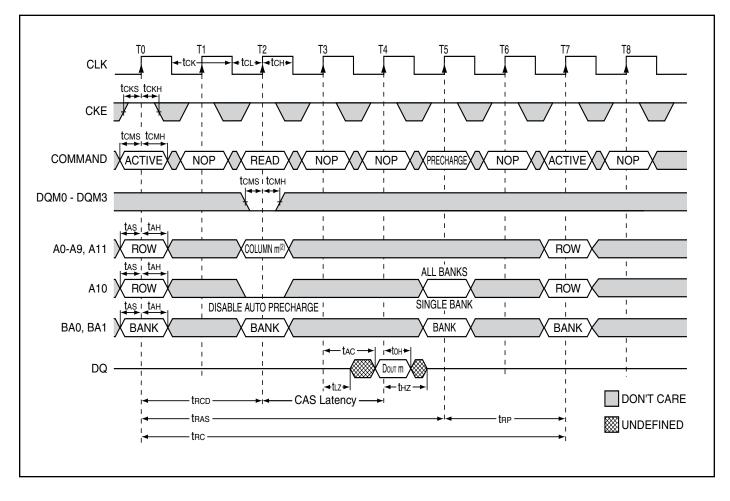

READ bursts are initiated with a READ command, as shown in the READ COMMAND diagram.

The starting column and bank addresses are provided with the READ command, and auto precharge is either enabled or disabled for that burst access. If auto precharge is enabled, the row being accessed is precharged at the completion of the burst. For the generic READ commands used in the following illustrations, auto precharge is disabled.

During READ bursts, the valid data-out element from the starting column address will be available following the CAS latency after the READ command. Each subsequent data-out element will be valid by the next positive clock edge. The CAS Latency diagram shows general timing for each possible CAS latency setting.

Upon completion of a burst, assuming no other commands have been initiated, the DQs will go High-Z. A full-page burst will continue until terminated. (At the end of the page, it will wrap to column 0 and continue.)