# **ADF7023-J\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

## Evaluation Kits <a> □</a>

· ADF7023-J Evaluation Board

## Documentation <a>□</a>

#### **Application Notes**

- AN-1276: Embedded Packet Error Rate Testing on the ADF7023 and ADF7023-J

- AN-1339: ADF7023-J AD\_15d4g Firmware Download Module

- AN-1340: ADF7023-J IEEE 802.15.4g/UBUSAir/FAN Firmware Module

- AN-1394: AES Encryption and Decryption for the ADF7023 and ADF7023-J

#### **Data Sheet**

ADF7023-J: High Performance, Low Power, ISM Band FSK/GFSK/MSK/GMSK Transceiver IC Data Sheet

## Software and Systems Requirements

• ADF7023 Evaluation Board Software

## Tools and Simulations <a> □</a>

· ADIsimSRD Design Studio

## Reference Materials

#### **Press**

Analog Devices and Renesas Wireless Communications Platform Achieves Wi-SUN Alliance Certification

#### **Product Selection Guide**

· RF Source Booklet

#### **Solutions Bulletins & Brochures**

• RF Transceivers for Short Range Devices

#### **Technical Articles**

- Low Power, Low Cost, Wireless ECG Holter Monitor

- RF Meets Power Lines: Designing Intelligent Smart Grid Systems that Promote Energy Efficiency

- Smart Metering Technology Promotes Energy Efficiency for a Greener World

- Understand Wireless Short-Range Devices for Global License-Free Systems

- Wireless Short Range Devices and Narrowband Communications

- Wireless Technologies for Smart Meters: Focus on Water Metering

## Design Resources <a>□</a>

- · ADF7023-J Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## Discussions <a>□</a>

View all ADF7023-J EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support <a> </a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Features                                    | 1  | Interrupts in Sport Mode             | 48 |

|---------------------------------------------|----|--------------------------------------|----|

| Applications                                | 1  | ADF7023-J Memory Map                 | 49 |

| Revision History                            | 3  | BBRAM                                | 49 |

| Functional Block Diagram                    | 4  | Modem Configuration RAM (MCR)        | 49 |

| General Description                         | 4  | Program ROM                          | 49 |

| Specifications                              | 6  | Program RAM                          | 49 |

| RF and Synthesizer Specifications           | 6  | Packet RAM                           | 50 |

| Transmitter Specifications                  | 7  | SPI Interface                        | 51 |

| Receiver Specifications                     | 9  | General Characteristics              | 51 |

| Timing and Digital Specifications           | 12 | Command Access                       | 51 |

| Auxilary Block Specifications               | 13 | Status Word                          | 51 |

| General Specifications                      | 14 | Command Queuing                      | 52 |

| Timing Specifications                       | 15 | Memory Access                        | 53 |

| Absolute Maximum Ratings                    | 16 | Low Power Modes                      | 56 |

| ESD Caution                                 | 16 | Example Low Power Modes              | 59 |

| Pin Configuration and Function Descriptions | 17 | Low Power Mode Timing Diagrams       | 61 |

| Typical Performance Characteristics         | 19 | WUC Setup                            | 62 |

| Terminology                                 | 26 | Firmware Timer Setup                 | 63 |

| Radio Control                               | 27 | Calibrating the RC Oscillator        | 63 |

| Radio States                                | 27 | Downloadable Firmware Modules        | 65 |

| Initialization                              | 29 | Writing a Module to Program RAM      | 65 |

| Commands                                    | 30 | Image Rejection Calibration Module   | 65 |

| Automatic State Transitions                 | 32 | AES Encryption and Decryption Module | 65 |

| State Transition and Command Timing         | 33 | Reed-Solomon Coding Module           | 65 |

| Sport Mode                                  | 37 | Radio Blocks                         | 67 |

| Packet Structure in Sport Mode              | 37 | Frequency Synthesizer                | 67 |

| Sport Mode in Transmit                      | 37 | Crystal Oscillator                   | 68 |

| Sport Mode in Receive                       | 37 | Modulation                           | 68 |

| Transmit Bit Latencies in Sport Mode        | 37 | RF Output Stage                      | 69 |

| Packet Mode                                 | 40 | PA/LNA Interface                     | 69 |

| Preamble                                    | 40 | Receive Channel Filter               | 69 |

| Sync Word                                   | 41 | Image Channel Rejection              | 69 |

| Payload                                     | 42 | Automatic Gain Control (AGC)         | 70 |

| CRC                                         | 43 | RSSI                                 | 70 |

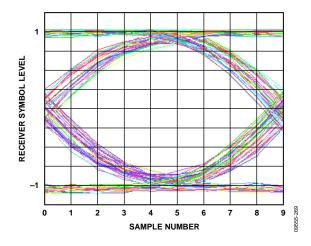

| Postamble                                   | 44 | 2FSK/GFSK/MSK/GMSK Demodulation      | 72 |

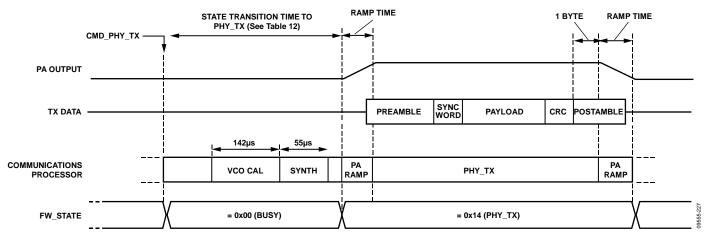

| Transmit Packet Timing                      | 44 | Clock Recovery                       | 73 |

| Data Whitening                              | 45 | Recommended Receiver Settings for    |    |

| Manchester Encoding                         | 45 | 2FSK/GFSK/MSK/GMSK                   |    |

| 8b/10b Encoding                             | 45 | Peripheral Features                  |    |

| Interrupt Generation                        | 46 | Analog-to-Digital Converter          | 76 |

| Temperature Sensor76                                                                      | Command Reference80                                        |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Test DAC76                                                                                | Register Maps81                                            |

| Transmit Test Modes76                                                                     | BBRAM Register Description83                               |

| Silicon Revision Readback76                                                               | MCR Register Description94                                 |

| Applications Information77                                                                | Packet RAM Register Description101                         |

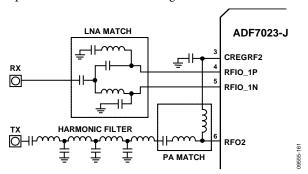

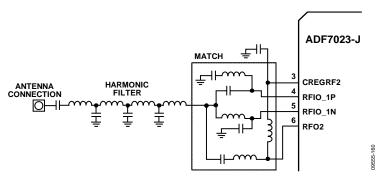

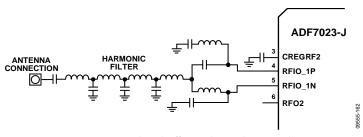

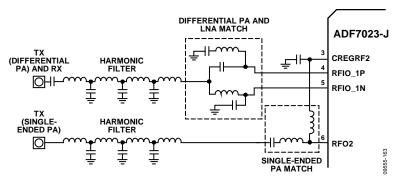

| Application Circuit77                                                                     | Outline Dimensions                                         |

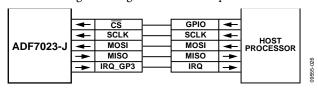

| Host Processor Interface                                                                  | Ordering Guide102                                          |

|                                                                                           | Ordering duide102                                          |

| PA/LNA Matching78                                                                         |                                                            |

| REVISION HISTORY                                                                          |                                                            |

| 3/14—Rev. C to Rev. D                                                                     | Changes to Table 7 and to table summary statement and      |

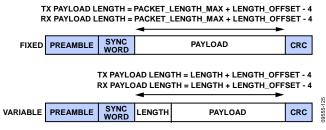

| Changes to Figure 5442                                                                    | changes to Figure 2 and Figure 315                         |

| Changes to Transmit Packet Timing Section and Figure 5644                                 | Changes to Figure 5 and Figure 719                         |

| Changes to Figure 6958                                                                    | Changes to Figure 4325                                     |

| Changes to Figure 7261                                                                    | Changes to PHY_SLEEP Section27                             |

| Change to Power Amplifier (PA) Section69                                                  | Changes to State Transition and Command Timing Section     |

| Changes to Table 88 and Table 8991                                                        | and changes to Table 1133                                  |

| Change to Table 9492                                                                      | Changes to Table 1234                                      |

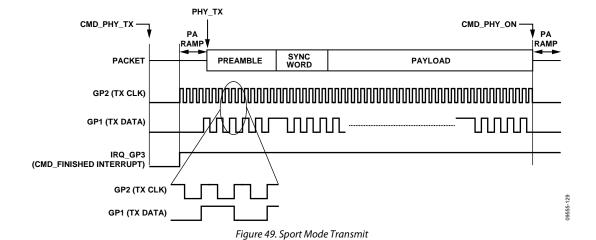

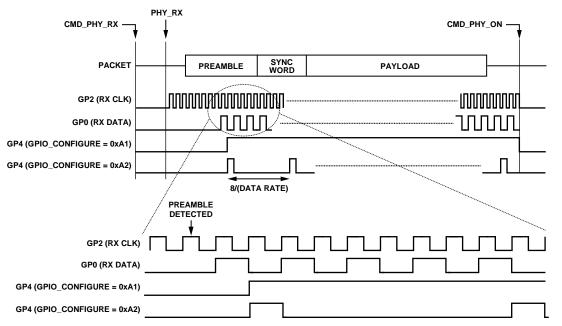

| Change to Table 9994                                                                      | Changes to Figure 49 and Figure 5038                       |

| Change to Table 10795                                                                     | Changes to Figure 51 and Figure 5239                       |

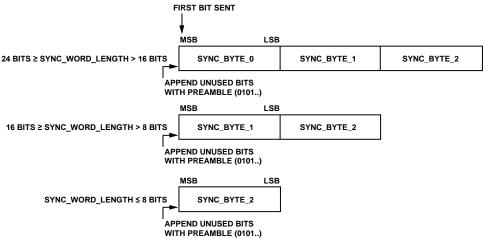

| Change to Table 11498                                                                     | Changes to Figure 5341                                     |

| - · · · · · · · · · · · · · · · · · · ·                                                   | Changes to Addressing Section42                            |

| 5/13—Rev. B to Rev. C                                                                     | Changes to Table 20 and changes to CRC Section             |

| Added t <sub>15</sub> to Table 7 and Figure 315                                           | Changes to Figure 56                                       |

| Changed Register 0x018 200 kbps Data Rate from 0x18 to                                    | Changes to Command Access Section                          |

|                                                                                           | Changes to Table 28                                        |

| 0x22; Table 3167                                                                          | · ·                                                        |

| 1/12 D A 4- D D                                                                           | Changes to Figure 69                                       |

| 1/13—Rev. A to Rev. B                                                                     | Changes to Table 29                                        |

| Change to Accuracy of Temperature Readback Parameter,                                     | Added Calibrating the RC Oscillator Section                |

| Table 5                                                                                   | Added Figure 75; Renumbered Sequentially64                 |

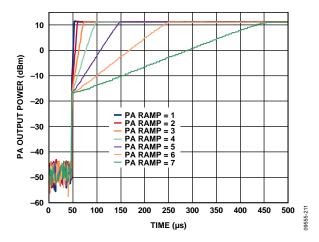

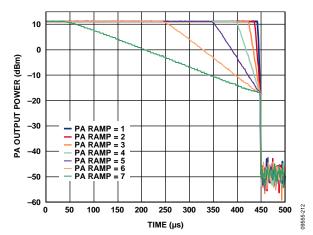

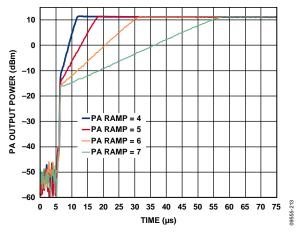

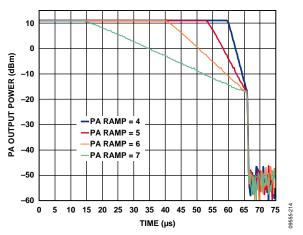

| Changes to Table 917                                                                      | Changes to Automatic PA Ramp Section and changes to Image  |

| Change to PHY_TX Section27                                                                | Channel Rejection Section69                                |

| Changes to Table 1236                                                                     | Changes to Temperature Sensor Section and changes to       |

| Changes to Figure 5644                                                                    | Table 4276                                                 |

| Changes to Interrupts in Sport Mode Section48                                             | Changes to Support for External PA and LNA Control Section |

| Changes to Table 2652                                                                     | and changes to Table 4479                                  |

| Changes to Table 2857                                                                     | Changes to Table 4781                                      |

| Changes to Table 2962                                                                     | Changes to Table 4882                                      |

| Changes to Crystal Oscillator Section and Table 3273                                      | Changes to Table 6986                                      |

| Change to Power Amplifier (PA) Section74                                                  | Changes to Table 7086                                      |

| Changes to Figure 8477                                                                    | Changes to Table 7688                                      |

| Changes to Table 4479                                                                     | Changes to Table 77 and to Table 7889                      |

| Changes to Table 9593                                                                     | Changes to Table 83 and to Table 8591                      |

| Change to Table 9994                                                                      | Changes to Table 93 and added Table 94; Renumbered         |

| Change to Table 137                                                                       | Sequentially                                               |

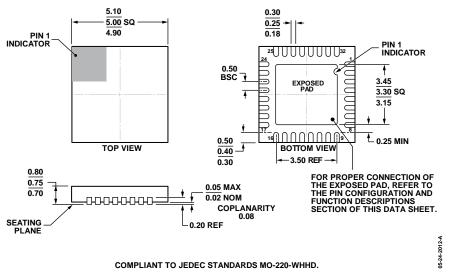

| Updated Outline Dimensions                                                                | Added Table 95 and Table 96                                |

| Opanica Saume Dimensions102                                                               | Changes to Table 10094                                     |

| 6/12—Rev. 0 to Rev. A                                                                     | Changes to Table 110                                       |

|                                                                                           | •                                                          |

| Changes to General Descriptions Section4 Changes to Calibration Time and to ADC Parameter | Added Table 123 and Table 12498 Changes to Table 144101    |

| in Table 513                                                                              |                                                            |

| 11 14015 3                                                                                | 5/11 Pavision 0. Initial Varsian                           |

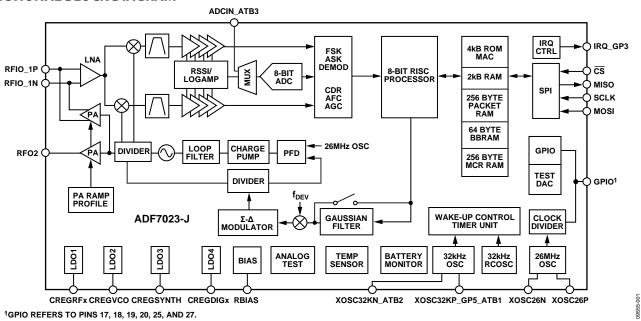

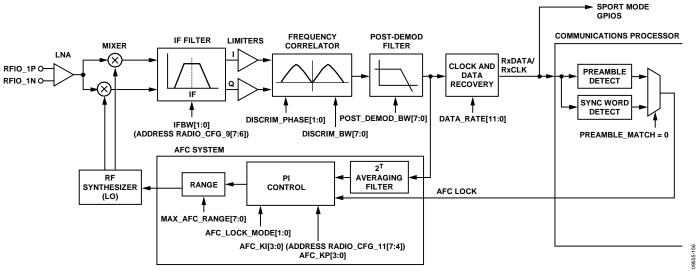

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **GENERAL DESCRIPTION**

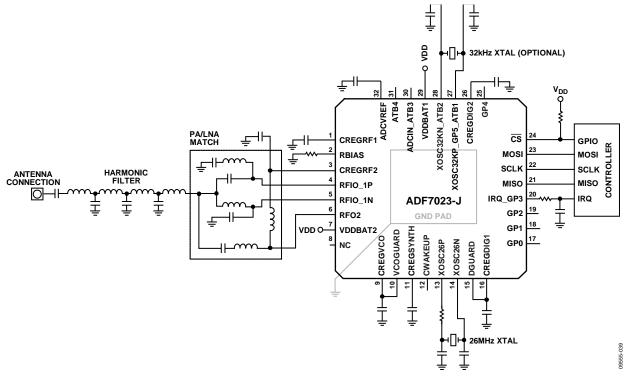

The ADF7023-J is a very low power, high performance, highly integrated 2FSK/GFSK/MSK/GMSK transceiver designed for operation in the 902 MHz to 958 MHz frequency band, which covers the ARIB Standard T96 band at 950 MHz. Data rates from 1 kbps to 300 kbps are supported.

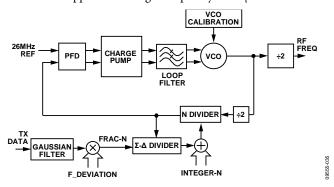

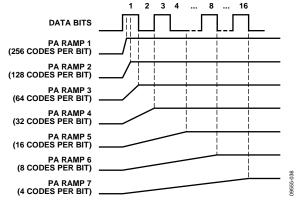

The transmit RF synthesizer contains a VCO and a low noise fractional-N phase locked loop (PLL) with an output channel frequency resolution of 400 Hz. The VCO operates at twice the fundamental frequency to reduce spurious emissions. The receive and transmit synthesizer bandwidths are automatically, and independently, configured to achieve optimum phase noise, modulation quality, and settling time. The transmitter output power is programmable from  $-20~\mathrm{dBm}$  to  $+13.5~\mathrm{dBm}$ , with automatic PA ramping to meet transient spurious specifications. The part possesses both single-ended and differential PAs, which allow for Tx antenna diversity.

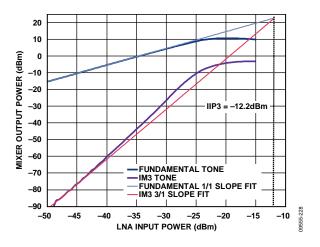

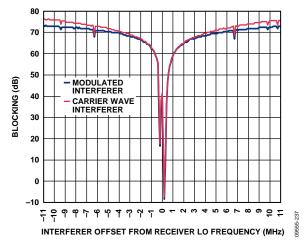

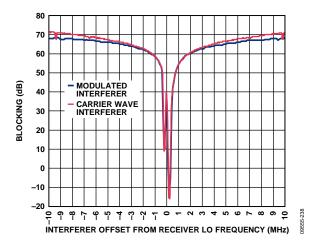

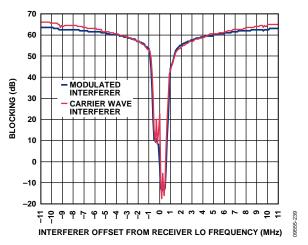

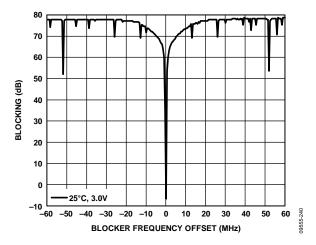

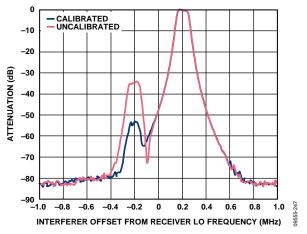

The receiver is exceptionally linear, achieving an IP3 specification of -12.2 dBm and -11.5 dBm at maximum gain and minimum gain, respectively, and an IP2 specification of 18.5 dBm and 27 dBm at maximum gain and minimum gain, respectively. The receiver achieves an interference blocking specification of 66 dB at a  $\pm 2$  MHz offset and 74 dB at a  $\pm 10$  MHz offset. Thus, the part is extremely resilient to the presence of interferers in spectrally noisy environments. The receiver features a novel, high speed, AFC loop, allowing the PLL to find and correct any RF frequency errors in the recovered packet. A patent pending image rejection calibration scheme is available by downloading the image rejection calibration firmware module to program RAM. The algorithm does not require the use of an external RF source nor does it require any user intervention once initiated. The results of the

calibration can be stored in nonvolatile memory for use on subsequent power-ups of the transceiver.

The ADF7023-J operates with a power supply range of 2.2 V to 3.6 V and has very low power consumption in both Tx and Rx modes, enabling long lifetimes in battery-operated systems while maintaining excellent RF performance. The device can enter a low power sleep mode in which the configuration settings are retained in the battery backup random access memory (BBRAM).

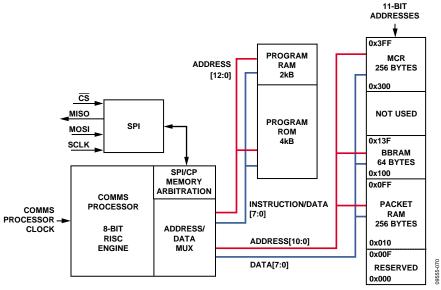

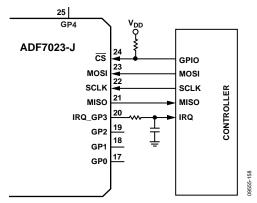

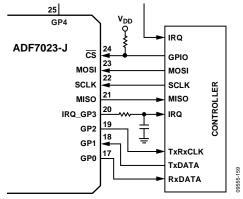

The ADF7023-J features an ultralow power, on-chip, communications processor. The communications processor, which is an 8-bit RISC processor, performs the radio control, packet management, and smart wake mode (SWM) functionality. The communications processor eases the processing burden of the companion processor by integrating the lower layers of a typical communication protocol stack. The communications processor also permits the download and execution of firmware modules. Available modules include image rejection (IR) calibration, advanced encryption standard (AES) encryption, and Reed-Solomon coding. These firmware modules are available online at ftp://ftp.analog.com/pub/RFL/FirmwareModules.

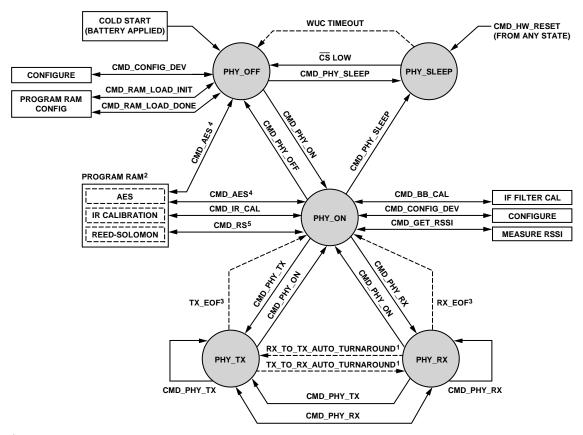

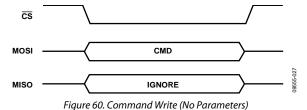

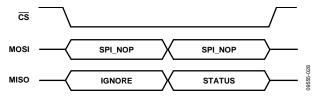

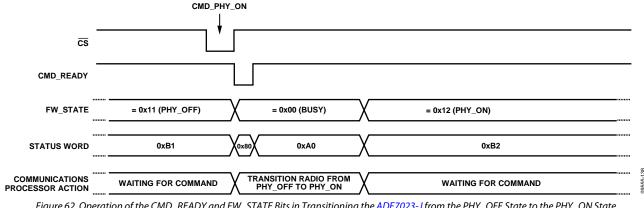

The communications processor provides a simple command-based radio control interface for the host processor. A single-byte command transitions the radio between states or performs a radio function.

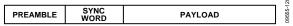

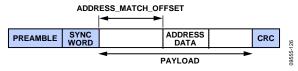

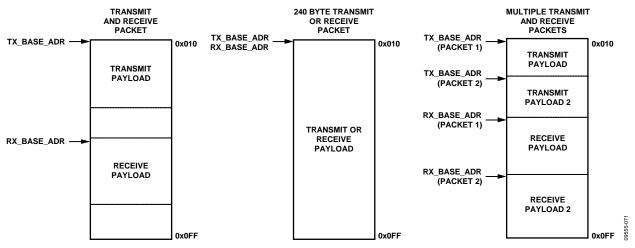

The communications processor provides support for generic packet formats. The packet format is highly flexible and fully programmable, thereby ensuring its compatibility with proprietary packet profiles. In transmit mode, the communications processor can be configured to add preamble, sync word, and CRC to the payload data stored in packet RAM. In receive mode, the

communications processor can detect and interrupt the host processor on reception of preamble, sync word, address, and CRC and store the received payload to packet RAM. The ADF7023-J uses an efficient interrupt system comprising MAC level interrupts and PHY level interrupts that can be individually set. The payload data plus the 16-bit CRC can be encoded/decoded using Manchester or 8b/10b encoding. Alternatively, data whitening and dewhitening can be applied.

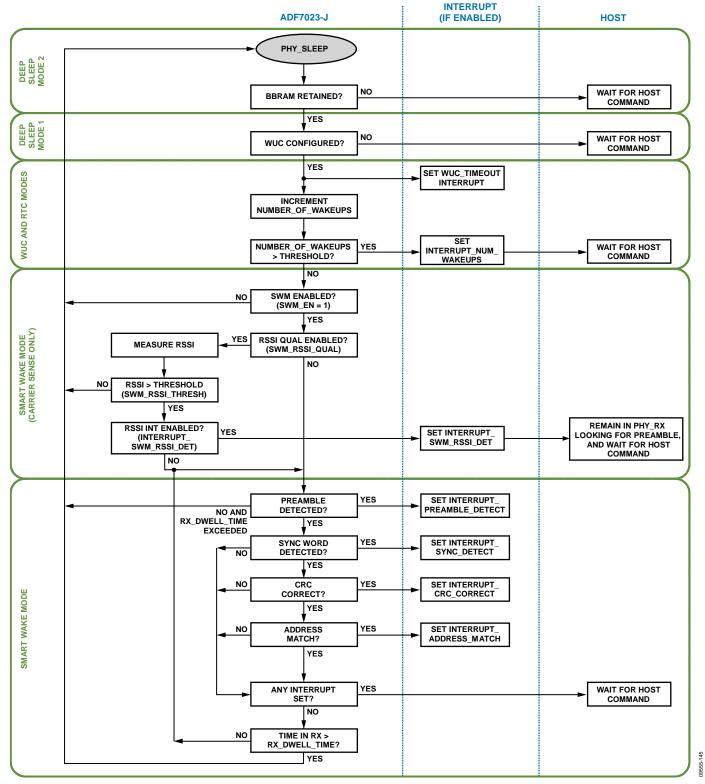

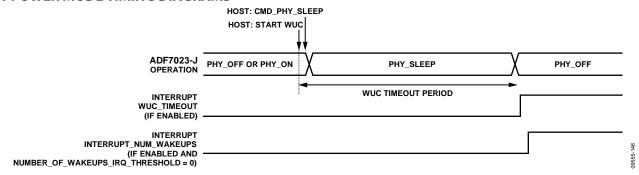

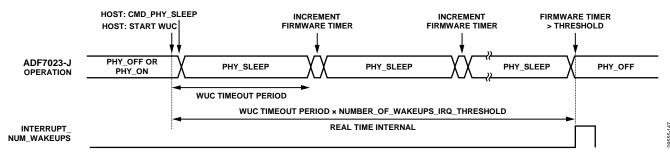

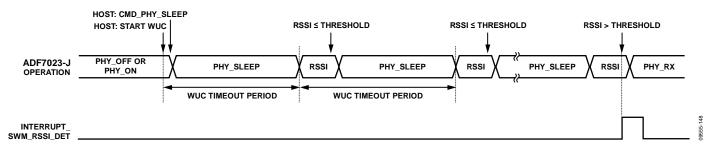

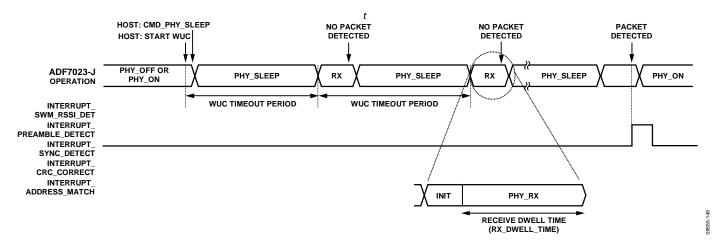

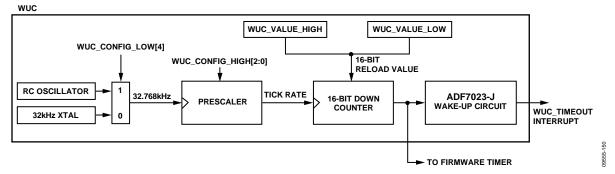

The SWM allows the ADF7023-J to wake up autonomously from sleep using the internal wake-up timer without intervention from the host processor. After wake-up, the ADF7023-J is controlled by the communications processor. This functionality allows carrier sense, packet sniffing, and packet reception while the host processor is in sleep, thereby reducing overall system current consumption. The smart wake mode can wake the host processor on an interrupt condition. These interrupt conditions can be configured to include the reception of valid preamble, sync word, CRC, or address match. Wake-up from sleep mode can also be triggered by the host processor. For systems requiring

very accurate wake-up timing, a 32 kHz oscillator can be used to drive the wake-up timer. Alternatively, the internal RC oscillator can be used, which gives lower current consumption in sleep.

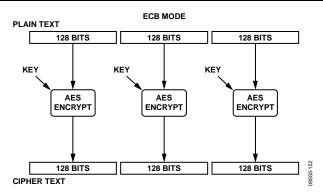

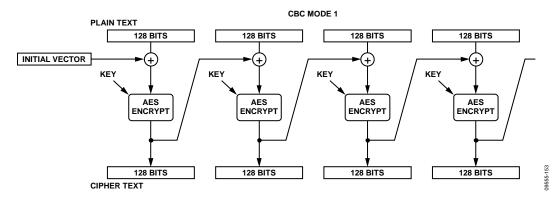

The ADF7023-J features an AES engine with hardware acceleration that provides 128-bit block encryption and decryption with key sizes of 128 bits, 192 bits, and 256 bits. Both electronic code book (ECB) and Cipher Block Chaining Mode 1 (CBC Mode 1) are supported. The AES engine can be used to encrypt/decrypt packet data and can be used as a standalone engine for encryption/decryption by the host processor. The AES engine is enabled on the ADF7023-J by downloading the AES firmware module to program RAM.

An on-chip, 8-bit ADC provides readback of an external analog input, the RSSI signal, or an integrated temperature sensor. An integrated battery voltage monitor raises an interrupt flag to the host processor whenever the battery voltage drops below a user-defined threshold.

# **SPECIFICATIONS**

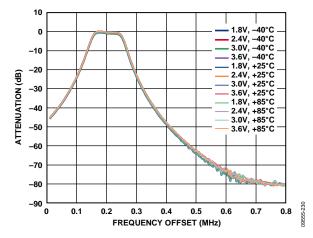

$V_{DD} = VDDBAT1 = VDDBAT2 = 2.2\ V\ to\ 3.6\ V, GND = 0\ V, T_A = T_{MIN}\ to\ T_{MAX}, unless\ otherwise\ noted.$  Typical specifications are at  $V_{\rm DD}=3~V$  and  $T_{\rm A}=25^{\circ}C$ .

#### RF AND SYNTHESIZER SPECIFICATIONS

Table 1.

| Parameter                                            | Min | Тур             | Max | Unit   | Test Conditions/Comments                                                                                                                                         |

|------------------------------------------------------|-----|-----------------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS                                   |     |                 |     |        |                                                                                                                                                                  |

| Frequency Range                                      | 902 |                 | 958 | MHz    |                                                                                                                                                                  |

| PHASE-LOCKED LOOP                                    |     |                 |     |        |                                                                                                                                                                  |

| Channel Frequency Resolution                         |     | 396.7           |     | Hz     |                                                                                                                                                                  |

| Phase Noise at Offset of                             |     |                 |     |        | PA output power = 10 dBm, RF frequency = 950 MHz                                                                                                                 |

| 600 kHz                                              |     | -116.3          |     | dBc/Hz | 130 kHz closed-loop bandwidth <sup>1</sup>                                                                                                                       |

| 800 kHz                                              |     | -119.4          |     | dBc/Hz | 130 kHz closed-loop bandwidth                                                                                                                                    |

| 600 kHz                                              |     | -113.8          |     | dBc/Hz | 223 kHz closed-loop bandwidth <sup>2</sup>                                                                                                                       |

| 800 kHz                                              |     | -117.2          |     | dBc/Hz | 223 kHz closed-loop bandwidth                                                                                                                                    |

| 1 MHz                                                |     | -126            |     | dBc/Hz |                                                                                                                                                                  |

| 2 MHz                                                |     | -131            |     | dBc/Hz |                                                                                                                                                                  |

| 10 MHz                                               |     | -142            |     | dBc/Hz |                                                                                                                                                                  |

| VCO Calibration Time                                 |     | 142             |     | μs     |                                                                                                                                                                  |

| Synthesizer Settling Time                            |     | 56              |     | μs     | Frequency synthesizer settles to within ±5 ppm of the target frequency within this time following the VCO calibration, transmit, and receive, 2FSK/GFSK/MSK/GMSK |

| Integer Boundary Spurious <sup>3</sup>               |     |                 |     |        | N = 35 or 36                                                                                                                                                     |

| $(26 \text{ MHz} \times \text{N}) + 0.1 \text{ MHz}$ |     | -39             |     | dBc    | Using 130 kHz synthesizer bandwidth, integer boundary spur at 910 MHz (26 MHz × 35), inside synthesizer loop bandwidth                                           |

| $(26 \text{ MHz} \times \text{N}) + 1.0 \text{ MHz}$ |     | <del>-</del> 79 |     | dBc    | Using 130 kHz synthesizer bandwidth, integer boundary spur at 910 MHz (26 MHz × 35), outside synthesizer loop bandwidth                                          |

| CRYSTAL OSCILLATOR                                   |     |                 |     |        |                                                                                                                                                                  |

| Crystal Frequency                                    |     | 26              |     | MHz    | Parallel load resonant crystal                                                                                                                                   |

| Recommended Load Capacitance                         | 7   |                 | 18  | pF     |                                                                                                                                                                  |

| Maximum Crystal ESR                                  |     | 1800            |     | Ω      | 26 MHz crystal with 18 pF load capacitance                                                                                                                       |

| Pin Capacitance                                      |     | 2.1             |     | pF     | Capacitance for XOSC26P and XOSC26N                                                                                                                              |

| Start-Up Time                                        |     | 310             |     | μs     | 26 MHz crystal with 7 pF load capacitance                                                                                                                        |

|                                                      |     | 388             |     | μs     | 26 MHz crystal with 18 pF load capacitance                                                                                                                       |

<sup>&</sup>lt;sup>1</sup> 130 kHz closed-loop bandwidth recommended for T96/15.4 g, 50 kbps and 100 kbps data rates (see Table 31).

$<sup>^2</sup>$  223 kHz closed-loop bandwidth recommended for T96/15.4 g, 200 kbps data rate (see Table 31).  $^3$  As the 26 MHz XTAL is fixed, integer boundary spurs occur at 910 MHz and 936 MHz (N = 35 and N = 36).

#### TRANSMITTER SPECIFICATIONS

Table 2.

| Parameter                                    | Min | Тур  | Max   | Unit | Test Conditions/Comments                                |

|----------------------------------------------|-----|------|-------|------|---------------------------------------------------------|

| DATA RATE                                    |     |      |       |      |                                                         |

| 2FSK/GFSK/MSK/GMSK                           | 1   |      | 300   | kbps |                                                         |

| Data Rate Resolution                         |     | 100  |       | bps  |                                                         |

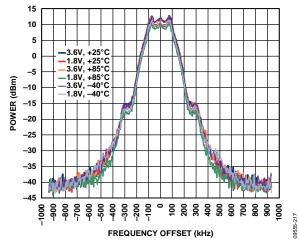

| MODULATION ERROR RATIO (MER) <sup>1</sup>    |     |      |       |      | RF frequency = 957.2 MHz, GFSK                          |

| 10 kbps to 49.5 kbps                         |     | 25.4 |       | dB   | Modulation index = 1                                    |

| 49.6 kbps to 129.5 kbps                      |     | 25.3 |       | dB   | Modulation index = 1                                    |

| 129.6 kbps to 179.1 kbps                     |     | 23.9 |       | dB   | Modulation index = 0.5                                  |

| 179.2 kbps to 239.9 kbps                     |     | 23.3 |       | dB   | Modulation index = 0.5                                  |

| 240 kbps to 300 kbps                         |     | 23   |       | dB   | Modulation index = 0.5                                  |

| MODULATION ERROR RATIO 15.4 g DATA RATES     |     |      |       |      | With T96 look-up table (LUT) <sup>2</sup>               |

| 50 kbps                                      |     | 25.4 |       | dB   | Modulation index = 1                                    |

| 100 kbps                                     |     | 28.9 |       | dB   | Modulation index = 1                                    |

| 200 kbps                                     |     | 25.9 |       | dB   | Modulation index = 1                                    |

| 100 kbps                                     |     | 24.3 |       | dB   | Modulation index = 0.5                                  |

| MODULATION                                   |     |      |       |      |                                                         |

| 2FSK/GFSK/MSK/GMSK Frequency Deviation       | 0.1 |      | 409.5 | kHz  |                                                         |

| Deviation Frequency Resolution               |     | 100  |       | Hz   |                                                         |

| Gaussian Filter Bandwidth-Time (BT) Product  |     | 0.5  |       |      |                                                         |

| SINGLE-ENDED PA                              |     |      |       |      |                                                         |

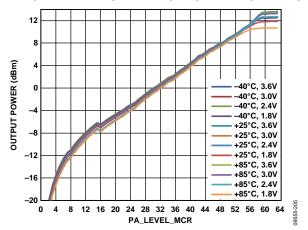

| Maximum Power <sup>3</sup>                   |     | 13.5 |       | dBm  | Programmable, separate PA and LNA match <sup>4</sup>    |

| Minimum Power                                |     | -20  |       | dBm  |                                                         |

| Transmit Power Variation vs. Temperature     |     | ±0.5 |       | dB   | From $-40$ °C to $+85$ °C, RF frequency = 958.0 MHz     |

| Transmit Power Variation vs. V <sub>DD</sub> |     | ±1   |       | dB   | From 2.2 V to 3.6 V, RF frequency = $958.0 \text{ MHz}$ |

| Transmit Power Flatness                      |     | ±1   |       | dB   | From 902 MHz to 928 MHz and 950 MHz to 958 MHz          |

| Programmable Step Size                       |     |      |       |      |                                                         |

| −20 dBm to +13.5 dBm                         |     | 0.5  |       | dB   | Programmable in 63 steps                                |

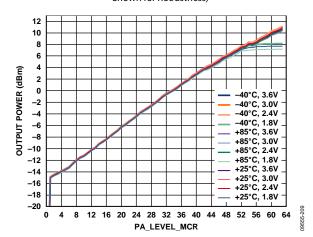

| DIFFERENTIAL PA                              |     |      |       |      |                                                         |

| Maximum Power <sup>3</sup>                   |     | 10   |       | dBm  | Programmable                                            |

| Minimum Power                                |     | -20  |       | dBm  |                                                         |

| Transmit Power Variation vs. Temperature     |     | ±1   |       | dB   | From $-40$ °C to $+85$ °C, RF frequency = 958.0 MHz     |

| Transmit Power Variation vs. VDD             |     | ±2   |       | dB   | From 2.2 V to 3.6 V, RF frequency = $958.0 \text{ MHz}$ |

| Transmit Power Flatness                      |     | ±1   |       | dB   | From 902 MHz to 928 MHz and 950 MHz to 958 MHz          |

| Programmable Step Size                       |     |      |       |      |                                                         |

| –20 dBm to +10 dBm                           |     | 0.5  |       | dB   | Programmable in 63 steps                                |

| Parameter                             | Min | Тур          | Max | Unit        | Test Conditions/Comments                                                                                                                                                                                                                                                                |

|---------------------------------------|-----|--------------|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPURIOUS EMISSIONS                    |     |              |     |             | Measured as per TELEC T-245 for T96 compliance, 950 MHz to 958 MHz band, single-ended PA with combined output. Fo spurious emissions compliance in the 1.8845 GHz to 1.9196 GHz frequency band, a seventh-order PA harmonic filter is used. This has an insertion loss of up to 1.5 dB. |

| 30 MHz to 710 MHz                     |     | -65          |     | dBm/100 kHz |                                                                                                                                                                                                                                                                                         |

| 710 MHz to 945 MHz                    |     | -63          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| 945 MHz to 950 MHz                    |     | -66          |     | dBm/100 kHz |                                                                                                                                                                                                                                                                                         |

| 958 MHz to 960 MHz                    |     | -60.7        |     | dBm/100 kHz | $DR = 100 \text{ kbps}, MI = 1, n = 2, f_C = 957.3 \text{ MHz}$                                                                                                                                                                                                                         |

| 960 MHz to 1 GHz                      |     | -64          |     | dBm/100 kHz |                                                                                                                                                                                                                                                                                         |

| 1 GHz to 1.215 GHz                    |     | -72          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| 1.215 GHz to 1.8845 GHz               |     | -76          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| 1.8845 GHz to 1.9196 GHz <sup>5</sup> |     | -69          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| 1.9196 GHz to 3 GHz                   |     | -66          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| 3 GHz to 5 GHz                        |     | -69          |     | dBm/1 MHz   |                                                                                                                                                                                                                                                                                         |

| OPTIMUM PA LOAD IMPEDANCE             |     |              |     |             |                                                                                                                                                                                                                                                                                         |

| Single-Ended PA in Transmit Mode      |     |              |     |             |                                                                                                                                                                                                                                                                                         |

| $f_{RF} = 915 \text{ MHz}$            |     | 50.8 + j10.2 |     | Ω           |                                                                                                                                                                                                                                                                                         |

| $f_{RF} = 954MHz$                     |     | 38.5 + j5.9  |     | Ω           |                                                                                                                                                                                                                                                                                         |

| Single-Ended PA in Receive Mode       |     |              |     |             | PA Impedance in Rx mode                                                                                                                                                                                                                                                                 |

| $f_{RF} = 915 \text{ MHz}$            |     | 9.4 – j124   |     | Ω           |                                                                                                                                                                                                                                                                                         |

| $f_{RF} = 954 \text{ MHz}$            |     | 8.8 – j118.5 |     | Ω           |                                                                                                                                                                                                                                                                                         |

| Differential PA in Transmit Mode      |     |              |     |             | Load impedance between RFIO_1P and RFIO_1N to ensure maximum output powe                                                                                                                                                                                                                |

| $f_{RF} = 915 \text{ MHz}$            |     | 20.5 + j36.4 |     | Ω           |                                                                                                                                                                                                                                                                                         |

| $f_{RF} = 954 \text{ MHz}$            |     | 28.1 + j17.3 |     | Ω           |                                                                                                                                                                                                                                                                                         |

<sup>&</sup>lt;sup>1</sup> MER is a measure of signal to noise ratio at optimal eye sampling point.

<sup>2</sup> Optimized PLL bandwidth settings vs. data rate defined in Table 31.

3 Measured as the maximum unmodulated power.

4 A combined single-ended PA and LNA match can reduce the maximum achievable output power by up to 1 dB.

5 This includes the second harmonic.

#### **RECEIVER SPECIFICATIONS**

Table 3.

| Parameter                                           | Min | Тур    | Max | Unit | Test Conditions/Comments                                                                                                     |

|-----------------------------------------------------|-----|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------|

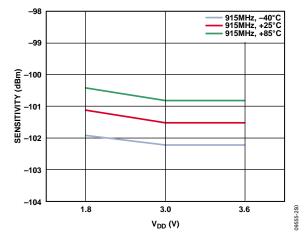

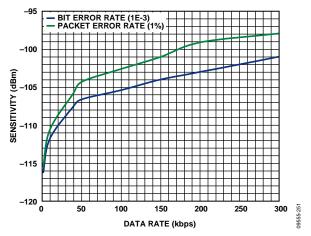

| 2FSK/MSK INPUT SENSITIVITY, BIT ERROR RATE (BER)    |     |        |     |      | At BER = 1E - 3, RF frequency = 915 MHz,<br>LNA and PA matched separately <sup>1</sup>                                       |

| 1.0 kbps                                            |     | -116   |     | dBm  | Frequency deviation = 4.8 kHz,<br>IF filter bandwidth = 100 kHz                                                              |

| 10 kbps                                             |     | -111   |     | dBm  | Frequency deviation = 9.6 kHz,<br>IF filter bandwidth = 100 kHz                                                              |

| 38.4 kbps                                           |     | -107.5 |     | dBm  | Frequency deviation = 20 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 50 kbps                                             |     | -106.5 |     | dBm  | Frequency deviation = 12.5 kHz,<br>IF filter bandwidth = 100 kHz                                                             |

| 100 kbps                                            |     | -105   |     | dBm  | Frequency deviation = 25 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 150 kbps                                            |     | -104   |     | dBm  | Frequency deviation = 37.5 kHz, IF filter bandwidth = 150 kHz                                                                |

| 200 kbps                                            |     | -103   |     | dBm  | Frequency deviation = 50 kHz,<br>IF filter bandwidth = 200 kHz                                                               |

| 300 kbps                                            |     | -100.5 |     | dBm  | Frequency deviation = 75 kHz, IF filter bandwidth = 300 kHz                                                                  |

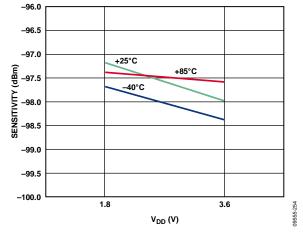

| GFSK/GMSK INPUT SENSITIVITY, BER                    |     |        |     |      | At BER = $1E - 3$ , RF frequency = $954$ MHz,<br>LNA and PA matched separately <sup>1</sup>                                  |

| 50 kbps                                             |     | -107.4 |     | dBm  | Frequency deviation = 25 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 100 kbps                                            |     | -105   |     | dBm  | Frequency deviation = 50 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 100 kbps                                            |     | -106   |     | dBm  | Frequency deviation = 40 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 200 kbps                                            |     | -102   |     | dBm  | Frequency deviation = 100 kHz,<br>IF filter bandwidth = 200 kHz                                                              |

| 200 kbps                                            |     | -103.3 |     | dBm  | Frequency deviation = 80 kHz,<br>IF filter bandwidth = 200 kHz                                                               |

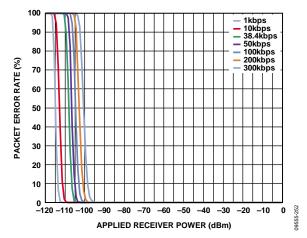

| 2FSK/MSK INPUT SENSITIVITY, PACKET ERROR RATE (PER) |     |        |     |      | At PER = 1%, RF frequency = 915 MHz,<br>LNA and PA matched separately, <sup>1</sup><br>packet length = 128 bits, packet mode |

| 1.0 kbps                                            |     | -115.5 |     | dBm  | Frequency deviation = 4.8 kHz,<br>IF filter bandwidth = 100 kHz                                                              |

| 9.6 kbps                                            |     | -110.6 |     | dBm  | Frequency deviation = 9.6 kHz,<br>IF filter bandwidth = 100 kHz                                                              |

| 38.4 kbps                                           |     | -106   |     | dBm  | Frequency deviation = 20 kHz,<br>IF filter bandwidth = 100 kHz                                                               |

| 50 kbps                                             |     | -104.3 |     | dBm  | Frequency deviation = 12.5 kHz,<br>IF filter bandwidth = 100 kHz                                                             |

| 100 kbps                                            |     | -102.6 |     | dBm  | Frequency deviation = 25 kHz, IF filter bandwidth = 100 kHz                                                                  |

| 150 kbps                                            |     | -101   |     | dBm  | Frequency deviation = 37.5 kHz, IF filter bandwidth = 150 kHz                                                                |

| 200 kbps                                            |     | -99.1  |     | dBm  | Frequency deviation = 50 kHz, IF filter bandwidth = 200 kHz                                                                  |

| 300 kbps                                            |     | -97.9  |     | dBm  | Frequency deviation = 75 kHz, IF filter bandwidth = 300 kHz                                                                  |

| Parameter                             | Min Typ | Max Unit | Test Conditions/Comments                                                                                                                                                                                                                                             |

|---------------------------------------|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

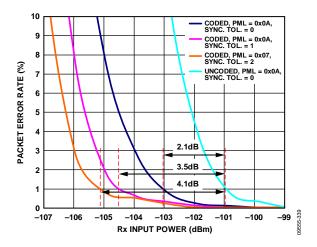

| GFSK/GMSK INPUT SENSITIVITY, PER      |         |          | At PER = 1%, RF frequency = 954 MHz,<br>LNA and PA matched separately,<br>packet length = 20 octets, packet mode                                                                                                                                                     |

| 50 kbps                               | -104.1  | dBm      | Frequency deviation = 25 kHz, IF filter bandwidth = 100 kHz                                                                                                                                                                                                          |

| 100 kbps                              | -101.1  | dBm      | Frequency deviation = 50 kHz, IF filter bandwidth = 100 kHz                                                                                                                                                                                                          |

| 100 kbps                              | -102.2  | dBm      | Frequency deviation = 40 kHz, IF filter bandwidth = 100 kHz                                                                                                                                                                                                          |

| 200 kbps                              | -98.5   | dBm      | Frequency deviation = 100 kHz, IF filter bandwidth = 200 kHz                                                                                                                                                                                                         |

| 200 kbps                              | -99.5   | dBm      | Frequency deviation = 80 kHz,<br>IF filter bandwidth = 200 kHz                                                                                                                                                                                                       |

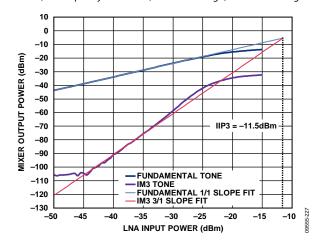

| LNA AND MIXER, INPUT IP3              |         |          | Receiver LO frequency ( $f_{LO}$ ) = 914.8 MHz,<br>$f_{SOURCE1} = f_{LO} + 0.4$ MHz, $f_{SOURCE2} = f_{LO} + 0.7$ MHz                                                                                                                                                |

| Minimum LNA Gain                      | -11.5   | dBm      | ·                                                                                                                                                                                                                                                                    |

| Maximum LNA Gain                      | -12.2   | dBm      |                                                                                                                                                                                                                                                                      |

| LNA AND MIXER, INPUT IP2              |         |          | Receiver LO frequency $(f_{LO}) = 920.8 \text{ MHz}$ ,<br>$f_{SOURCE1} = f_{LO} + 1.1 \text{ MHz}$ , $f_{SOURCE2} = f_{LO} + 1.3 \text{ MHz}$                                                                                                                        |

| Maximum LNA Gain, Maximum Mixer Gain  | 18.5    | dBm      |                                                                                                                                                                                                                                                                      |

| Minimum LNA Gain, Minimum Mixer Gain  | 27      | dBm      |                                                                                                                                                                                                                                                                      |

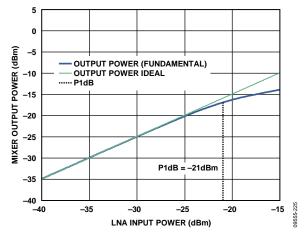

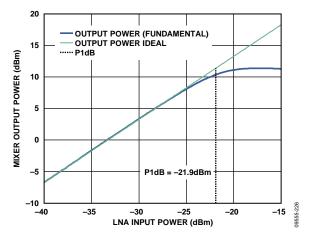

| LNA AND MIXER, 1 dB COMPRESSION POINT |         |          | RF frequency = 915 MHz                                                                                                                                                                                                                                               |

| Maximum LNA Gain, Maximum Mixer Gain  | -21.9   | dBm      |                                                                                                                                                                                                                                                                      |

| Minimum LNA Gain, Minimum Mixer Gain  | -21     | dBm      |                                                                                                                                                                                                                                                                      |

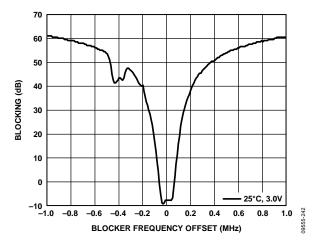

| ADJACENT CHANNEL REJECTION            |         |          |                                                                                                                                                                                                                                                                      |

| CW Interferer                         |         |          | Desired signal at –87 dBm, CW interferer power level increased until BER = 62 <sup>-6</sup> , image calibrated                                                                                                                                                       |

| ±200 kHz Offset                       | 38      | dB       | IF BW = 100 kHz, wanted signal:<br>$f_{DEV} = 25 \text{ kHz}$ , DR = 50 kbps                                                                                                                                                                                         |

| +400 kHz Offset                       | 51      | dB       |                                                                                                                                                                                                                                                                      |

| –400 kHz Offset                       | 33/39   | dB       | Uncalibrated/internal calibration; using an IF of 200 kHz, –400 kHz is the image frequency                                                                                                                                                                           |

| CO-CHANNEL REJECTION                  | -6      | dB       | Desired signal at –87 dBm,<br>data rate = 50 kbps,<br>frequency deviation = 25 kHz,<br>RF frequency = 954 MHz                                                                                                                                                        |

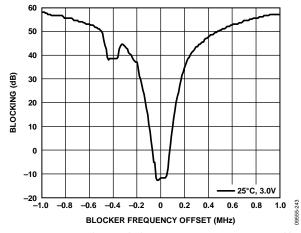

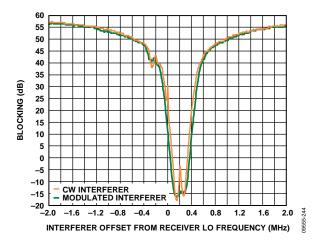

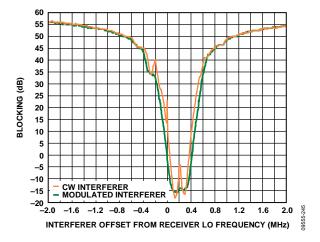

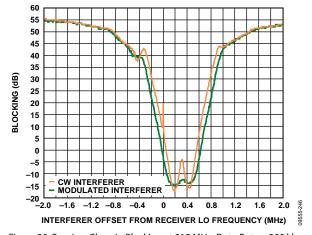

| BLOCKING                              |         |          |                                                                                                                                                                                                                                                                      |

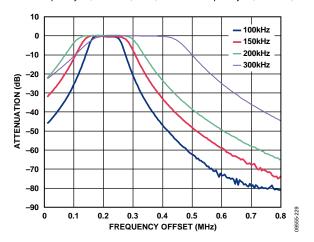

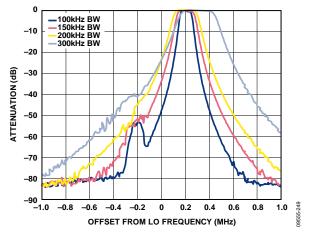

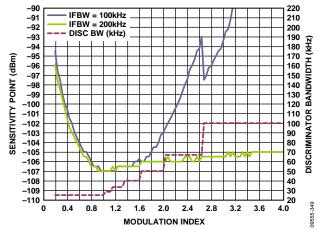

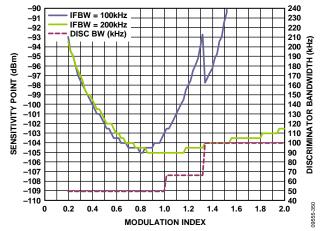

| RF Frequency = 954 MHz                |         |          | Desired signal 3 dB above the input sensitivity level, data rate = 50 kbps, CW interferer power level increased until BER = 10 <sup>-3</sup> (see the Typical Performance Characteristics section for blocking at other offsets and IF bandwidths), image calibrated |

| ±2 MHz                                | 65      | dB       |                                                                                                                                                                                                                                                                      |

| ±10 MHz                               | 72      | dB       |                                                                                                                                                                                                                                                                      |

| ±60 MHz                               | 76      | dB       |                                                                                                                                                                                                                                                                      |

| IMAGE CHANNEL ATTENUATION             |         |          | Measured as image attenuation at the IF filter output, carrier wave interferer at 400 kHz below the channel frequency, 100 kHz IF filter bandwidth                                                                                                                   |

| 954 MHz                               | 36/43.8 | dB       | Uncalibrated/calibrated                                                                                                                                                                                                                                              |

| プリヤ IVIITZ                            | 30/43.0 | uB       | Oncalibrated/Calibrated                                                                                                                                                                                                                                              |

| Parameter                                       | Min | Тур             | Max | Unit | <b>Test Conditions/Comments</b>                                                                            |

|-------------------------------------------------|-----|-----------------|-----|------|------------------------------------------------------------------------------------------------------------|

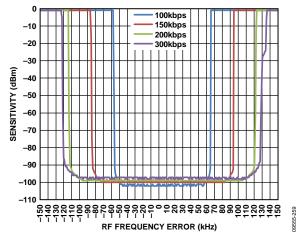

| AFC                                             |     |                 |     |      |                                                                                                            |

| Accuracy                                        |     | 1               |     | kHz  |                                                                                                            |

| Maximum Pull-In Range                           |     |                 |     |      | Achievable pull-in range dependent on discriminator bandwidth and modulation                               |

| 300 kHz IF Filter Bandwidth                     |     | ±150            |     | kHz  |                                                                                                            |

| 200 kHz IF Filter Bandwidth                     |     | ±100            |     | kHz  |                                                                                                            |

| 150 kHz IF Filter Bandwidth                     |     | ±75             |     | kHz  |                                                                                                            |

| 100 kHz IF Filter Bandwidth                     |     | ±50             |     | kHz  |                                                                                                            |

| PREAMBLE LENGTH                                 |     |                 |     |      | Minimum number of preamble bits to ensure the minimum PER across the full input power range (see Table 41) |

| AFC Off, AGC Lock on Sync Word Detection        |     |                 |     |      | Sync word length 24 bits                                                                                   |

| 38.4 kbps                                       |     | 8               |     | Bits | Sync word tolerance = 0                                                                                    |

| 300 kbps                                        |     | 24              |     | Bits | Sync word tolerance = 1                                                                                    |

| AFC On, AFC and AGC Lock on Preamble Detection  |     |                 |     |      |                                                                                                            |

| 9.6 kbps                                        |     | 46              |     | Bits |                                                                                                            |

| 38.4 kbps                                       |     | 44              |     | Bits |                                                                                                            |

| 50 kbps                                         |     | 50              |     | Bits |                                                                                                            |

| 100 kbps                                        |     | 52              |     | Bits |                                                                                                            |

| 150 kbps                                        |     | 54              |     | Bits |                                                                                                            |

| 200 kbps                                        |     | 58              |     | Bits |                                                                                                            |

| 300 kbps                                        |     | 64              |     | Bits |                                                                                                            |

| AFC On, AFC and AGC Lock on Sync Word Detection |     |                 |     |      | Sync word length 24 bits                                                                                   |

| 38.4 kbps                                       |     | 14              |     | Bits | Sync word tolerance = 0                                                                                    |

| 300 kbps                                        |     | 32              |     | Bits | Sync word tolerance = 1                                                                                    |

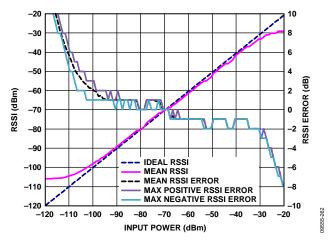

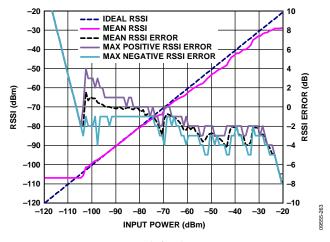

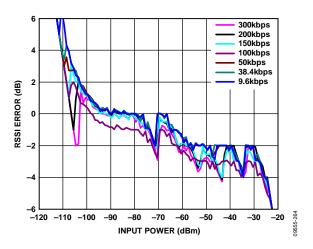

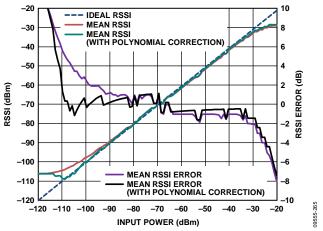

| RSSI                                            |     |                 |     |      |                                                                                                            |

| Range at Input                                  |     | −97 to −26      |     | dBm  |                                                                                                            |

| Linearity                                       |     | ±2              |     | dB   |                                                                                                            |

| Absolute Accuracy                               |     | ±3              |     | dB   |                                                                                                            |

| SATURATION (MAXIMUM INPUT LEVEL)                |     |                 |     |      |                                                                                                            |

| 2FSK/GFSK/MSK/GMSK                              |     | 12              |     | dBm  |                                                                                                            |

| LNA INPUT IMPEDANCE                             |     |                 |     |      |                                                                                                            |

| Receive Mode                                    |     |                 |     |      |                                                                                                            |

| $f_{RF} = 915 \text{ MHz}$                      |     | 75.9 –<br>j32.3 |     | Ω    |                                                                                                            |

| $f_{RF} = 954 \text{ MHz}$                      |     | 74.6 –<br>j32.5 |     | Ω    |                                                                                                            |

| Transmit Mode                                   |     |                 |     |      |                                                                                                            |

| $f_{RF} = 915 \text{ MHz}$                      |     | 7.7 + j8.6      |     | Ω    |                                                                                                            |

| $f_{RF} = 954 \text{ MHz}$                      |     | 7.7 + j8.9      |     | Ω    |                                                                                                            |

| Rx SPURIOUS EMISSIONS <sup>2</sup>              |     | <u>-</u>        |     |      |                                                                                                            |

| Maximum < 1 GHz                                 |     | -66             |     | dBm  | At antenna input, unfiltered conductive                                                                    |

| Maximum > 1 GHz                                 |     | -62             |     | dBm  | At antenna input, unfiltered conductive                                                                    |

$<sup>^1</sup>$  Sensitivity for combined matching network case is typically 1 dB less than separate matching networks.  $^2$  Follow the matching and layout guidelines to achieve the relevant ARIB-T96/TELEC T-245 specifications.

## **TIMING AND DIGITAL SPECIFICATIONS**

#### Table 4.

| Parameter                                         | Min                 | Тур             | Max                 | Unit | Test Conditions/Comments                                                       |

|---------------------------------------------------|---------------------|-----------------|---------------------|------|--------------------------------------------------------------------------------|

| Rx AND Tx TIMING PARAMETERS                       |                     |                 |                     |      | See the State Transition and Command                                           |

|                                                   |                     |                 |                     |      | Timing section for more details                                                |

| PHY_ON to PHY_RX (on CMD_PHY_RX)                  |                     | 300             |                     | μs   | Includes VCO calibration and synthesizer settling                              |

| PHY_ON to PHY_TX (on CMD_PHY_TX)                  |                     | 296             |                     | μs   | Includes VCO calibration and synthesizer settling, does not include PA ramp-up |

| LOGIC INPUTS                                      |                     |                 |                     |      |                                                                                |

| Input High Voltage, V <sub>INH</sub>              | $0.7 \times V_{DD}$ |                 |                     | V    |                                                                                |

| Input Low Voltage, V <sub>INL</sub>               |                     |                 | $0.2 \times V_{DD}$ | V    |                                                                                |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> |                     |                 | ±1                  | μΑ   |                                                                                |

| Input Capacitance, C <sub>IN</sub>                |                     |                 | 10                  | рF   |                                                                                |

| LOGIC OUTPUTS                                     |                     |                 |                     |      |                                                                                |

| Output High Voltage, V <sub>OH</sub>              | $V_{\text{DD}}-0.4$ |                 |                     | V    | $I_{OH} = 500  \mu A$                                                          |

| Output Low Voltage, V <sub>OL</sub>               |                     |                 | 0.4                 | V    | $I_{OL} = 500 \mu\text{A}$                                                     |

| GPIO Rise/Fall                                    |                     |                 | 5                   | ns   |                                                                                |

| GPIO Load                                         |                     |                 | 10                  | рF   |                                                                                |

| Maximum Output Current                            |                     | 5               |                     | mA   |                                                                                |

| ATB OUTPUTS                                       |                     |                 |                     |      | Used for external PA and LNA control                                           |

| ADCIN_ATB3 and ATB4                               |                     |                 |                     |      |                                                                                |

| Output High Voltage, V <sub>OH</sub>              |                     | 1.8             |                     | V    |                                                                                |

| Output Low Voltage, Vol                           |                     | 0.1             |                     | V    |                                                                                |

| Maximum Output Current                            |                     | 0.5             |                     | mA   |                                                                                |

| XOSC32KP_GP5_ATB1 and XOSC32KN_ATB2               |                     |                 |                     |      |                                                                                |

| Output High Voltage, V <sub>OH</sub>              |                     | $V_{\text{DD}}$ |                     | V    |                                                                                |

| Output Low Voltage, Vol                           |                     | 0.1             |                     | V    |                                                                                |

| Maximum Output Current                            |                     | 5               |                     | mA   |                                                                                |

## **AUXILARY BLOCK SPECIFICATIONS**

Table 5.

| Parameter                        | Min                 | Тур    | Max                  | Unit     | Test Conditions/Comments                                   |

|----------------------------------|---------------------|--------|----------------------|----------|------------------------------------------------------------|

| 32 kHz RC OSCILLATOR             |                     |        |                      |          |                                                            |

| Frequency                        |                     | 32.768 |                      | kHz      | After calibration                                          |

| Frequency Accuracy               |                     | 1.5    |                      | %        | After calibration at 25°C                                  |

| Frequency Drift                  |                     |        |                      |          |                                                            |

| Temperature Coefficient          |                     | 0.14   |                      | %/°C     |                                                            |

| Voltage Coefficient              |                     | 4      |                      | %/V      |                                                            |

| Calibration Time                 |                     | 1.25   |                      | ms       |                                                            |

| 32 kHz XTAL OSCILLATOR           |                     |        |                      |          |                                                            |

| Frequency                        |                     | 32.768 |                      | kHz      |                                                            |

| Start-Up Time                    |                     | 630    |                      | ms       | 32.768 kHz crystal with 7 pF load capacitance              |

| WAKE UP CONTROLLER (WUC)         |                     |        |                      |          |                                                            |

| Hardware Timer                   |                     |        |                      |          |                                                            |

| Wake-Up Period                   | $61 \times 10^{-6}$ |        | $1.31 \times 10^{5}$ | sec      |                                                            |

| Firmware Timer                   |                     |        |                      |          |                                                            |

| Wake-Up Period                   | 1                   |        | 2 <sup>16</sup>      | Hardware | Firmware counter counts of the number of                   |

|                                  |                     |        |                      | periods  | hardware wake-ups, resolution of 16 bits                   |

| ADC                              |                     |        |                      |          | Maximum input voltage at ADCIN_ATB3 is 1.8 V               |

| Resolution                       |                     | 8      |                      | Bits     |                                                            |

| DNL                              |                     | ±1     |                      | LSB      | $V_{DD}$ from 2.2 V to 3.6 V, $T_A = 25$ °C                |

| INL                              |                     | ±1     |                      | LSB      | $V_{DD}$ from 2.2 V to 3.6 V, $T_A = 25$ °C                |

| Conversion Time                  |                     | 1      |                      | μs       |                                                            |

| Input Capacitance                |                     | 12.4   |                      | pF       |                                                            |

| BATTERY MONITOR                  |                     |        |                      |          |                                                            |

| Absolute Accuracy                |                     | ±45    |                      | mV       |                                                            |

| Alarm Voltage Setpoint           | 1.7                 |        | 2.7                  | V        |                                                            |

| Alarm Voltage Step Size          |                     | 62     |                      | mV       | 5-bit resolution                                           |

| Start-Up Time                    |                     |        | 100                  | μs       |                                                            |

| Current Consumption              |                     | 30     |                      | μΑ       | When enabled                                               |

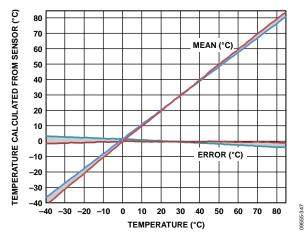

| TEMPERATURE SENSOR               |                     |        |                      |          |                                                            |

| Range                            | -40                 |        | +85                  | °C       |                                                            |

| Resolution                       |                     | 0.3    |                      | °C       | With averaging                                             |

| Accuracy of Temperature Readback |                     | +7/-4  |                      | ℃        | Overtemperature range -40°C to +85°C (calibrated at +25°C) |

|                                  |                     | ±4     |                      | °C       | Overtemperature range –36°C to +84°C (calibrated at +25°C) |

|                                  |                     | ±3     |                      | °C       | Overtemperature range –12°C to +79°C (calibrated at +25°C) |

#### **GENERAL SPECIFICATIONS**

### Table 6.

| Parameter                     | Min | Тур   | Max | Unit | Test Conditions/Comments                                                                                                                                                               |

|-------------------------------|-----|-------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMPERATURE RANGE, TA         | -40 |       | +85 | °C   |                                                                                                                                                                                        |

| VOLTAGE SUPPLY                |     |       |     |      |                                                                                                                                                                                        |