# Contents

| 1 | Desci                                                                                                                                                      | ription                                                                                                                                                                                                                                                                                                         |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Signa                                                                                                                                                      | Il description                                                                                                                                                                                                                                                                                                  |

|   | 2.1                                                                                                                                                        | Serial Data output (Q)                                                                                                                                                                                                                                                                                          |

|   | 2.2                                                                                                                                                        | Serial Data input (D)                                                                                                                                                                                                                                                                                           |

|   | 2.3                                                                                                                                                        | Serial Clock (C)                                                                                                                                                                                                                                                                                                |

|   | 2.4                                                                                                                                                        | Chip Select (S) 8                                                                                                                                                                                                                                                                                               |

|   | 2.5                                                                                                                                                        | Hold (HOLD)                                                                                                                                                                                                                                                                                                     |

|   | 2.6                                                                                                                                                        | Write Protect (W)                                                                                                                                                                                                                                                                                               |

|   | 2.7                                                                                                                                                        | V <sub>SS</sub> ground                                                                                                                                                                                                                                                                                          |

|   | 2.8                                                                                                                                                        | Supply voltage (V <sub>CC</sub> )                                                                                                                                                                                                                                                                               |

|   | 2.9                                                                                                                                                        | Supply voltage (V <sub>CC</sub> )                                                                                                                                                                                                                                                                               |

|   |                                                                                                                                                            | 2.9.1 Operating supply voltage V <sub>CC</sub>                                                                                                                                                                                                                                                                  |

|   |                                                                                                                                                            | 2.9.2 Device reset                                                                                                                                                                                                                                                                                              |

|   |                                                                                                                                                            | 2.9.3 Power-up conditions                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                                                            | 2.9.4 Power-down                                                                                                                                                                                                                                                                                                |

|   |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| 3 | Conn                                                                                                                                                       | ecting to the SPI bus11                                                                                                                                                                                                                                                                                         |

| 3 | <b>Conn</b><br>3.1                                                                                                                                         | ecting to the SPI bus                                                                                                                                                                                                                                                                                           |

| 3 | 3.1                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                               |

| - | 3.1                                                                                                                                                        | SPI modes                                                                                                                                                                                                                                                                                                       |

| - | 3.1<br><b>Opera</b>                                                                                                                                        | SPI modes       12         ating features       13                                                                                                                                                                                                                                                              |

| - | 3.1<br><b>Opera</b><br>4.1                                                                                                                                 | SPI modes       12         ating features       13         Hold condition       13                                                                                                                                                                                                                              |

| - | <ul> <li>3.1</li> <li><b>Opera</b></li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul>                                                                       | SPI modes    12      ating features    13      Hold condition    13      Status register    13                                                                                                                                                                                                                  |

| 4 | <ul> <li>3.1</li> <li><b>Opera</b></li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Memo</li> </ul>                                                         | SPI modes       12         ating features       13         Hold condition       13         Status register       13         Data protection and protocol control       14                                                                                                                                       |

| 4 | <ul> <li>3.1</li> <li><b>Opera</b></li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>Memo</li> </ul>                                                         | SPI modes       12         ating features       13         Hold condition       13         Status register       13         Data protection and protocol control       14         ory organization       15                                                                                                     |

| 4 | 3.1<br>Opera<br>4.1<br>4.2<br>4.3<br>Memo                                                                                                                  | SPI modes12ating features13Hold condition13Status register13Data protection and protocol control14ory organization15actions16                                                                                                                                                                                   |

| 4 | 3.1<br>Opera<br>4.1<br>4.2<br>4.3<br>Memo<br>6.1                                                                                                           | SPI modes       12         ating features       13         Hold condition       13         Status register       13         Data protection and protocol control       14         ory organization       15         actions       16         Write Enable (WREN)       16                                       |

| 4 | <ul> <li>3.1</li> <li><b>Opera</b></li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li><b>Memo</b></li> <li><b>Instru</b></li> <li>6.1</li> <li>6.2</li> </ul> | SPI modes       12         ating features       13         Hold condition       13         Status register       13         Data protection and protocol control       14         ory organization       15         attions       16         Write Enable (WREN)       16         Write Disable (WRDI)       17 |

|    |        | 6.3.3 BP1, BP0 bits              |

|----|--------|----------------------------------|

|    | 6.4    | Write Status Register (WRSR) 20  |

|    | 6.5    | Read from Memory Array (READ) 22 |

|    | 6.6    | Write to Memory Array (WRITE) 23 |

| 7  | Powe   | r-up and delivery states 25      |

|    | 7.1    | Power-up state                   |

|    | 7.2    | Initial delivery state           |

| 8  | Maxir  | num rating                       |

| 9  | DC ar  | nd AC parameters 27              |

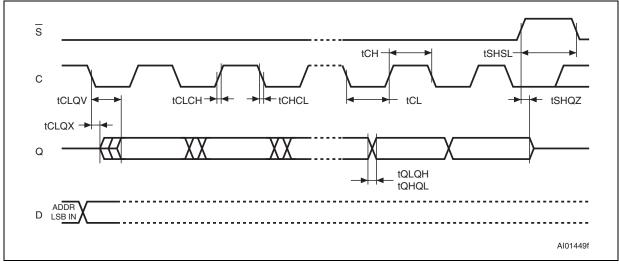

| 10 | Packa  | age mechanical data 37           |

| 11 | Part r | numbering                        |

| 12 | Revis  | ion history                      |

# List of tables

| Table 1.  | Device summary                                                        | 1   |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2.  | Signal names                                                          | 7   |

| Table 3.  | Write-protected block size 1                                          | 4   |

| Table 4.  | Instruction set                                                       | 6   |

| Table 5.  | Status register format                                                | 8   |

| Table 6.  | Address range bits                                                    | 2   |

| Table 7.  | Absolute maximum ratings 2                                            |     |

| Table 8.  | Operating conditions (M950x0)                                         |     |

| Table 9.  | Operating conditions (M950x0-W) 2                                     |     |

| Table 10. | Operating conditions (M950x0-R)2                                      | 27  |

| Table 11. | AC test measurement conditions 2                                      | 27  |

| Table 12. | Capacitance                                                           |     |

| Table 13. | DC characteristics (M950x0, device grade 3)2                          |     |

| Table 14. | DC characteristics (M950x0-W, device grade 6) 2                       |     |

| Table 15. | DC characteristics (M950x0-W, device grade 3) 3                       |     |

| Table 16. | DC characteristics (M950x0-R, device grade 6)                         |     |

| Table 17. | AC characteristics (M950x0, device grade 3)                           |     |

| Table 18. | AC characteristics (M950x0-W, device grade 6)                         |     |

| Table 19. | AC characteristics (M950x0-W, device grade 3)                         |     |

| Table 20. | AC characteristics (M950x0-R, device grade 6)                         | \$4 |

| Table 21. | SO8N — 8-lead plastic small outline, 150 mils body width, package     |     |

|           | mechanical data                                                       |     |

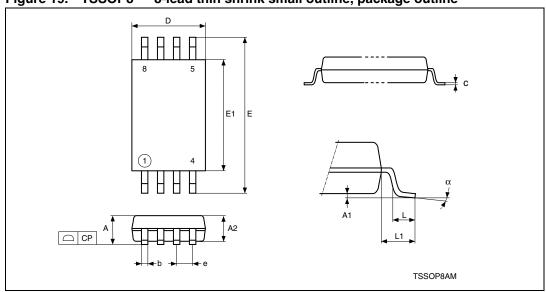

| Table 22. | TSSOP8 — 8-lead thin shrink small outline, package mechanical data    | 8   |

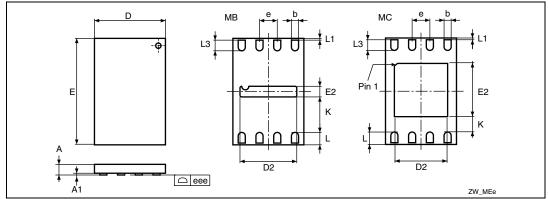

| Table 23. | UFDFPN8 (MLP8) 8-lead ultra thin fine pitch dual flat package no lead |     |

|           | 2 × 3mm, data                                                         |     |

| Table 24. | Ordering information scheme                                           |     |

| Table 25. | Document revision history4                                            | 1   |

|           |                                                                       |     |

# List of figures

| Figure 1   |                                                                          |

|------------|--------------------------------------------------------------------------|

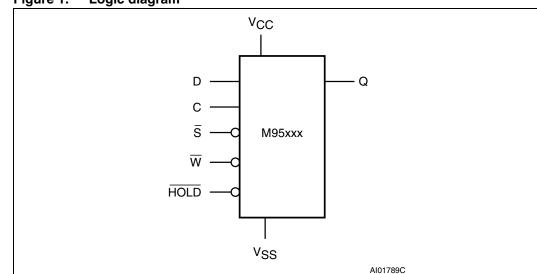

| Figure 1.  | Logic diagram                                                            |

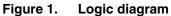

| Figure 2.  | 8-pin package connections                                                |

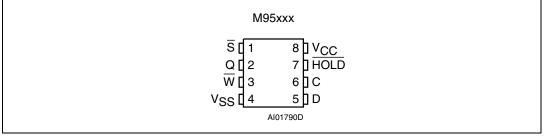

| Figure 3.  | Bus master and memory devices on the SPI bus                             |

| Figure 4.  | SPI modes supported                                                      |

| Figure 5.  | Hold condition activation                                                |

| Figure 6.  | Block diagram                                                            |

| Figure 7.  | Write Enable (WREN) sequence                                             |

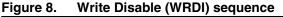

| Figure 8.  | Write Disable (WRDI) sequence                                            |

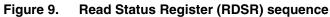

| Figure 9.  | Read Status Register (RDSR) sequence 19                                  |

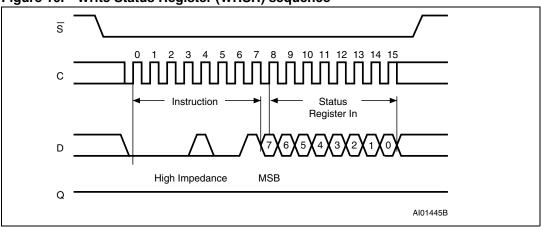

| Figure 10. | Write Status Register (WRSR) sequence                                    |

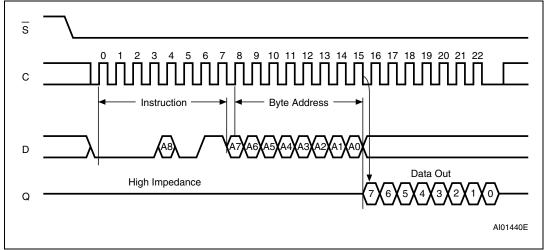

| Figure 11. | Read from Memory Array (READ) sequence                                   |

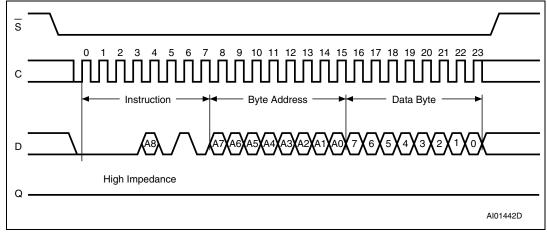

| Figure 12. | Byte Write (WRITE) sequence                                              |

| Figure 13. | Page Write (WRITE) sequence                                              |

| Figure 14. | AC test measurement I/O waveform                                         |

| Figure 15. | Serial input timing                                                      |

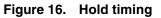

| Figure 16. | Hold timing                                                              |

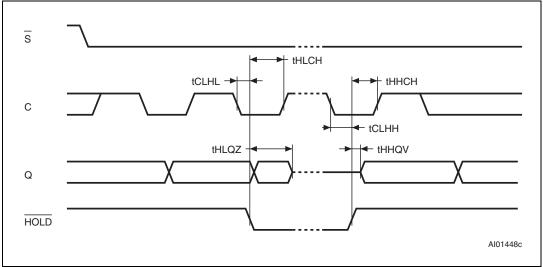

| Figure 17. | Serial output timing                                                     |

| Figure 18. | SO8N — 8-lead plastic small outline 150 mils body width, package outline |

| Figure 19. | TSSOP8 — 8-lead thin shrink small outline, package outline               |

| Figure 20. | UFDFPN8 (MLP8) 8-lead ultra thin fine pitch dual flat package no lead    |

| -          | 2 × 3mm, outline                                                         |

## 1 Description

The M95040 is a 4 Kbit (512 x 8) electrically erasable programmable memory (EEPROM), accessed by a high-speed SPI-compatible bus. The other members of the family (M95020 and M95010) are identical, though proportionally smaller (2 and 1 Kbit, respectively).

Each device is accessed by a simple serial interface that is SPI-compatible. The bus signals are C, D and Q.

The device is selected when Chip Select ( $\overline{S}$ ) is taken low. Communications with the device can be interrupted using Hold (HOLD). WRITE instructions are disabled by Write Protect ( $\overline{W}$ ).

1. See Section 10: Package mechanical data for package dimensions, and how to identify pin-1.

| Signal name     | Function           |

|-----------------|--------------------|

| С               | Serial Clock       |

| D               | Serial Data input  |

| Q               | Serial Data output |

| S               | Chip Select        |

| W               | Write Protect      |

| HOLD            | Hold               |

| V <sub>CC</sub> | Supply voltage     |

| V <sub>SS</sub> | Ground             |

#### Table 2.Signal names

## 2 Signal description

During all operations,  $V_{CC}$  must be held stable and within the specified valid range:  $V_{CC}$ (min) to  $V_{CC}$ (max).

All of the input and output signals can be held high or low (according to voltages of  $V_{IH}$ ,  $V_{OH}$ ,  $V_{IL}$  or  $V_{OL}$ , as specified in *Table 13: DC characteristics (M950x0, device grade 3)* to *Table 16: DC characteristics (M950x0-R, device grade 6)*). These signals are described next.

## 2.1 Serial Data output (Q)

This output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of Serial Clock (C).

### 2.2 Serial Data input (D)

This input signal is used to transfer data serially into the device. It receives instructions, addresses, and the data to be written. Values are latched on the rising edge of Serial Clock (C).

### 2.3 Serial Clock (C)

This input signal provides the timing of the serial interface. Instructions, addresses, or data present at Serial Data Input (D) are latched on the rising edge of Serial Clock (C). Data on Serial Data Output (Q) changes after the falling edge of Serial Clock (C).

## 2.4 Chip Select $(\overline{S})$

When this input signal is high, the device is deselected and Serial Data Output (Q) is at high impedance. Unless an internal Write cycle is in progress, the device will be in the Standby Power mode. Driving Chip Select  $(\overline{S})$  low selects the device, placing it in the Active Power mode.

After Power-up, a falling edge on Chip Select  $(\overline{S})$  is required prior to the start of any instruction.

## 2.5 Hold (HOLD)

The Hold (HOLD) signal is used to pause any serial communications with the device without deselecting the device.

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don't Care.

To start the Hold condition, the device must be selected, with Chip Select ( $\overline{S}$ ) driven low.

## 2.6 Write Protect ( $\overline{W}$ )

This input signal is used to control whether the memory is write protected. When Write Protect  $(\overline{W})$  is held low, writes to the memory are disabled, but other operations remain enabled. Write Protect  $(\overline{W})$  must either be driven high or low, but must not be left floating.

## 2.7 V<sub>SS</sub> ground

$V_{SS}$  is the reference for the  $V_{CC}$  supply voltage.

## 2.8 Supply voltage (V<sub>CC</sub>)

## 2.9 Supply voltage (V<sub>CC</sub>)

## 2.9.1 Operating supply voltage V<sub>CC</sub>

Prior to selecting the memory and issuing instructions to it, a valid and stable  $V_{CC}$  voltage within the specified [ $V_{CC}$ (min),  $V_{CC}$ (max)] range must be applied (see *Table 8: Operating conditions (M950x0), Table 9: Operating conditions (M950x0-W)* and *Table 10: Operating conditions (M950x0-R)*). This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal write cycle ( $t_W$ ). In order to secure a stable DC supply voltage, it is recommended to decouple the  $V_{CC}$  line with a suitable capacitor (usually of the order of 10 nF to 100 nF) close to the  $V_{CC}/V_{SS}$  package pins.

### 2.9.2 Device reset

In order to prevent inadvertent write operations during power-up, a power-on-reset (POR) circuit is included. At power-up, the device does not respond to any instruction until  $V_{CC}$  reaches the internal reset threshold voltage (this threshold is defined in *Table 8: Operating conditions (M950x0), Table 9: Operating conditions (M950x0-W)* and *Table 10: Operating conditions (M950x0-R)* as  $V_{RES}$ ).

When  $V_{CC}$  passes over the POR threshold, the device is reset and is in the following state:

- in Standby Power mode

- deselected (note that, to be executed, an instruction must be preceded by a falling edge on Chip Select (S))

- Status register value:

- the Write Enable Latch (WEL) is reset to 0

- Write In Progress (WIP) is reset to 0

- The SRWD, BP1 and BP0 bits remain unchanged (non-volatile bits)

When  $V_{CC}$  passes over the POR threshold, the device is reset and enters the Standby Power mode. The device must not be accessed until  $V_{CC}$  reaches a valid and stable  $V_{CC}$ voltage within the specified [ $V_{CC}$ (min),  $V_{CC}$ (max)] range defined in *Table 8: Operating conditions (M950x0), Table 9: Operating conditions (M950x0-W)* and *Table 10: Operating conditions (M950x0-R)*.

### 2.9.3 Power-up conditions

When the power supply is turned on,  $V_{CC}$  rises continuously from  $V_{SS}$  to  $V_{CC}$ . During this time, the Chip Select ( $\overline{S}$ ) line is not allowed to float but should follow the  $V_{CC}$  voltage. It is therefore recommended to connect the  $\overline{S}$  line to  $V_{CC}$  via a suitable pull-up resistor (see *Figure 3: Bus master and memory devices on the SPI bus*).

In addition, the Chip Select  $(\overline{S})$  input offers a built-in safety feature, as the  $\overline{S}$  input is edge sensitive as well as level sensitive: after power-up, the device does not become selected until a falling edge has first been detected on Chip Select  $(\overline{S})$ . This ensures that Chip Select  $(\overline{S})$  must have been high, prior to going low to start the first operation.

The V<sub>CC</sub> voltage has to rise continuously from 0 V up to the minimum V<sub>CC</sub> operating voltage defined in *Table 8: Operating conditions (M950x0), Table 9: Operating conditions (M950x0-W)* and *Table 10: Operating conditions (M950x0-R)* and the rise time must not vary faster than 1 V/µs.

### 2.9.4 Power-down

During power-down (continuous decrease in the V<sub>CC</sub> supply voltage below the minimum V<sub>CC</sub> operating voltage defined in *Table 8: Operating conditions (M950x0), Table 9: Operating conditions (M950x0-W)* and *Table 10: Operating conditions (M950x0-R)*), the device must be:

- deselected (Chip Select S should be allowed to follow the voltage applied on V<sub>CC</sub>)

- in Standby Power mode (there should not be any internal write cycle in progress).

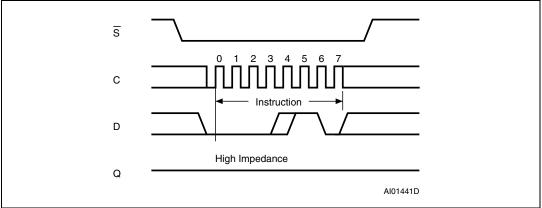

## 3 Connecting to the SPI bus

The device is fully compatible with the SPI protocol.

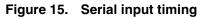

All instructions, addresses and input data bytes are shifted in to the device, most significant bit first. The Serial Data Input (D) is sampled on the first rising edge of the Serial Clock (C) after Chip Select  $(\overline{S})$  goes low.

All output data bytes are shifted out of the device, most significant bit first. The Serial Data Output (Q) is latched on the first falling edge of the Serial Clock (C) after the instruction (such as the Read from Memory Array and Read Status Register instructions) have been clocked into the device.

*Figure 3: Bus master and memory devices on the SPI bus* shows an example of three memory devices connected to an MCU, on an SPI bus. Only one memory device is selected at a time, so only one memory device drives the Serial Data output (Q) line at a time, the other memory devices are high impedance.

The pull-up resistor R (represented in *Figure 3: Bus master and memory devices on the SPI bus*) ensures that a device is not selected if the bus master leaves the S line in the high impedance state.

In applications where the bus master might enter a state where all SPI bus inputs/outputs would be in high impedance at the same time (for example, if the bus master is reset during the transmission of an Instruction), the clock line (C) must be connected to an external pull-down resistor so that, if all inputs/outputs become high impedance, the C line is pulled low (while the  $\overline{S}$  line is pulled high): this ensures that  $\overline{S}$  and C do not become high at the same time, and so, that the t<sub>SHCH</sub> requirement is met. The typical value of R is 100 k $\Omega$

Figure 3. Bus master and memory devices on the SPI bus

1. The Write Protect ( $\overline{W}$ ) and Hold ( $\overline{HOLD}$ ) signals should be driven, high or low as appropriate.

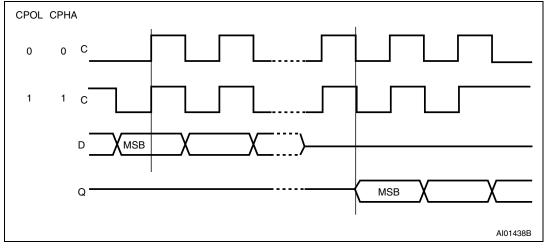

### 3.1 SPI modes

The device can be driven by a microcontroller with its SPI peripheral running in either of the two following modes:

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from the falling edge of Serial Clock (C).

The difference between the two modes, as shown in *Figure 4: SPI modes supported*, is the clock polarity when the bus master is in Stand-by mode and not transferring data:

- C remains at 0 for (CPOL=0, CPHA=0)

- C remains at 1 for (CPOL=1, CPHA=1)

#### Figure 4. SPI modes supported

12/44

## 4 **Operating features**

### 4.1 Hold condition

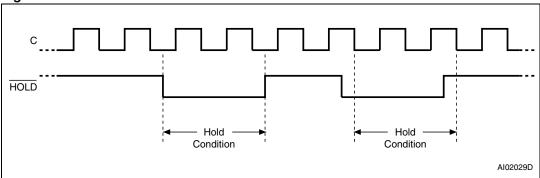

The Hold (HOLD) signal is used to pause any serial communications with the device without resetting the clocking sequence.

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don't Care.

To enter the Hold condition, the device must be selected, with Chip Select  $(\overline{S})$  low.

Normally, the device is kept selected, for the whole duration of the Hold condition. Deselecting the device while it is in the Hold condition has the effect of resetting the state of the device, and this mechanism can be used if it is required to reset any processes that had been in progress.

The Hold condition starts when the Hold ( $\overline{HOLD}$ ) signal is driven low at the same time as Serial Clock (C) already being low (as shown in *Figure 5: Hold condition activation*).

The Hold condition ends when the Hold ( $\overline{HOLD}$ ) signal is driven high at the same time as Serial Clock (C) already being low.

*Figure 5: Hold condition activation* also shows what happens if the rising and falling edges are not timed to coincide with Serial Clock (C) being low.

Figure 5. Hold condition activation

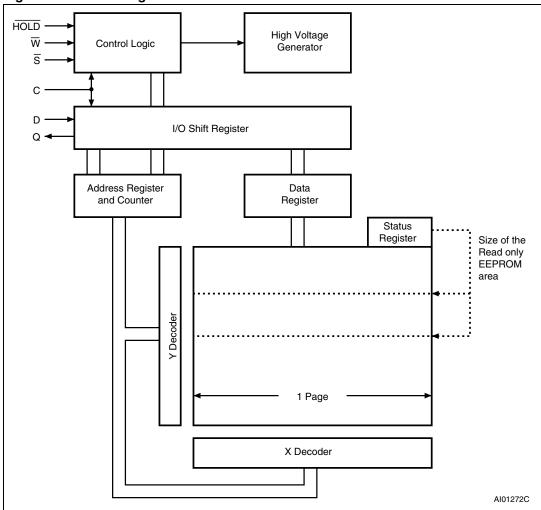

### 4.2 Status register

*Figure 6: Block diagram* shows the position of the Status register in the control logic of the device. This register contains a number of control bits and status bits, as shown in *Table 5: Status register format*. For a detailed description of the Status register bits, see *Section 6.3: Read Status Register (RDSR)*.

## 4.3 Data protection and protocol control

To help protect the device from data corruption in noisy or poorly controlled environments, a number of safety features have been built in to the device. The main security measures can be summarized as follows:

- The WEL bit is reset at power-up.

- Chip Select (S) must rise after the eighth clock count (or multiple thereof) in order to start a non-volatile Write cycle (in the memory array or in the Status register).

- Accesses to the memory array are ignored during the non-volatile programming cycle, and the programming cycle continues unaffected.

- Invalid Chip Select  $(\overline{S})$  and Hold  $(\overline{HOLD})$  transitions are ignored.

For any instruction to be accepted and executed, Chip Select  $(\overline{S})$  must be driven high after the rising edge of Serial Clock (C) that latches the last bit of the instruction, and before the next rising edge of Serial Clock (C).

For this, "the last bit of the instruction" can be the eighth bit of the instruction code, or the eighth bit of a data byte, depending on the instruction (except in the case of RDSR and READ instructions). Moreover, the "next rising edge of CLOCK" might (or might not) be the next bus transaction for some other device on the bus.

When a Write cycle is in progress, the device protects it against external interruption by ignoring any subsequent READ, WRITE or WRSR instruction until the present cycle is complete.

|   | Status register bits |     | Protected block | Protected array addresses |           |           |  |

|---|----------------------|-----|-----------------|---------------------------|-----------|-----------|--|

|   | BP1                  | BP0 | FIOLECIEU DIOCK | M95040                    | M95020    | M95010    |  |

| ſ | 0                    | 0   | none            | none                      | none      | none      |  |

|   | 0                    | 1   | Upper quarter   | 180h - 1FFh               | C0h - FFh | 60h - 7Fh |  |

| ſ | 1                    | 0   | Upper half      | 100h - 1FFh               | 80h - FFh | 40h - 7Fh |  |

|   | 1                    | 1   | Whole memory    | 000h - 1FFh               | 00h - FFh | 00h - 7Fh |  |

Table 3. Write-protected block size

# 5 Memory organization

The memory is organized as shown in Figure 6: Block diagram.

Figure 6. Block diagram

## 6 Instructions

Each instruction starts with a single-byte code, as summarized in Table 4: Instruction set.

If an invalid instruction is sent (one not contained in *Table 4: Instruction set*), the device automatically deselects itself.

| Instruction | Description            | Instruction Format                     |

|-------------|------------------------|----------------------------------------|

| WREN        | Write Enable           | 0000 X110 <sup>(1)</sup>               |

| WRDI        | Write Disable          | 0000 X100 <sup>(1)</sup>               |

| RDSR        | Read Status Register   | 0000 X101 <sup>(1)</sup>               |

| WRSR        | Write Status Register  | 0000 X001 <sup>(1)</sup>               |

| READ        | Read from Memory Array | 0000 A <sub>8</sub> 011 <sup>(2)</sup> |

| WRITE       | Write to Memory Array  | 0000 A <sub>8</sub> 010 <sup>(2)</sup> |

1. X = Don't Care.

2. A8 = 1 for the upper half of the memory array of the M95040, and 0 for the lower half, and is Don't Care for other devices.

## 6.1 Write Enable (WREN)

The Write Enable Latch (WEL) bit must be set prior to each WRITE and WRSR instruction. The only way to do this is to send a Write Enable instruction to the device.

As shown in *Figure 7: Write Enable (WREN) sequence*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in, on Serial Data Input (D). The device then enters a wait state. It waits for a the device to be deselected, by Chip Select  $(\overline{S})$  being driven high.

Figure 7. Write Enable (WREN) sequence

## 6.2 Write Disable (WRDI)

One way of resetting the Write Enable Latch (WEL) bit is to send a Write Disable instruction to the device.

As shown in *Figure 8: Write Disable (WRDI) sequence*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in, on Serial Data Input (D).

The device then enters a wait state. It waits for a the device to be deselected, by Chip Select  $(\overline{S})$  being driven high.

The Write Enable Latch (WEL) bit, in fact, becomes reset by any of the following events:

- Power-up

- WRDI instruction execution

- WRSR instruction completion

- WRITE instruction completion

- Write Protect  $(\overline{W})$  line being held low.

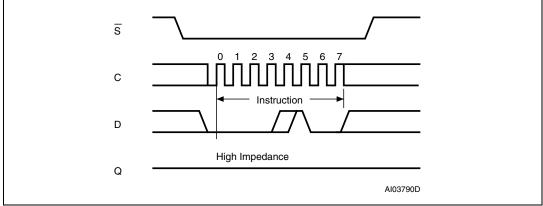

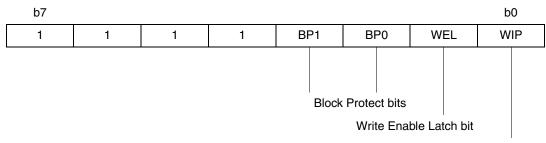

### 6.3 Read Status Register (RDSR)

The Read Status Register instruction is used to read the Status Register.

As shown in *Figure 9*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte are then shifted in, on Serial Data Input (D). The current state of the bits in the Status register is shifted out, on Serial Data Out (Q). The Read Cycle is terminated by driving Chip Select  $(\overline{S})$  high.

The Status Register is always readable, even if a Write or Write Status Register cycle is in progress. During a Write Status Register cycle, the values of the non-volatile bits (BP0, BP1) become available when a new RDSR instruction is executed, after completion of the Write cycle. On the other hand, the two read-only bits (Write Enable Latch (WEL), Write In Progress (WIP)) are dynamically updated during the ongoing Write cycle.

It is also possible to read the Status Register contents continuously, as described in *Figure 9*.

Bits b7, b6, b5 and b4 are always read as 1. The status and control bits of the Status register are as follows:

Status register format

#### Write In Progress bit

#### 6.3.1 WIP bit

Table 5.

The Write In Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status register cycle. When set to 1, such a cycle is in progress, when reset to 0 no such cycle is in progress.

#### 6.3.2 WEL bit

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write or Write Status Register instruction is accepted.

#### 6.3.3 BP1, BP0 bits

The Block Protect (BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Write instructions. These bits are written with the Write Status Register (WRSR) instruction. When one or both of the Block Protect (BP1, BP0) bits is set to 1, the relevant memory area (as defined in *Table 3: Write-protected block size*) becomes protected against Write (WRITE) instructions. The Block Protect (BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set.

### 6.4 Write Status Register (WRSR)

The Write Status Register (WRSR) instruction allows new values to be written to the Status register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed.

The Write Status Register (WRSR) instruction is entered by driving Chip Select  $(\overline{S})$  low, sending the instruction code followed by the data byte on Serial Data input (D), and driving the Chip Select  $(\overline{S})$  signal high. Chip Select  $(\overline{S})$  must be driven high after the rising edge of Serial Clock (C) that latches in the eighth bit of the data byte, and before the next rising edge of Serial Clock (C). Otherwise, the Write Status Register (WRSR) instruction is not executed.

Driving the Chip Select  $(\overline{S})$  signal high at a byte boundary of the input data triggers the selftimed write cycle that takes t<sub>W</sub> to complete (as specified in *Table 13: DC characteristics* (M950x0, device grade 3) to *Table 20: AC characteristics* (M950x0-R, device grade 6)). The instruction sequence is shown in *Figure 10: Write Status Register* (WRSR) sequence.

While the Write Status Register cycle is in progress, the Status register may still be read to check the value of the Write in progress (WIP) bit: the WIP bit is 1 during the self-timed write cycle  $t_W$ , and, 0 when the write cycle is complete. The WEL bit (Write enable latch) is also reset at the end of the write cycle  $t_W$ .

The Write Status Register (WRSR) instruction allows the user to change the values of the BP1, BP0 bits which define the size of the area that is to be treated as read only, as defined in *Table 3: Write-protected block size*.

The contents of the BP1, BP0 bits are updated after the completion of the WRSR instruction, including the  $t_W$  write cycle.

The Write Status Register (WRSR) instruction has no effect on the b7, b6, b5, b4, b1 and b0 bits in the Status register. Bits b7, b6, b5, b4 are always read as 0.

The instruction is not accepted, and is not executed, under the following conditions:

- if the Write Enable Latch (WEL) bit has not been set to 1 (by executing a Write Enable instruction just before)

- if a write cycle is already in progress

- if the device has not been deselected, by Chip Select (S) being driven high, after the eighth bit, b0, of the data byte has been latched in

- if Write Protect ( $\overline{W}$ ) is low during the WRSR command (instruction, address and data)

### 6.5 Read from Memory Array (READ)

As shown in *Figure 11: Read from Memory Array (READ) sequence*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte and address byte are then shifted in, on Serial Data Input (D). For the M95040, the most significant address bit, A8, is incorporated as bit b3 of the instruction byte, as shown in *Table 4: Instruction set*. The address is loaded into an internal address register, and the byte of data at that address is shifted out, on Serial Data Output (Q).

If Chip Select  $(\overline{S})$  continues to be driven low, an internal bit-pointer is automatically incremented at each clock cycle, and the corresponding data bit is shifted out.

When the highest address is reached, the address counter rolls over to zero, allowing the Read cycle to be continued indefinitely. The whole memory can, therefore, be read with a single READ instruction.

The Read cycle is terminated by driving Chip Select  $(\overline{S})$  high. The rising edge of the Chip Select  $(\overline{S})$  signal can occur at any time during the cycle.

The first byte addressed can be any byte within any page.

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

#### Table 6.Address range bits

| Device       | M95040 | M95020 | M95010 |

|--------------|--------|--------|--------|

| Address Bits | A8-A0  | A7-A0  | A6-A0  |

#### Figure 11. Read from Memory Array (READ) sequence

1. Depending on the memory size, as shown in *Table 6: Address range bits*, the most significant address bits are Don't Care.

### 6.6 Write to Memory Array (WRITE)

As shown in *Figure 12: Byte Write (WRITE) sequence*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte, address byte, and at least one data byte are then shifted in, on Serial Data input (D). The instruction is terminated by driving Chip Select  $(\overline{S})$  high at a byte boundary of the input data. The self-timed Write cycle, triggered by the rising edge of Chip Select  $(\overline{S})$ , continues for a period t<sub>W</sub> (as specified in *Table 13: DC characteristics (M950x0, device grade 3)* to *Table 20: AC characteristics* (M950x0-R, device grade 6)). After this time, the Write in Progress (WIP) bit is reset to 0.

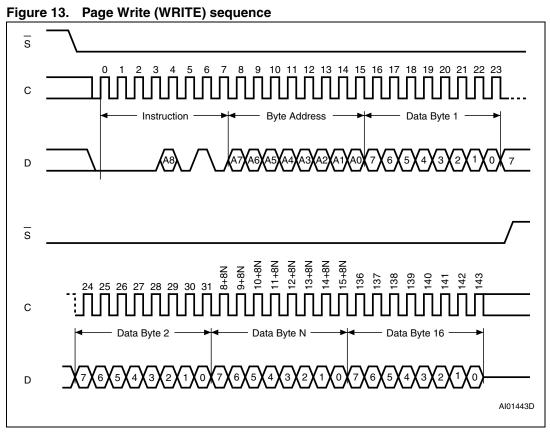

In the case of *Figure 12: Byte Write (WRITE) sequence*, Chip Select  $(\overline{S})$  is driven high after the eighth bit of the data byte has been latched in, indicating that the instruction is being used to write a single byte. If, though, Chip Select  $(\overline{S})$  continues to be driven low, as shown in *Figure 13: Page Write (WRITE) sequence*, the next byte of input data is shifted in, so that more than a single byte, starting from the given address towards the end of the same page, can be written in a single internal Write cycle. If Chip Select  $(\overline{S})$  still continues to be driven low, the next byte of input data is shifted in, and used to overwrite the byte at the start of the current page.

The instruction is not accepted, and is not executed, under the following conditions:

- if the Write Enable Latch (WEL) bit has not been set to 1 (by executing a Write Enable instruction just before)

- if a Write cycle is already in progress

- if the device has not been deselected, by Chip Select (S) being driven high, at a byte boundary (after the rising edge of Serial Clock (C) that latches the last data bit, and before the next rising edge of Serial Clock (C) occurs anywhere on the bus)

- if Write Protect (W) is low or if the addressed page is in the area protected by the Block Protect (BP1 and BP0) bits

Note:

The self-timed write cycle  $t_W$  is internally executed as a sequence of two consecutive events: [Erase addressed byte(s)], followed by [Program addressed byte(s)]. An erased bit is read as "0" and a programmed bit is read as "1".

#### Figure 12. Byte Write (WRITE) sequence

1. Depending on the memory size, as shown in *Table 6: Address range bits*, the most significant address bits are Don't Care.

# 1. Depending on the memory size, as shown in *Table 6: Address range bits*, the most significant address bits are Don't Care.

## 7 Power-up and delivery states

### 7.1 Power-up state

After Power-up, the device is in the following state:

- low power Standby Power mode

- deselected (after Power-up, a falling edge is required on Chip Select (S) before any instructions can be started).

- not in the Hold Condition

- the Write Enable Latch (WEL) is reset to 0

- Write In Progress (WIP) is reset to 0

The BP1 and BP0 bits of the Status register are unchanged from the previous power-down (they are non-volatile bits).

## 7.2 Initial delivery state

The device is delivered with the memory array set at all 1s (FFh). The Block Protect (BP1 and BP0) bits are initialized to 0.

## 8 Maximum rating

Stressing the device outside the ratings listed in *Table 7: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and operation of the device at these, or any other conditions outside those indicated in the operating sections of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

|                   | , see a s |              |                      |      |

|-------------------|-----------------------------------------------------------------------------------------------------------------|--------------|----------------------|------|

| Symbol            | Parameter                                                                                                       | Min.         | Max.                 | Unit |

|                   | Ambient operating temperature                                                                                   | -40          | 130                  | °C   |

| T <sub>STG</sub>  | Storage temperature                                                                                             | -65          | 150                  | °C   |

| T <sub>LEAD</sub> | Lead temperature during soldering                                                                               | see note (1) |                      | °C   |

| V <sub>O</sub>    | Output voltage                                                                                                  | -0.50        | V <sub>CC</sub> +0.6 | V    |

| VI                | Input voltage                                                                                                   | -0.50        | V <sub>CC</sub> +1.0 | V    |

| I <sub>OL</sub>   | DC output current (Q = 0)                                                                                       | -            | 5                    | mA   |

| I <sub>IH</sub>   | DC output current (Q = 1)                                                                                       | -            | 5                    | mA   |

| V <sub>CC</sub>   | Supply voltage                                                                                                  | -0.50        | 6.5                  | V    |

| V <sub>ESD</sub>  | Electrostatic pulse (Human Body Model) voltage <sup>(2)</sup>                                                   | -            | 4000                 | V    |

Table 7.

Absolute maximum ratings

1. Compliant with JEDEC Std J-STD-020C (for small body, Sn-Pb or Pb assembly), the ST ECOPACK® 7191395 specification, and the European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU.

Positive and negative pulses applied on pin pairs, according to the AEC-Q100-002 (compliant with JEDEC Std JESD22-A114, C1=100pF, R1=1500Ω, R2=500Ω)

## 9 DC and AC parameters

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristic tables that follow are derived from tests performed under the measurement conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

#### Table 8.Operating conditions (M950x0)

| Symbol          | Parameter                                      | Min. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                                 | 4.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature (device grade 3) | -40  | 125  | °C   |

#### Table 9. Operating conditions (M950x0-W)

| Symbol          | Parameter                                      | Min. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                                 | 2.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature (device grade 6) | -40  | 85   | °C   |

|                 | Ambient operating temperature (device grade 3) | -40  | 125  | °C   |

#### Table 10. Operating conditions (M950x0-R)

| Symbol          | Parameter                     | Min. | Max. | Unit |

|-----------------|-------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | 1.8  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -40  | 85   | °C   |

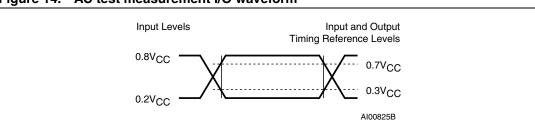

#### Table 11. AC test measurement conditions

| Symbol | Parameter                                  | Min.                       | Max.                 | Unit |

|--------|--------------------------------------------|----------------------------|----------------------|------|

| CL     | Load capacitance                           | 30                         |                      | pF   |

|        | Input rise and fall times                  | -                          | 50                   | ns   |

|        | Input pulse voltages                       | $0.2V_{CC}$ to $0.8V_{CC}$ |                      | V    |

|        | Input and output timing reference voltages | 0.3V <sub>CC</sub> t       | o 0.7V <sub>CC</sub> | V    |

1. Output Hi-Z is defined as the point where data out is no longer driven.

#### Figure 14. AC test measurement I/O waveform

#### Table 12.Capacitance

| Symbol           | Parameter                      | Test condition         | Min. | Max. | Unit |

|------------------|--------------------------------|------------------------|------|------|------|

| C <sub>OUT</sub> | Output capacitance (Q)         | V <sub>OUT</sub> = 0 V | -    | 8    | pF   |

| C <sub>IN</sub>  | Input capacitance (D)          | V <sub>IN</sub> = 0 V  | -    | 8    | pF   |

|                  | Input capacitance (other pins) | V <sub>IN</sub> = 0 V  | -    | 6    | pF   |

1. Sampled only, not 100% tested, at  $T_A=25^{\circ}C$  and a frequency of 5MHz.

| Table 13. DC charact | eristics (M950x0) | , device grade 3) |

|----------------------|-------------------|-------------------|

|----------------------|-------------------|-------------------|

| Symbol                          | Parameter                              | Test condition                                                                                 | Min.                | Max.                | Unit |

|---------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|---------------------|---------------------|------|

| ILI                             | Input leakage current                  | $V_{IN} = V_{SS} \text{ or } V_{CC}$                                                           | -                   | ± 2                 | μA   |

| I <sub>LO</sub>                 | Output leakage current                 | $\overline{S} = V_{CC}, V_{OUT} = V_{SS} \text{ or } V_{CC}$                                   | -                   | ± 2                 | μA   |

| I <sub>CC</sub>                 | Supply current                         | $C = 0.1V_{CC}/0.9V_{CC} \text{ at 5 MHz},$<br>$V_{CC} = 5 \text{ V}, \text{ Q} = \text{open}$ | -                   | 3                   | mA   |

| I <sub>CC1</sub>                | Supply current<br>(Standby Power mode) | $\overline{S} = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$ $V_{CC} = 5 \text{ V}$             | -                   | 5                   | μA   |

| V <sub>IL</sub>                 | Input low voltage                      |                                                                                                | -0.45               | 0.3 V <sub>CC</sub> | V    |

| V <sub>IH</sub>                 | Input high voltage                     |                                                                                                | $0.7 V_{CC}$        | V <sub>CC</sub> +1  | V    |

| V <sub>OL</sub>                 | Output low voltage                     | $I_{OL} = 2 \text{ mA}, V_{CC} = 5 \text{ V}$                                                  | -                   | 0.4                 | V    |

| V <sub>OH</sub>                 | Output high voltage                    | $I_{OH} = -2 \text{ mA}, \text{ V}_{CC} = 5 \text{ V}$                                         | 0.8 V <sub>CC</sub> | -                   | V    |

| V <sub>RES</sub> <sup>(1)</sup> | Internal reset threshold voltage       |                                                                                                | 2.5                 | 4.0                 | V    |

1. Characterized only, not 100% tested.

| Symbol                          | Peremeter                              | Test condition                                                                          | Min.                | Max.                | Unit |

|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------|---------------------|---------------------|------|

| Symbol                          | Parameter                              | Test condition                                                                          | MIIN.               | max.                | Unit |

| Ι <sub>LI</sub>                 | Input leakage current                  | $V_{IN} = V_{SS} \text{ or } V_{CC}$                                                    | -                   | ± 2                 | μA   |

| I <sub>LO</sub>                 | Output leakage current                 | $\overline{S} = V_{CC}, V_{OUT} = V_{SS} \text{ or } V_{CC}$                            | -                   | ± 2                 | μA   |

| I <sub>CC</sub>                 | Supply current                         | C = $0.1V_{CC}/0.9V_{CC}$ at 5 MHz,<br>V <sub>CC</sub> = 2.5 V, Q = open                | -                   | 2                   | mA   |

| I <sub>CC1</sub>                | Supply current<br>(Standby Power mode) | $\overline{S} = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$<br>$V_{CC} = 2.5 \text{ V}$ | -                   | 1                   | μA   |

| V <sub>IL</sub>                 | Input low voltage                      |                                                                                         | -0.45               | 0.3 V <sub>CC</sub> | V    |

| V <sub>IH</sub>                 | Input high voltage                     |                                                                                         | 0.7 V <sub>CC</sub> | V <sub>CC</sub> +1  | V    |

| V <sub>OL</sub>                 | Output low voltage                     | l <sub>OL</sub> = 1.5 mA, V <sub>CC</sub> = 2.5 V                                       | -                   | 0.4                 | V    |

| V <sub>OH</sub>                 | Output high voltage                    | $I_{OH}$ = -0.4 mA, $V_{CC}$ = 2.5 V                                                    | 0.8 V <sub>CC</sub> | -                   | V    |

| V <sub>RES</sub> <sup>(1)</sup> | Internal reset threshold voltage       |                                                                                         | 1.0                 | 1.65                | V    |

Table 14.

DC characteristics (M950x0-W, device grade 6)

1. Characterized only, not 100% tested.

| Table 13. DC characteristics (M350X0-W, device grade 5) |                                        |                                                                                                                                              |                     |                     |      |  |  |  |

|---------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|--|--|--|

| Symbol                                                  | I Parameter Test condition             |                                                                                                                                              | Min.                | Max.                | Unit |  |  |  |

| Ι <sub>LI</sub>                                         | Input leakage current                  | $V_{IN} = V_{SS} \text{ or } V_{CC}$                                                                                                         | -                   | ± 2                 | μA   |  |  |  |

| I <sub>LO</sub>                                         | Output leakage current                 | $\overline{S} = V_{CC}, V_{OUT} = V_{SS} \text{ or } V_{CC}$                                                                                 | -                   | ± 2                 | μA   |  |  |  |

| I <sub>CC</sub>                                         | Supply current                         | $\label{eq:C} \begin{array}{l} C = 0.1 V_{CC} / 0.9 V_{CC} \text{ at 5 MHz}, \\ V_{CC} = 2.5 \text{ V}, \text{ Q} = \text{open} \end{array}$ | -                   | 2                   | mA   |  |  |  |

| I <sub>CC1</sub>                                        | Supply current<br>(Standby Power mode) | $\overline{S} = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$<br>$V_{CC} = 2.5 \text{ V}$                                                      | -                   | 2                   | μA   |  |  |  |

| V <sub>IL</sub>                                         | Input low voltage                      |                                                                                                                                              | -0.45               | 0.3 V <sub>CC</sub> | V    |  |  |  |

| $V_{IH}$                                                | Input high voltage                     |                                                                                                                                              | $0.7 V_{CC}$        | V <sub>CC</sub> +1  | V    |  |  |  |

| V <sub>OL</sub>                                         | Output low voltage                     | $I_{OL}$ = 1.5 mA, $V_{CC}$ = 2.5 V                                                                                                          | -                   | 0.4                 | V    |  |  |  |

| V <sub>OH</sub>                                         | Output high voltage                    | $I_{OH} = -0.4 \text{ mA}, V_{CC} = 2.5 \text{ V}$                                                                                           | 0.8 V <sub>CC</sub> | -                   | V    |  |  |  |

| $V_{RES}^{(1)}$                                         | Internal reset threshold voltage       |                                                                                                                                              | 1.0                 | 1.65                | V    |  |  |  |

Table 15.

DC characteristics (M950x0-W, device grade 3)

1. Characterized only, not 100% tested.

| Table 16. | DC characteristics (M950x0-R, device grade 6) |

|-----------|-----------------------------------------------|

|-----------|-----------------------------------------------|

| Symbol           | Parameter                           | Test condition                                                                                                                                                                                | Min.               | Max.               | Unit |

|------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Ι <sub>LI</sub>  | Input leakage current               | $V_{IN} = V_{SS}$ or $V_{CC}$                                                                                                                                                                 | -                  | ± 2                | μA   |

| I <sub>LO</sub>  | Output leakage<br>current           | S = V <sub>CC</sub> , voltage applied on Q = V <sub>SS</sub> or V <sub>CC</sub>                                                                                                               | -                  | ± 2                | μΑ   |

|                  | Supply current                      | $\label{eq:V_CC} \begin{array}{l} V_{CC} = 2.5 \ \text{V}, \ C = 0.1 \ \text{V}_{CC} \ \text{or} \ 0.9 \text{V}_{CC}, \\ \text{f}_{C} = 5 \ \text{MHz}, \ \text{Q} = \text{open} \end{array}$ | -                  | 3                  | mA   |

| ICCR             | (Read)                              | $V_{CC}$ = 1.8 V, C = 0.1 $V_{CC}$ or 0.9 $V_{CC}$ at max clock frequency, Q = open                                                                                                           | -                  | 2                  | mA   |

|                  |                                     | $V_{CC}$ = 5.0 V, $\overline{S}$ = V <sub>CC</sub> , $V_{IN}$ = V <sub>SS</sub> or V <sub>CC</sub>                                                                                            | -                  | 2                  | μA   |

| I <sub>CC1</sub> | Supply current<br>(Standby)         | $V_{CC}$ = 2.5 V, $\overline{S}$ = $V_{CC}$ , $V_{IN}$ = $V_{SS}$ or $V_{CC}$                                                                                                                 | -                  | 1                  | μA   |

|                  |                                     | $V_{CC}$ = 1.8 V, $\overline{S}$ = $V_{CC}$ , $V_{IN}$ = $V_{SS}$ or $V_{CC}$                                                                                                                 | -                  | 1                  | μA   |

| Ň                | Input low voltogo                   | 2.5 V < V <sub>CC</sub> < 5.5 V                                                                                                                                                               | -0.45              | 0.3V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Input low voltage                   | 1.8 V < V <sub>CC</sub> < 2.5 V                                                                                                                                                               | -0.45              | $0.25V_{CC}$       | V    |

| V                | Input high voltage                  | 2.5 V < V <sub>CC</sub> < 5.5 V                                                                                                                                                               | $0.7V_{CC}$        | V <sub>CC</sub> +1 | V    |

| V <sub>IH</sub>  | Input high voltage                  | 1.8 V < V <sub>CC</sub> < 2.5 V                                                                                                                                                               | $0.75V_{CC}$       | V <sub>CC</sub> +1 | V    |

| V <sub>OL</sub>  | Output low voltage                  | $V_{CC} = 2.5 \text{ V}, I_{OL} = 1.5 \text{ mA},$<br>or $V_{CC} = 5.5 \text{ V}, I_{OL} = 2 \text{ mA}$                                                                                      | -                  | 0.2V <sub>CC</sub> | V    |

| -                |                                     | $V_{CC} = 1.8 \text{ V}, \text{ I}_{OL} = 0.15 \text{ mA}$                                                                                                                                    | -                  | 0.3                | V    |

| V <sub>OH</sub>  | Output high voltage                 | $V_{CC} = 2.5 \text{ V}, I_{OH} = -0.4 \text{ mA},$<br>or $V_{CC} = 5.5 \text{ V}, I_{OH} = -2 \text{ mA},$<br>or $V_{CC} = 1.8 \text{ V}, I_{OH} = -0.1 \text{ mA}$                          | 0.8V <sub>CC</sub> | -                  | v    |

| $V_{RES}^{(1)}$  | Internal reset<br>threshold voltage |                                                                                                                                                                                               | 1.0                | 1.65               | ۷    |

1. Characterized only, not 100% tested.

|                                  |                   | Test conditions specified in <i>Table 11</i> and <i>Tal</i> | ble 8 |      |      |

|----------------------------------|-------------------|-------------------------------------------------------------|-------|------|------|

| Symbol                           | Alt.              | Parameter                                                   | Min.  | Max. | Unit |

| f <sub>C</sub>                   | f <sub>SCK</sub>  | Clock frequency                                             | D.C.  | 5    | MHz  |

| t <sub>SLCH</sub>                | t <sub>CSS1</sub> | S active setup time                                         | 90    | -    | ns   |

| t <sub>SHCH</sub>                | t <sub>CSS2</sub> | S not active setup time                                     | 90    | -    | ns   |

| t <sub>SHSL</sub>                | t <sub>CS</sub>   | S deselect time                                             | 100   | -    | ns   |

| t <sub>CHSH</sub>                | t <sub>CSH</sub>  | S active hold time                                          | 90    | -    | ns   |

| t <sub>CHSL</sub>                |                   | S not active hold time                                      | 90    | -    | ns   |

| t <sub>CH</sub> <sup>(1)</sup>   | t <sub>CLH</sub>  | Clock high time                                             | 90    | -    | ns   |

| t <sub>CL</sub> <sup>(1)</sup>   | t <sub>CLL</sub>  | Clock low time                                              | 90    | -    | ns   |

| t <sub>CLCH</sub> <sup>(2)</sup> | t <sub>RC</sub>   | Clock rise time                                             |       | 1    | μs   |

| t <sub>CHCL</sub> <sup>(2)</sup> | t <sub>FC</sub>   | Clock fall time                                             |       | 1    | μs   |

| t <sub>DVCH</sub>                | t <sub>DSU</sub>  | Data in setup time                                          | 20    | -    | ns   |

| t <sub>CHDX</sub>                | t <sub>DH</sub>   | Data in hold time                                           | 30    | -    | ns   |

| t <sub>HHCH</sub>                |                   | Clock low hold time after HOLD not active                   | 70    | -    | ns   |

| t <sub>HLCH</sub>                |                   | Clock low hold time after HOLD active                       | 40    | -    | ns   |

| t <sub>CLHL</sub>                |                   | Clock low setup time before HOLD active                     | 0     | -    | ns   |

| t <sub>CLHH</sub>                |                   | Clock low setup time before HOLD not active                 | 0     | -    | ns   |

| t <sub>SHQZ</sub> <sup>(2)</sup> | t <sub>DIS</sub>  | Output disable time                                         | -     | 100  | ns   |

| t <sub>CLQV</sub>                | t <sub>V</sub>    | Clock low to output valid                                   | -     | 60   | ns   |

| t <sub>CLQX</sub>                | t <sub>HO</sub>   | Output hold time                                            | 0     | -    | ns   |

| t <sub>QLQH</sub> <sup>(2)</sup> | t <sub>RO</sub>   | Output rise time                                            | -     | 50   | ns   |

| t <sub>QHQL</sub> <sup>(2)</sup> | t <sub>FO</sub>   | Output fall time                                            | -     | 50   | ns   |

| t <sub>HHQV</sub>                | t <sub>LZ</sub>   | HOLD high to output valid                                   | -     | 50   | ns   |

| t <sub>HLQZ</sub> <sup>(2)</sup> | t <sub>HZ</sub>   | HOLD low to output high-Z                                   | -     | 100  | ns   |

| t <sub>W</sub>                   | t <sub>WC</sub>   | Write time                                                  | -     | 5    | ms   |

Table 17.

AC characteristics (M950x0, device grade 3)

1.  $t_{CH}$  +  $t_{CL}$  must never be less than the shortest possible clock period, 1 /  $f_C(max)$

|                                  |                   | Test conditions specified in <i>Table 11</i> and <i>Table</i> | ble 9 |      |      |

|----------------------------------|-------------------|---------------------------------------------------------------|-------|------|------|

| Symbol                           | Alt.              | Parameter                                                     | Min.  | Max. | Unit |

| f <sub>C</sub>                   | f <sub>SCK</sub>  | Clock frequency                                               | D.C.  | 10   | MHz  |

| t <sub>SLCH</sub>                | t <sub>CSS1</sub> | S active setup time                                           | 15    | -    | ns   |

| t <sub>SHCH</sub>                | t <sub>CSS2</sub> | S not active setup time                                       | 15    | -    | ns   |

| t <sub>SHSL</sub>                | t <sub>CS</sub>   | S deselect time                                               | 40    | -    | ns   |

| t <sub>CHSH</sub>                | t <sub>CSH</sub>  | S active hold time                                            | 25    | -    | ns   |

| t <sub>CHSL</sub>                |                   | S not active hold time                                        | 15    | -    | ns   |

| t <sub>CH</sub> <sup>(1)</sup>   | t <sub>CLH</sub>  | Clock high time                                               | 40    | -    | ns   |

| t <sub>CL</sub> <sup>(1)</sup>   | t <sub>CLL</sub>  | Clock low time                                                | 40    | -    | ns   |

| t <sub>CLCH</sub> <sup>(2)</sup> | t <sub>RC</sub>   | Clock rise time                                               | -     | 1    | μs   |

| t <sub>CHCL</sub> <sup>(2)</sup> | t <sub>FC</sub>   | Clock fall time                                               | -     | 1    | μs   |

| t <sub>DVCH</sub>                | t <sub>DSU</sub>  | Data in setup time                                            | 15    | -    | ns   |

| t <sub>CHDX</sub>                | t <sub>DH</sub>   | Data in hold time                                             | 15    | -    | ns   |

| t <sub>HHCH</sub>                |                   | Clock low hold time after HOLD not active                     | 15    | -    | ns   |

| t <sub>HLCH</sub>                |                   | Clock low hold time after HOLD active                         | 20    | -    | ns   |

| t <sub>CLHL</sub>                |                   | Clock low setup time before HOLD active                       | 0     | -    | ns   |

| t <sub>CLHH</sub>                |                   | Clock low setup time before HOLD not active                   | 0     | -    | ns   |

| t <sub>SHQZ</sub> <sup>(2)</sup> | t <sub>DIS</sub>  | Output disable time                                           | -     | 25   | ns   |

| t <sub>CLQV</sub>                | t <sub>V</sub>    | Clock low to output valid                                     | -     | 35   | ns   |

| t <sub>CLQX</sub>                | t <sub>HO</sub>   | Output hold time                                              | 0     | -    | ns   |

| t <sub>QLQH</sub> <sup>(2)</sup> | t <sub>RO</sub>   | Output rise time                                              | -     | 20   | ns   |

| t <sub>QHQL</sub> <sup>(2)</sup> | t <sub>FO</sub>   | Output fall time                                              | -     | 20   | ns   |

| t <sub>HHQV</sub>                | t <sub>LZ</sub>   | HOLD high to output valid                                     | -     | 25   | ns   |

| t <sub>HLQZ</sub> <sup>(2)</sup> | t <sub>HZ</sub>   | HOLD low to output high-Z                                     | -     | 35   | ns   |

| t <sub>W</sub>                   | t <sub>WC</sub>   | Write time                                                    | -     | 5    | ms   |

| Table 18. | AC characteristics | (M950x0-W, | device q | rade 6) |

|-----------|--------------------|------------|----------|---------|

|           |                    |            |          |         |

1.  $t_{CH}$  +  $t_{CL}$  must never be less than the shortest possible clock period, 1 /  $f_C(max)$

| Test conditions specified in <i>Table 11</i> and <i>Table 9</i> |                   |                                             |      |      |      |  |

|-----------------------------------------------------------------|-------------------|---------------------------------------------|------|------|------|--|

| Symbol                                                          | Alt.              | Parameter                                   | Min. | Max. | Unit |  |

| f <sub>C</sub>                                                  | f <sub>SCK</sub>  | Clock frequency                             | D.C. | 5    | MHz  |  |

| t <sub>SLCH</sub>                                               | t <sub>CSS1</sub> | S active setup time                         | 90   | -    | ns   |  |

| t <sub>SHCH</sub>                                               | t <sub>CSS2</sub> | S not active setup time                     | 90   | -    | ns   |  |

| t <sub>SHSL</sub>                                               | t <sub>CS</sub>   | S deselect time                             | 100  | -    | ns   |  |

| t <sub>CHSH</sub>                                               | t <sub>CSH</sub>  | S active hold time                          | 90   | -    | ns   |  |

| t <sub>CHSL</sub>                                               |                   | S not active hold time                      | 90   | -    | ns   |  |

| t <sub>CH</sub> <sup>(1)</sup>                                  | t <sub>CLH</sub>  | Clock high time                             | 90   | -    | ns   |  |

| t <sub>CL</sub> <sup>(1)</sup>                                  | t <sub>CLL</sub>  | Clock low time                              | 90   | -    | ns   |  |

| t <sub>CLCH</sub> <sup>(2)</sup>                                | t <sub>RC</sub>   | Clock rise time                             | -    | 1    | μs   |  |

| t <sub>CHCL</sub> <sup>(2)</sup>                                | t <sub>FC</sub>   | Clock fall time                             | -    | 1    | μs   |  |

| t <sub>DVCH</sub>                                               | t <sub>DSU</sub>  | Data in setup time                          | 20   | -    | ns   |  |

| t <sub>CHDX</sub>                                               | t <sub>DH</sub>   | Data in hold time                           | 30   | -    | ns   |  |

| t <sub>HHCH</sub>                                               |                   | Clock low hold time after HOLD not active   | 70   | -    | ns   |  |

| t <sub>HLCH</sub>                                               |                   | Clock low hold time after HOLD active       | 40   | -    | ns   |  |

| t <sub>CLHL</sub>                                               |                   | Clock low setup time before HOLD active     | 0    | -    | ns   |  |

| t <sub>CLHH</sub>                                               |                   | Clock low setup time before HOLD not active | 0    | -    | ns   |  |

| t <sub>SHQZ</sub> <sup>(2)</sup>                                | t <sub>DIS</sub>  | Output disable time                         | -    | 100  | ns   |  |

| t <sub>CLQV</sub>                                               | t <sub>V</sub>    | Clock low to output valid                   | -    | 60   | ns   |  |

| t <sub>CLQX</sub>                                               | t <sub>HO</sub>   | Output hold time                            | 0    | -    | ns   |  |

| t <sub>QLQH</sub> <sup>(2)</sup>                                | t <sub>RO</sub>   | Output rise time                            | -    | 50   | ns   |  |