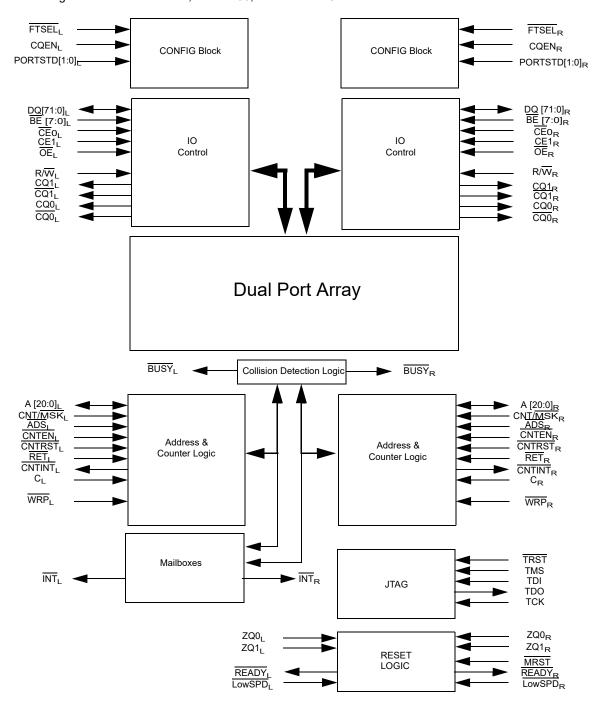

### **Logic Block Diagram**

The Logic Block Diagrams for the FullFlex72, FullFlex36, and FullFlex18 families follow. [2, 3, 4]

### Notes

- 2. The CYD36S18V18 device has 21 address bits. The CYD36S36V18 and CYD18S18V18 devices have 20 address bits. The CYD36S72V18, CYD18S36V18, and CYD09S18V18 devices have 19 address bits. The CYD09S72V18 device has 17 address bits. The CYD02S36V18 has 16 address bits.

- 3. The FullFlex72 family of devices has 72 data lines. The FullFlex36 family of devices has 36 data lines. The FullFlex18 family of devices has 18 data lines.

- 4. The FullFlex72 family of devices has eight byte enables. The FullFlex36 family of devices has four byte enables. The FullFlex18 family of devices has two byte enables.

### Contents

| Selection Guide                                          |      |

|----------------------------------------------------------|------|

| Pin Definitions                                          |      |

| Functional Overview                                      |      |

| Selectable IO Standard                                   |      |

| Clocking                                                 |      |

| Selectable Pipelined or Flow through Mode                |      |

| DLL                                                      |      |

| Echo Clocking                                            |      |

| Deterministic Access Control                             |      |

| Variable Impedance Matching                              | . 12 |

| Address Counter                                          |      |

| and Mask Register Operations [28]                        | . 13 |

| Counter Load Operation [20]                              | 13   |

| Mask Load Operation [28]                                 |      |

| Counter Readback Operation                               |      |

| Mask Readback Operation                                  |      |

| Counter Reset Operation                                  |      |

| Mask Reset Operation Increment Operation <sup>[31]</sup> | .13  |

|                                                          |      |

| Hold Operation                                           |      |

| Retransmit                                               |      |

| Counter Interrupt                                        |      |

| Counting by Two                                          |      |

| Counting by Four                                         |      |

| Master Reset                                             |      |

| IEEE 1149.1 Serial Boundary Scan (JTAG)                  |      |

| Maximum Ratings                                          |      |

| Operating Range                                          |      |

| Power Supply Requirements                                |      |

| Electrical Characteristics                               |      |

| Electrical Characteristics                               |      |

| Electrical Characteristics                               |      |

| Capacitance                                              |      |

| Thermal Resistance                                       |      |

| AC Test I and and Waveforms                              |      |

| Switching Characteristics               | 25       |

|-----------------------------------------|----------|

| Switching Waveforms                     |          |

| Ordering Information                    | 42       |

| 512K × 72 (36-Mbit) 1.8 V/1.5 V         |          |

| Synchronous CYD36S72V18 Dual-Port SRAM  | 42       |

| 256K × 72 (18-Mbit) 1.8 V/1.5 V         |          |

| Synchronous CYD18S72V18 Dual-Port SRAM  | 42       |

| 128K × 72 (9-Mbit) 1.8 V/1.5 V          |          |

| Synchronous CYD09S72V18 Dual-Port SRAM  | 42       |

| 1024K × 36 (36-Mbit) 1.8 V/1.5 V        |          |

| Synchronous CYD36S36V18 Dual-Port SRAM  | 42       |

| 512K × 36 (18-Mbit) 1.8 V/1.5 V         |          |

| Synchronous CYD18S36V18 Dual-Port SRAM  | 42       |

| 256K × 36 (9-Mbit) 1.8 V/1.5 V          |          |

| Synchronous CYD09S36V18 Dual-Port SRAM  | 42       |

| 64K × 36 (2-Mbit) 1.8 V or 1.5 V        |          |

| Synchronous CYD02S36V18 Dual-Port SRAM  | 42       |

| 2048K × 18 (36-Mbit) 1.8 V/1.5 V        |          |

| Synchronous CYD36S18V18 Dual-Port SRAM  | 42       |

| 1024K × 18 (18-Mbit) 1.8 V/1.5 V        |          |

| Synchronous CYD18S18V18 Dual-Port SRAM  | 42       |

| 512K × 18 (9-Mbit) 1.8 V/1.5 V          |          |

| Synchronous CYD09S18V18 Dual-Port SRAM  |          |

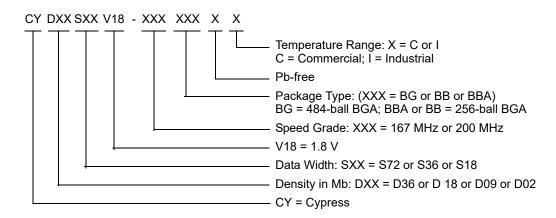

| Ordering Code Definitions               |          |

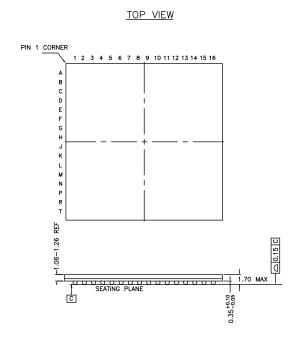

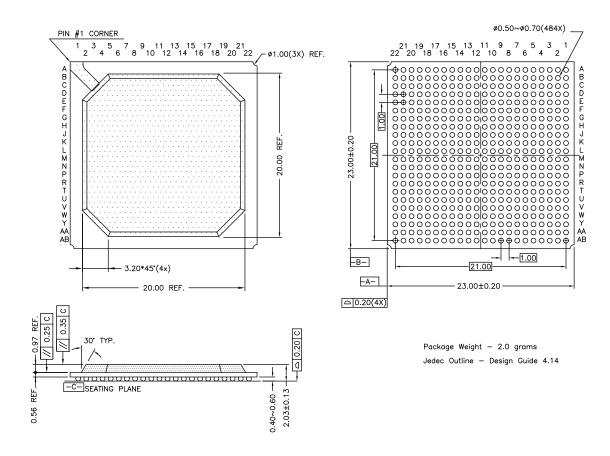

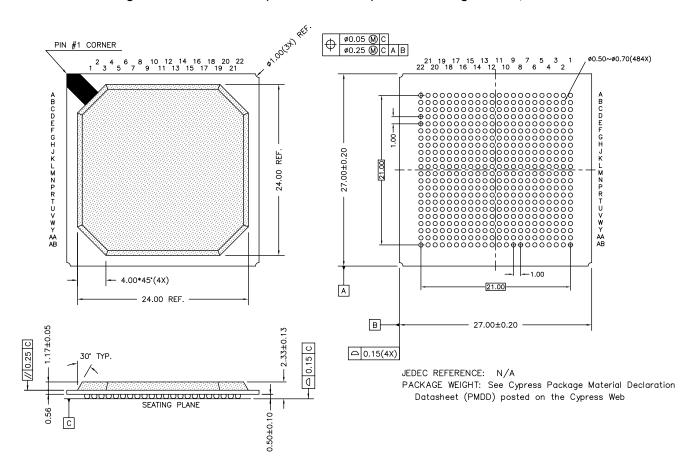

| Package Diagrams                        |          |

| Acronyms                                |          |

| Document Conventions                    |          |

| Units of Measure                        |          |

| Document History Page                   |          |

| Sales, Solutions, and Legal Information |          |

| Worldwide Sales and Design Support      |          |

| Products                                |          |

| PSoC® Solutions                         |          |

| Cypress Developer Community             |          |

| Lochnical Support                       | <u> </u> |

## Figure 1. FullFlex72 SDR 484-ball BGA Pinout (Top View)

|    |                     |                     |                        |             |        |             |        | Figure | <del>.</del> | ex72 SD   | R 484                 | -ball E             | FullFlex72 SDR 484-ball BGA Pinout (Top View) | t (Top Vie | (M     |               |        |        |            |                        |                     |                     |

|----|---------------------|---------------------|------------------------|-------------|--------|-------------|--------|--------|--------------|-----------|-----------------------|---------------------|-----------------------------------------------|------------|--------|---------------|--------|--------|------------|------------------------|---------------------|---------------------|

|    | 1                   | 2                   | 3                      | 4           | 2      | 9           | 7      | 8      | 6            | 10        | 1                     | 12                  | 13                                            | 14         | 15     | 16            | 17     | 18     | 19         | 20                     | 21                  | 22                  |

|    | DNO                 | DQ61L               | DQ59L                  | DQ57L       | DQ54L  | DQ51L       | DQ48L  | DQ45L  | DQ42L        | DQ39L     | DQ36L                 | DQ36R               | DQ39R                                         | DQ42R      | DQ45R  | DQ48R         | DQ51R  | DQ54R  | DQ57R      | DQ59R                  | DQ61R               | DNO                 |

|    | DQ63L               | DQ62L               | DQ60L                  | DQ58L       | DQ55L  | DQ52L       | DQ49L  | DQ46L  | DQ43L        | DQ40L     | DQ37L                 | DQ37R               | DQ40R                                         | DQ43R      | DQ46R  | DQ49R         | DQ52R  | DQ55R  | DQ58R      | DQ60R                  | DQ62R               | DQ63R               |

|    | DQ65L               | DQ64L               | NSS                    | SSA         | DQ56L  | DQ53L       | DQ50L  | DQ47L  | DQ44L        | DQ41L     | DQ38L                 | . DQ38R             | DQ41R                                         | DQ44R      | DQ47R  | DQ50R         | DQ53R  | DQ56R  | NSS        | NSS                    | DQ64R               | DQ65R               |

|    | DQ67L               | DQ66L               | VSS                    | SSA         | NSS    | <u>CQ1L</u> | CQ1L   | SSA    | LOWSPDL      | PORTSTD0L | - ZQ0L <sup>[5]</sup> | BUSYL               | CNTINTL                                       | PORTSTD1L  | DNO    | CQ1R          | CQ1R   | NSS    | NSS        | NSS                    | DQ66R               | DQ67R               |

| -  | DQ69L               | DQ68L               | VDDIOL                 | SSA         | NSS    | VDDIOL      | VDDIOL | VDDIOL | VDDIOL       | VDDIOL    | VTTL                  | VTTL                | VTTL                                          | VDDIOR     | VDDIOR | VDDIOR        | VDDIOR | DNO    | NSS        | VDDIOR                 | DQ68R               | DQ69R               |

|    | DQ71L               | DQ70L               | CE1L                   | CE0L        | VDDIOL | VDDIOL      | VDDIOL | VDDIOL | VDDIOL       | VCORE     | VCORE                 | = VCORE             | CORE                                          | VDDIOR     | VDDIOR | VDDIOR VDDIOR |        | VDDIOR | CEOR       | CE1R                   | DQ70R               | DQ71R               |

| -  | AOL                 | A1L                 | RETL                   | BE4L        | VDDIOL | VDDIOL      | VREFL  | NSS    | NSS          | NSS       | NSS                   | NSS                 | NSS                                           | NSS        | NSS    | VREFR         | VDDIOR | VDDIOR | BE4R       | RETR                   | A1R                 | A0R                 |

| •  | A2L                 | A3L                 | WRPL                   | BESL        | VDDIOL | VDDIOL      | VSS    | NSS    | NSS          | VSS       | NSS                   | NSS                 | NSS                                           | VSS        | NSS    | VSS           | VDDIOR | VDDIOR | BE5R       | WRPR                   | A3R                 | A2R                 |

| -  | A4L                 | A5L                 | READYL                 | BEGL        | VDDIOL | VDDIOL      | NSS    | NSS    | VSS          | VSS       | NSS                   | NSS                 | NSS                                           | NSS        | NSS    | NSS           | VDDIOR | VDDIOR | BEGR       | READYR                 | A5R                 | A4R                 |

| -  | A6L                 | A7L                 | ZQ1L <sup>[5, 6]</sup> | BE7L        | VTTL   | VCORE       | NSS    | NSS    | NSS          | NSS       | NSS                   | NSS                 | NSS                                           | NSS        | NSS    | NSS           | VCORE  | VDDIOR | BE7R       | ZQ1R <sup>[5, 6]</sup> | A7R                 | A6R                 |

|    | A8L                 | A9L                 | CL                     | <u> 130</u> | VTTL   | VCORE       | NSS    | NSS    | NSS          | NSS       | ۸SS                   | NSS                 | NSS                                           | NSS        | NSS    | NSS           | VCORE  | VTTL   | <u>OER</u> | CR                     | A9R                 | A8R                 |

|    | A10L                | A11L                | NSS                    | BE3L        | VTTL   | VCORE       | SSA    | SSA    | NSS          | NSS       | ۸SS                   | NSS                 | NSS                                           | SSA        | NSS    | NSS           | VCORE  | VTTL   | BE3R       | NSS                    | A11R                | A10R                |

|    | A12L                | A13L                | ADSL                   | BEZL        | VDDIOL | VCORE       | NSS    | SSA    | NSS          | NSS       | ۸SS                   | NSS                 | NSS                                           | NSS        | NSS    | NSS           | VCORE  | VTTL   | BE2R       | ADSR                   | A13R                | A12R                |

|    | A14L                | A15L (              | CNT/MSKL               | BE1L        | VDDIOL | VDDIOL      | NSS    | SSA    | NSS          | NSS       | ۸SS                   | NSS                 | NSS                                           | NSS        | NSS    | NSS           | VDDIOR | VDDIOR | BE1R       | CNT/MSKR               | A15R                | A14R                |

| -  | A16L <sup>[9]</sup> | A17L <sup>[8]</sup> | CNTENL                 | BE0L        | VDDIOL | VDDIOL      | SSA    | SSA    | NSS          | NSS       | NSS                   | NSS                 | NSS                                           | SSA        | NSS    | NSS           | VDDIOR | VDDIOR | BEOR       | CNTENR                 | A17R <sup>[8]</sup> | A16R <sup>[9]</sup> |

|    | A18L <sup>[7]</sup> | DNG                 | CNTRSTL                | <u>INTL</u> | VDDIOL | VDDIOL      | VREFL  | SSA    | NSS          | NSS       | ۸SS                   | NSS                 | NSS                                           | NSS        | NSS    | VREFR         | VDDIOR | VDDIOR | INTR       | CNTRSTR                | DNO                 | A18R <sup>[7]</sup> |

| -  | DQ35L               | DQ34L               | R/WL                   | COENL       | VDDIOL | VDDIOL      | VDDIOL | VDDIOL | VDDIOL       | VCORE     | VCORE                 | = VCORE             | CORE                                          | VDDIOR     | VDDIOR | VDDIOR VDDIOR |        | VDDIOR | CQENR      | R/WR                   | DQ34R               | DQ35R               |

| -  | DQ33L               | DQ32L               | FTSELL                 | Λοραίοι     | DNO    | VDDIOL      | VDDIOL | VDDIOL | VDDIOL       | VTTL      | VTTL                  | VTTL                | VDDIOR                                        | VDDIOR     | VDDIOR | VDDIOR        | VDDIOR | TRST   | VDDIOR     | FTSELR                 | DQ32R               | DQ33R               |

| *  | DQ31L               | DQ30L               | NSS                    | MRST        | NSS    | <u> </u>    | COOL   | DNO    | PORTSTD1R    | CNTINTR   | BUSYR                 | ZQ0R <sup>[5]</sup> | PORTSTDOR                                     | LOWSPDR    | NSS    | CQ0R          | CQOR   | NSS    | IQL        | TDO                    | DQ30R               | DQ31R               |

|    | DQ29L               | DQ28L               | NSS                    | NSS         | DQ20L  | DQ17L       | DQ14L  | DQ11L  | DQ8L         | DQ5L      | DQ2L                  | DQ2R                | DQ5R                                          | DQ8R       | DQ11R  | DQ14R         | DQ17R  | DQ20R  | TMS        | TCK                    | DQ28R               | DQ29R               |

| ₹  | DQ27L               | DQ26L               | DQ24L                  | DQ22L       | DQ19L  | DQ16L       | DQ13L  | DQ10L  | DQ7L         | DQ4L      | DQ1L                  | DQ1R                | DQ4R                                          | DQ7R       | DQ10R  | DQ13R         | DQ16R  | DQ19R  | DQ22R      | DQ24R                  | DQ26R               | DQ27R               |

| AB | DNO                 | DQ25L               | DQ23L                  | DQ21L       | DQ18L  | DQ15L       | DQ12L  | DO9L   | DQ6L         | DO3L      | DQ0L                  | DQ0R                | DQ3R                                          | DQ6R       | DQ9R   | DQ12R         | DQ15R  | DQ18R  | DQ21R      | DQ23R                  | DQ25R               | DNO                 |

- Notes

5. Leave this ball unconnected to disable VIM.

6. This ball is applicable only for 36-Mbit and DNU for 18-Mbit and lower densities.

7. Leave this ball unconnected for CYD09S72V18 and CYD09S72V18.

8. Leave this ball unconnected for CYD09S72V18.

9. Leave this ball unconnected for CYD04S72V18.

Page 4 of 51

### CYDXXS72V18 CYDXXS36V18 CYDXXS18V18

Figure 2. FullFlex36 SDR 484-ball BGA Pinout (Top View)[10]

|          |          |                          |               |        |        |        | )<br>  |           | ו מווו ופעסס סבוע לסל-ממון בסטין וווסמר (יוסף אופאי). | 2                    | ב<br>ב               | 1000      |           |        |        |        |        |        |                      |                     |         |      |

|----------|----------|--------------------------|---------------|--------|--------|--------|--------|-----------|-------------------------------------------------------|----------------------|----------------------|-----------|-----------|--------|--------|--------|--------|--------|----------------------|---------------------|---------|------|

|          | - 2      | 3                        | 4             | ĸ      | 9      | 7      | œ      | စ         | 6                                                     | £                    | 12                   | 13        | 4         | 15     | 16     | 11     | 18     | 19     | 20                   | 21                  |         | 22   |

| ∢        | DNU DNU  | UN DNU                   | DNO           | DNO    | DQ33L  | DQ30L  | DQ27L  | DQ24L     | DQ21L                                                 | DQ18L                | DQ18R                | DQ21R     | DQ24R     | DQ27R  | DQ30R  | DQ33R  | DNO    | DNG    | DNO                  | DNO                 |         | DNO  |

| Ф        | DNU DN   | DNO DNO                  | NO            | DNO    | DQ34L  | DQ31L  | DQ28L  | DQ25L     | DQ22L                                                 | DQ19L                | DQ19R                | DQ22R     | DQ25R     | DQ28R  | DQ31R  | DQ34R  | DNO    | DNO    | DNO                  | DNO                 |         | DNO  |

| ပ        | DNU DN   | SSA NNO                  | NSS           | DNO    | DQ35L  | DQ32L  | DQ29L  | DQ26L     | DQ23L                                                 | DQ20L                | DQ20R                | DQ23R     | DQ26R     | DQ29R  | DQ32R  | DQ35R  | DNG    | VSS    | NSS                  | DNO                 |         | DNO  |

| ٥        | DNU DN   | DNU VSS                  | NSS           | NSS    | CQ1L   | CQ1L   | NSS    | LOWSPDL   | PORTSTD0L                                             | ZQ0L <sup>[11]</sup> | BUSYL                | CNTINTL   | PORTSTD1L | DNO    | CQ1R   | CQ1R   | NSS    | VSS    | VSS                  | DNO                 |         | DNO  |

| ш        | DNU DN   | DNU VDDIOL               | SSA -         | NSS    | VDDIOL | VDDIOR | VDDIOR | VDDIOR    | VDDIOR                                                | VTTL                 | VTTL                 | VTTL      | NDDIOL    | VDDIOL | VDDIOL | VDDIOL | DNG    | VSS    | VDDIOR               | R DNU               |         | DNO  |

| ш        | DNO DN   | DNU CE1L                 | CEOL          | VDDIOL | VDDIOL | VDDIOR | VDDIOR | VDDIOR    | VCORE                                                 | VCORE                | VCORE                | VCORE     | ΛΦΒΙΟΓ    | VDDIOL | VDDIOL | VDDIOR | VDDIOR | CEOR   | CE1R                 | DNO                 |         | DNO  |

| ø        | A0L A1   | A1L RETL                 | BE2L          | VDDIOL | VDDIOL | VREFL  | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | VREFR  | VDDIOR | VDDIOR | BE2R   | RETR                 | A1R                 |         | AOR  |

| Ξ        | A2L A3   | A3L WRPL                 | BE3L          | VDDIOL | VDDIOL | NSS    | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | NSS    | VDDIOR | VDDIOR | BE3R   | WRPR                 | A3R                 |         | A2R  |

| 7        | A4L A5   | ASL READYL               | ONO -         | VDDIOL | VDDIOL | NSS    | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | NSS    | VDDIOR | VDDIOR | DNO    | READYR               | 'R A5R              |         | A4R  |

| ×        | A6L A7   | A7L ZQ1L <sup>[11]</sup> | I DNU         | VTTL   | VCORE  | NSS    | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | NSS    | VCORE  | VDDIOR | DNO    | ZQ1R <sup>[11]</sup> | <sup>11</sup> ] A7R |         | A6R  |

| _        | A8L A9   | A9L CL                   | OEL           | VTTL   | VCORE  | NSS    | VSS    | NSS       | NSS                                                   | NSS                  | NSS                  | VSS       | SSA       | VSS    | NSS    | VCORE  | VTTL   | OER    | CR                   | A9R                 |         | A8R  |

| Σ        | A10L A1  | A11L VSS                 | ONO           | VTTL   | VCORE  | NSS    | VSS    | NSS       | NSS                                                   | NSS                  | SSA                  | VSS       | SSA       | NSS    | NSS    | VCORE  | VTTL   | DNO    | NSS                  | A11R                |         | A10R |

| z        | A12L A1: | A13L ADSL                | NO            | VDDIOL | VCORE  | NSS    | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | NSS    | VCORE  | VTTL   | DNO    | ADSR                 | A13R                |         | A12R |

| ۵.       | A14L A1  | A15L CNT/MSKL            | KL BE1L       | VDDIOL | VDDIOL | NSS    | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | NSS    | VDDIOR | VDDIOR | BE1R   | CNT/MSKR             | KR A15R             |         | A14R |

| ď        | A16L A1  | A17L CNTENL              | BEOL          | VDDIOL | VDDIOL | NSS    | VSS    | NSS       | NSS                                                   | NSS                  | SSA                  | VSS       | SSA       | NSS    | NSS    | VDDIOR | VDDIOR | BEOR   | CNTENR               |                     | A17R A1 | A16R |

| _        | A18L A19 | A19L CNTRSTL             | <u>L INTL</u> | VDDIOL | VDDIOL | VREFL  | NSS    | NSS       | NSS                                                   | NSS                  | SSA                  | NSS       | SSA       | NSS    | VREFR  | VDDIOR | VDDIOR | INTR   | CNTRSTR              | <u>TR</u> A19R      |         | A18R |

| <b>¬</b> | DNU DNU  | NU R/WL                  | CQENL         | VDDIOL | VDDIOL | VDDIOR | VDDIOR | VDDIOR    | VCORE                                                 | VCORE                | VCORE                | VCORE     | ΛΦΒΙΟΓ    | VDDIOL | VDDIOL | VDDIOR | VDDIOR | CQENR  | R/WR                 | DNO                 |         | DNU  |

| >        | DNO DN   | DNU FTSELL               | _ VDDIOL      | DNO    | VDDIOR | VDDIOR | VDDIOR | VDDIOR    | VTTL                                                  | VTTL                 | VTTL                 | VDDIOL    | ΛΡΕΙΟΓ    | VDDIOL | VDDIOL | VDDIOR | TRST   | VDDIOR | FTSELR               | R DNU               |         | DNO  |

| >        | DNU DN   | DNU VSS                  | MRST          | NSS    | CQ0L   | CGOL   | DNO    | PORTSTD1R | CNTINTR                                               | BUSYR                | ZQ0R <sup>[11]</sup> | PORTSTDOR | LOWSPDR   | NSS    | CQ0R   | CQ0R   | NSS    | TDI    | TDO                  | DNO                 |         | DNU  |

| >        | DNU DN   | DNU VSS                  | VSS           | DNO    | DQ17L  | DQ14L  | DQ11L  | DQ8L      | DQ5L                                                  | DQ2L                 | DQ2R                 | DQ5R      | DQ8R      | DQ11R  | DQ14R  | DQ17R  | DNO    | TMS    | TCK                  | DNO                 |         | DNO  |

| <b>₹</b> | DNU DNU  | UNO DNU                  | DNO           | DNO    | DQ16L  | DQ13L  | DQ10L  | DQ7L      | DQ4L                                                  | DQ1L                 | DQ1R                 | DQ4R      | DQ7R      | DQ10R  | DQ13R  | DQ16R  | DNO    | DNC    | DNO                  | DNO                 |         | DNO  |

| AB       | DNU DNU  | UNO UNU                  | ONO           | DNO    | DQ15L  | DQ12L  | DQ9L   | DQ6L      | DQ3L                                                  | DQ0L                 | DQ0R                 | DQ3R      | DQ6R      | DQ9R   | DQ12R  | DQ15R  | DNO    | DNO    | DNO                  | DNO                 |         | DNU  |

|          |          |                          |               |        |        |        |        |           |                                                       |                      |                      |           |           |        |        |        |        |        |                      |                     |         |      |

# Figure 3. FullFlex18 SDR 484-ball BGA Pinout (Top View)[12]

|        |        |         |                      |            |        |             |        | rigure | S. FUIITI | ex io our | √ 404-D              | מוו סקצ              | ruilliex to SDR 404-Dali BGA Pillout (10p view) | IOD VIEW  | · · · · · |        |        |        |        |                      |      |      |

|--------|--------|---------|----------------------|------------|--------|-------------|--------|--------|-----------|-----------|----------------------|----------------------|-------------------------------------------------|-----------|-----------|--------|--------|--------|--------|----------------------|------|------|

|        | -      | 7       | က                    | 4          | ß      | 9           | 7      | œ      | o         | 9         | £                    | 12                   | 13                                              | 41        | 15        | 16     | 11     | 18     | 19     | 20                   | 2    | 22   |

| 4      | DNO    | DNO     | DNO                  | DNO        | DNG    | DNO         | DNG    | DNO    | DQ15L     | DQ12L     | DQ9L                 | DQ9R                 | DQ12R                                           | DQ15R     | DNO       | DNO    | DNO    | DNO    | DNG    | DNG                  | DNO  | DNO  |

| m      | DNU D  | DNO     | DNU                  | DNO        | DNO    | DNO         | DNO    | DNO    | DQ16L     | DQ13L     | DQ10L                | DQ10R                | DQ13R                                           | DQ16R     | DNO       | DNO    | DNO    | DNO    | DNO    | DNO                  | DNO  | DNO  |

| ပ      | DNO    | DNO     | NSS                  | NSS        | DNG    | DNO         | NO     | DNO    | DQ17L     | DQ14L     | DQ11L                | DQ11R                | DQ14R                                           | DQ17R     | DNO       | DNO    | DNO    | DNG    | NSS    | SSA                  | DNO  | DNO  |

| ٥      | DNO D  | DNO     | NSS                  | NSS        | NSS    | <u>CQ1L</u> | CQ1L   | NSS    | LOWSPDL   | PORTSTD0L | ZQ0L <sup>[13]</sup> | BUSYL                | CNTINTL                                         | PORTSTD1L | DNO       | CQ1R   | CQ1R   | SSA    | NSS    | SSA                  | DNO  | DNO  |

| ш      |        | DNU     | VDDIOL               | NSS        | NSS    | VDDIOL      | VDDIOR | VDDIOR | VDDIOR    | VDDIOR    | VTTL                 | VTTL                 | ATTL                                            | VDDIOL    | VDDIOL    | VDDIOL | VDDIOL | DNO    | NSS    | VDDIOR               | DNG  | DNO  |

| ш      | DNO    | DNO     | CE1L                 | CEOL       | VDDIOL | VDDIOL      | VDDIOR | VDDIOR | VDDIOR    | VCORE     | VCORE                | VCORE                | VCORE                                           | VDDIOL    | VDDIOL    | VDDIOL | VDDIOR | VDDIOR | CE0R   | CE1R                 | DNO  | DNO  |

| ŋ      | AOL A  | A1L F   | RETL                 | BE1L       | VDDIOL | VDDIOL      | VREFL  | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | NSS       | SSA       | VREFR  | VDDIOR | VDDIOR | BE1R   | RETR                 | A1R  | AOR  |

| I      | A2L A  | A3L V   | WRPL                 | DNO        | VDDIOL | VDDIOL      | SSA    | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | VSS       | NSS       | VSS    | VDDIOR | VDDIOR | DNO    | WRPR                 | A3R  | A2R  |

| 7      | A4L A  | A5L RE  | READYL               | DNO        | VDDIOL | VDDIOL      | SSA    | NSS    | NSS       | SSA       | NSS                  | NSS                  | SSA                                             | VSS       | NSS       | VSS    | VDDIOR | VDDIOR | DNO    | READYR               | A5R  | A4R  |

| ×      | A6L A  | A7L Z0  | ZQ1L <sup>[13]</sup> | DNO        | VTTL   | VCORE       | SSA    | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | NSS       | SSA       | SSA    | VCORE  | VDDIOR | DNG    | ZQ1R <sup>[13]</sup> | A7R  | A6R  |

| _      | A8L A  | A9L     | CL                   | <u>OEL</u> | VTTL   | VCORE       | SSA    | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | VSS       | NSS       | VSS    | VCORE  | VTTL   | OER    | CR                   | A9R  | A8R  |

| Σ      | A10L A | A11L    | NSS                  | DNO        | VTTL   | VCORE       | SSA    | NSS    | NSS       | NSS       | VSS                  | NSS                  | SSA                                             | VSS       | NSS       | VSS    | VCORE  | VTTL   | DNO    | NSS                  | A11R | A10R |

| z      | A12L A | A13L 7  | ADSL                 | DNO        | VDDIOL | VCORE       | SSA    | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | VSS       | NSS       | NSS    | VCORE  | VTTL   | DNO    | ADSR                 | A13R | A12R |

| ۵      | A14L A | A15L CN | CNT/MSKL             | DNO        | VDDIOL | VDDIOL      | NSS    | NSS    | NSS       | NSS       | VSS                  | NSS                  | NSS                                             | VSS       | NSS       | VSS    | VDDIOR | VDDIOR | DNO    | CNT/MSKR             | A15R | A14R |

| 2      | A16L A | A17L CI | CNTENL               | BEOL       | VDDIOL | VDDIOL      | SSA    | NSS    | NSS       | NSS       | VSS                  | NSS                  | SSA                                             | VSS       | NSS       | VSS    | VDDIOR | VDDIOR | BEOR   | CNTENR               | A17R | A16R |

| -      | A18L A | A19L CN | CNTRSTL              | INTL       | VDDIOL | VDDIOL      | VREFL  | NSS    | NSS       | NSS       | NSS                  | NSS                  | SSA                                             | VSS       | NSS       | VREFR  | VDDIOR | VDDIOR | INTR   | CNTRSTR              | A19R | A18R |

| ,<br>, | A20L D | DNU     | R/WL (               | CQENL      | VDDIOL | VDDIOL      | VDDIOR | VDDIOR | VDDIOR    | VCORE     | VCORE                | VCORE                | VCORE                                           | VDDIOL    | VDDIOL    | VDDIOL | VDDIOR | VDDIOR | CQENR  | R/WR                 | DNO  | A20R |

| >      | DNO D  | DNU F   | FTSELL V             | VDDIOL     | DNG    | VDDIOR      | VDDIOR | VDDIOR | VDDIOR    | VTTL      | VTTL                 | VTTL                 | ΛΟΒΙΟΓ                                          | VDDIOL    | VDDIOL    | VDDIOL | VDDIOR | TRST   | VDDIOR | FTSELR               | DNO  | DNO  |

| >      | DNO D  | DNO     | NSS                  | MRST       | NSS    | CQ0L        | COOL   | DNO    | PORTSTD1R | CNTINTR   | BUSYR                | ZQ0R <sup>[13]</sup> | PORTSTD0R                                       | LOWSPDR   | NSS       | CQ0R   | CQ0R   | SSA    | TDI    | ОДТ                  | DNO  | DNO  |

| >      | DNO    | DNU     | VSS                  | NSS        | DNO    | DNO         | DNO    | DNO    | DQ8L      | DQ5L      | DQ2L                 | DQ2R                 | DQ5R                                            | DQ8R      | DNO       | DNU    | DNO    | DNO    | TMS    | TCK                  | DNO  | DNO  |

| ¥      | DNO    | DNO     | DNU                  | DNO        | DNO    | DNO         | DNO    | DNO    | DQ7L      | DQ4L      | DQ1L                 | DQ1R                 | DQ4R                                            | DQ7R      | DNO       | DNU    | DNO    | DNO    | DNO    | DNO                  | DNO  | DNO  |

| AB     | DNO D  | DNO     | DNU                  | DNO        | DNO    | DNO         | NO     | DNO    | DQ6L      | DO3L      | DQ0L                 | DQ0R                 | DQ3R                                            | DQ6R      | DNG       | DNG    | DNO    | NO     | DNO    | ONG                  | DNO  | DNO  |

**Notes** 12. Use this pinout only for device CYD36S18V18 of the FullFlex18 family. 13. Leave this ball unconnected to disable VIM.

Page 6 of 51

## CYPRESS

CYDXXS36V18 CYDXXS18V18

CYDXXS72V18

### Figure 4. FullFlex36 SDR 256-ball BGA (Top View)

|                                                |    |       |       |                      |         |             |         |                      |       |           |             |        |                      |                      |          |       | 1     |

|------------------------------------------------|----|-------|-------|----------------------|---------|-------------|---------|----------------------|-------|-----------|-------------|--------|----------------------|----------------------|----------|-------|-------|

|                                                | 16 | DQ32R | DQ33R | DQ34R                | AOR     | A2R         | A4R     | A6R                  | A8R   | A10R      | A12R        | A14R   | A16R <sup>[17]</sup> | A18R <sup>[15]</sup> | DQ16R    | DQ15R | DQ14R |

|                                                | 15 | DQ30R | DQ31R | DQ35R                | A1R     | A3R         | A5R     | A7R                  | A9R   | A11R      | A13R        | A15R   | A17R <sup>[16]</sup> | DNO                  | DQ17R    | DQ13R | DQ12R |

|                                                | 41 | DQ28R | DQ29R | RETR                 | WRPR    | CE0R        | CNTINTR | BUSYR                | CR    | NSS       | OER         | ADSR   | RWR                  | CNT/MSKR             | CNTENR   | DQ11R | DQ10R |

|                                                | 13 | DQ26R | DQ27R | INTR                 | VREFR   | CE1R        | BE3R    | BE2R                 | VTTL  | PORTSTD1R | <u>BE1R</u> | BEOR   | CQENR                | VREFR                | CNTRSTR  | DQ9R  | DQ8R  |

|                                                | 12 | DQ24R | DQ25R | CQ1R                 | FTSELR  | VDDIOR      | VDDIOR  | VDDIOR               | VCORE | VCORE     | VDDIOR      | VDDIOR | VDDIOR               | PORTSTD0R            | CQ0R     | DQ7R  | DQ6R  |

| (Mala                                          | 7  | DQ22R | DQ23R | CQ1R                 | LOWSPDR | VDDIOR      | NSS     | NSS                  | NSS   | NSS       | NSS         | NSS    | VDDIOR               | READYR               | CQ0R     | DQ5R  | DQ4R  |

| מבו) עסה                                       | 10 | DQ20R | DQ21R | ZQ0R <sup>[14]</sup> | NSS     | VDDIOR      | NSS     | SSA                  | SSA   | SSA       | NSS         | SSA    | VDDIOR               | DNG                  | IQL      | аєба  | DQ2R  |

| igule 4. Full lead our 200-ball box (10p view) | 6  | DQ18R | DQ19R | MRST                 | VTTL    | VCORE       | NSS     | SSA                  | SSA   | SSA       | NSS         | SSA    | VCORE                | VTTL                 | OQL      | DQ1R  | DQ0R  |

| AGC 001                                        | œ  | DQ18L | DQ19L | TRST                 | VTTL    | VCORE       | NSS     | NSS                  | NSS   | NSS       | VSS         | NSS    | VCORE                | VTTL                 | TMS      | DQ1L  | DQ0L  |

|                                                | 7  | DQ20L | DQ21L | DNO                  | VSS     | VDDIOL      | VSS     | NSS                  | NSS   | NSS       | VSS         | NSS    | VDDIOL               | DNO                  | TCK      | DQ3L  | DQ2L  |

| t all de la                                    | 9  | DQ22L | DQ23L | CQ1L                 | LOWSPDL | VDDIOL      | NSS     | SSA                  | SSA   | SSA       | NSS         | SSA    | VDDIOL               | READYL               | <u> </u> | DOSL  | DQ4L  |

|                                                | S. | DQ24L | DQ25L | CQ1L                 | FTSELL  | VDDIOL      | VDDIOL  | ZQ0L <sup>[14]</sup> | VCORE | VCORE     | VDDIOL      | VDDIOL | VDDIOL               | PORTSTD0L            | CQ0L     | DQ7L  | DQ6L  |

|                                                | 4  | DQ26L | DQ27L | <u>INT</u>           | VREFL   | CE1L        | BE3L    | BEZL                 | VTTL  | PORTSTD1L | BE1L        | BEOL   | COENL                | VREFL                | CNTRSTL  | DQ9L  | DQ8L  |

|                                                | က  | DQ28L | DQ29L | RETL                 | WRPL    | <u>CE0L</u> | CNTINTL | BUSYL                | CF    | SSA       | <u>OEL</u>  | ADSL   | R/WL                 | CNT/MSKL             | CNTENL   | DQ11L | DQ10L |

|                                                | 7  | DQ30L | DQ31L | DQ35L                | A1L     | A3L         | A5L     | A7L                  | A9L   | A11L      | A13L        | A15L   | A17L <sup>[16]</sup> | DNO                  | DQ17L    | DQ13L | DQ12L |

|                                                | -  | DQ32L | DQ33L | DQ34L                | AOL     | A2L         | A4L     | A6L                  | A8L   | A10L      | A12L        | A14L   | A16L <sup>[17]</sup> | A18L <sup>[15]</sup> | DQ16L    | DQ15L | DQ14L |

|                                                |    |       |       |                      |         |             |         |                      |       |           |             |        |                      |                      |          |       |       |

Notes

14. Leave this ball unconnected to disable VIM.

15. Leave this ball unconnected for CYD09S36V18 and CYD02S36V18.

16. Leave this ball unconnected for CYD02S36V18.

17. Leave this ball unconnected for CYD02S36V18.

A B

ပ Ω шш

G I 7 ¥ \_ Σ Z ₾ œ

## CYPRESS EMBEDGE IN TOHOGRAPH

CYDXXS36V18 CYDXXS18V18

CYDXXS72V18

### Figure 5. FullFlex18 SDR 256-ball BGA (Top View)

|    |                      |                      |             |           |                      | Ligare  | o. rullrie | AUS SUK | 7.00-Dall | rigure 5. ruiiriex is SDR 256-baii bGA (10p view) | o view) |           |             |            |                      |                      |

|----|----------------------|----------------------|-------------|-----------|----------------------|---------|------------|---------|-----------|---------------------------------------------------|---------|-----------|-------------|------------|----------------------|----------------------|

|    | -                    | 7                    | ო           | 4         | ß                    | 9       | 7          | œ       | 6         | 10                                                | 7       | 12        | 13          | 4          | 15                   | 16                   |

| ⋖  | DNO                  | DNG                  | DNG         | DQ17L     | DQ16L                | DQ13L   | DQ12L      | DQ9L    | DQ9R      | DQ12R                                             | DQ13R   | DQ16R     | DQ17R       | DNG        | DNO                  | DNO                  |

| æ  | DNO                  | DNG                  | DNG         | DNG       | DQ15L                | DQ14L   | DQ11L      | DQ10L   | DQ10R     | DQ11R                                             | DQ14R   | DQ15R     | DNO         | DNO        | DNO                  | DNC                  |

| ပ  | DNO                  | DNO                  | RETL        | INT       | CQ1L                 | CQ1L    | DNC        | TRST    | MRST      | ZQ0R <sup>[18]</sup>                              | CQ1R    | CQ1R      | NTR         | RETR       | DNO                  | DNC                  |

| ٥  | A0L                  | A1L                  | WRPL        | VREFL     | FTSELL               | LOWSPDL | NSS        | VTTL    | VTTL      | NSS                                               | LOWSPDR | FTSELR    | VREFR       | WRPR       | A1R                  | AOR                  |

| ш  | A2L                  | A3L                  | <u>CE0L</u> | CE1L      | VDDIOL               | VDDIOL  | VDDIOL     | VCORE   | VCORE     | VDDIOR                                            | VDDIOR  | VDDIOR    | CE1R        | CEOR       | A3R                  | A2R                  |

| ш  | A4L                  | A5L                  | CNTINTL     | DNO       | VDDIOL               | NSS     | NSS        | NSS     | NSS       | VSS                                               | VSS     | VDDIOR    | DNO         | CNTINTR    | A5R                  | A4R                  |

| O  | A6L                  | A7L                  | BUSYL       | DNG       | ZQ0L <sup>[18]</sup> | NSS     | NSS        | SSA     | NSS       | NSS                                               | NSS     | VDDIOR    | DNO         | BUSYR      | A7R                  | A6R                  |

| I  | A8L                  | A9L                  | CL          | VTTL      | VCORE                | NSS     | NSS        | SSA     | SSA       | SSA                                               | NSS     | VCORE     | VTTL        | CR         | A9R                  | A8R                  |

|    | A10L                 | A11L                 | SSA         | PORTSTD1L | VCORE                | NSS     | NSS        | NSS     | NSS       | NSS                                               | VSS     | VCORE     | PORTSTD1R   | NSS        | A11R                 | A10R                 |

| ×  | A12L                 | A13L                 | <u>0er</u>  | BE1L      | VDDIOL               | \SS     | NSS        | NSS     | NSS       | NSS                                               | VSS     | VDDIOR    | <u>BE1R</u> | <u>OER</u> | A13R                 | A12R                 |

| _  | A14L                 | A15L                 | ADSL        | BEOL      | VDDIOL               | NSS     | NSS        | SSA     | SSA       | SSA                                               | NSS     | VDDIOR    | BEOR        | ADSR       | A15R                 | A14R                 |

| Σ  | A16L                 | A17L                 | R/WL        | CQENL     | VDDIOL               | VDDIOL  | VDDIOL     | VCORE   | VCORE     | VDDIOR                                            | VDDIOR  | VDDIOR    | CQENR       | R/WR       | A17R                 | A16R                 |

| Z  | A18L <sup>[20]</sup> | A19L <sup>[19]</sup> | CNT/MSKL    | VREFL     | PORTSTDOL            | READYL  | DNO        | VTTL    | VTTL      | ONG                                               | READYR  | PORTSTD0R | VREFR       | CNT/MSKR   | A19R <sup>[19]</sup> | A18R <sup>[20]</sup> |

| Δ. | DNO                  | DNG                  | CNTENL      | CNTRSTL   | COOL                 | COOL    | TCK        | TMS     | TDO       | IQL                                               | CQOR    | CQ0R      | CNTRSTR     | CNTENR     | DNO                  | DNC                  |

| œ  | DNO                  | NA                   | NO          | DNG       | DQ6L                 | DQ5L    | DQ2L       | DQ1L    | DQ1R      | DQ2R                                              | DQ5R    | DQ6R      | DNO         | DNO        | DNO                  | DNO                  |

| -  | DNO                  | NA                   | NO          | DQ8L      | DQ7L                 | DQ4L    | DQ3L       | 70OG    | DQ0R      | DQ3R                                              | DQ4R    | DQ7R      | DQ8R        | DNO        | DNO                  | DNO                  |

Notes

18. Leave this ball unconnected to disable VIM.

19. Leave this ball unconnected for CYD09S18V18.

20. Leave this ball unconnected for CYD04S18V18.

Document Number: 38-06082 Rev. \*S

### **Selection Guide**

| Parameter                                                            | -200                | -167                | Unit |

|----------------------------------------------------------------------|---------------------|---------------------|------|

| f <sub>MAX</sub> <sup>[22]</sup>                                     | 200                 | 167                 | MHz  |

| Maximum access time (clock to data)                                  | 3.3                 | 4.0                 | ns   |

| Typical operating current I <sub>CC</sub>                            | 800 <sup>[21]</sup> | 700 <sup>[21]</sup> | mA   |

| Typical standby current for I <sub>SB3</sub> (both ports CMOS level) | 210 <sup>[21]</sup> | 210 <sup>[21]</sup> | mA   |

### **Pin Definitions**

| Left Port             | Right Port            | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[20:0] <sub>L</sub>  | A[20:0] <sub>R</sub>  | Address inputs. <sup>[23]</sup>                                                                                                                                                                                                                                                                                                                                  |

| DQ[71:0] <sub>L</sub> | DQ[71:0] <sub>R</sub> | Data bus input and output. <sup>[24]</sup>                                                                                                                                                                                                                                                                                                                       |

| BE[7:0] <sub>L</sub>  | BE[7:0] <sub>R</sub>  | <b>Byte select inputs.</b> <sup>[25]</sup> Asserting these signals enables read and write operations to the corresponding bytes of the memory array.                                                                                                                                                                                                             |

| BUSY <sub>L</sub>     | BUSY <sub>R</sub>     | <b>Port busy output</b> . When there is an address match and both chip enables are active for both ports, an external BUSY signal is asserted on the fifth clock cycles from when the collision occurs.                                                                                                                                                          |

| C <sub>L</sub>        | C <sub>R</sub>        | Clock signal. Maximum clock input rate is f <sub>MAX</sub> .                                                                                                                                                                                                                                                                                                     |

| CE0 <sub>L</sub>      | CE0 <sub>R</sub>      | Active LOW chip enable input.                                                                                                                                                                                                                                                                                                                                    |

| CE1 <sub>L</sub>      | CE1 <sub>R</sub>      | Active HIGH chip enable input.                                                                                                                                                                                                                                                                                                                                   |

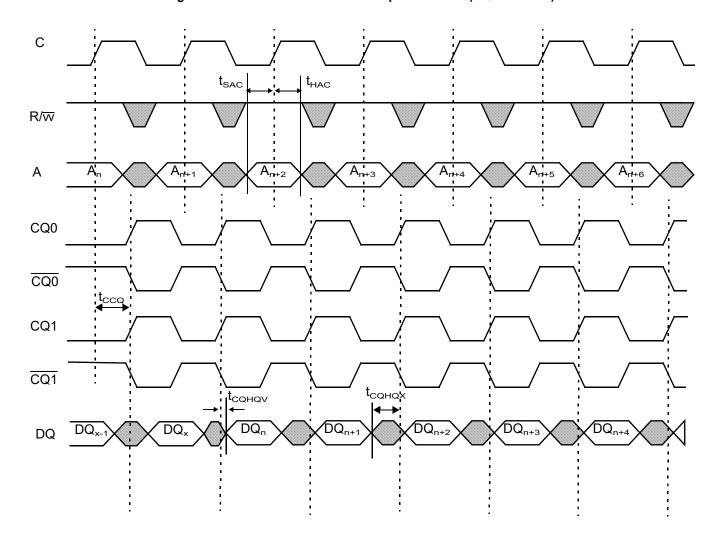

| CQEN <sub>L</sub>     | CQEN <sub>R</sub>     | Echo clock enable input. Assert HIGH to enable echo clocking on respective port.                                                                                                                                                                                                                                                                                 |

| CQ0 <sub>L</sub>      | CQ0 <sub>R</sub>      | Echo clock signal output for DQ[35:0] for FullFlex72 devices. Echo clock signal output for DQ[17:0] for FullFlex36 devices. Echo clock signal output for DQ[8:0] for FullFlex18 devices.                                                                                                                                                                         |

| CQ0 <sub>L</sub>      | CQ0 <sub>R</sub>      | Inverted echo clock signal output for DQ[35:0] for FullFlex72 devices. Inverted echo clock signal output for DQ[17:0] for FullFlex36 devices. Inverted echo clock signal output for DQ[8:0] for FullFlex18 devices.                                                                                                                                              |

| CQ1 <sub>L</sub>      | CQ1 <sub>R</sub>      | Echo clock signal output for DQ[71:36] for FullFlex72 devices. Echo clock signal output for DQ[35:18] for FullFlex36 devices. Echo clock signal output for DQ[17:9] for FullFlex18 devices.                                                                                                                                                                      |

| CQ1 <sub>L</sub>      | CQ1 <sub>R</sub>      | Inverted echo clock signal output for DQ[71:36] for FullFlex72 devices. Inverted echo clock signal output for DQ[35:18] for FullFlex36 devices. Inverted echo clock signal output for DQ[17:9] for FullFlex18 devices.                                                                                                                                           |

| ZQ[1:0] <sub>L</sub>  | ZQ[1:0] <sub>R</sub>  | VIM output impedance matching input. [26] To use, connect a calibrating resistor between ZQ and ground. The resistor must be five times larger than the intended line impedance driven by the dual port. Assert HIGH or leave DNU to disable VIM.                                                                                                                |

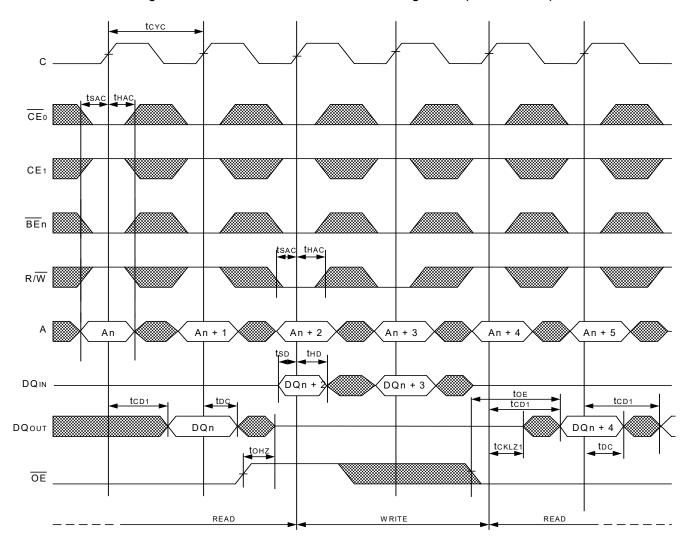

| ŌĒL                   | ŌĒ <sub>R</sub>       | Output enable input. This asynchronous signal must be asserted LOW to enable the DQ data pins during read operations.                                                                                                                                                                                                                                            |

| INT <sub>L</sub>      | ĪNT <sub>R</sub>      | <b>Mailbox interrupt flag output</b> . The mailbox permits communications between ports. The upper two memory locations are used for message passing. INT <sub>L</sub> is asserted LOW when the right port writes to the mailbox location of the left port, and vice versa. An interrupt to a port is deasserted HIGH when it reads the contents of its mailbox. |

- 21. For 18 Mbit x72 commercial configuration only; refer to Electrical Characteristics on page 19 for complete information. 22. SDR mode with two pipelined stages.

- 23. The CYD36S18V18 device has 21 address bits. The CYD36S36V18 and CYD08S18V18 devices have 20 address bits. The CYD36S72V18, CYD18S36V18, and CYD09S18V18 devices have 19 address bits. The CYD18S72V18 and CYD09S36V18 devices have 18 address bits. The CYD09S72V18 device has 17 address bits. The CYD02S36V18 has 16 address bits.

- 24. The FullFlex72 family of devices has 72 data lines. The FullFlex36 family of devices has 36 data lines. The FullFlex18 family of devices has 18 data lines.

- 25. The FullFlex72 family of devices has eight byte enables. The FullFlex36 family of devices has four byte enables. The FullFlex18 family of devices has two byte enables. 26. The pin ZQ[1] is applicable only for 36 Mbit devices. This pin is DNU for 18 Mbit and lower density devices.

### Pin Definitions (continued)

| Left Port                                 | Right Port                                | Description                                                                                                                                                                                                                                                               |  |  |  |  |

|-------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LowSPD <sub>L</sub>                       | LowSPD <sub>R</sub>                       | <b>Port low speed select input</b> . Assert this pin LOW to disable the DLL. In flow through mode, this pin needs to be asserted low.                                                                                                                                     |  |  |  |  |

| PORTSTD[1:0] <sub>L</sub> <sup>[27,</sup> | PORTSTD[1:0] <sub>R</sub> <sup>[27,</sup> | Port clock/Address/Control/Data/Echo clock/I/O standard select input. Assert these pins LOW/LOW for LVTTL, LOW/HIGH for HSTL, HIGH/LOW for 2.5 V LVCMOS, and HIGH/HIGH for 1.8 V LVCMOS, respectively. These pins are driven by VTTL referenced levels.                   |  |  |  |  |

| $R/\overline{W}_L$                        | R/W <sub>R</sub>                          | <b>Read/Write enable input</b> . Assert this pin LOW to write to, or HIGH to read from the dual port memory array.                                                                                                                                                        |  |  |  |  |

| READY <sub>L</sub>                        | READY <sub>R</sub>                        | <b>Port DLL ready output</b> . This signal is asserted LOW when the DLL and variable impedance matching circuits complete calibration. This is a wired OR capable output.                                                                                                 |  |  |  |  |

| CNT/MSK <sub>L</sub>                      | CNT/MSK <sub>R</sub>                      | Port counter/Mask select input. Counter control input.                                                                                                                                                                                                                    |  |  |  |  |

| ADS <sub>L</sub>                          | ADS <sub>R</sub>                          | Port counter address load strobe input. Counter control input.                                                                                                                                                                                                            |  |  |  |  |

| CNTENL                                    | CNTENR                                    | Port counter enable input. Counter control input.                                                                                                                                                                                                                         |  |  |  |  |

| CNTRST <sub>L</sub>                       | CNTRST <sub>R</sub>                       | Port counter reset input. Counter control input.                                                                                                                                                                                                                          |  |  |  |  |

| CNTINT <sub>L</sub>                       | CNTINT <sub>R</sub>                       | <b>Port counter interrupt output</b> . This pin is asserted LOW one cycle before the unmasked portion of the counter is incremented to all "1s".                                                                                                                          |  |  |  |  |

| WRPL                                      | WRP <sub>R</sub>                          | <b>Port counter wrap input</b> . When the burst counter reaches the maximum count, on the next counter increment WRP is set LOW to load the unmasked counter bits to 0. It is set HIGH to load the counter with the value stored in the mirror register.                  |  |  |  |  |

| RET <sub>L</sub>                          | RET <sub>R</sub>                          | <b>Port counter retransmit input</b> . Assert this pin LOW to reload the initial address for repeated access to the same segment of memory.                                                                                                                               |  |  |  |  |

| VREF <sub>L</sub> <sup>[28]</sup>         | VREF <sub>R</sub> <sup>[28]</sup>         | Port external HSTL I/O reference input. This pin is left DNU when HSTL is not used.                                                                                                                                                                                       |  |  |  |  |

| VDDIO <sub>L</sub>                        | VDDIO <sub>R</sub>                        | Port data I/O power supply.                                                                                                                                                                                                                                               |  |  |  |  |

| FTSEL                                     | FTSEL <sub>R</sub>                        | <b>Port flow through mode select input</b> . Assert this pin LOW to select flow through mode. Assert this pin HIGH to select Pipelined mode.                                                                                                                              |  |  |  |  |

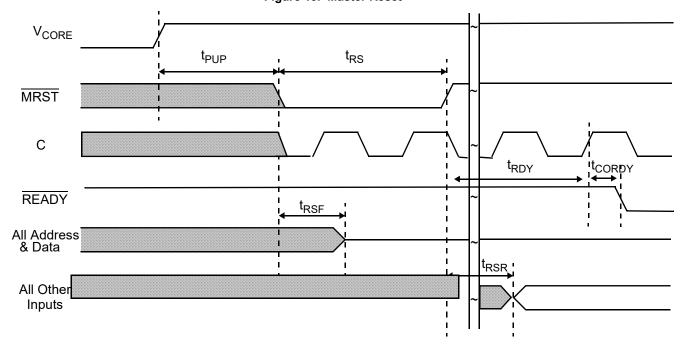

| MRST                                      |                                           | Master reset input. MRST is an asynchronous input signal and affects both ports. Asserting MRST LOW performs all of the reset functions as described in the text. A MRST operation is required at power up. This pin is driven by a VDDIO <sub>L</sub> referenced signal. |  |  |  |  |

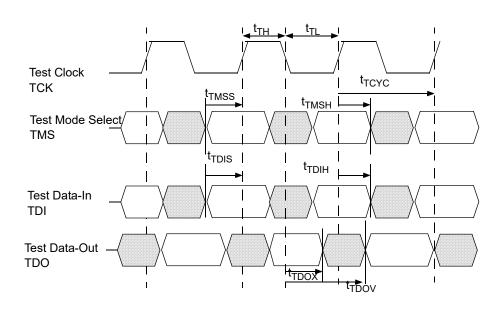

| TMS                                       |                                           | <b>JTAG test mode select input</b> . It controls the advance of JTAG TAP state machine. State machine transitions occur on the rising edge of TCK. Operation for LVTTL or 2.5 V LVCMOS.                                                                                   |  |  |  |  |

| TDI                                       |                                           | JTAG test data input. Data on the TDI input is shifted serially into selected registers. Operation for LVTTL or 2.5 V LVCMOS.                                                                                                                                             |  |  |  |  |

| TRST                                      |                                           | JTAG reset input. Operation for LVTTL or 2.5 V LVCMOS.                                                                                                                                                                                                                    |  |  |  |  |

| TCK                                       |                                           | JTAG test clock input. Operation for LVTTL or 2.5 V LVCMOS.                                                                                                                                                                                                               |  |  |  |  |

| TDO                                       |                                           | <b>JTAG test data output</b> . TDO transitions occur on the falling edge of TCK. TDO is normally tri-stated except when captured data is shifted out of the JTAG TAP. Operation for LVTTL or 2.5 V LVCMOS.                                                                |  |  |  |  |

| VSS                                       |                                           | Ground inputs.                                                                                                                                                                                                                                                            |  |  |  |  |

| VCORE                                     |                                           | Device core power supply.                                                                                                                                                                                                                                                 |  |  |  |  |

| VTTL                                      |                                           | LVTTL power supply.                                                                                                                                                                                                                                                       |  |  |  |  |

Document Number: 38-06082 Rev. \*S Page 10 of 51

Notes

27. PORTSTD[1:0]<sub>L</sub> and PORTSTD[1:0]<sub>R</sub> have internal pull-down resistors.

28. HSTL support and the corresponding tests support has been removed from the device from WW1830. This change does not impact any other functionality.

### **Functional Overview**

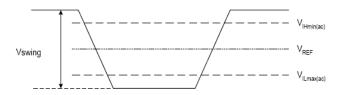

### Selectable I/O Standard

The FullFlex device families offer the option to choose one of the four port standards for the device. Each port independently selects standards from single-ended HSTL class I, single-ended LVTTL, 2.5 V LVCMOS, or 1.8 V LVCMOS. The selection of the standard is determined by the PORTSTD pins for each port. These pins must be connected to an LVTTL power suppy. This determines the input clock, address, control, data, and Echo clock standard for each port as shown in Table 1.

Table 1. Port Standard Selection

| PORTSTD1 | PORTSTD0 | I/O Standard |

|----------|----------|--------------|

| VSS      | VSS      | LVTTL        |

| VSS      | VTTL     | HSTL         |

| VTTL     | VSS      | 2.5 V LVCMOS |

| VTTL     | VTTL     | 1.8 V LVCMOS |

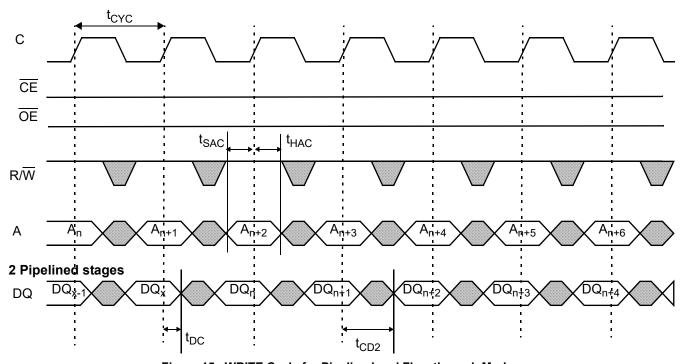

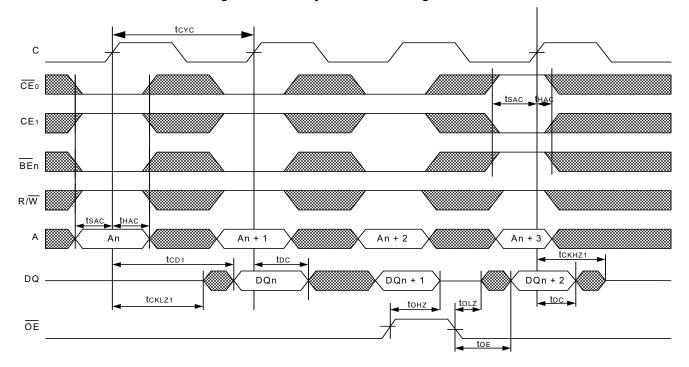

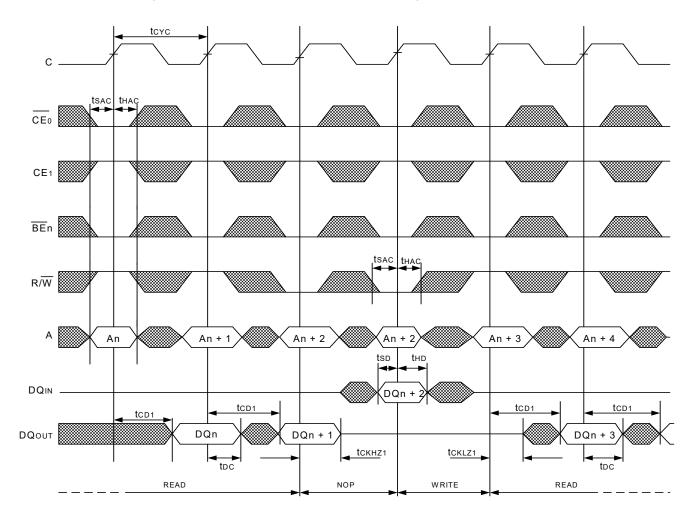

### Clocking

Separate clocks synchronize the operations on each port. Each port has one clock input C. In this mode, all the transactions on the address, control, and data are on the C rising edge. All transactions on the address, control, data input, output, and byte enables occur on the C rising edge.

Table 2. Data Pin Assignment

| BE Pin Name | Data Pin Name |

|-------------|---------------|

| BE[7]       | DQ[71:63]     |

| BE[6]       | DQ[62:54]     |

| BE[5]       | DQ[53:45]     |

| BE[4]       | DQ[44:36]     |

| BE[3]       | DQ[35:27]     |

| BE[2]       | DQ[26:18]     |

| BE[1]       | DQ[17:9]      |

| BE[0]       | DQ[8:0]       |

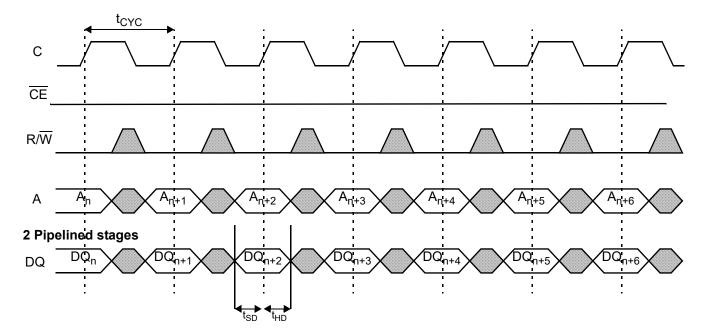

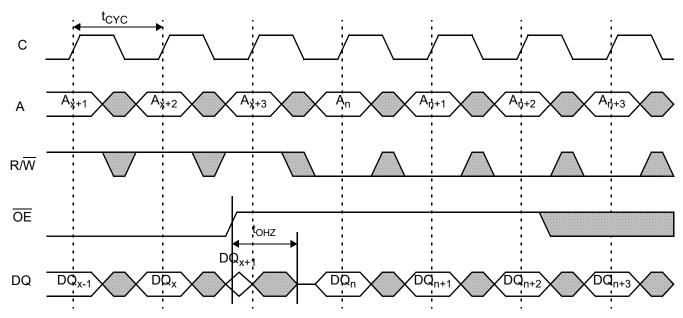

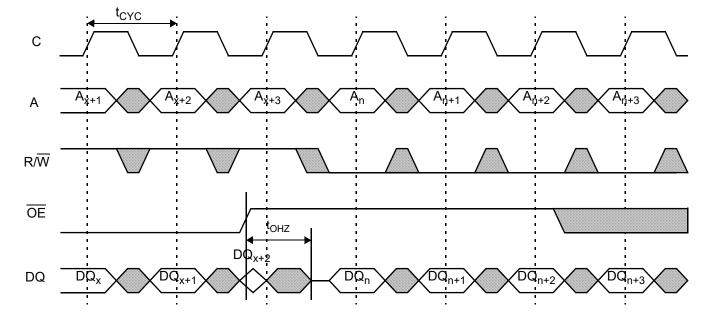

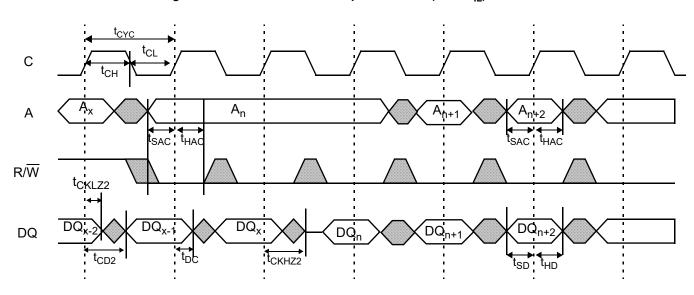

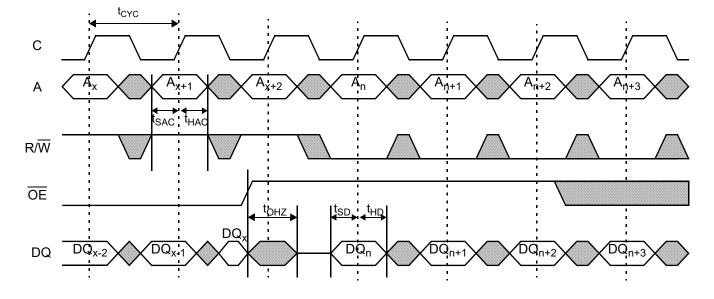

### Selectable Pipelined or Flow through Mode

To meet data rate and throughput requirements, the FullFlex families offer selectable pipelined or flow through mode. Echo clocks are not supported in flow through mode and the DLL must be disabled.

Flow through mode is selected by the FTSEL pin. Strapping this pin HIGH selects pipelined mode. Strapping this pin LOW selects flow through mode.

### DLL

The FullFlex familes of devices have an on-chip DLL. Enabling the DLL reduces the clock to data valid ( $t_{\rm CD}$ ) time enabling more setup time for the receiving device. In flow through mode, the DLL must be disabled. This is selectable by strapping LowSPD low.

Whenever the operating frequency is altered beyond the Clock Input Cycle to Cycle Jitter specification, reset the DLL, followed by 1024 clocks before any valid operation.

LowSPD pins are used to reset the DLLs for a single port independent of all other circuitry. MRST is used to reset all DLLs on the chip. For more information on DLL lock and reset time, see Master Reset on page 18.

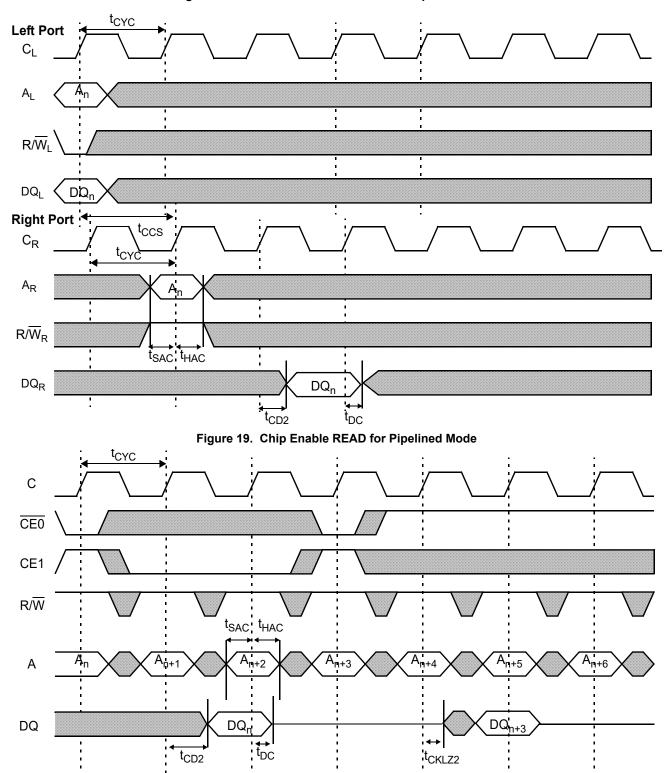

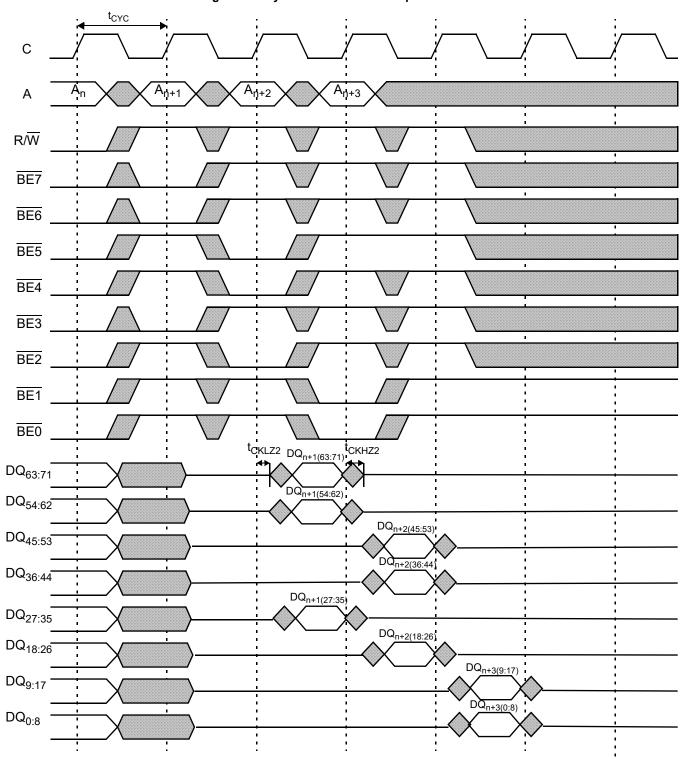

### **Echo Clocking**

As the speed of data increases, on-board delays caused by parasitics make it extremely difficult to provide accurate clock trees. To counter this problem, the FullFlex families incorporate Echo Clocks. Echo Clocks are enabled on a per port basis. The dual port receives input clocks that are used to clock in the address and control signals for a read operation. The dual port retransmits the input clocks relative to the data output. The buffered clocks are provided on the CQ1/CQ1 and CQ0/CQ0 outputs. Each port has a pair of Echo clocks. Each clock is associated with half the data bits. The output clock matches the corresponding ports I/O configuration.

To enable echo clock outputs, tie CQEN HIGH. To disable echo clock outputs, tie CQEN LOW.

Data Out XXX

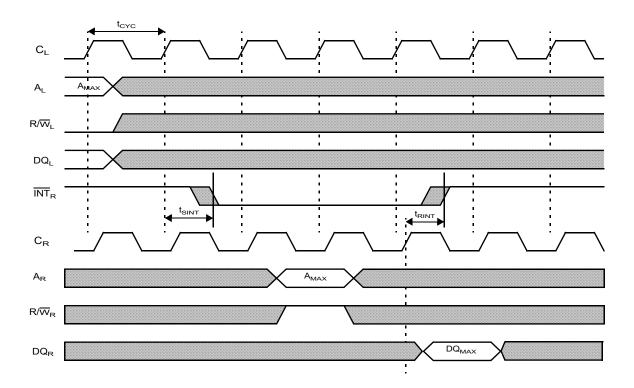

Figure 6. SDR Echo Clock Delay

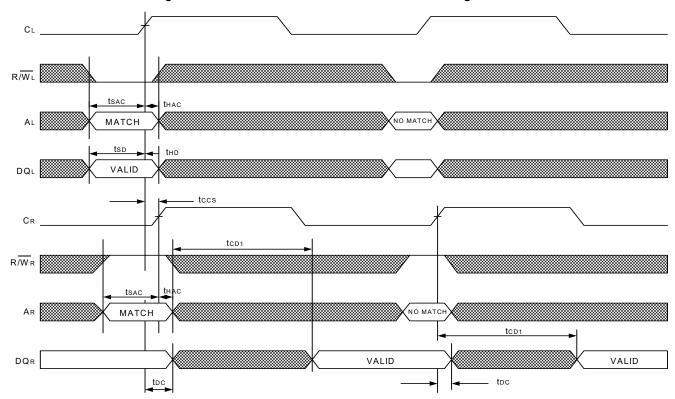

### **Deterministic Access Control**

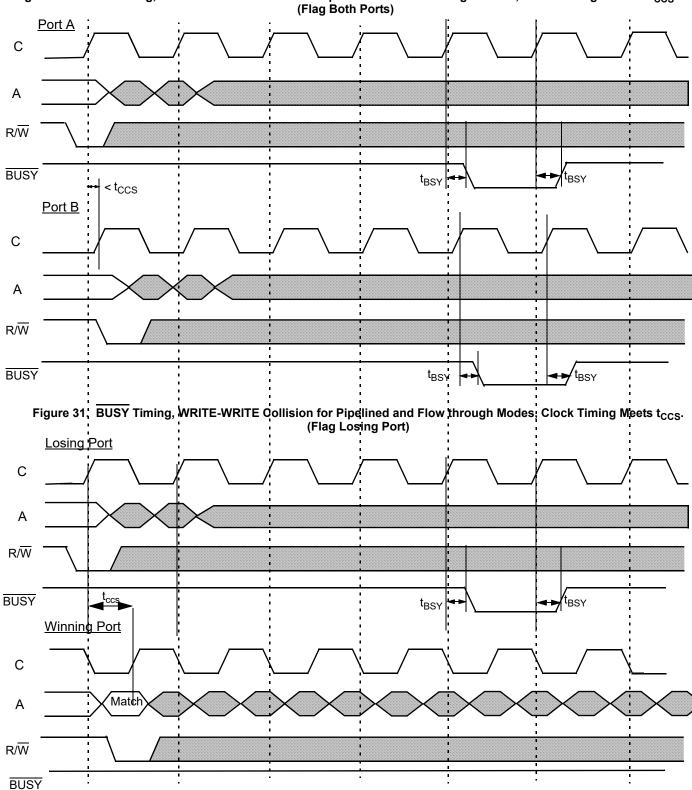

Echo Clock

Deterministic Access Control is provided for ease of design. The circuitry detects when both ports access the same location and provides an external BUSY flag to the port on which data is corrupted. The collision detection logic saves the address in conflict (Busy Address) to a readable register. In the case of multiple collisions, the first busy address is written to the busy address register.

If both ports access the same location at the same time and only one port is doing a write, if  $t_{CCS}$  is met, then the data written to and read from the address is valid data. For example, if the right port is reading and the left port is writing and the left ports clock meets  $t_{CCS}$ , then the data read from the address by the right port is the old data. In the same case, if the right ports clock meets  $t_{CCS}$ , then the data read out of the address from the right port is the new data. In the above case, if  $t_{CCS}$  is violated by the either ports clock with respect to the other port and the right port gets the external BUSY flag, the data from the right port is corrupted. Table 3 on page 12 shows the  $t_{CCS}$  timing that must be met to quarantee the data.

Table 4 on page 12 shows that, in the case of the left port writing and the right port reading, when an external BUSY flag is asserted on the right port, the data read out of the device is not quaranteed.

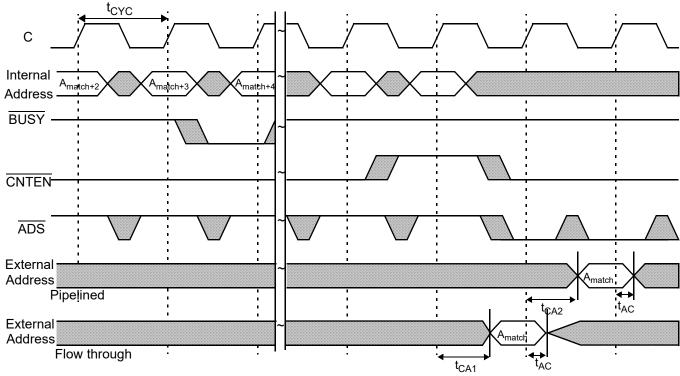

The value in the busy address register is read back to the address lines. The required input control signals for this function are shown in Table 7 on page 14. The value in the busy address register is read out to the address lines  $t_{\text{CA}}$  after the same

amount of latency as a data read operation. After an initial address match, the BUSY flag is asserted and the address under contention is saved in the busy address register. All the following address matches enable to generate the BUSY flag. However,

none of the addresses are saved into the busy address register. When a busy readback is performed, the address of the first match that happens at least two clocks cycles after the busy readback is saved into the busy address register.

Table 3. t<sub>CCS</sub> Timing for All Operating Modes

| Port A - Early | Arriving Port | Port B - Late | Arriving Port | t <sub>CCS</sub>                                          | Unit  |

|----------------|---------------|---------------|---------------|-----------------------------------------------------------|-------|

| Mode           | Active Edge   | Mode          |               | C Rise to Opposite C Rise Setup Time for Non Corrupt Data | Oilit |

| SDR            | С             | SDR           | С             | $t_{CYC(min)} - 0.5$                                      | ns    |

Table 4. Deterministic Access Control Logic

| Left Port | Right Port | Left Clock         | Right Clock                             | BUSYL | BUSYR | Description                  |

|-----------|------------|--------------------|-----------------------------------------|-------|-------|------------------------------|

| Read      | Read       | Х                  | Х                                       | Н     | Н     | No collision                 |

| Write     | Read       | > t <sub>CCS</sub> | 0                                       | Н     | Н     | Read OLD data                |

|           |            | 0                  | > t <sub>CCS</sub>                      | Н     | Н     | Read NEW data                |

|           |            | < t <sub>CCS</sub> | 0                                       | Н     | Н     | Read OLD data                |

|           |            |                    |                                         | Н     | L     | Data not guaranteed          |

|           |            | 0                  | < t <sub>CCS</sub>                      | Н     | Н     | Read NEW data                |

|           |            |                    |                                         | Н     | L     | Data Not guaranteed          |

| Read      | Write      | > t <sub>CCS</sub> | 0                                       | Н     | Н     | Read NEW data                |

|           |            | 0                  | > t <sub>CCS</sub>                      | Н     | Н     | Read OLD data                |

|           |            | < t <sub>CCS</sub> | 0                                       | Н     | Н     | Read NEW data                |

|           |            |                    |                                         | L     | Н     | Data Not guaranteed          |

|           |            | 0                  | < t <sub>CCS</sub>                      | Н     | Н     | Read OLD data                |

|           |            |                    |                                         | L     | Н     | Data not guaranteed          |

| Write     | Write      | 0                  | >-t <sub>CCS</sub> & < t <sub>CCS</sub> | L     | L     | Array data corrupted         |

|           |            | 0                  | > t <sub>CCS</sub>                      | L     | Н     | Array stores right port data |

|           |            | > t <sub>CCS</sub> | 0                                       | Н     | L     | Array stores left port data  |

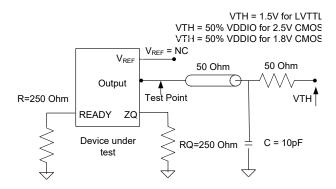

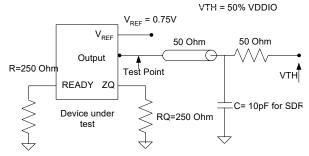

### Variable Impedance Matching

Each port contains a variable impedance matching circuit to set the impedance of the I/O driver to match the impedance of the on-board traces. The impedance is set for all outputs except JTAG and is done by port. To take advantage of the VIM feature, connect a calibrating resistor (RQ) that is five times the value of the intended line impedance from the  $\mathrm{ZQ}_{[1:0]}^{[29]}$  pin to  $\mathrm{V}_{SS}$ . The output impedance is then adjusted to account for drifts in supply voltage and temperature every 1024 clock cycles. If a port's clock is suspended, the VIM circuit retains its last setting until the clock is restarted. On restart, it then resumes periodic adjustment. In the case of a significant change in device temperature or supply voltage, recalibration happens every 1024 clock cycles. A master reset initializes the VIM circuitry. Table 5 shows the VIM parameters and Table 6 describes the VIM operation modes.

To disable VIM, connect the ZQ pin to VDDIO of the relative supply for the I/Os before a Master Reset.

Table 5. Variable Impedance Matching Parameters

| Parameter        | Min | Max  | Unit   | Tolerance |

|------------------|-----|------|--------|-----------|

| RQ value         | 100 | 275  | Ω      | ±2%       |

| Output impedance | 20  | 55   | Ω      | ±15%      |

| Reset time       | -   | 1024 | Cycles | _         |

| Update time      | _   | 1024 | Cycles | _         |

**Table 6. Variable Impedance Matching Operation**

| RQ Connection                                 | Output Configuration                                    |

|-----------------------------------------------|---------------------------------------------------------|

| 100 $\Omega$ –275 $\Omega$ to V <sub>SS</sub> | Output driver impedance = RQ/5 ± 15% at Vout = VDDIO/2  |

|                                               | VIM disabled. Rout $\leq$ 20 $\Omega$ at Vout = VDDIO/2 |

### Note

29. The pin ZQ[1] is applicable only for 36 Mbit devices. This pin is DNU for 18 Mbit and lower density devices.

Document Number: 38-06082 Rev. \*S Page 12 of 51

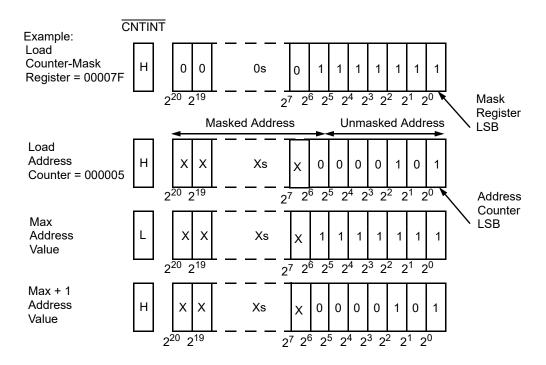

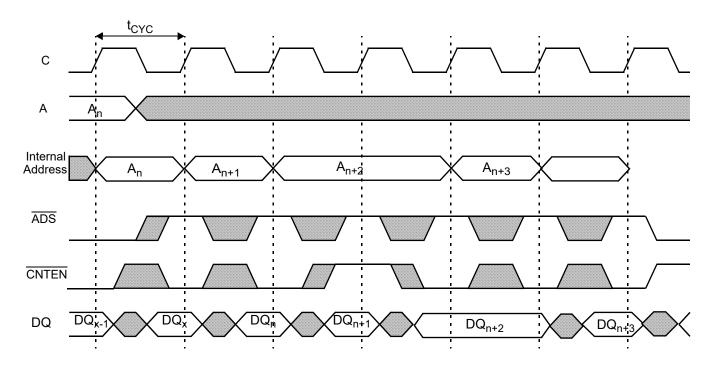

### Address Counter and Mask Register Operations [30]

Each port of the FullFlex family contains a programmable burst address counter. The burst counter contains four registers: a counter register, a mask register, a mirror register, and a busy address register.

The **counter register** contains the address used to access the RAM array. It is changed only by the master reset (MRST), counter reset, counter load, retransmit, and counter increment operations.

The mask register value affects the counter increment and counter reset operations by preventing the corresponding bits of the counter register from changing. It also affects the counter interrupt output (CNTINT). The mask register is only changed by mask reset, mask load, and MRST. The mask load operation loads the value of the address bus into the mask register. The mask register defines the counting range of the counter register. The mask register is divided into two or three consecutive regions. Zero or more 0s define the masked region and one or more 1s define the unmasked portion of the counter register. The counter register may be divided up to three regions. The region containing the least significant bits must be no more than two 0s. Bits one and zero may be 10 respectively, masking the least significant counter bit and causing the counter to increment by two instead of one. If bits one and zero are 00, the two least significant bits are masked and the counter increments by four instead of one. For example, in the case of a 256 K × 72 configuration, a mask register value of 003FC divides the mask register into three regions. With bit 0 being the least significant bit and bit 17 being the most significant bit, the two least significant bits are masked, the next eight bits are unmasked, and the remaining bits are masked.

The **mirror register** reloads a counter register on retransmit operations (see Retransmit on page 15) and wrap functions (see Counter Interrupt on page 15 below). The last value loaded into the counter register is stored in the mirror register. The mirror register is only changed by master reset (MRST), counter reset, and counter load.

Table 7 on page 14 summarizes the operations of these registers and the required input control signals. All signals except MRST are synchronized to the ports clock.

### Counter Load Operation [30]

For both non-burst and burst read or write accesses, the external address is loaded through counter load operation as shown in Table 7 on page 14. The address counter and mirror registers are loaded with the address value presented on the address lines. This value ranges from 0 to 1FFFFF.

### Mask Load Operation [30]

The mask register is loaded with the address value presented on the address bus. This value ranges from 0 to 1FFFFF though not all values permit correct increment operations. Permitted values are in the form of  $2^n-1$ ,  $2^n-2$ , or  $2^n-4$ . The counter register is only segmented up to three regions. From the most significant bit to the least significant bit, permitted values have zero or more 0s, one or more 1s, and the least significant two bits are 11, 10, or 00. Thus 1FFFFE, 07FFFF, and 003FFC are permitted values but 02FFFF, 003FFA, and 07FFE4 are not.

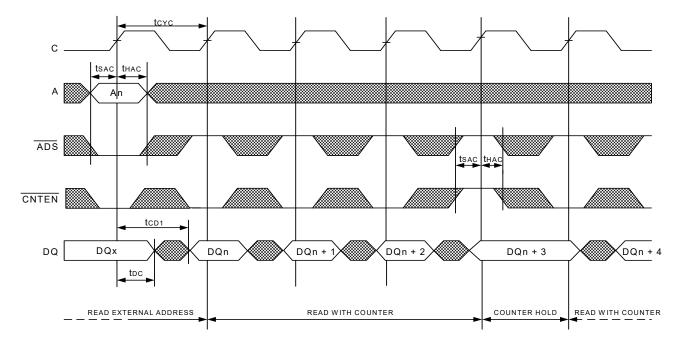

### **Counter Readback Operation**

The internal value of the counter register is read out on the address lines. The address is valid  $\underline{t_{CA}}$  after the selected number of latency cycles configured by FTSEL. The data bus (DQ) is tri-stated on the cycle that the address is presented on the address lines. Figure 7 on page 16 shows a block diagram of this logic.

### Mask Readback Operation

The internal value of the mask register is read out on the address lines. The address is valid  $t_{CA}$  after the selected number of latency cycles configured by FTSEL. The data bus (DQ) is tri-stated on the cycle that the address is presented on the address lines. Figure 7 on page 16 shows a block diagram of the operation.

### **Counter Reset Operation**

All unmasked bits of the counter and mirror registers are reset to '0'. All masked bits remain unchanged. A mask reset followed by a counter reset resets the counter and mirror registers to 00000.

### **Mask Reset Operation**

The mask register is reset to all 1s, that unmasks every bit of the burst counter.

### Note

<sup>30.</sup> The CYD36S18V18 device has 21 address bits. The CYD36S36V18 and CYD18S18V18 devices have 20 address bits. The CYD36S72V18, CYD18S36V18, and CYD09S18V18 devices have 19 address bits. The CYD09S72V18 device has 17 address bits. The CYD02S36V18 has 16 address bits.

### Table 7. Burst Counter and Mask Register Control Operations