|        | DESCRIPTION                                     |    |  |  |  |  |  |  |

|--------|-------------------------------------------------|----|--|--|--|--|--|--|

|        | DESCRIPTION                                     |    |  |  |  |  |  |  |

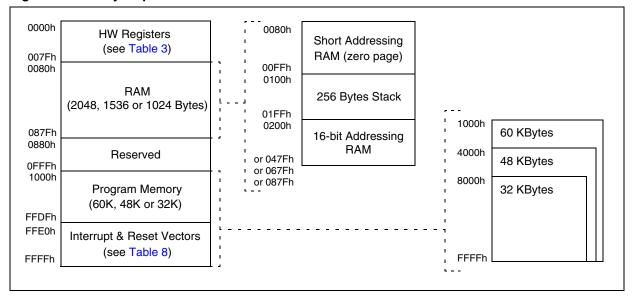

|        | ISTER & MEMORY MAP                              |    |  |  |  |  |  |  |

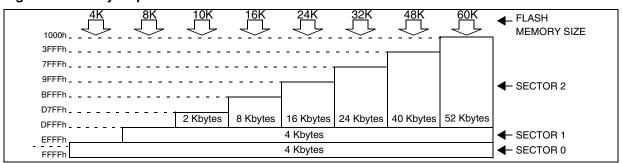

|        | SH PROGRAM MEMORY                               |    |  |  |  |  |  |  |

|        | INTRODUCTION                                    |    |  |  |  |  |  |  |

|        | MAIN FEATURES                                   |    |  |  |  |  |  |  |

| 4.3    | STRUCTURE                                       | 18 |  |  |  |  |  |  |

|        | 4.3.1 Read-out Protection                       |    |  |  |  |  |  |  |

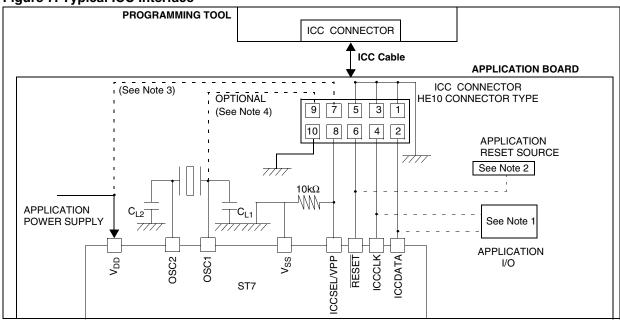

|        | ICC INTERFACE                                   |    |  |  |  |  |  |  |

|        | ICP (IN-CIRCUIT PROGRAMMING)                    |    |  |  |  |  |  |  |

| 4.6    | IAP (IN-APPLICATION PROGRAMMING)                | 20 |  |  |  |  |  |  |

| 4.7    | RELATED DOCUMENTATION                           |    |  |  |  |  |  |  |

|        | 4.7.1 Register Description                      |    |  |  |  |  |  |  |

|        | TRAL PROCESSING UNIT                            |    |  |  |  |  |  |  |

|        | INTRODUCTION                                    |    |  |  |  |  |  |  |

|        | MAIN FEATURES                                   |    |  |  |  |  |  |  |

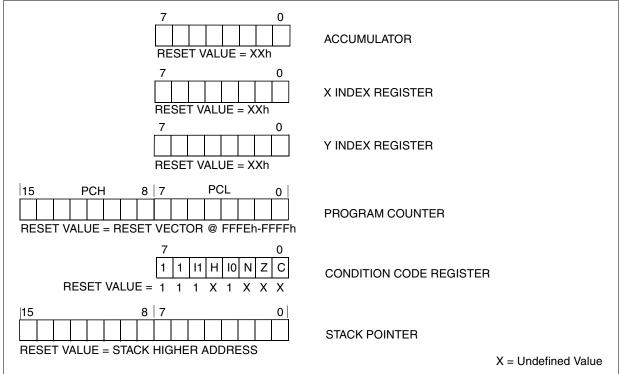

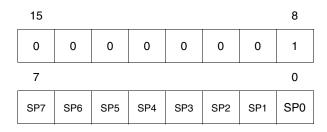

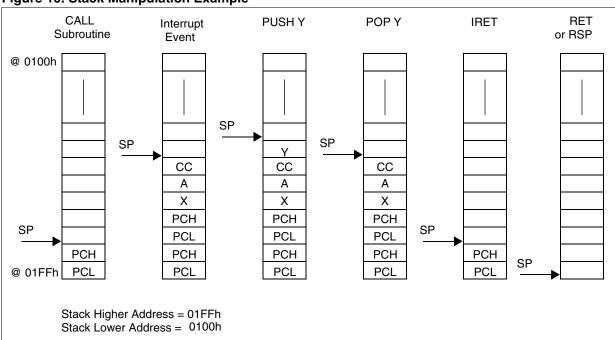

|        | CPU REGISTERS                                   |    |  |  |  |  |  |  |

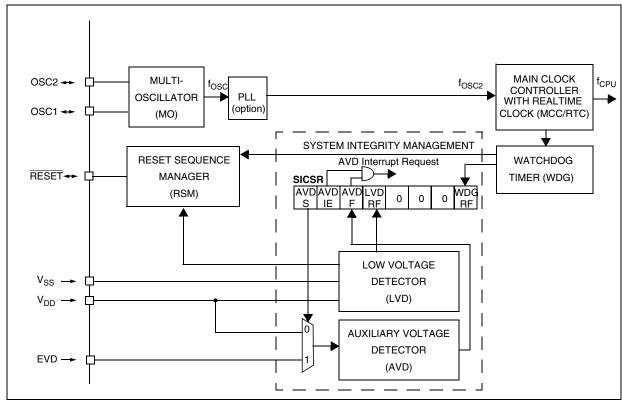

|        | PLY, RESET AND CLOCK MANAGEMENT                 |    |  |  |  |  |  |  |

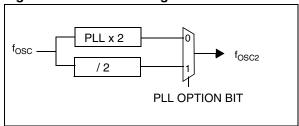

|        | PHASE LOCKED LOOP                               |    |  |  |  |  |  |  |

|        | MULTI-OSCILLATOR (MO)                           |    |  |  |  |  |  |  |

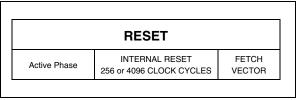

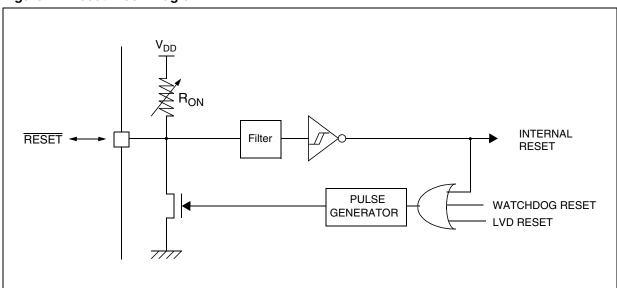

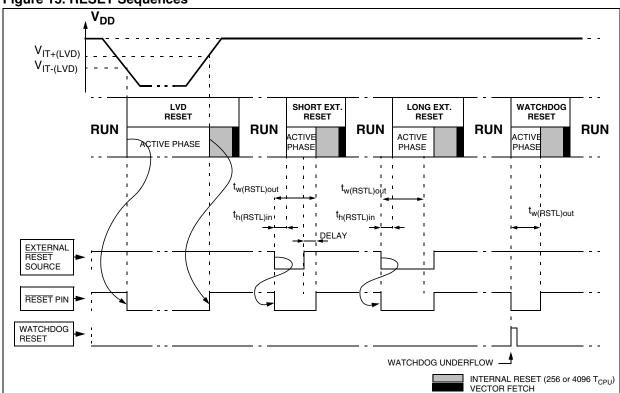

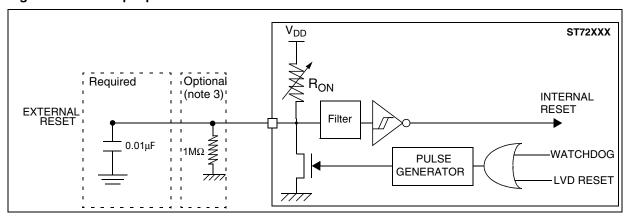

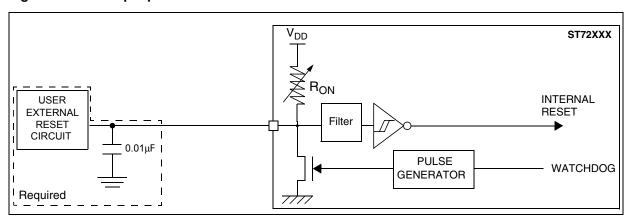

| 6.3    | RESET SEQUENCE MANAGER (RSM)                    | 26 |  |  |  |  |  |  |

|        | 6.3.1 Introduction                              |    |  |  |  |  |  |  |

|        | 6.3.2 Asynchronous External RESET pin           |    |  |  |  |  |  |  |

|        | 6.3.3 External Power-On RESET                   |    |  |  |  |  |  |  |

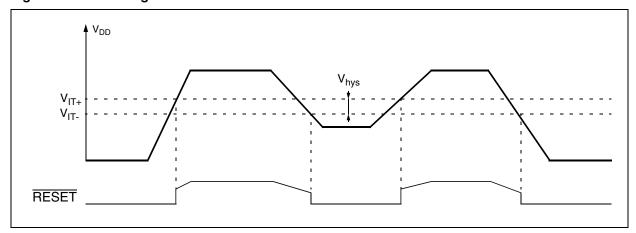

|        | 6.3.4 Internal Low Voltage Detector (LVD) RESET |    |  |  |  |  |  |  |

| 6.4    | SYSTEM INTEGRITY MANAGEMENT (SI)                |    |  |  |  |  |  |  |

|        | 6.4.1 Low Voltage Detector (LVD)                |    |  |  |  |  |  |  |

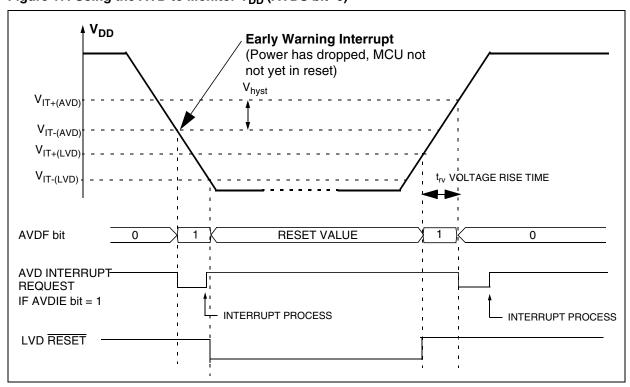

|        | 6.4.2 Auxiliary Voltage Detector (AVD)          |    |  |  |  |  |  |  |

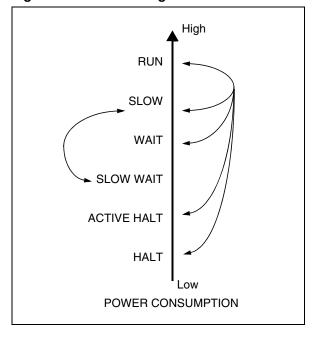

|        | 6.4.3 Low Power Modes                           |    |  |  |  |  |  |  |

|        | 6.4.4 Register Description                      |    |  |  |  |  |  |  |

| 7 INTE | RRUPTS                                          |    |  |  |  |  |  |  |

| 7.1    | INTRODUCTION                                    |    |  |  |  |  |  |  |

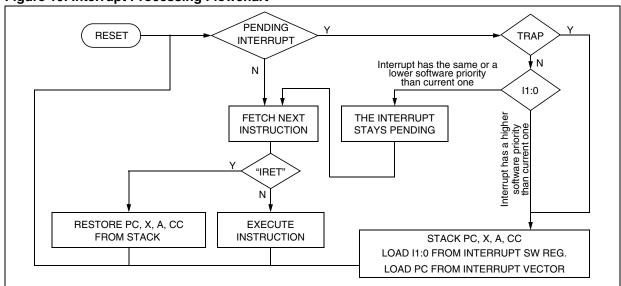

|        | MASKING AND PROCESSING FLOW                     |    |  |  |  |  |  |  |

|        | INTERRUPTS AND LOW POWER MODES                  |    |  |  |  |  |  |  |

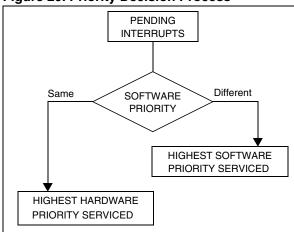

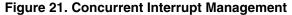

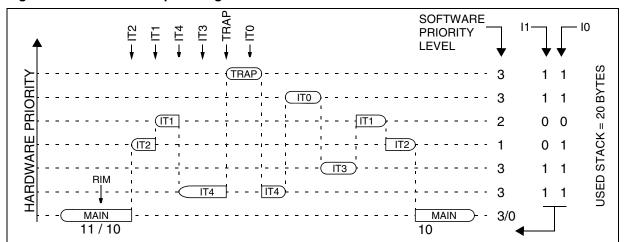

|        | CONCURRENT & NESTED MANAGEMENT                  |    |  |  |  |  |  |  |

|        | INTERRUPT REGISTER DESCRIPTION                  |    |  |  |  |  |  |  |

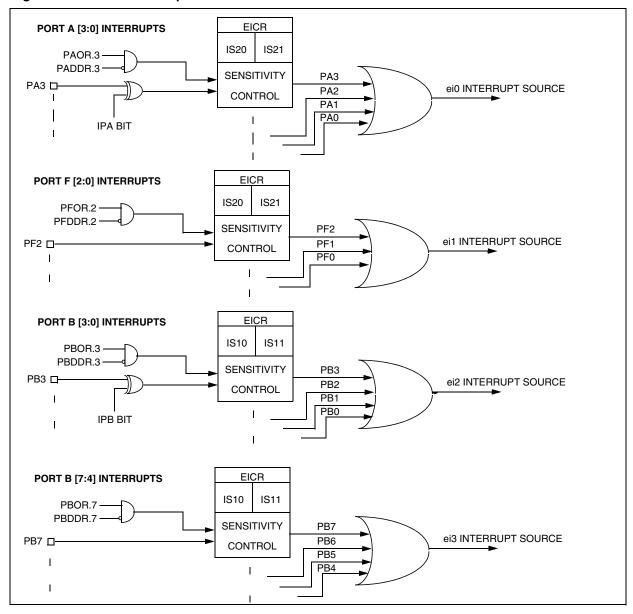

| 7.6    | EXTERNAL INTERRUPTS                             |    |  |  |  |  |  |  |

|        | 7.6.1 I/O Port Interrupt Sensitivity            |    |  |  |  |  |  |  |

|        | EXTERNAL INTERRUPT CONTROL REGISTER (EICR)      |    |  |  |  |  |  |  |

|        | ER SAVING MODES                                 |    |  |  |  |  |  |  |

|        | INTRODUCTION                                    |    |  |  |  |  |  |  |

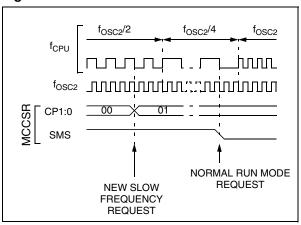

|        | SLOW MODE                                       |    |  |  |  |  |  |  |

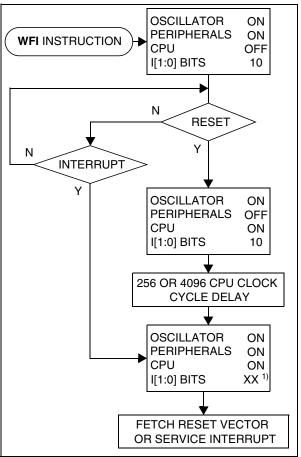

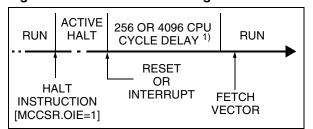

| 8.3    | WAIT MODE                                       | 42 |  |  |  |  |  |  |

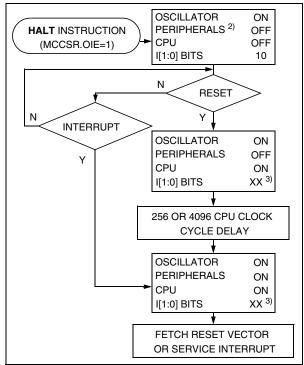

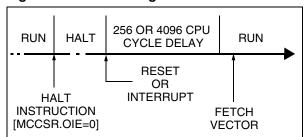

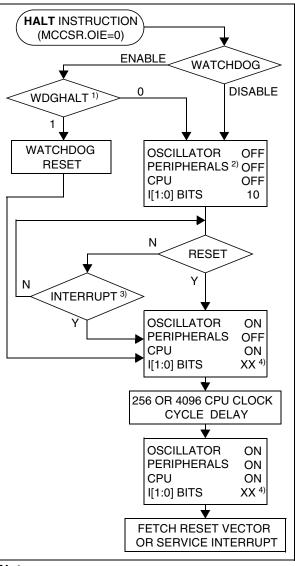

| 8.4    | ACTIV    | E-HALT AND HALT MODES                         | 43 |  |  |  |  |  |  |  |

|--------|----------|-----------------------------------------------|----|--|--|--|--|--|--|--|

|        | 8.4.1    | ACTIVE-HALT MODE                              | 43 |  |  |  |  |  |  |  |

|        | 8.4.2    |                                               |    |  |  |  |  |  |  |  |

|        |          |                                               |    |  |  |  |  |  |  |  |

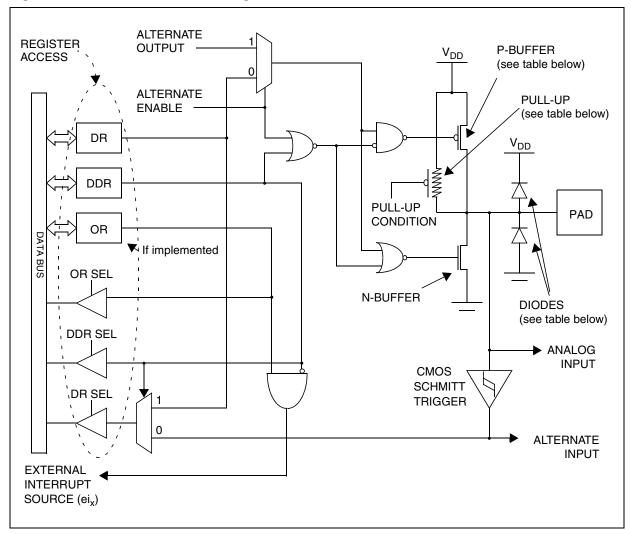

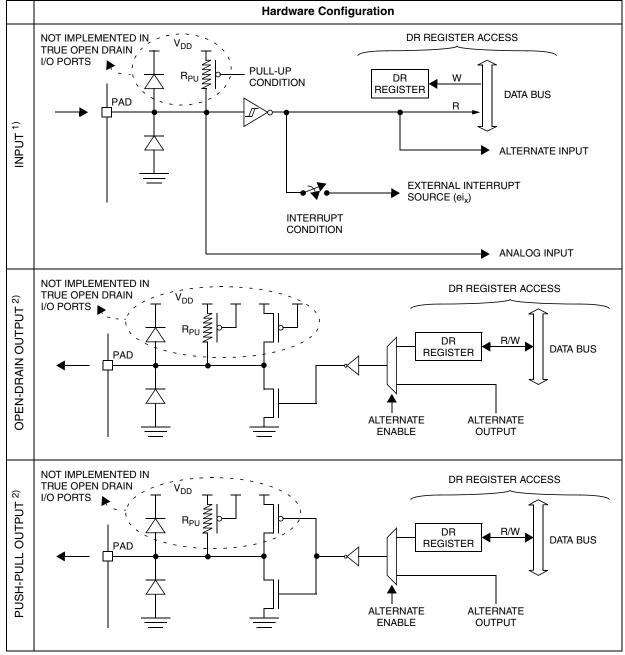

| 9.1    | INTRO    | DUCTION                                       | 46 |  |  |  |  |  |  |  |

| 9.2    | FUNC     | FIONAL DESCRIPTION                            | 46 |  |  |  |  |  |  |  |

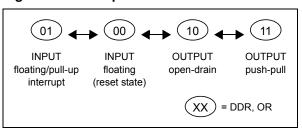

|        | 9.2.1    | Input Modes                                   | 46 |  |  |  |  |  |  |  |

|        | 9.2.2    | 2.2 Output Modes                              |    |  |  |  |  |  |  |  |

|        | 9.2.3    | ,                                             |    |  |  |  |  |  |  |  |

| 9.3    | I/O PO   | RT IMPLEMENTATION                             | 49 |  |  |  |  |  |  |  |

| 9.4    | LOW P    | OWER MODES                                    | 49 |  |  |  |  |  |  |  |

| 9.5    | INTER    | RUPTS                                         | 49 |  |  |  |  |  |  |  |

|        | 9.5.1    | I/O Port Implementation                       | 50 |  |  |  |  |  |  |  |

| 10 ON- | CHIP P   | ERIPHERALS                                    |    |  |  |  |  |  |  |  |

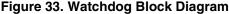

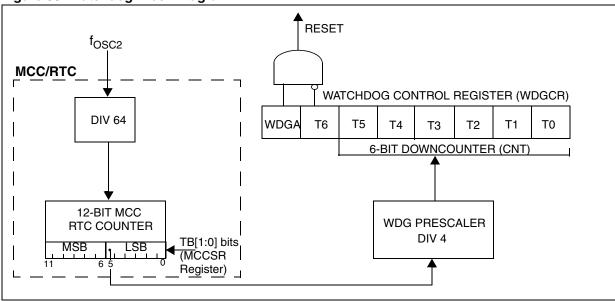

| 10.1   | 1 WATC   | HDOG TIMER (WDG)                              | 52 |  |  |  |  |  |  |  |

|        | 10.1.1   | Introduction                                  | 52 |  |  |  |  |  |  |  |

|        |          | Main Features                                 |    |  |  |  |  |  |  |  |

|        |          | Functional Description                        |    |  |  |  |  |  |  |  |

|        |          | How to Program the Watchdog Timeout           |    |  |  |  |  |  |  |  |

|        |          | Low Power Modes                               |    |  |  |  |  |  |  |  |

|        |          | Hardware Watchdog Option                      |    |  |  |  |  |  |  |  |

|        |          | Using Halt Mode with the WDG (WDGHALT option) |    |  |  |  |  |  |  |  |

|        |          | Interrupts                                    |    |  |  |  |  |  |  |  |

| 10.0   |          | Register Description                          |    |  |  |  |  |  |  |  |

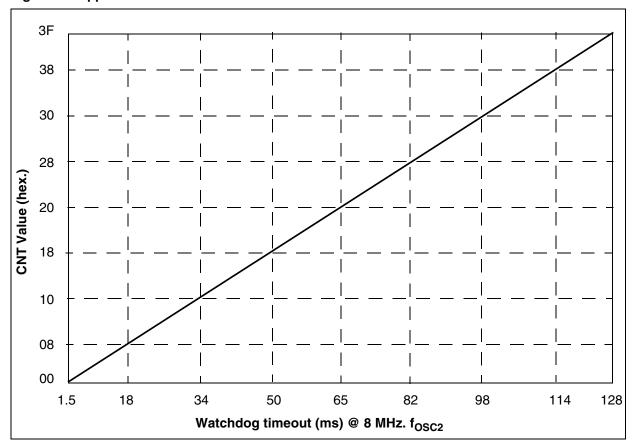

| 10.2   |          | ,                                             |    |  |  |  |  |  |  |  |

|        |          | Programmable CPU Clock Prescaler              |    |  |  |  |  |  |  |  |

|        |          | Clock-out Capability                          |    |  |  |  |  |  |  |  |

|        |          | Beeper                                        |    |  |  |  |  |  |  |  |

|        |          | Low Power Modes                               |    |  |  |  |  |  |  |  |

|        |          | Interrupts                                    |    |  |  |  |  |  |  |  |

|        |          | Register Description                          |    |  |  |  |  |  |  |  |

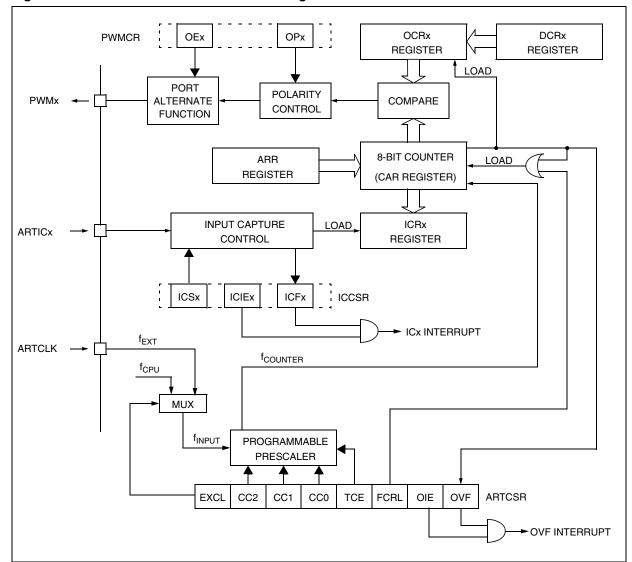

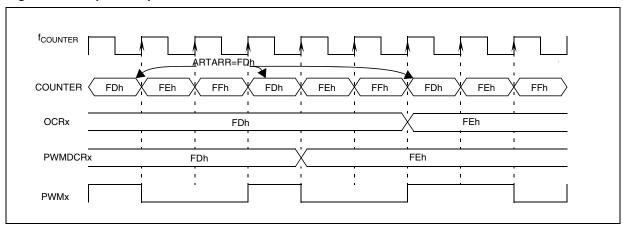

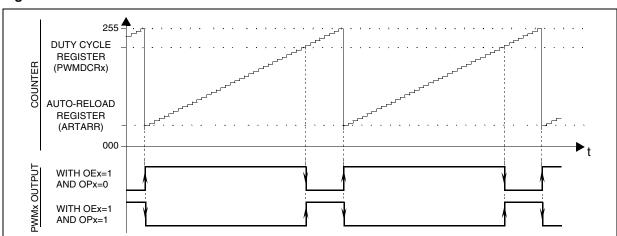

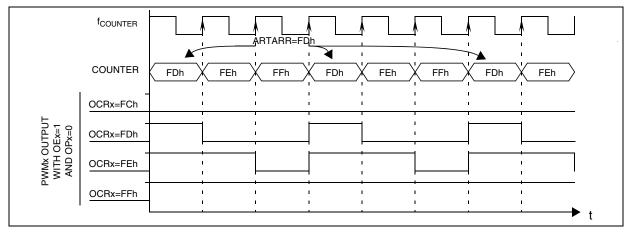

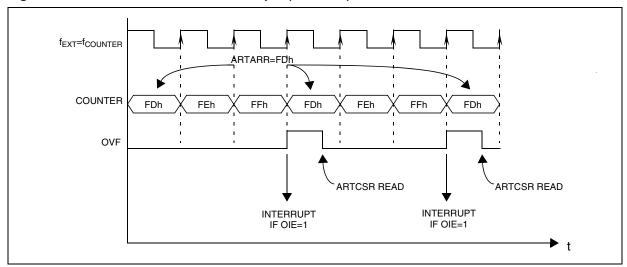

| 10.3   |          | AUTO-RELOAD TIMER (ART)                       |    |  |  |  |  |  |  |  |

|        | 10.3.1   | Introduction                                  | 60 |  |  |  |  |  |  |  |

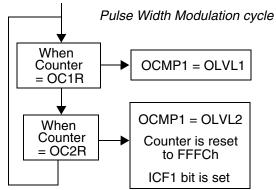

|        | 10.3.2   | Functional Description                        | 61 |  |  |  |  |  |  |  |

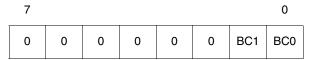

|        | 10.3.3   | Register Description                          | 65 |  |  |  |  |  |  |  |

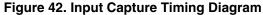

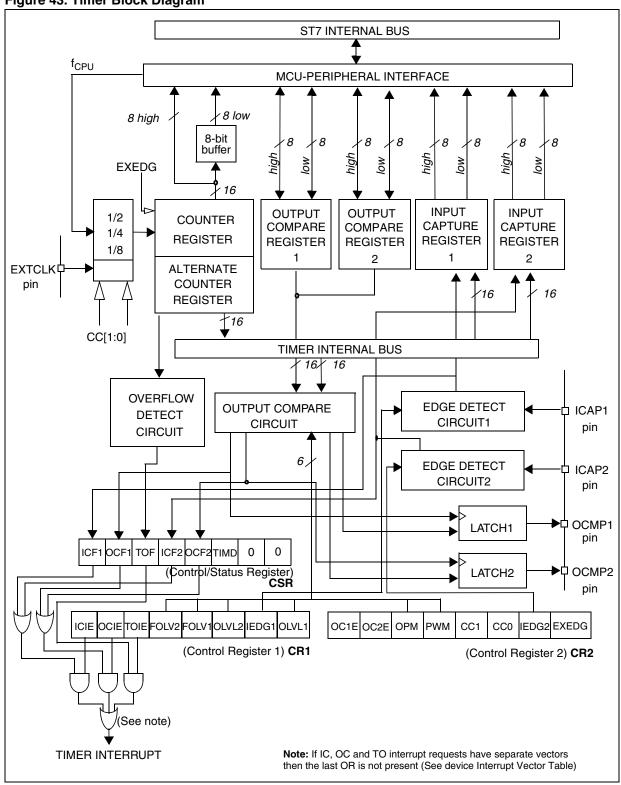

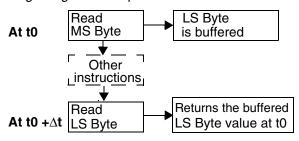

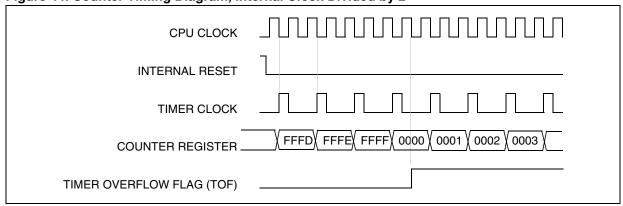

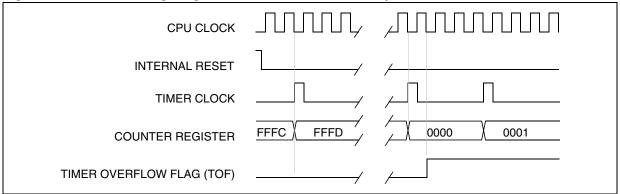

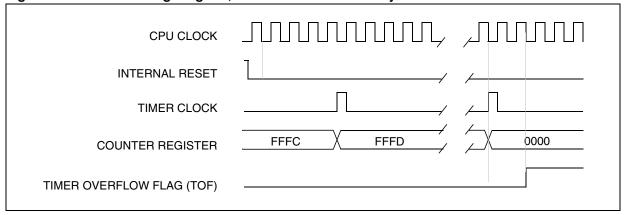

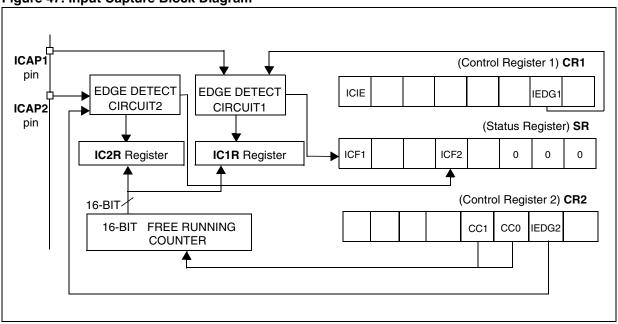

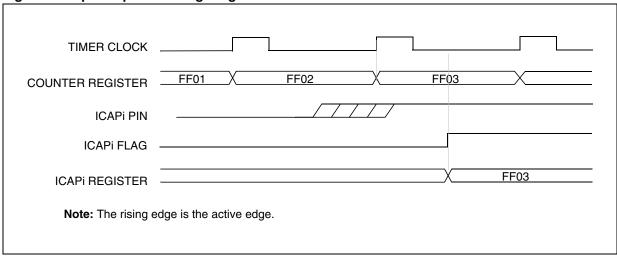

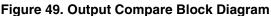

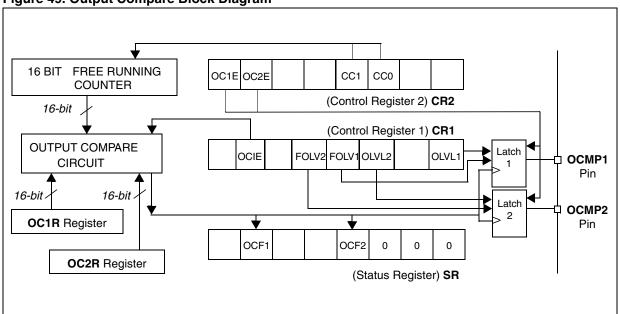

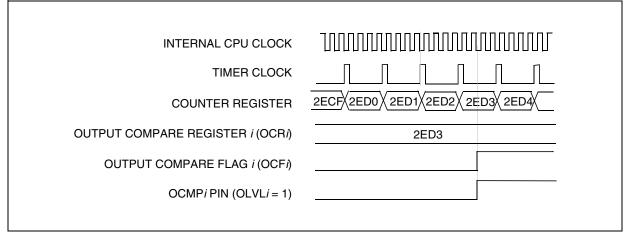

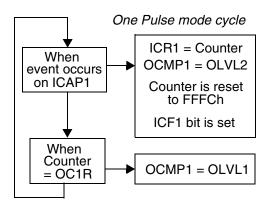

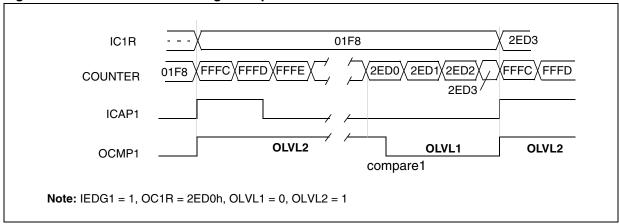

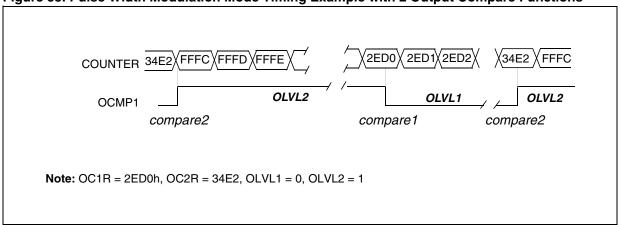

| 10.4   | 4 16-BIT | TIMER                                         | 69 |  |  |  |  |  |  |  |

|        | 10.4.1   | Introduction                                  | 69 |  |  |  |  |  |  |  |

|        |          | Main Features                                 |    |  |  |  |  |  |  |  |

|        |          | Functional Description                        |    |  |  |  |  |  |  |  |

|        |          | Low Power Modes                               |    |  |  |  |  |  |  |  |

|        |          | Interrupts                                    |    |  |  |  |  |  |  |  |

|        |          | Summary of Timer Modes                        |    |  |  |  |  |  |  |  |

| 10 5   |          | Register Description                          |    |  |  |  |  |  |  |  |

| 10.0   |          | • •                                           |    |  |  |  |  |  |  |  |

|        |          | Introduction                                  |    |  |  |  |  |  |  |  |

|        | 10.5.2   | Main Features                                 | QQ |  |  |  |  |  |  |  |

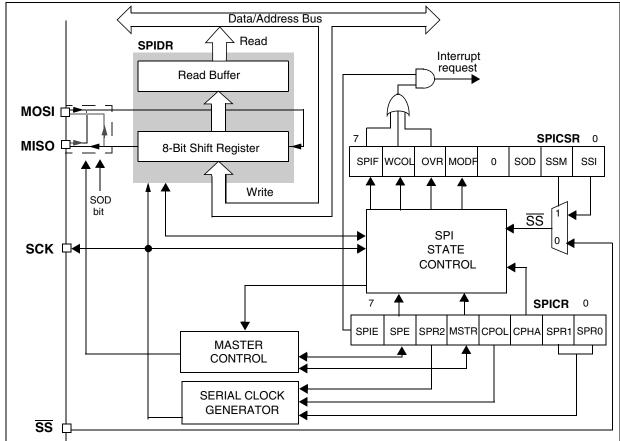

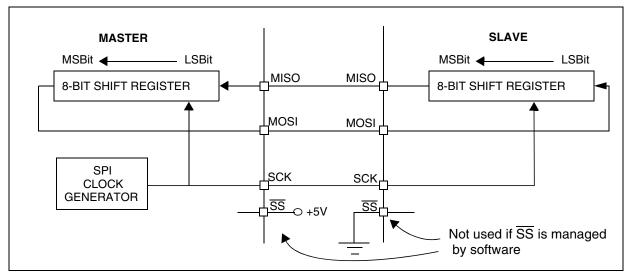

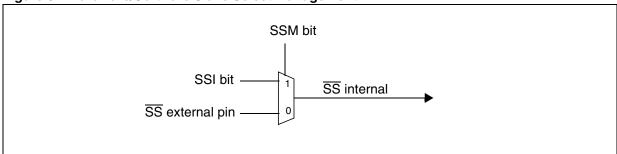

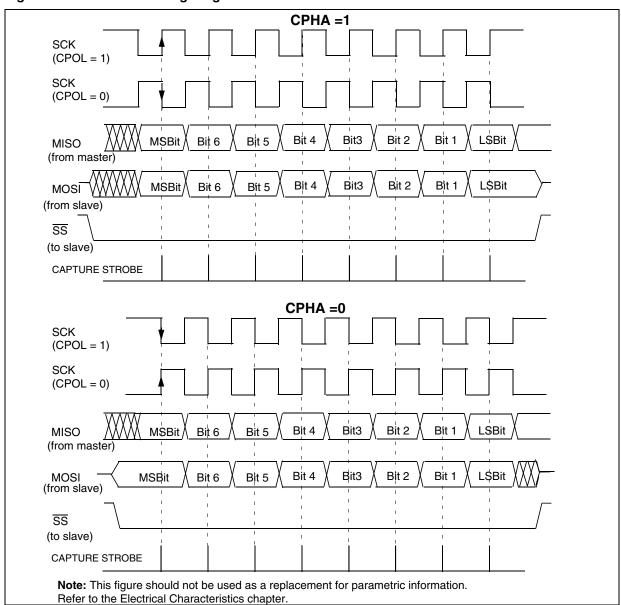

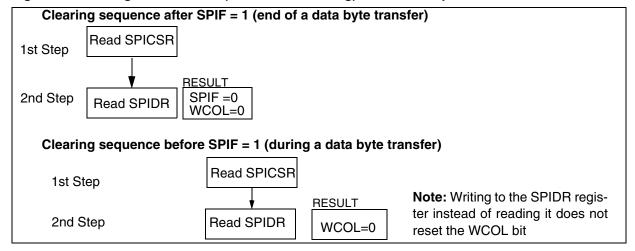

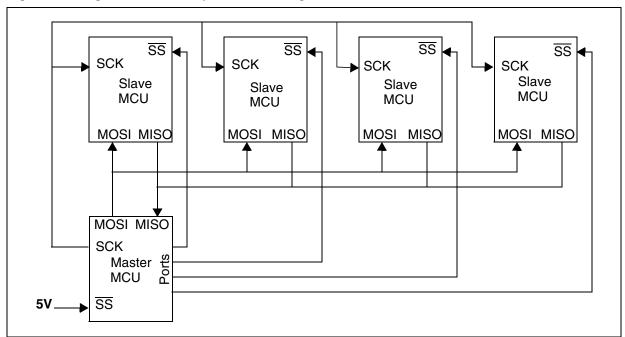

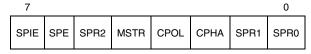

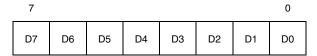

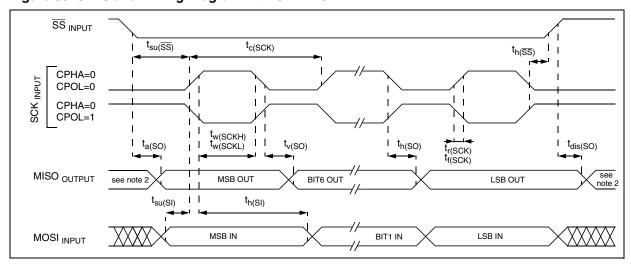

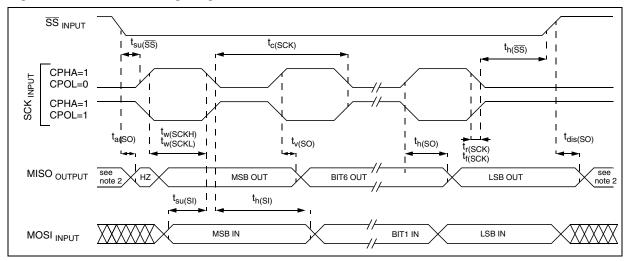

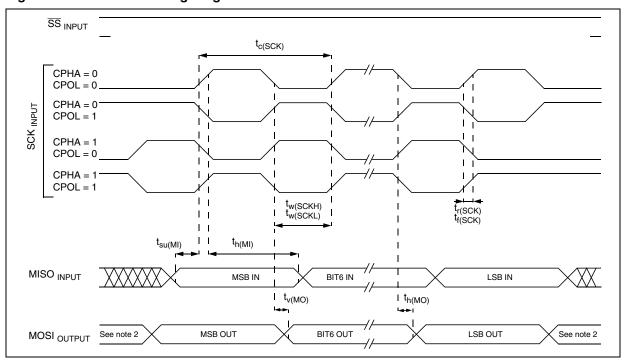

| 10.5.3        | General Description              | . 88 |

|---------------|----------------------------------|------|

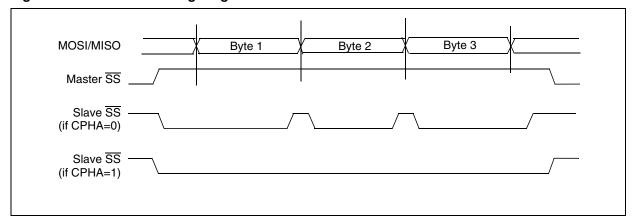

|               | Clock Phase and Clock Polarity   |      |

|               | Error Flags                      |      |

|               | Low Power Modes                  |      |

|               | nterrupts                        |      |

|               | Register Description             |      |

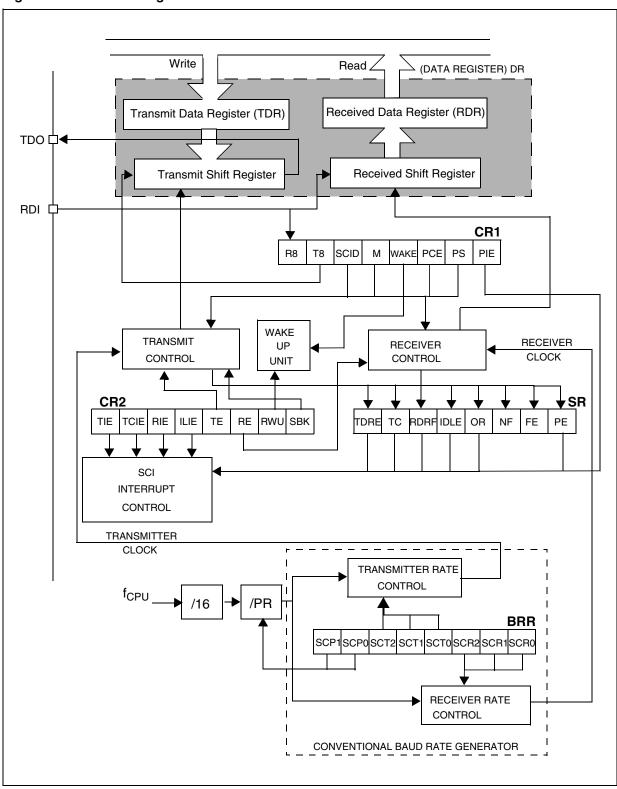

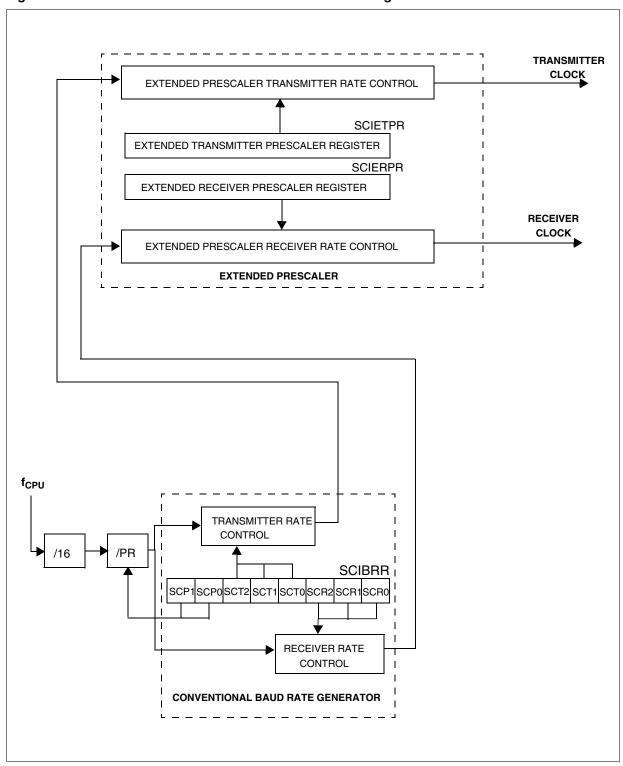

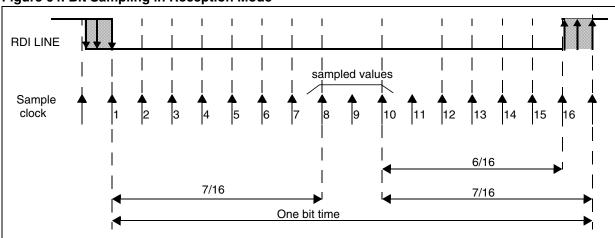

|               | COMMUNICATIONS INTERFACE (SCI)   |      |

|               |                                  |      |

|               | ntroduction                      |      |

|               |                                  |      |

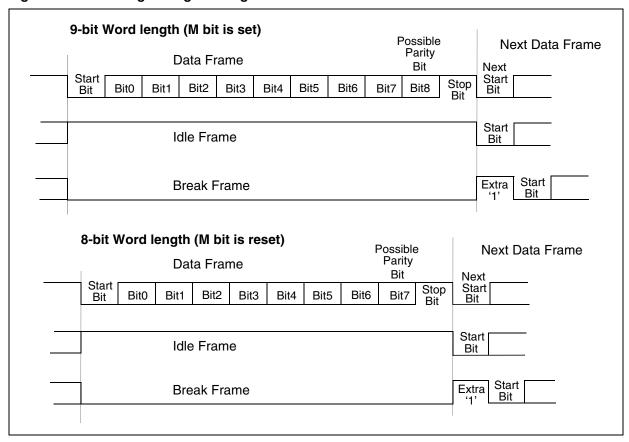

|               | General Description              |      |

|               | Functional Description           |      |

|               |                                  |      |

|               | nterrupts                        |      |

|               | Register Description             |      |

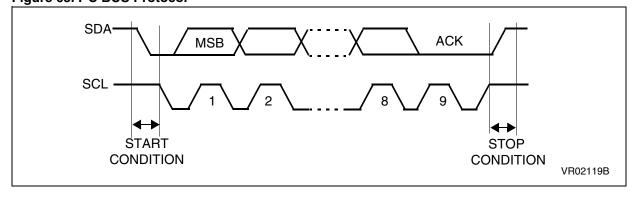

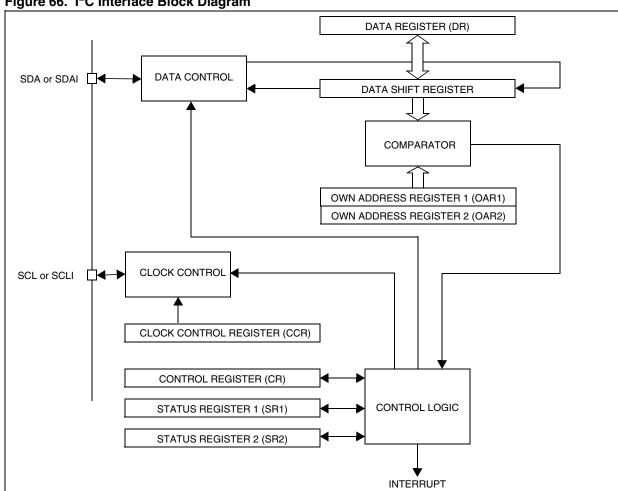

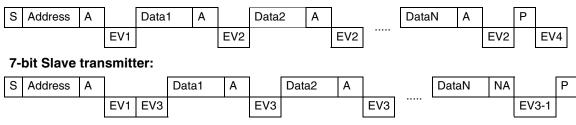

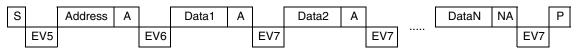

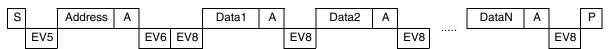

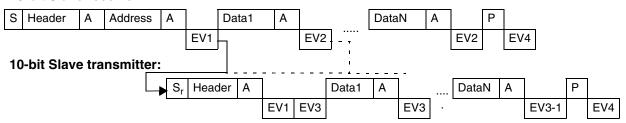

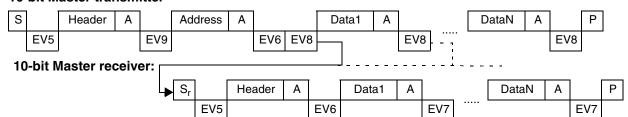

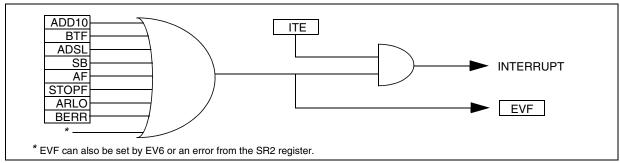

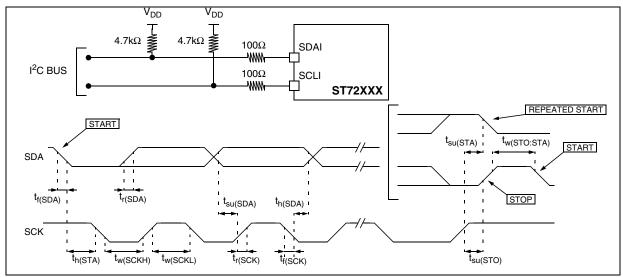

|               | INTERFACE (I2C)                  |      |

|               | ntroduction                      |      |

|               | Main Features                    |      |

|               | General Description              |      |

|               | Functional Description           |      |

|               | Low Power Modes                  |      |

|               | nterrupts                        |      |

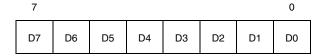

|               | Register Description             |      |

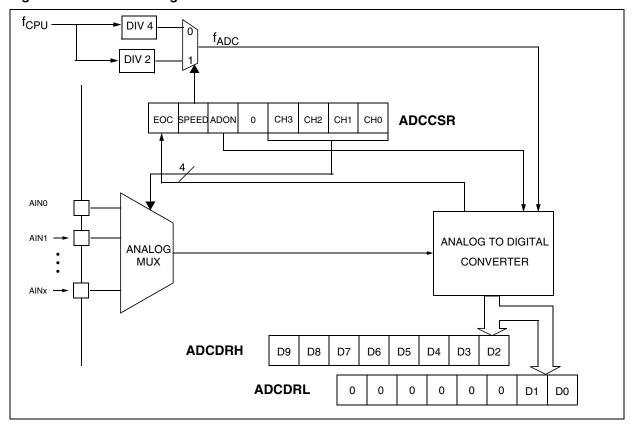

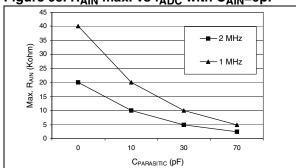

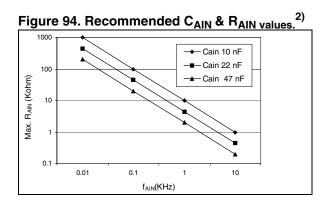

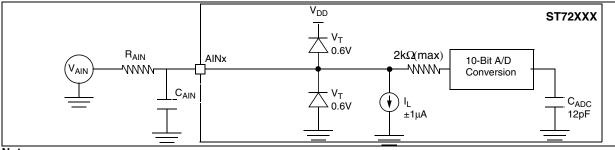

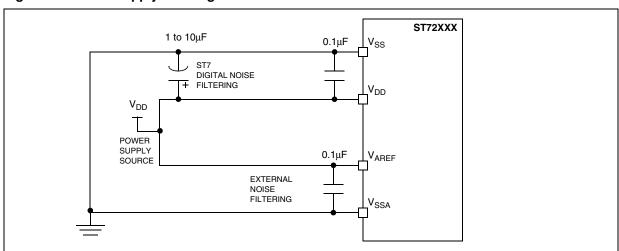

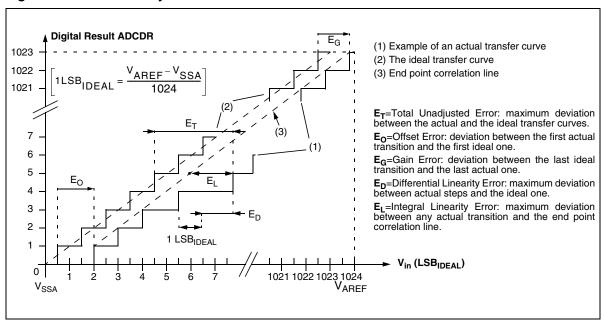

| 10.8 10-BIT A | /D CONVERTER (ADC)               | 128  |

| 10.8.1 l      | ntroduction                      | 128  |

| 10.8.2 N      | Main Features                    | 128  |

| 10.8.3 F      | Functional Description           | 129  |

| 10.8.4 L      | Low Power Modes                  | 129  |

| 10.8.5 l      | nterrupts                        | 129  |

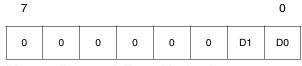

| 10.8.6 F      | Register Description             | 130  |

| 11 INSTRUCTIO | N SET                            | 132  |

| 11.1 CPU AD   | DRESSING MODES                   | 132  |

|               | nherent                          |      |

|               | mmediate                         |      |

|               | Direct                           |      |

|               | ndexed (No Offset, Short, Long)  |      |

|               | ndirect (Short, Long)            |      |

|               | ndirect Indexed (Short, Long)    |      |

|               | Relative mode (Direct, Indirect) |      |

|               | CTION GROUPS                     |      |

|               |                                  |      |

|               | _ CHARACTERISTICS                |      |

|               | ETER CONDITIONS                  |      |

|               | Minimum and Maximum values       |      |

| 12.1.2 7      | Гуріcal values                   | 138  |

|               | Гуріcal curves                   |      |

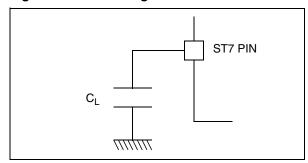

| 12.1.4 L      | Loading capacitor                | 138  |

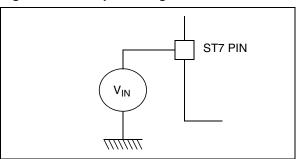

| 12.1.5 F      | Pin input voltage                | 138  |

| 12.2 ABSOLU   | ITE MAXIMUM BATINGS              | 139  |

| 12.2.1 Voltage Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 12.2.2 Current Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

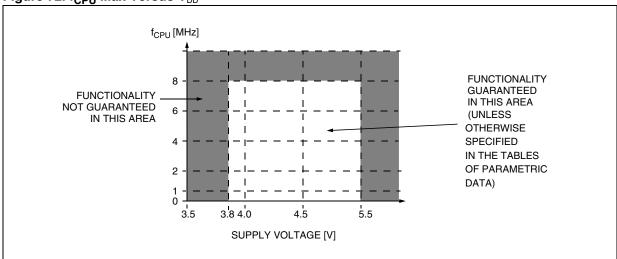

| 12.3 OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

| 12.3.1 General Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 12.3.2 Operating Conditions with Low Voltage Detector (LVD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

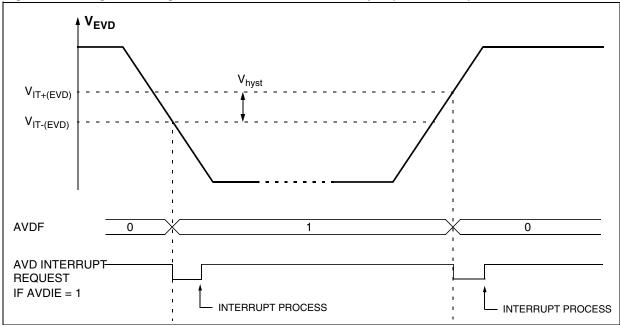

| 12.3.4 External Voltage Detector (EVD) Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

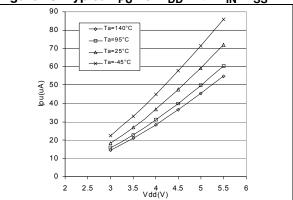

| 12.4 SUPPLY CURRENT CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 12.4.1 CURRENT CONSUMPTION  12.4.2 Supply and Clock Managers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| 12.4.3 On-Chip Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

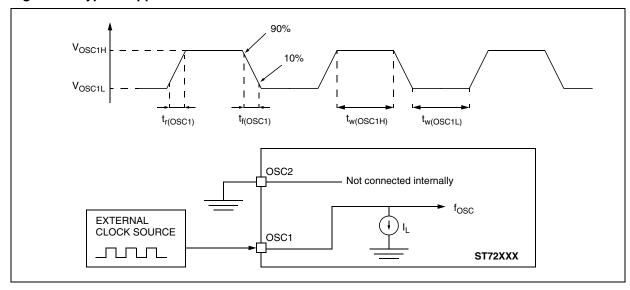

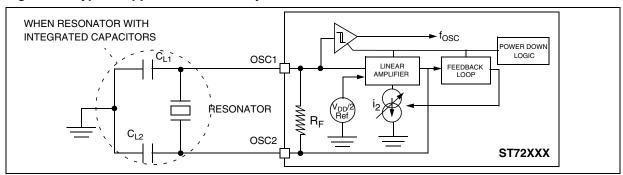

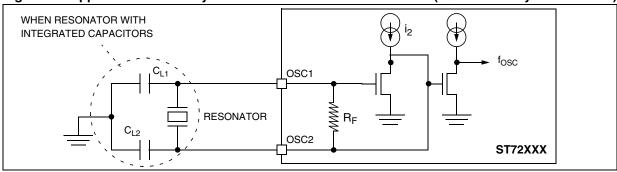

| 12.5 CLOCK AND TIMING CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 12.5.1 General Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 145           |

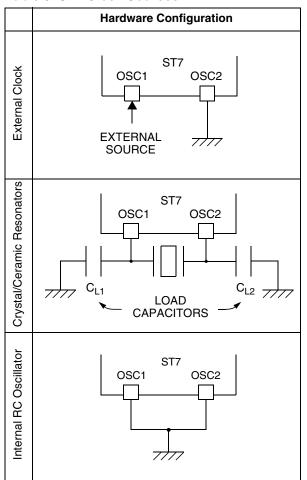

| 12.5.2 External Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 145           |

| 12.5.3 Crystal and Ceramic Resonator Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

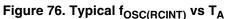

| 12.5.4 RC Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 12.6 MEMORY CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| 12.6.1 RAM and Hardware Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| 12.6.2 FLASH Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

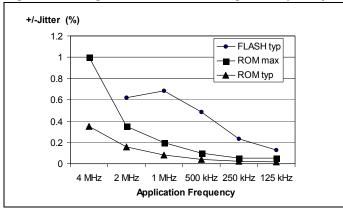

| 12.7 EMC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152           |

| 12.7.1 Functional EMS (Electro Magnetic Susceptibility)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

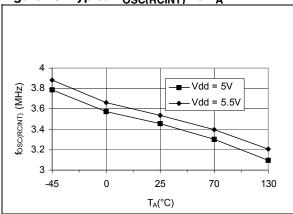

| 12.7.2 Electro Magnetic Interference (EMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

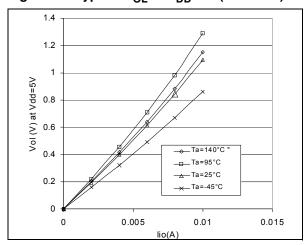

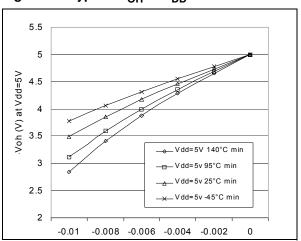

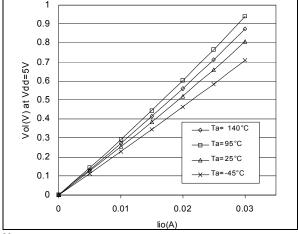

| 12.8.1 General Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

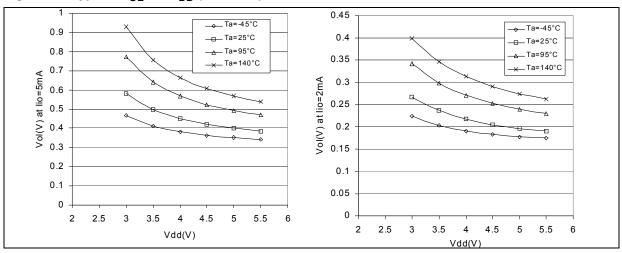

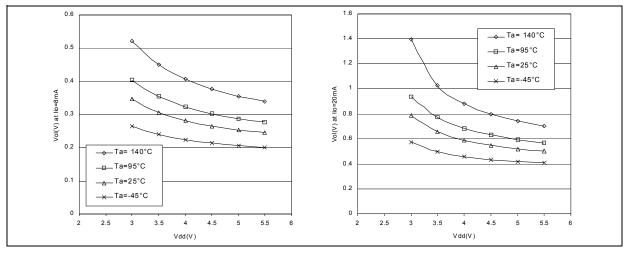

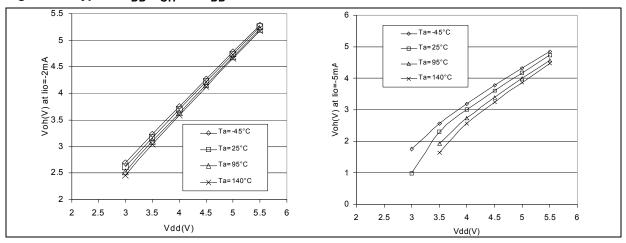

| 12.8.2 Output Driving Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| 12.9 CONTROL PIN CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| 12.9.1 Asynchronous RESET Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

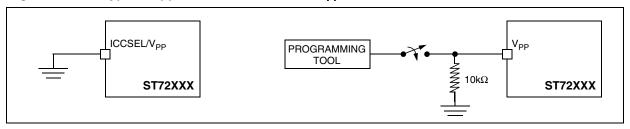

| 12.9.2 ICCSEL/VPP Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 12.10TIMER PERIPHERAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| 12.10.1 8-Bit PWM-ART Auto-Reload Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |

| 12.10.2 16-Bit Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

| 12.11.1 SPI - Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |