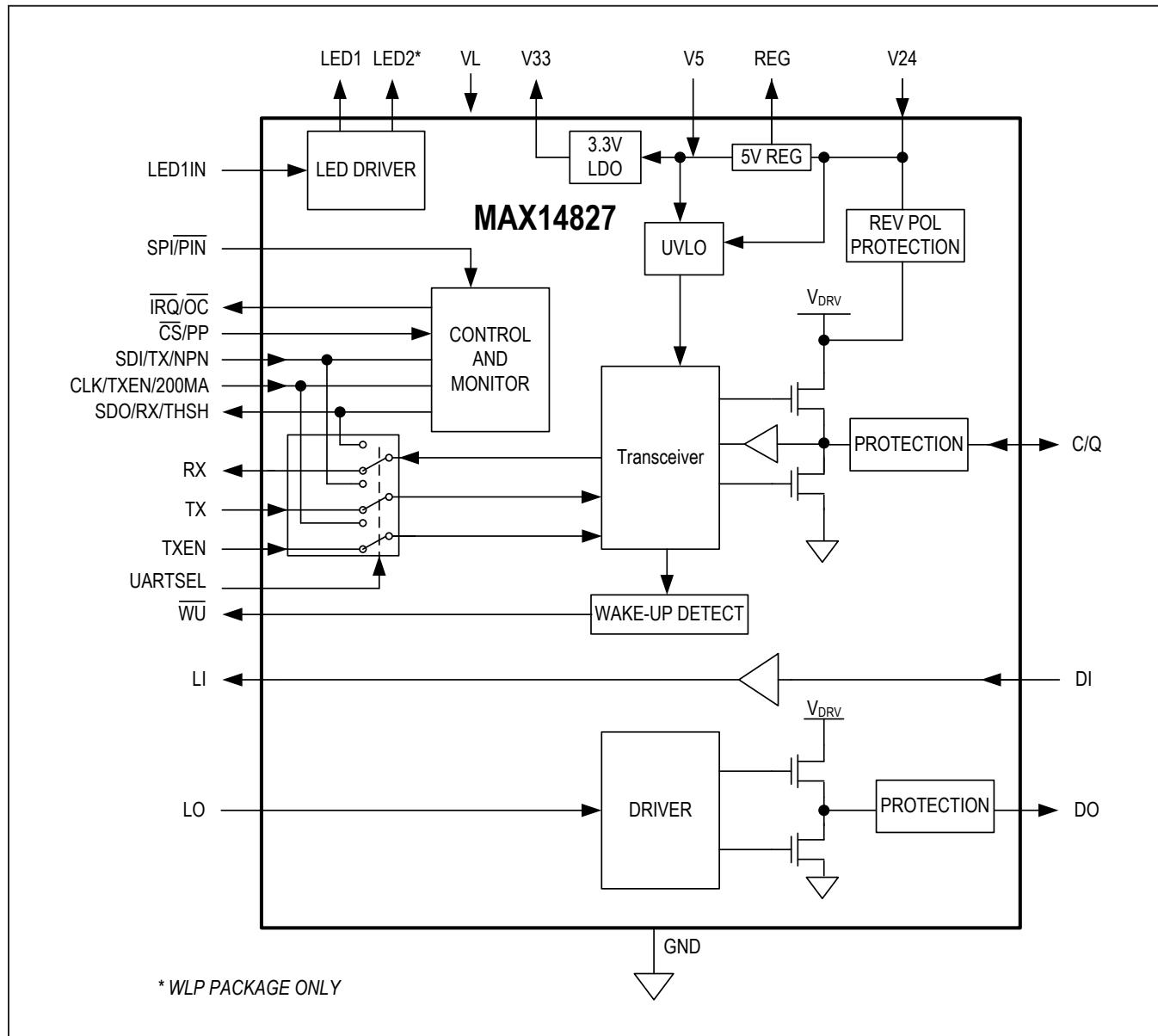

## Functional Diagram

## Absolute Maximum Ratings

(All voltages referenced to GND, unless otherwise noted.)

|             |                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------|

| V24         | -70V to +65V                                                                                          |

| REG         | -0.3V to (V <sub>5</sub> + 16V)                                                                       |

| V5, VL      | -0.3V to +6V                                                                                          |

| V33         | -0.3V to (V <sub>5</sub> + 0.3V)                                                                      |

| C/Q, DO, DI | MIN: Larger of -70V and (V <sub>24</sub> - 70V) to MAX: the lower of +70V and (V <sub>24</sub> + 70V) |

### Logic Inputs:

|                                   |                                  |

|-----------------------------------|----------------------------------|

| CS/PP, TXEN, TX, LED1IN, LI,      |                                  |

| UARTSEL, CLK/TXEN/200MA, SPI/PIN, |                                  |

| SDI/TX/NPN                        | -0.3V to (V <sub>L</sub> + 0.3V) |

### Logic Outputs:

|                            |                                  |

|----------------------------|----------------------------------|

| RX, LI, LO WU, SDO/RX/THSH | -0.3V to (V <sub>L</sub> + 0.3V) |

| IRQ/OC                     | -0.3V to +6V                     |

| LED1, LED2                 | -0.3V to (V <sub>5</sub> +0.3V)  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Package Information

| PACKAGE TYPE: 24 TQFN                 |                         |

|---------------------------------------|-------------------------|

| Package Code                          | T2444+4                 |

| Outline Number                        | <a href="#">21-0139</a> |

| Land Pattern Number                   | <a href="#">90-0022</a> |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |                         |

| Junction to Ambient ( $\theta_{JA}$ ) | 36°C/W                  |

| Junction to Case ( $\theta_{JC}$ )    | 3°C/W                   |

| PACKAGE TYPE: 25 WLP                  |                                                |

|---------------------------------------|------------------------------------------------|

| Package Code                          | W252L2+1                                       |

| Outline Number                        | <a href="#">21-0787</a>                        |

| Land Pattern Number                   | Refer to <a href="#">Application Note 1891</a> |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |                                                |

| Junction to Ambient ( $\theta_{JA}$ ) | 71°C/W                                         |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](#). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](#).

## DC Electrical Characteristics

( $V_{24} = 9\text{V to }60\text{V}$ ,  $V_5 = 4.5\text{V to }5.5\text{V}$ ,  $V_L = 2.5\text{V to }5.5\text{V}$ ,  $V_{GND} = 0\text{V}$ ; REG unconnected, all logic inputs at  $V_L$  or  $GND$ ;  $T_A = -40^\circ\text{C to }+125^\circ\text{C}$ , unless otherwise noted. Typical values are at  $V_{24} = 24\text{V}$ ,  $V_5 = 5\text{V}$ ,  $V_L = 3.3\text{V}$ , and  $T_A = +25^\circ\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL                    | CONDITIONS                                                                 | MIN                                                                                                                       | TYP  | MAX  | UNITS |

|-----------------------------------------------|---------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| V24 Supply Voltage                            | $V_{24}$                  |                                                                            | 9                                                                                                                         | 60   |      | V     |

| V24 Undervoltage-Lockout Threshold            | $V_{24\text{UVLO}}$       | $V_{24}$ rising                                                            | 6                                                                                                                         | 7.8  | 9    | V     |

|                                               |                           | $V_{24}$ falling                                                           | 6                                                                                                                         | 7.2  | 9    |       |

| V24 Undervoltage-Lockout-Threshold Hysteresis | $V_{24\text{UVLO\_HYST}}$ |                                                                            |                                                                                                                           | 570  |      | mV    |

| V24 Supply Current                            | $I_{24}$                  | V5 powered externally, REG is unconnected                                  | C/Q and DO disabled ( $CQ\_Dis = 1$ , $DO\_Dis = 1$ )                                                                     | 0.14 | 0.5  | mA    |

|                                               |                           |                                                                            | C/Q and DO in push-pull configuration, $CL[10] = 11$ , C/Q and DO high, no load on C/Q or DO                              | 1.1  | 1.75 |       |

|                                               |                           |                                                                            | C/Q and DO in push-pull configuration, $CL[10] = 11$ , C/Q and DO low, no load on C/Q or DO                               | 1.4  | 1.8  |       |

| V24 Low-Voltage Warning Threshold             | $V_{24W}$                 |                                                                            | 14.5                                                                                                                      | 16.5 | 18   | V     |

| V5 Supply Voltage                             |                           |                                                                            | 4.5                                                                                                                       | 5.5  |      | V     |

| V5 Undervoltage-Lockout Threshold             | $V_{5\text{UVLO}}$        | $V_5$ rising                                                               | 2.8                                                                                                                       | 3.5  | 4.5  | V     |

|                                               |                           | $V_5$ falling                                                              | 2.8                                                                                                                       | 3.45 | 4.5  |       |

| V5 Supply Current                             | $I_{5\text{\_IN}}$        | External 5V applied to $V_5$ , REG is unconnected, no load on LED1 or LED2 | C/Q and DO disabled ( $CQ\_Dis = 1$ , $DO\_Dis = 1$ ), $V_{33}$ disabled ( $V_{33\_Dis} = 1$ )                            | 0.64 | 0.9  | mA    |

|                                               |                           |                                                                            | C/Q and DO in push-pull configuration, $CL[10] = 11$ , C/Q and DO high, $V_{33}$ enabled, no load on C/Q, DO, or $V_{33}$ | 1.37 | 1.75 |       |

|                                               |                           |                                                                            | C/Q and DO in push-pull configuration, $CL[10] = 11$ , C/Q and DO low, $V_{33}$ enabled, no load on C/Q, DO, or $V_{33}$  | 1.41 | 1.8  |       |

## DC Electrical Characteristics (continued)

( $V_{24}$  = 9V to 60V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $V_{GND}$  = 0V; REG unconnected, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL               | CONDITIONS                                                                                                                     | MIN                   | TYP  | MAX   | UNITS    |

|--------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-------|----------|

| VL Logic-Level Supply Voltage              | $V_L$                |                                                                                                                                | 2.5                   |      | 5.5   | V        |

| VL Undervoltage Threshold                  | $V_{LUVLO}$          |                                                                                                                                | 0.9                   | 1.7  | 2.4   | V        |

| VL Logic-Level Supply Current              | $I_L$                | All logic inputs at $V_L$ or GND, all logic outputs unconnected                                                                |                       | 0.25 | 3     | $\mu$ A  |

| <b>5V LINEAR REGULATOR/CONTROLLER (V5)</b> |                      |                                                                                                                                |                       |      |       |          |

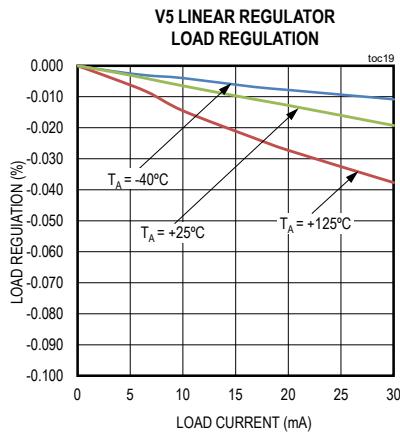

| V5 Output Voltage                          | $V_5$                | REG = V5, no load on V5, 9V $\leq$ $V_{24}$ $\leq$ 60V                                                                         | 4.75                  | 5.00 | 5.25  | V        |

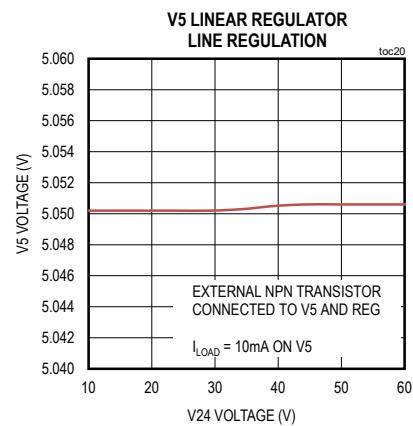

| Load Regulation                            | $\Delta V_5_{\_LDR}$ | REG = V5, 0mA $<$ $I_{LOAD}$ $<$ 30mA, $V_{24}$ = 24V                                                                          |                       | 0.02 | 0.2   | %        |

| Line Regulation                            | $\Delta V_5_{\_LNR}$ | REG = V5, $I_{LOAD}$ = 1mA, $V_{24}$ from 9V to 60V                                                                            | 0.01                  | 4    |       | mV/V     |

| REG Output Current                         | $I_{REG}$            | Internal regulator or external NPN                                                                                             |                       |      | 30    | mA       |

| $V_{24}$ REG Dropout Voltage               | $\Delta V_{REG}$     | $V_{24}$ = 9V, $V_5$ = 4.5V, $I_{REG}$ = 5mA                                                                                   |                       | 2.35 |       | V        |

| REG Open Voltage                           | $V_{REG\_OPN}$       | $V_{24}$ = 60V, $V_5$ = 4.5V, no load on REG                                                                                   | 10                    | 13   | 16    | V        |

| V5 Capacitance                             | $CV_5$               | Allowed capacitance on V5, REG connected to V5 (Note 2)                                                                        | 0.8                   | 1    | 2     | $\mu$ F  |

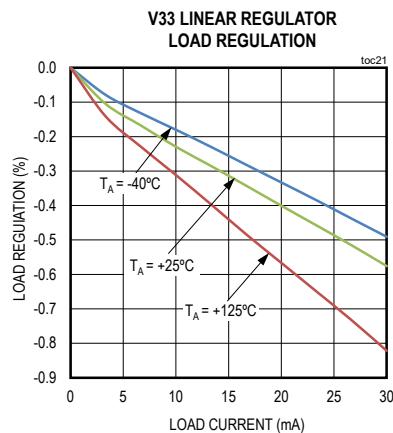

| <b>3.3V LINEAR REGULATOR (V33)</b>         |                      |                                                                                                                                |                       |      |       |          |

| V33 Output Voltage                         | $V_{33}$             | No load on V33                                                                                                                 | 3.1                   | 3.3  | 3.5   | V        |

| V33 Load Regulation                        | $V_{33\_LDR}$        | 0mA $<$ $I_{LOAD}$ $<$ 30mA                                                                                                    | 0                     | 0.4  | 0.8   | %        |

| V33 Capacitance                            | $CV_{33}$            | Allowed capacitance on V33, V33 enabled (Note 3)                                                                               | 0.8                   | 1    |       | $\mu$ F  |

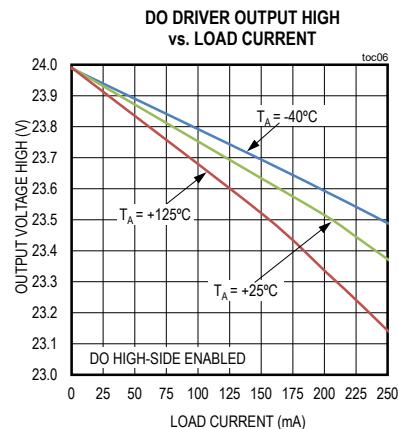

| <b>C/Q, DO DRIVER</b>                      |                      |                                                                                                                                |                       |      |       |          |

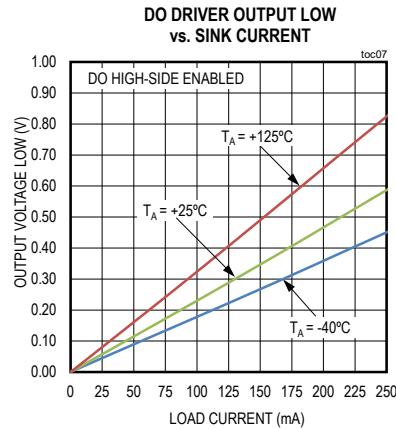

| Driver On-Resistance                       | $R_{OH}$             | High-side enabled, $V_{24}$ = 24V, CL[10] = 11, $I_{LOAD}$ = -200mA                                                            |                       | 2.65 | 4.6   | $\Omega$ |

|                                            | $R_{OL}$             | Low-side enabled, $V_{24}$ = 24V, CL[10] = 11, $I_{LOAD}$ = +200mA                                                             |                       | 2.3  | 4.45  |          |

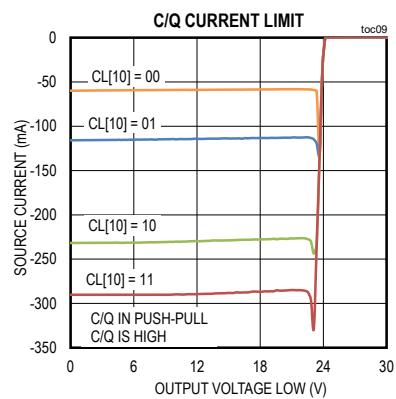

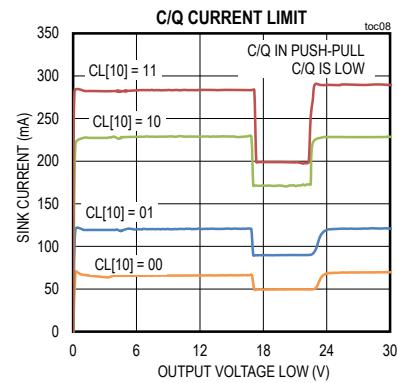

| Driver Current Limit                       | $I_{CL}$             | SPI/PIN = high, $V_{DRIVER}$ = ( $V_{24}$ - 3V) or 3V, CL_Dis = 0                                                              | CL[10] = 00           | 50   | 65    | 80       |

|                                            |                      |                                                                                                                                | CL[10] = 01           | 100  | 120   | 150      |

|                                            |                      |                                                                                                                                | CL[10] = 10           | 200  | 230   | 275      |

|                                            |                      |                                                                                                                                | CL[10] = 11           | 250  | 290   | 350      |

|                                            |                      | SPI/PIN = low, $V_{DRIVER}$ = ( $V_{24}$ - 3V) or 3V                                                                           | CLK/TXEN/200MA = low  | 100  | 120   | 150      |

|                                            |                      |                                                                                                                                | CLK/TXEN/200MA = high | 200  | 230   | 275      |

| Driver Peak Current                        | $I_{CL\_PEAK}$       | DC current                                                                                                                     |                       |      | 490   | mA       |

| C/Q Leakage Current                        | $I_{LEAK\_CQ}$       | C/Q driver is disabled (C/Q_Dis = 1), RX disabled (Rx_Dis = 1), $V_{24}$ = 24V, ( $V_{24}$ - 65V) $\leq$ $V_{C/Q}$ $\leq$ +60V | -70                   |      | +10   | $\mu$ A  |

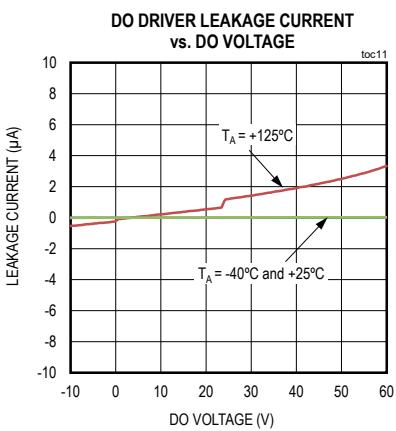

| DO Leakage Current                         | $I_{LEAK\_DO}$       | DO driver is disabled (DO_Dis = 1), $V_{24}$ = 24V, ( $V_{24}$ - 65V) $\leq$ $V_{DO}$ $\leq$ +60V                              | -10                   |      | +10   | $\mu$ A  |

| C/Q Output Reverse Current                 | $I_{REV\_CQ}$        | C/Q driver enabled and in push-pull configuration, $V_{24}$ = 30V, $V_{C/Q}$ = ( $V_{24}$ + 5V) or ( $V_{GND}$ - 5V)           | -60                   |      | +1000 | $\mu$ A  |

## DC Electrical Characteristics (continued)

( $V_{24}$  = 9V to 60V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $V_{GND}$  = 0V; REG unconnected, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                    | SYMBOL         | CONDITIONS                                                                                                         |                                                                                | MIN           | TYP  | MAX   | UNITS         |

|------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|------|-------|---------------|

| DO Output Reverse Current    | $I_{REV\_DO}$  | DO driver enabled and in push-pull configuration, $V_{24}$ = 30V, $V_{DO}$ = ( $V_{24}$ + 5V) or ( $V_{GND}$ - 5V) |                                                                                | -60           |      | +1000 | $\mu A$       |

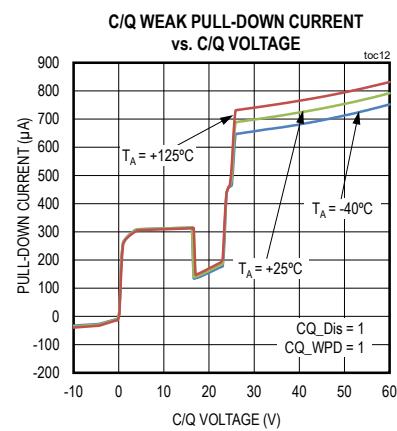

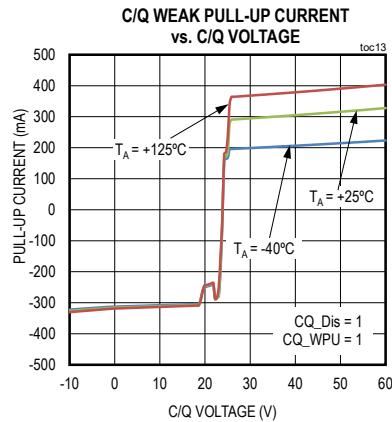

| Weak Pulldown Current        | $I_{PD}$       | SPI/PIN = high, driver disabled ( $CQ\_Dis$ = 1, $DO\_Dis$ = 1)                                                    | $V_{DRIVER}$ = 5V, $CQ\_WPD$ = 1, $DO\_WPD$ = 1, $CQ\_WPU$ = 0, $DO\_WPU$ = 0  | 200           | 300  | 400   | $\mu A$       |

|                              |                |                                                                                                                    | $V_{DRIVER}$ = 24V, $CQ\_WPD$ = 1, $DO\_WPD$ = 1, $CQ\_WPU$ = 0, $DO\_WPU$ = 0 | 200           | 470  | 1000  |               |

| Weak Pullup Current          | $I_{PU}$       | SPI/PIN = high, driver disabled ( $CQ\_Dis$ = 1, $DO\_Dis$ = 1), $V_{DRIVER}$ = $V_{24}$ - 5V                      | $CQ\_WPU$ = 1, $DO\_WPU$ = 1, $CQ\_WPD$ = 0, $DO\_WPD$ = 0,                    | -400          | -300 | -200  | $\mu A$       |

| <b>C/Q, DI RECEIVER</b>      |                |                                                                                                                    |                                                                                |               |      |       |               |

| Input Voltage Range          | $V_{IN}$       | For valid RX/LI logic                                                                                              |                                                                                | $V_{24}$ - 65 | +65  |       | V             |

| C/Q, DI Input Threshold High | $V_{TH}$       | C/Q driver disabled                                                                                                | $V_{24}$ > 18V                                                                 | 11            | 11.8 | 12.5  | V             |

|                              |                |                                                                                                                    | $V_{24}$ < 18V                                                                 | 59            | 65.5 | 72    | % of $V_{24}$ |

| C/Q, DI Input Threshold Low  | $V_{TL}$       | C/Q driver disabled                                                                                                | $V_{24}$ > 18V                                                                 | 9             | 9.8  | 10.5  | V             |

|                              |                |                                                                                                                    | $V_{24}$ < 18V                                                                 | 45            | 54.5 | 63    | % of $V_{24}$ |

| C/Q, DI Input Hysteresis     | $V_{HYS\_CQ}$  | C/Q driver disabled                                                                                                | $V_{24}$ > 18V                                                                 |               | 2    |       | V             |

|                              |                |                                                                                                                    | $V_{24}$ < 18V                                                                 |               | 11   |       | % of $V_{24}$ |

| C/Q Input Capacitance        | $C_{IN\_CQ}$   | Driver disabled, weak pull-up and pull-down disabled, $f$ = 100kHz                                                 |                                                                                |               | 50   |       | pF            |

| DI Input Capacitance         | $C_{IN\_DI}$   | $f$ = 100kHz                                                                                                       |                                                                                |               | 10   |       | pF            |

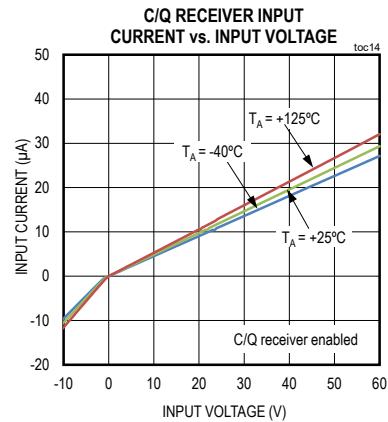

| C/Q Input Current            | $I_{IN\_CQ}$   | C/Q driver disabled ( $CQ\_Dis$ = 1), C/Q receiver enabled, $V_{24}$ = 24V                                         | $-5V \leq V_{C/Q} \leq (V_{24} + 5V)$                                          | -10           |      | +30   | $\mu A$       |

|                              |                |                                                                                                                    | $(V_{24} - 65V) \leq V_{C/Q} \leq +60V$                                        | -70           |      | +70   |               |

| DI Leakage Current           | $I_{LEAK\_DI}$ | DI receiver disabled ( $DI\_Dis$ = 1), $V_{24}$ = 24V, $(V_{24} - 65V) \leq V_{DI} \leq +60V$                      |                                                                                | -40           |      | +150  | $\mu A$       |

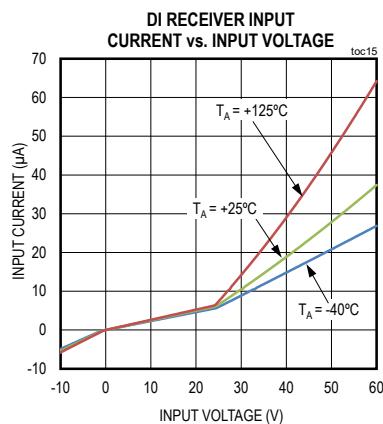

| DI Input Current             | $I_{IN\_DI}$   | DI receiver enabled, $V_{24}$ = 24V                                                                                | $-5V \leq V_{DI} \leq (V_{24} + 5V)$                                           | -10           |      | +35   | $\mu A$       |

|                              |                |                                                                                                                    | $(V_{24} - 65V) \leq V_{DI} \leq +60V$                                         | -40           |      | +200  |               |

## DC Electrical Characteristics (continued)

( $V_{24} = 9V$  to  $60V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_L = 2.5V$  to  $5.5V$ ,  $V_{GND} = 0V$ ; REG unconnected, all logic inputs at  $V_L$  or  $GND$ ;  $T_A = -40^\circ C$  to  $+125^\circ C$ , unless otherwise noted. Typical values are at  $V_{24} = 24V$ ,  $V_5 = 5V$ ,  $V_L = 3.3V$ , and  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                                                                                                                                                                            | SYMBOL            | CONDITIONS                                                                                     | MIN | TYP              | MAX              | UNITS      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------|-----|------------------|------------------|------------|

| <b>LOGIC INPUTS (<math>\overline{CS}/PP</math>, <math>TXEN</math>, <math>TX</math>, <math>LO</math>, <math>LED1IN</math>, <math>CLK/TXEN/200mA</math>, <math>SPI/\overline{PIN}</math>, <math>SDI/TX/NPN</math>)</b> |                   |                                                                                                |     |                  |                  |            |

| Logic Input Voltage Low                                                                                                                                                                                              | $V_{IL}$          |                                                                                                |     |                  | $0.2 \times V_L$ | V          |

| Logic Input Voltage High                                                                                                                                                                                             | $V_{IH}$          |                                                                                                |     | $0.8 \times V_L$ |                  | V          |

| Logic Input Leakage Current                                                                                                                                                                                          | $I_{LEAK}$        | Logic input = $GND$ or $VL$                                                                    | -1  |                  | +1               | $\mu A$    |

| <b>LOGIC OUTPUTS (RX, LI, WU, IRQ/OC, SDO/RX/THSH)</b>                                                                                                                                                               |                   |                                                                                                |     |                  |                  |            |

| Logic Output Voltage Low                                                                                                                                                                                             | $V_{OL}$          | $I_{OUT} = -5mA$                                                                               |     |                  | 0.4              | V          |

| Logic Output Voltage High                                                                                                                                                                                            | $V_{OH}$          | $I_{OUT} = 5mA$                                                                                |     | $V_5 - 0.4$      |                  | V          |

| IRQ/OC Open-Drain Leakage Current                                                                                                                                                                                    | $I_{LK\_OD}$      | $\overline{IRQ}/\overline{OC}$ high impedance,<br>$\overline{IRQ}/\overline{OC} = GND$ or $VL$ | -1  |                  | +1               | $\mu A$    |

| SDO Leakage Current                                                                                                                                                                                                  | $I_{LK\_SDO}$     | $SPI/\overline{PIN} = high$ , $\overline{CS}/PP = high$ , $SDO/RX/THSH = GND$ or $VL$          | -1  |                  | +1               | $\mu A$    |

| RX, LI Leakage Current                                                                                                                                                                                               | $I_{LK\_RXLI}$    | $SPI/\overline{PIN} = high$ , $DI\_Dis = 1$ ,<br>$RX\_Dis = 1$ , $RX/LI = GND$ or $VL$         | -1  |                  | +1               | $\mu A$    |

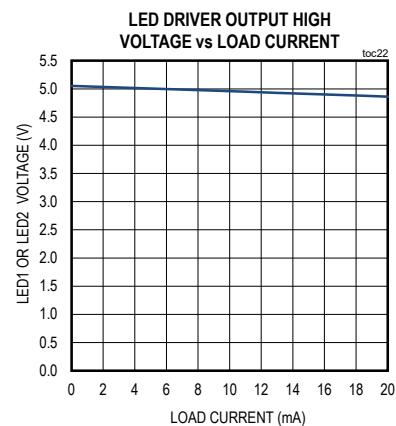

| <b>LED DRIVERS (LED1, LED2)</b>                                                                                                                                                                                      |                   |                                                                                                |     |                  |                  |            |

| LED Output Voltage Low                                                                                                                                                                                               | $V_{LEDOL}$       | $I_{OUT} = -5mA$                                                                               |     |                  | 0.4              | V          |

| LED Output Voltage High                                                                                                                                                                                              | $V_{LEDOH}$       | $I_{OUT} = 10mA$                                                                               |     | $V_5 - 0.4$      |                  | V          |

| <b>THERMAL MANAGEMENT</b>                                                                                                                                                                                            |                   |                                                                                                |     |                  |                  |            |

| Thermal Warning Threshold                                                                                                                                                                                            | $T_{WRN}$         | Die junction temperature rising,<br>$TempW$ and $TempWInt$ bits are set                        |     | $+140$           |                  | $^\circ C$ |

| Thermal Warning Threshold Hysteresis                                                                                                                                                                                 | $T_{WRN\_HYS}$    | Die junction temperature falling,<br>$TempW$ bit cleared                                       |     | 15               |                  | $^\circ C$ |

| Per-Driver Thermal Shutdown Temperature                                                                                                                                                                              | $T_{SHUT\_D}$     | Driver temperature rising, temperature at<br>which the driver is turned off                    |     | $+160$           |                  | $^\circ C$ |

| Per-Driver Thermal Shutdown Temperature Hysteresis                                                                                                                                                                   | $T_{SHUT\_DHYS}$  | Driver temperature falling                                                                     |     | 15               |                  | $^\circ C$ |

| IC Thermal Shutdown                                                                                                                                                                                                  | $T_{SHUT\_IC}$    | Die temperature rising, $ThShut$ and<br>$ThShutInt$ bits are set                               |     | $+170$           |                  | $^\circ C$ |

| IC Thermal-Shutdown Hysteresis                                                                                                                                                                                       | $T_{SHUT\_ICHYS}$ | Die temperature falling, $ThShut$ bit is<br>cleared                                            |     | 15               |                  | $^\circ C$ |

## AC Electrical Characteristics

( $V_{24}$  = 18V to 30V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V,  $V_{GND}$  = 0V; REG unconnected, all logic inputs at  $V_L$  or GND;  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                  | SYMBOL         | CONDITIONS                                                    | MIN            | TYP   | MAX  | UNITS |

|--------------------------------------------|----------------|---------------------------------------------------------------|----------------|-------|------|-------|

| <b>C/Q, DO DRIVER</b>                      |                |                                                               |                |       |      |       |

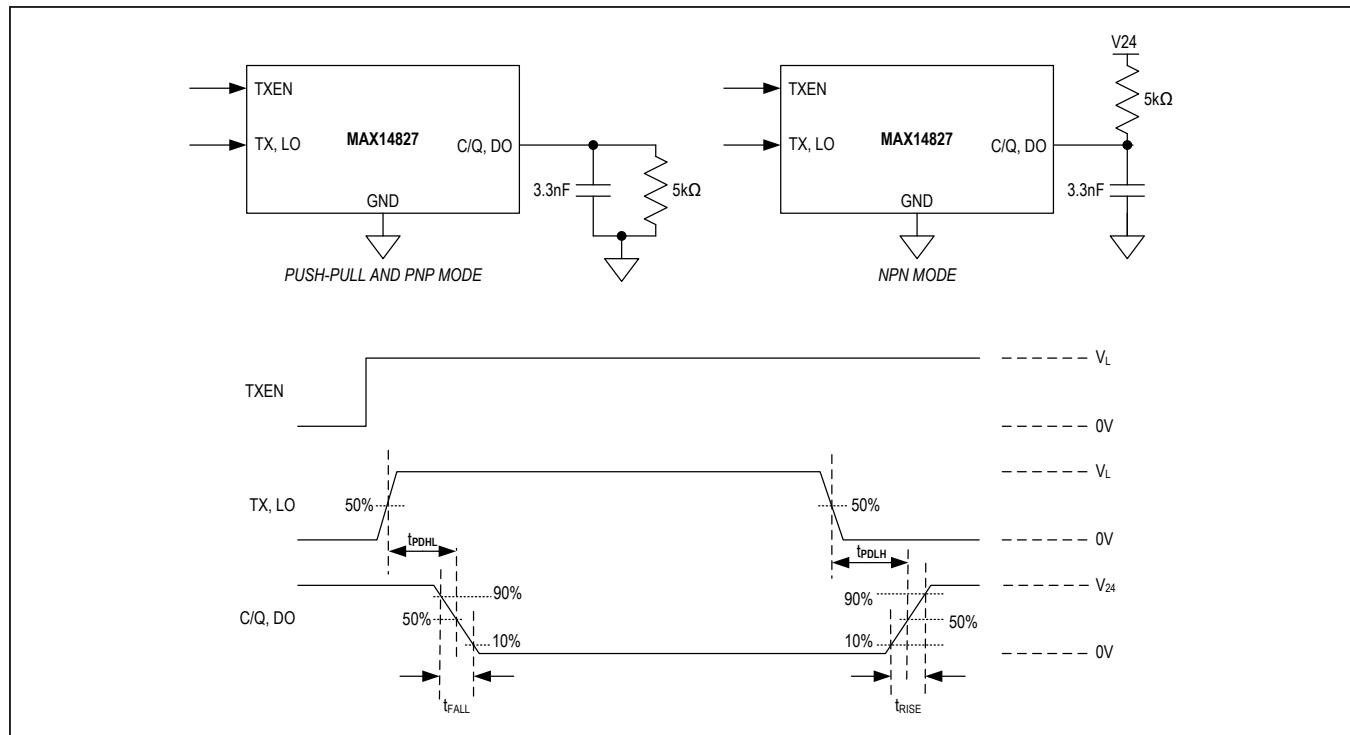

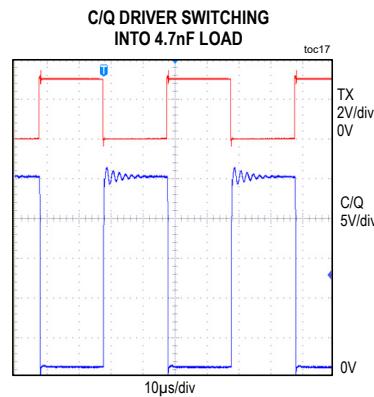

| Driver Low-to-High Propagation Delay       | $t_{PDH\_PP}$  | Push-pull and PNP configuration, Figure1                      | 0.16           | 0.4   | 0.4  | μs    |

| Driver High-to-Low Propagation Delay       | $t_{PDHL\_PP}$ | Push-pull and NPN configuration, Figure1                      | 0.28           | 0.4   | 0.4  | μs    |

| Driver Skew                                | $t_{SKew}$     | Push-pull configuration, Figure 1<br>  $t_{PDH}$ - $t_{PDHL}$ | -0.3           | +0.3  | +0.3 | μs    |

| Driver Rise Time                           | $t_{RISE}$     | Push-pull and PNP configuration, Figure 1                     | 0.12           | 0.4   | 0.4  | μs    |

| Driver Fall Time                           | $t_{FALL}$     | Push-pull and NPN configuration, Figure 1                     | 0.12           | 0.4   | 0.4  | μs    |

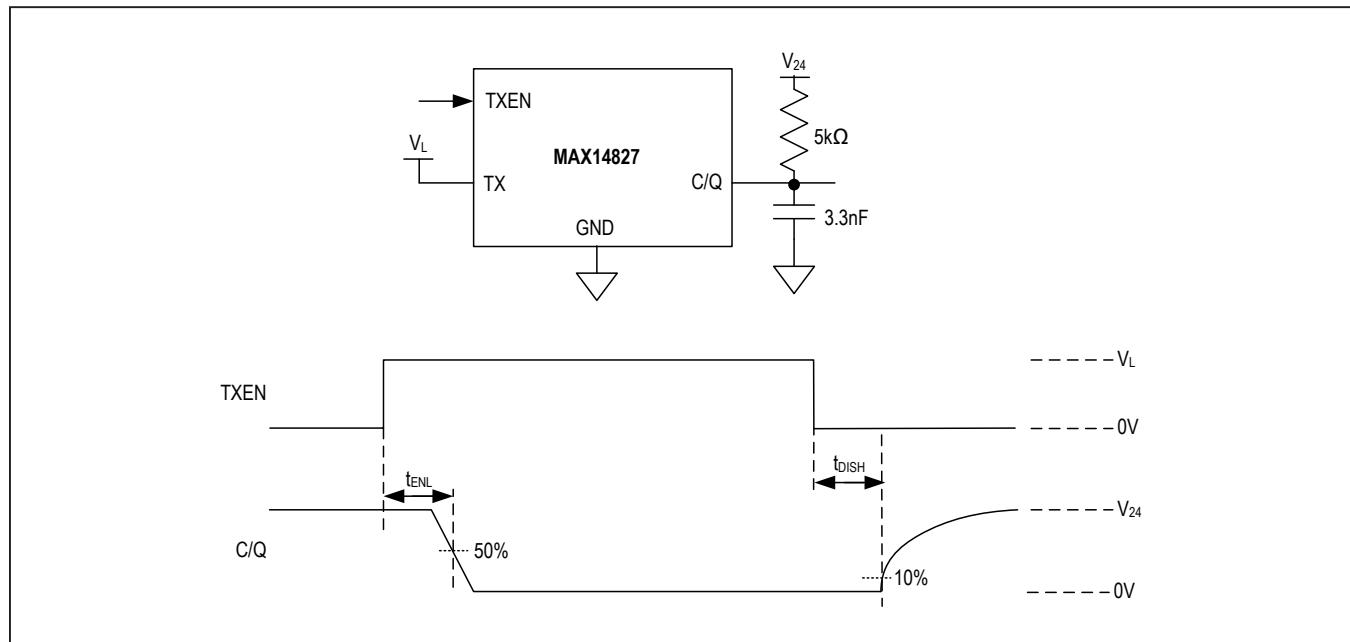

| Driver Enable Time High                    | $t_{ENH}$      | Push-pull and PNP configuration, CQDOPar = 1 for DO, Figure 2 | 0.15           | 0.4   | 0.4  | μs    |

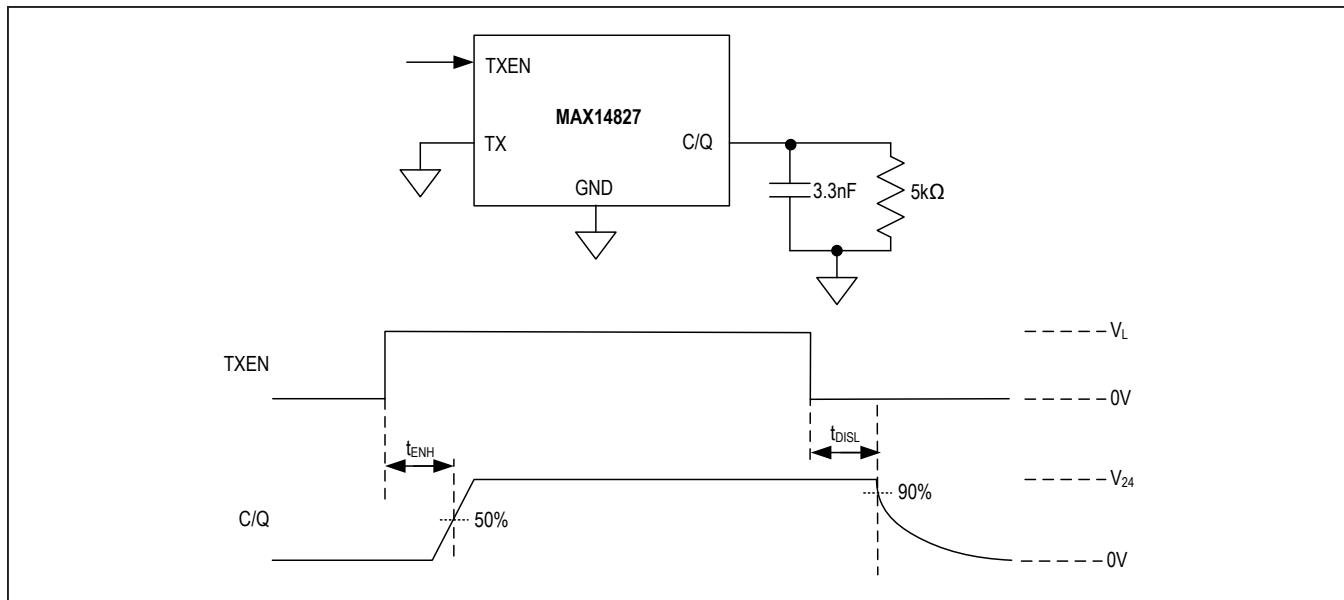

| Driver Enable Time Low                     | $t_{ENL}$      | Push-pull and NPN configuration, CQDOPar = 1 for DO, Figure 3 | 0.27           | 0.4   | 0.4  | μs    |

| Driver Disable Time High                   | $t_{DISH}$     | Push-pull and PNP configuration, CQDOPar = 1 for DO, Figure 2 | 1.8            | 3     | 3    | μs    |

| Driver Disable Time Low                    | $t_{DISL}$     | Push-pull and NPN configuration, CQDOPar = 1 for DO, Figure 3 | 1.5            | 3     | 3    | μs    |

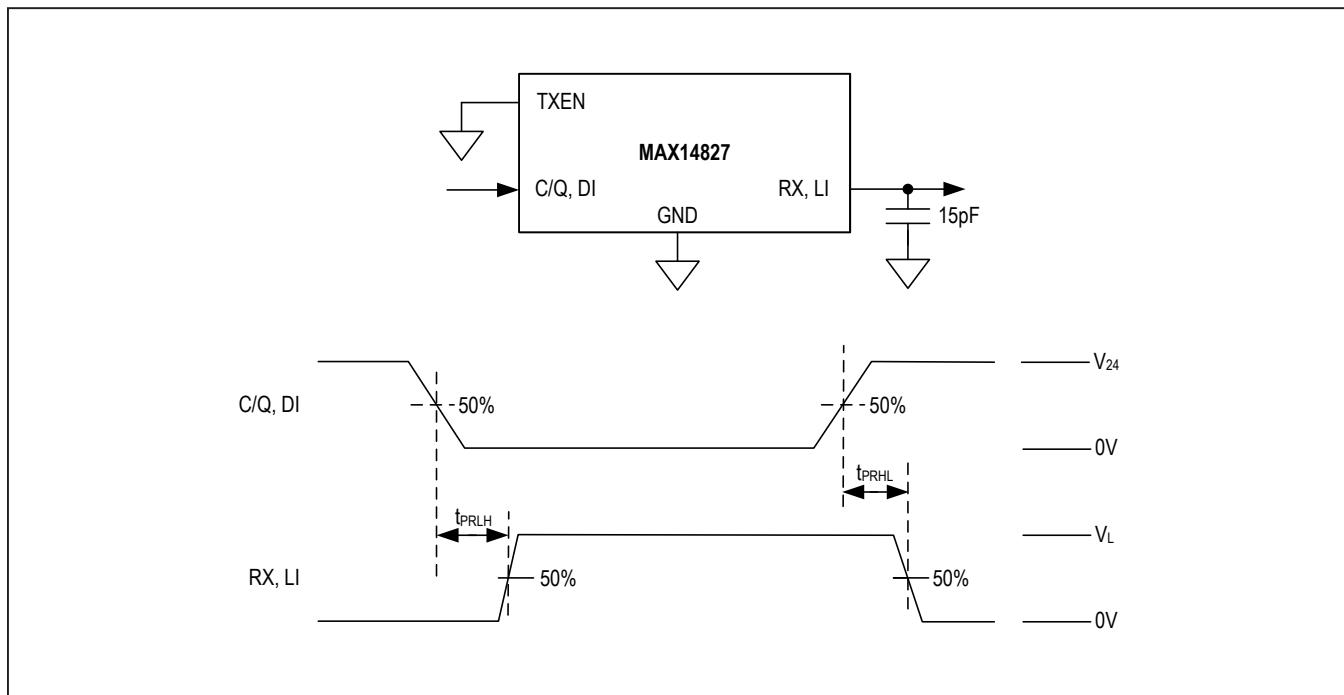

| <b>C/Q, DI RECEIVER (Figure 4)</b>         |                |                                                               |                |       |      |       |

| C/Q Receiver Low-to-High Propagation Delay | $t_{PRLH\_CQ}$ | SPI/ $\overline{PIN}$ = high or low, CQFil = 0                | 0.85           | 1.3   | 2.1  | μs    |

|                                            |                | SPI/ $\overline{PIN}$ = high, CQFil = 1                       | 0.2            | 0.3   | 0.5  |       |

| C/Q Receiver High-to-Low Propagation Delay | $t_{PRHL\_CQ}$ | SPI/ $\overline{PIN}$ = high or low, CQFil = 0                | 0.85           | 1.3   | 2.1  | μs    |

|                                            |                | SPI/ $\overline{PIN}$ = high, CQFil = 1                       | 0.2            | 0.3   | 0.5  |       |

| DI Receiver Low-to-High Propagation Delay  | $t_{PRLH\_DI}$ |                                                               | 1.3            | 2.2   | 3.5  | μs    |

| DI Receiver High-to-Low Propagation Delay  | $t_{PRHL\_DI}$ |                                                               | 1.3            | 2.2   | 3.5  | μs    |

| <b>DRIVER CURRENT LIMITING</b>             |                |                                                               |                |       |      |       |

| Blanking Time                              | $t_{CL\_ARBL}$ | SPI/ $\overline{PIN}$ = high                                  | CL_BL[10] = 00 | 0.128 |      | ms    |

|                                            |                |                                                               | CL_BL[10] = 01 | 0.5   |      |       |

|                                            |                |                                                               | CL_BL[10] = 10 | 1     |      |       |

|                                            |                |                                                               | CL_BL[10] = 11 | 5     |      |       |

|                                            |                | SPI/ $\overline{PIN}$ = low                                   |                | 0.128 |      |       |

| Autoretry Period                           | $t_{CL\_ARP}$  | SPI/ $\overline{PIN}$ = high,<br>ArEn = 1 (Note 3)            | TAr[10] = 00   | 50    |      | ms    |

|                                            |                |                                                               | TAr[10] = 01   | 100   |      |       |

|                                            |                |                                                               | TAr[10] = 10   | 200   |      |       |

|                                            |                |                                                               | TAr[10] = 11   | 500   |      |       |

## AC Electrical Characteristics (continued)

( $V_{24} = 18V$  to  $30V$ ,  $V_5 = 4.5V$  to  $5.5V$ ,  $V_L = 2.5V$  to  $5.5V$ ,  $V_{GND} = 0V$ ; REG unconnected, all logic inputs at  $V_L$  or  $GND$ ;  $T_A = -40^\circ C$  to  $+125^\circ C$ , unless otherwise noted. Typical values are at  $V_{24} = 24V$ ,  $V_5 = 5V$ ,  $V_L = 3.3V$ , and  $T_A = +25^\circ C$ , unless otherwise noted.)

(Note 2)

| PARAMETER                                                                    | SYMBOL      | CONDITIONS                     | MIN  | TYP | MAX | UNITS   |

|------------------------------------------------------------------------------|-------------|--------------------------------|------|-----|-----|---------|

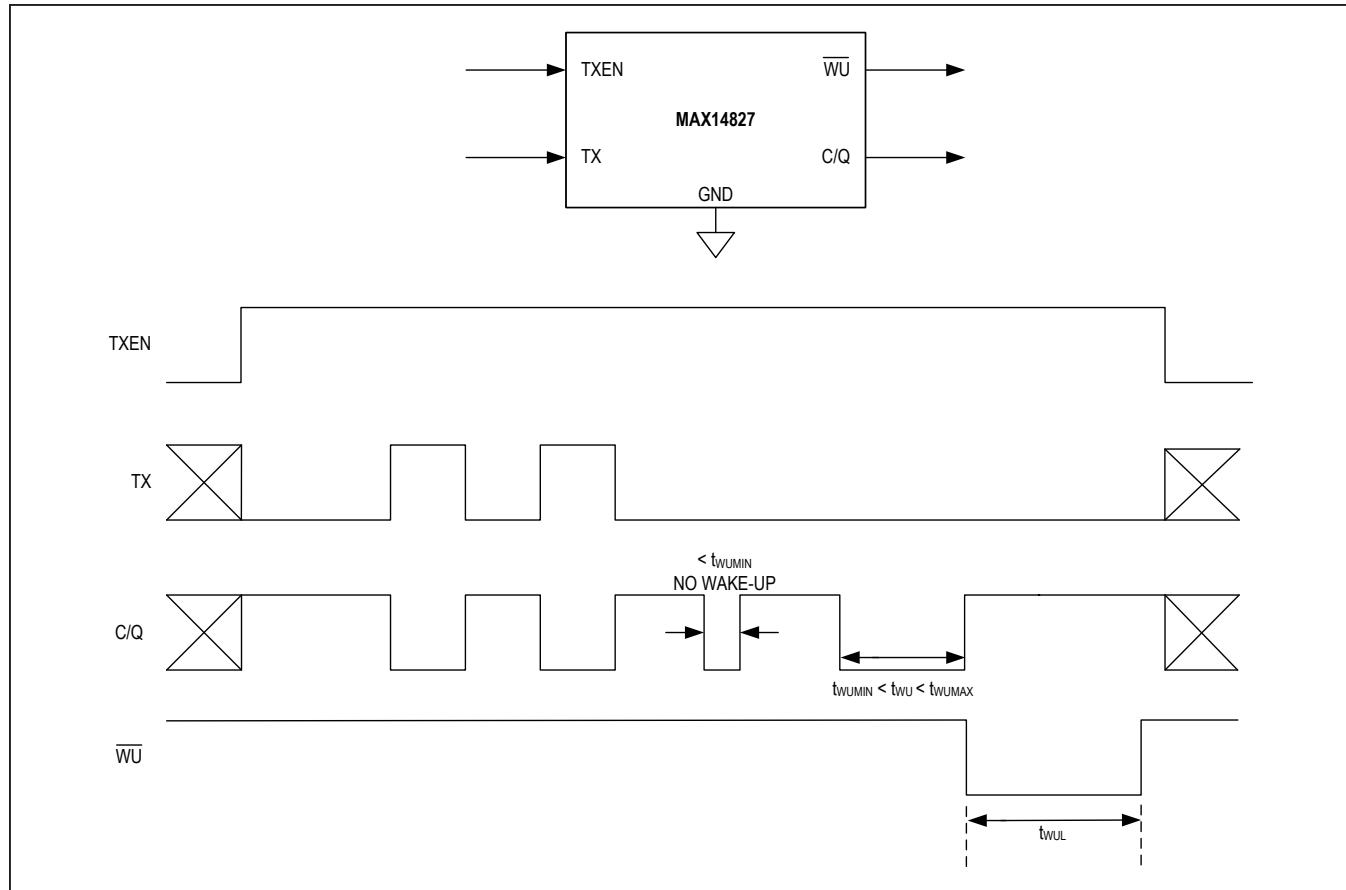

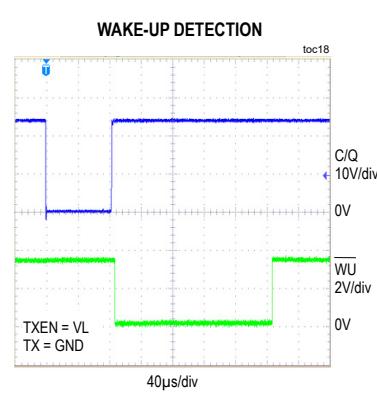

| <b>WAKE-UP DETECTION (Figure 5)</b>                                          |             |                                |      |     |     |         |

| Wake-Up Input Minimum Pulse Width                                            | $t_{WUMIN}$ | $C_L = 3nF$                    | 55   | 66  | 75  | $\mu s$ |

| Wake-Up Input Maximum Pulse Width                                            | $t_{WUMAX}$ |                                | 85   | 95  | 110 | $\mu s$ |

| WU Output Low Time                                                           | $t_{WUL}$   | Valid wake-up condition on C/Q | 100  | 200 | 300 | $\mu s$ |

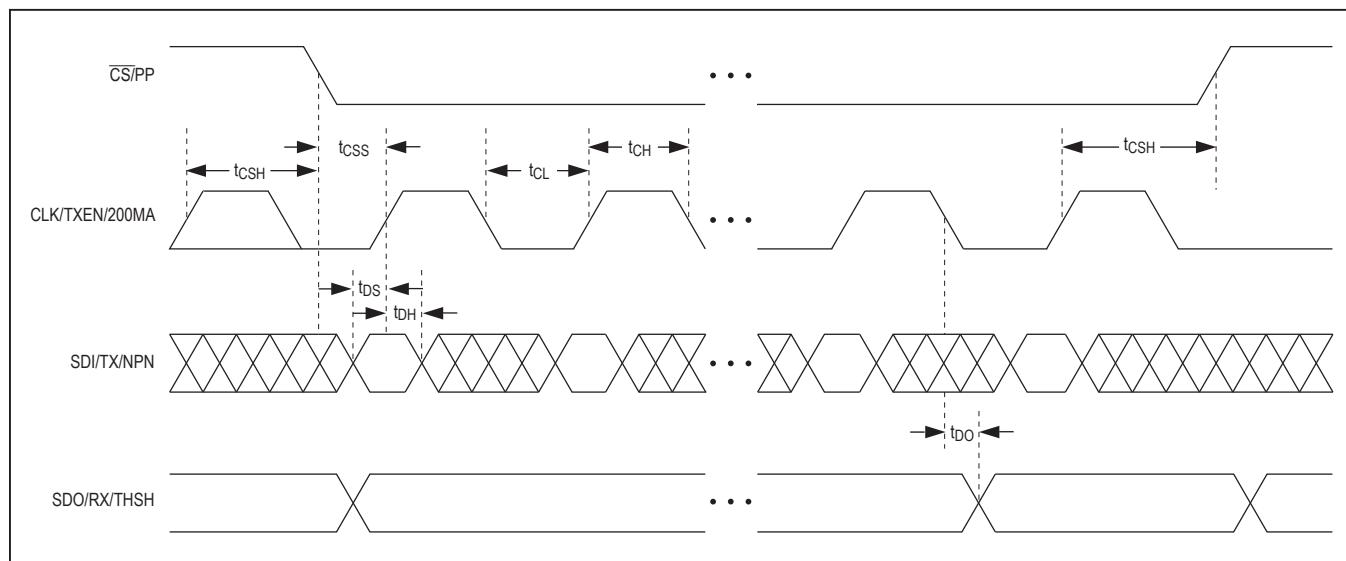

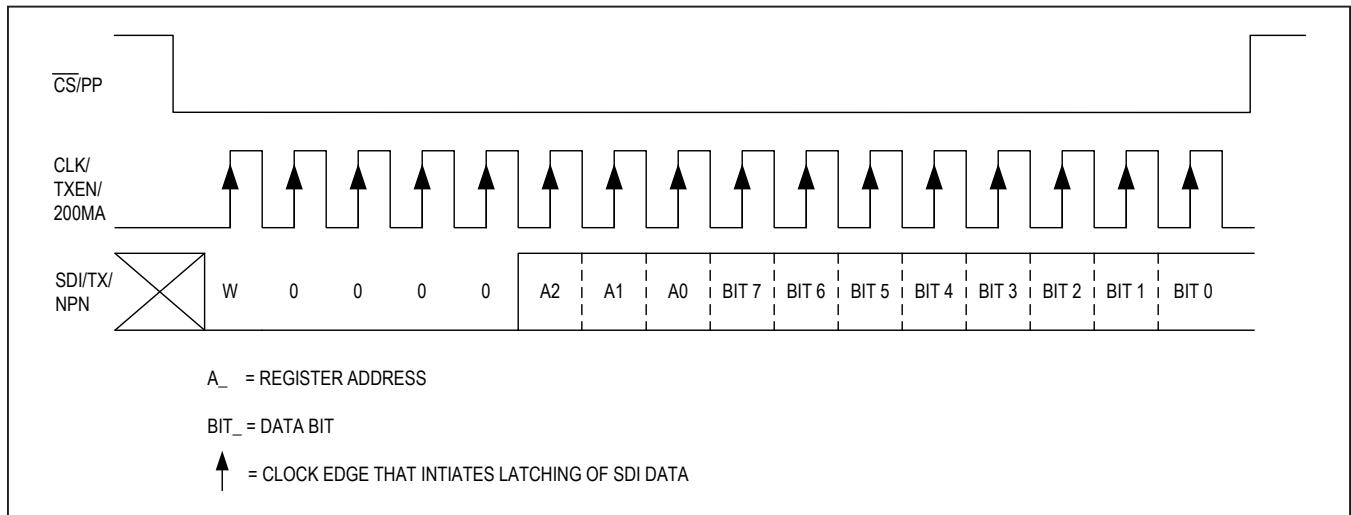

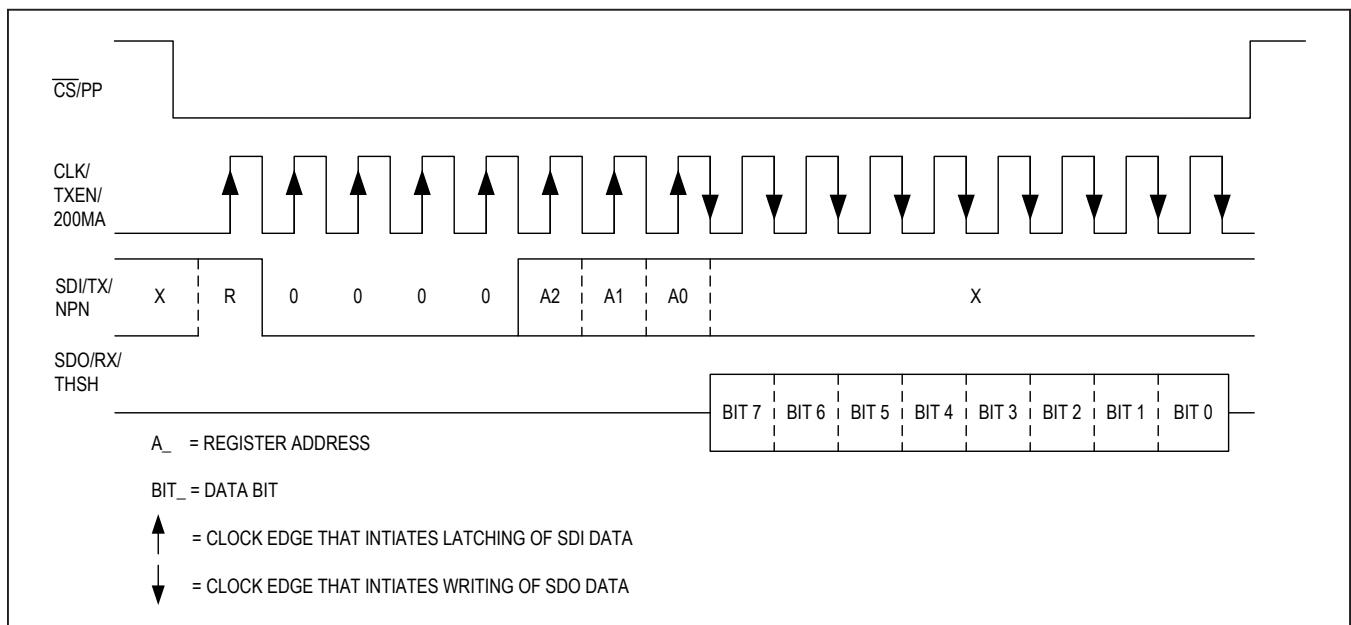

| <b>SPI TIMING (CS/PP, CLK/TXEN/200MA,SDI,TX/NPN, SDO/RX/THSH) (Figure 6)</b> |             |                                |      |     |     |         |

| Maximum SPI Clock Frequency                                                  |             |                                | 12.5 |     |     | MHz     |

| CLK/TXEN/200MA Clock Period                                                  | $t_{CH+CL}$ |                                | 80   |     |     | ns      |

| CLK/TXEN/200MA Pulse-Width High                                              | $t_{CH}$    |                                | 40   |     |     | ns      |

| CLK/TXEN/200MA Pulse-Width Low                                               | $t_{CL}$    |                                | 40   |     |     | ns      |

| CS/PP Fall to CLK/TXEN/200MA Rise Time                                       | $t_{CSS}$   |                                | 20   |     |     | ns      |

| CLK/TXEN/200MA Rise to CS/PP Rise Hold Time                                  | $t_{CSH}$   |                                | 40   |     |     | ns      |

| SDI/TX/NPN Hold Time                                                         | $t_{DH}$    |                                | 10   |     |     | ns      |

| SDI/TX/NPN Setup Time                                                        | $t_{DS}$    |                                |      | 25  |     | ns      |

| Output Data Propagation Delay                                                | $t_{DO}$    |                                |      | 20  |     | ns      |

| SDO/RX/THSH Rise and Fall Times                                              | $t_{FT}$    |                                |      | 20  |     | ns      |

| Minimum CS/PP Pulse                                                          | $t_{CSW}$   |                                |      | 10  |     | ns      |

**Note 1:** All devices are 100% production tested at  $T_A = +25^\circ C$ . Limits over the operating temperature range are guaranteed by design.

**Note 2:** Not production tested. Guaranteed by design.

**Note 3:** Autoretry functionality is not available in pin-mode.

Figure 1. C/Q and LO Driver Propagation Delays and Rise/Fall Times

Figure 2. C/Q Driver Enable Low and Disable High Timing with External Pullup Resistor

Figure 3. C/Q Driver Enable High and Disable Low Timing

Figure 4. C/Q and DI Receiver Propagation Delays

Figure 5. Wake-Up Detection Timing

Figure 6. SPI Timing Diagram

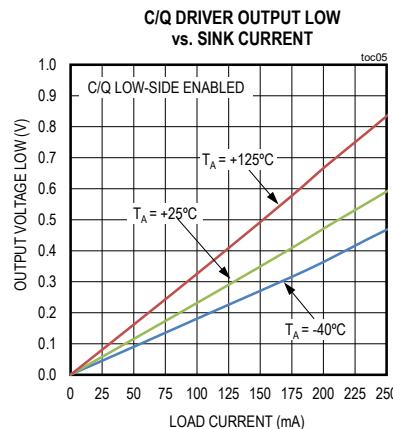

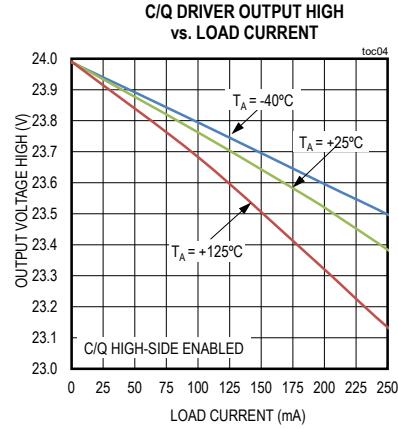

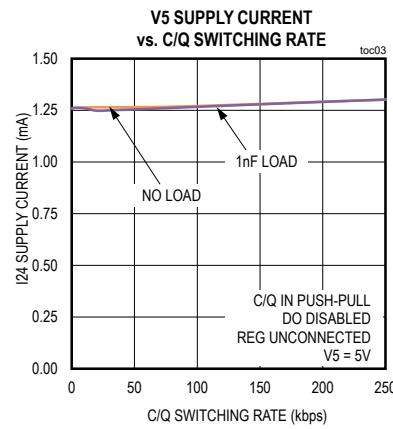

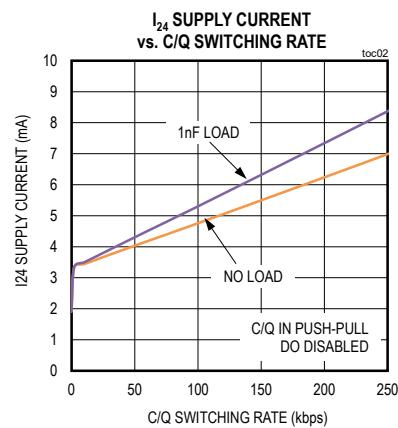

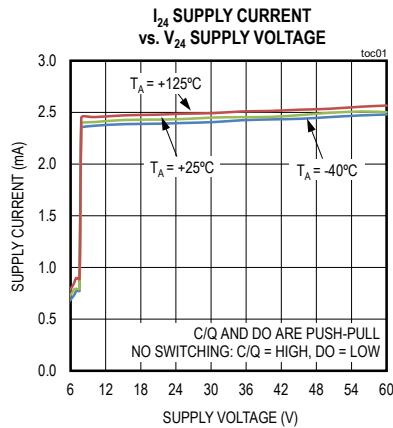

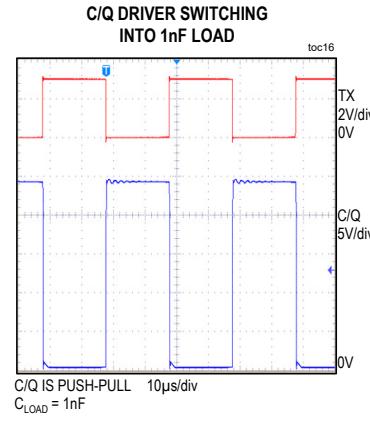

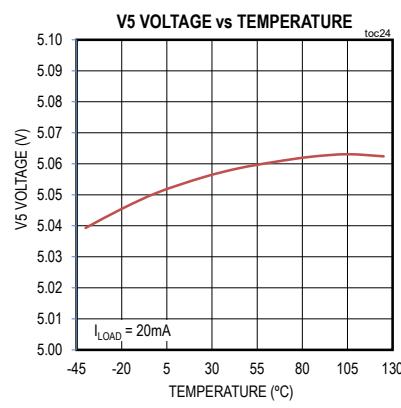

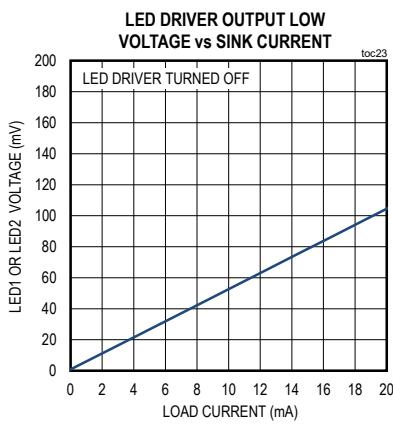

## Typical Operating Characteristics

( $V_{24} = 24V$ ,  $V_L = V_{33}$ , REG is shorted to  $V_5$ , C/Q and DO in push-pull configuration,  $T_A = +25^\circ C$ , unless otherwise noted.)

## Typical Operating Characteristics (continued)

( $V_{24} = 24V$ ,  $V_L = V_{33}$ , REG is shorted to V5, C/Q and DO in push-pull configuration,  $T_A = +25^\circ C$ , unless otherwise noted.)

## Typical Operating Characteristics (continued)

( $V_{24} = 24V$ ,  $V_L = V_{33}$ , REG is shorted to V5, C/Q and DO in push-pull configuration,  $T_A = +25^\circ C$ , unless otherwise noted.)

## Typical Operating Characteristics

( $V_{24} = 24V$ ,  $V_L = V_{33}$ , REG is shorted to  $V_5$ , C/Q and DO in push-pull configuration,  $T_A = +25^\circ C$ , unless otherwise noted.)

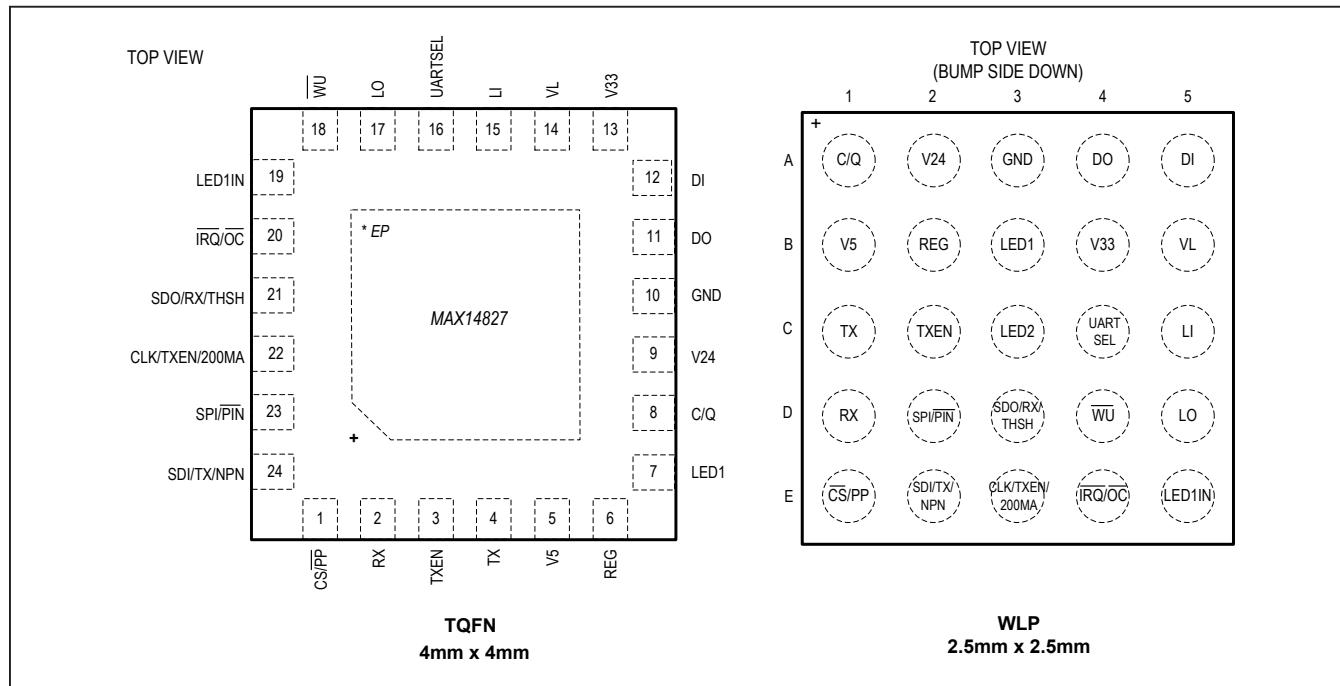

## Pin Configuration

## Pin Description

| PIN  |     | NAME  | PIN DESCRIPTION                                                                                                                                                            | FUNCTION                                                                                                                                                                                          |                                      |                                                                                                                                                               |  |  |

|------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN | WLP |       |                                                                                                                                                                            | PARALLEL MODE<br>(SPI/PIN = high)                                                                                                                                                                 | MULTIPLEXED MODE<br>(SPI/PIN = high) | PIN MODE<br>(SPI/PIN = low)                                                                                                                                   |  |  |

|      |     |       |                                                                                                                                                                            | UARTSEL = Low                                                                                                                                                                                     | UARTSEL = high                       |                                                                                                                                                               |  |  |

| 1    | E1  | CS/PP | SPI active-low chip-select input. Drive CS/PP low to start the SPI read/write cycle. Drive CS/PP high to end the SPI cycle. UART interface is enabled on RX, TX, and TXEN. | SPI chip-select and UART signal select input. When CS/PP is high, the SPI interface is disabled and UART interface mode is enabled on the SDO/RX/THSH, SDI/TX/NPN, and CLK/TXEN/200MA logic pins. |                                      | Push-pull select input. Drive CS/PP high to enable push-pull mode for the C/Q and DO drivers. Drive CS/PP low to select PNP or NPN operation for the drivers. |  |  |

| 2    | D1  | RX    | C/Q Receiver Logic Output                                                                                                                                                  | RX is the inverse logic of C/Q. RX can be disabled with the SPI interface. RX is high impedance when Rx_Dis = 1.                                                                                  |                                      | RX is the inverse logic of C/Q. RX is always active.                                                                                                          |  |  |

## Pin Description (continued)

| PIN  |     | NAME | PIN DESCRIPTION                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                   |                                                                                                                 |  |  |

|------|-----|------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| TQFN | WLP |      |                                | PARALLEL MODE (SPI/PIN = high)                                                                                                                                                                                                                                                                                                                                                                                            | MULTIPLEXED MODE (SPI/PIN = high)                                                                                                                                                                                 | PIN MODE (SPI/PIN = low)                                                                                        |  |  |

|      |     |      |                                | UARTSEL = Low                                                                                                                                                                                                                                                                                                                                                                                                             | UARTSEL = high                                                                                                                                                                                                    |                                                                                                                 |  |  |

| 3    | C2  | TXEN | C/Q Driver Enable Logic Input  | Drive TXEN high to enable the C/Q driver. See Table 1.                                                                                                                                                                                                                                                                                                                                                                    | With $\overline{CS}/PP$ low and ENMPX = 0, drive TXEN high to enable C/Q.                                                                                                                                         | Drive TXEN high to enable the C/Q driver. Drive TXEN low to disable the C/Q driver and enable the C/Q receiver. |  |  |

| 4    | C1  | TX   | C/Q Driver Communication Input | The logic on the C/Q output is the inverse logic level of the signal on the TX input. See Table 1.                                                                                                                                                                                                                                                                                                                        | With $\overline{CS}/PP$ low and ENMPX = 0, the logic on the C/Q output is the inverse logic level of the signal on the SDI/TX/NPN input. Signals on TX are ignored. See the Mode Selection table.                 | The logic on the C/Q output is the inverse logic level of the signal on the TX input when TXEN is high.         |  |  |

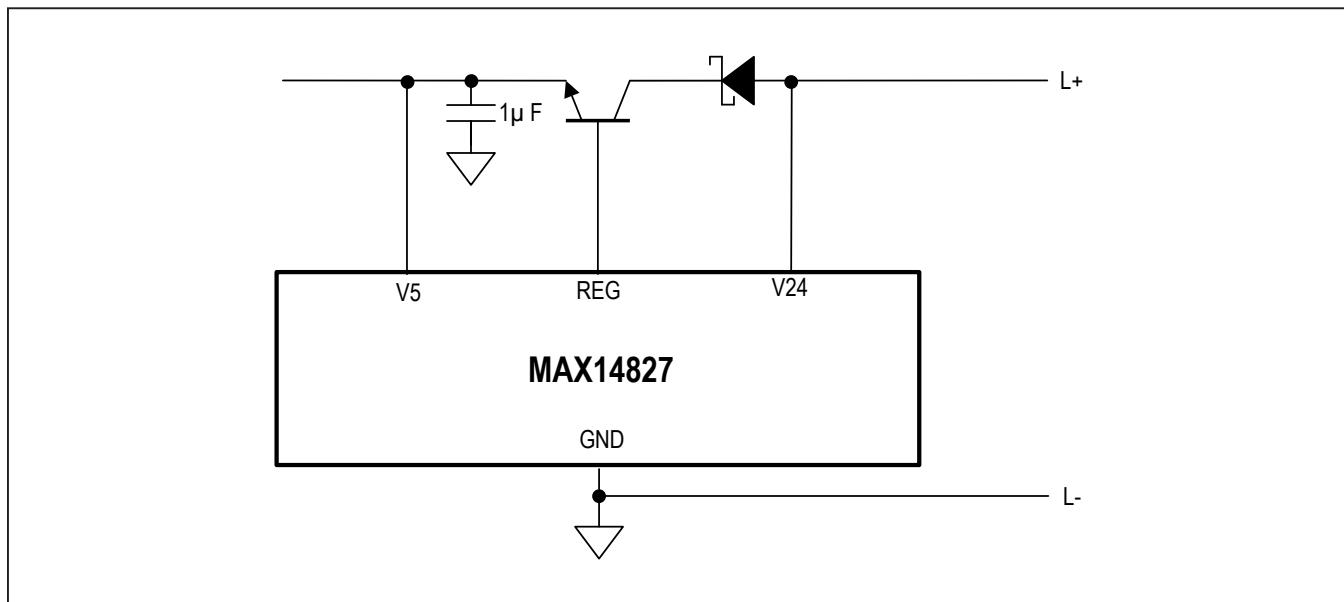

| 5    | B1  | V5   | 5V Power-Supply Input/Output   | 5V must be present on V5 for normal operation. Bypass V5 to GND with a $1\mu F$ capacitor. V5 can be supplied by the internal 5V linear regulator or by an external regulator. To use the internal regulator, connect V5 to REG, or to the emitter of an external NPN transistor. To bypass the internal regulator, connect an external 5V supply directly to V5.                                                         |                                                                                                                                                                                                                   |                                                                                                                 |  |  |

| 6    | B2  | REG  | 5V Regulator Control Output    | To use the internal linear regulator, connect REG to V5 or connect REG to the base of an external NPN pass transistor. Leave REG unconnected and connect V5 to an external 5V supply to bypass the internal regulator.                                                                                                                                                                                                    |                                                                                                                                                                                                                   |                                                                                                                 |  |  |

| 7    | B3  | LED1 | LED Driver Output 1            | LED1 is a 5V logic output. Connect a current-limiting resistor in series between LED1 and the LED to limit the LED current. LED1 can be controlled by driving the LED1IN high or low, or through the SPI interface. Set the LED1b bit high to turn on the LED, clear the LED1b bit to turn off the LED. Alternatively, drive the LED1IN input high to turn on the LED, drive LED1IN low to turn off the LED. See Table 2. | LED1 is a 5V logic output. Connect a current-limiting resistor in series between LED1 and the LED to limit the LED current. Drive the LED1IN input high to turn on the LED, drive LED1IN low to turn off the LED. |                                                                                                                 |  |  |

| -    | C3  | LED2 | LED Driver Output 2            | LED2 is a 5V logic output. Connect a current-limiting resistor in series between LED2 and the LED to limit the LED current. Set the LED2b bit high to turn on the LED, clear the LED2b bit to turn off the LED.                                                                                                                                                                                                           | LED2 cannot be controlled in pin-mode. LED2 is off.                                                                                                                                                               |                                                                                                                 |  |  |

## Pin Description (continued)

| PIN  |     | NAME | PIN DESCRIPTION               | FUNCTION                                                                                                                                                                                                                                                                      |                                                                                                                                                                                         |                                                          |  |  |

|------|-----|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| TQFN | WLP |      |                               | PARALLEL MODE<br>( $\overline{\text{SPI/PIN}} = \text{high}$ )                                                                                                                                                                                                                | MULTIPLEXED<br>MODE<br>( $\overline{\text{SPI/PIN}} = \text{high}$ )                                                                                                                    | PIN MODE<br>( $\overline{\text{SPI/PIN}} = \text{low}$ ) |  |  |

|      |     |      |                               | $\text{UARTSEL} = \text{Low}$                                                                                                                                                                                                                                                 | $\text{UARTSEL} = \text{high}$                                                                                                                                                          |                                                          |  |  |

| 8    | A1  | C/Q  | C/Q Transceiver Output/ Input | The C/Q driver can be controlled and monitored with the logic input/output pins or through the SPI interface. Drive TXEN high to enable the C/Q driver. The logic on the C/Q output is the inverse logic-level of the signal in the TX input. RX is the logic inverse of C/Q. | Drive TXEN high to enable the C/Q driver. The logic on the C/Q output is the inverse logic-level of the signal in the TX input. RX is the logic inverse of C/Q.                         | Configure the C/Q driver with the pin-mode inputs.       |  |  |

| 9    | A2  | V24  | Power-Supply Input            | Bypass V24 to GND with a $1\mu\text{F}$ ceramic capacitor as close to the device as possible.                                                                                                                                                                                 |                                                                                                                                                                                         |                                                          |  |  |

| 10   | A3  | GND  | Ground                        |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                         |                                                          |  |  |

| 11   | A4  | DO   | DO Driver Output              | DO is the inverse logic level of the LO input. The DO driver can be enabled/disabled, configured, controlled, and monitored with the logic input/output pins or through the SPI interface.                                                                                    | DO is the inverse logic level of the LO input. Configure the DO driver with the pin-mode inputs. DO cannot be disabled in pin-mode.                                                     |                                                          |  |  |

| 12   | A5  | DI   | DI Receiver Input             | The DI receiver can be monitored on the LI output or through the SPI interface. The LI output is the inverse logic-level of the signal on the DI input. Connect a $1\text{k}\Omega$ resistor in series with the DI pin.                                                       | The LI output is the inverse logic-level of the signal on the DI input. The DI receiver cannot be disabled in pin-mode. Connect a $1\text{k}\Omega$ resistor in series with the DI pin. |                                                          |  |  |

| 13   | B4  | V33  | 3.3V Linear Regulator Output  | Bypass V33 to GND with a $1\mu\text{F}$ capacitor as close to the IC as possible. The V33 regulator can be disabled through the SPI interface.                                                                                                                                | Bypass V33 to GND with a $1\mu\text{F}$ capacitor as close to the IC as possible. V33 cannot be disabled in pin-mode.                                                                   |                                                          |  |  |

| 14   | B5  | VL   | Logic-Level Supply Input      | VL defines the logic levels on all of the logic inputs and outputs. Apply a voltage from 2.5V to 5.5V on VL. Bypass VL to GND with a $0.1\mu\text{F}$ ceramic capacitor.                                                                                                      |                                                                                                                                                                                         |                                                          |  |  |

| 15   | C5  | LI   | DI Receiver Logic Output      | The LI output is the inverse logic-level of the signal on the DI input. Disable the LI output through the SPI interface. LI is high impedance when the DI_Dis bit is set.                                                                                                     | The LI output is the inverse logic-level of the signal on the DI input. LI cannot be disabled in pin-mode.                                                                              |                                                          |  |  |

## Pin Description (continued)

| PIN  |     | NAME                       | PIN DESCRIPTION                                                   | FUNCTION                                                                                                                                                                                |                                                                                                                                                    |                                                                                                                                 |  |  |

|------|-----|----------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN | WLP |                            |                                                                   | PARALLEL MODE<br>( $\overline{\text{SPI/PIN}} = \text{high}$ )                                                                                                                          | MULTIPLEXED MODE<br>( $\overline{\text{SPI/PIN}} = \text{high}$ )                                                                                  | PIN MODE<br>( $\overline{\text{SPI/PIN}} = \text{low}$ )                                                                        |  |  |

|      |     |                            |                                                                   | UARTSEL = Low                                                                                                                                                                           | UARTSEL = high                                                                                                                                     |                                                                                                                                 |  |  |

| 16   | C4  | UARTSEL                    | UART Interface Select Logic Input                                 | Drive UARTSEL low to use RX, TX, and TXEN for UART signaling.                                                                                                                           | When $\overline{\text{CS/PP}}$ is high, use SDO/RX/THSH, SDI/TX/NPN, and CLK/TXEN/200MA for UART signaling.                                        | UARTSEL is inactive when SPI/PIN is low.                                                                                        |  |  |

| 17   | D5  | LO                         | DO Driver Logic Input                                             | The logic on the DO output is the inverse logic-level of the signal on the LO input. Configure, control, and monitor the DO output through the logic pins or through the SPI interface. | The logic on the DO output is the inverse logic-level of the signal on the LO input. Configure the DO driver with the pin-mode inputs.             |                                                                                                                                 |  |  |

| 18   | D4  | $\overline{\text{WU}}$     | Wake-Up Request Push-Pull Output                                  | $\overline{\text{WU}}$ asserts low for 200 $\mu$ s when an IO-Link 80 $\mu$ s wake-up condition is detected on the C/Q line.                                                            |                                                                                                                                                    |                                                                                                                                 |  |  |

| 19   | E5  | LED1IN                     | LED1 Driver Logic Input                                           | Drive LED1IN high or low to enable/disable the LED1 driver. The LED1 driver can also be controlled through the SPI interface. See Table 2.                                              | Drive LED1IN high to turn on the LED connected to LED1. Drive LED1IN low to turn the LED driver off.                                               |                                                                                                                                 |  |  |

| 20   | E4  | $\overline{\text{IRQ/OC}}$ | Open-Drain Interrupt/Over-current Output                          | $\overline{\text{IRQ/OC}}$ asserts when any bit in the INTERRUPT register is set. $\overline{\text{IRQ/OC}}$ deasserts when the INTERRUPT register is read.                             | $\overline{\text{IRQ/OC}}$ asserts low when the load current on the C/Q or DO output exceeds the set current limit.                                |                                                                                                                                 |  |  |

| 21   | D3  | SDO/RX/THSH                | SPI Serial Data Output/RX Logic Output/Thermal Shutdown Indicator | SPI serial data output                                                                                                                                                                  | When $\overline{\text{CS/PP}}$ is high, the SPI interface is disabled and UART interface mode is enabled. SDO/RX/THSH is the logic inverse of C/Q. | SDO/RX/THSH asserts low when the IC enters thermal shutdown. SDO/RX/THSH deasserts when the device returns to normal operation. |  |  |

## Pin Description (continued)

| PIN  |     | NAME           | PIN DESCRIPTION                                                             | FUNCTION                                                                                          |                                                                                                                                                                                                 |                                                                                                                                                                                                                 |  |  |

|------|-----|----------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN | WLP |                |                                                                             | PARALLEL MODE<br>(SPI/PIN = high)                                                                 |                                                                                                                                                                                                 | PIN MODE<br>(SPI/PIN = low)                                                                                                                                                                                     |  |  |

|      |     |                |                                                                             | UARTSEL = Low                                                                                     |                                                                                                                                                                                                 |                                                                                                                                                                                                                 |  |  |

| 22   | E3  | CLK/TXEN/200MA | SPI Clock Input/<br>UART TXEN Input/<br>Current Limit Setting Input         | SPI clock input                                                                                   | When $\overline{CS}/\overline{PP}$ is high, the SPI interface is disabled and UART interface mode is enabled. Drive CLK/TXEN/200MA high to enable the C/Q driver.                               | Drive CLK/TXEN/200MA high to enable a 200mA current limit on the C/Q and DO driver outputs. Drive CLK/TXEN/200MA low to set the current limit for the driver outputs to 100mA.                                  |  |  |

| 23   | D2  | SPI/PIN        | SPI or Pin-Mode Select Input                                                | Drive SPI/PIN high for SPI or UART interface operation. Drive SPI/PIN low for pin-mode operation. |                                                                                                                                                                                                 |                                                                                                                                                                                                                 |  |  |

| 24   | E2  | SDI/TX/NPN     | SPI Serial Data Input/<br>TX Logic Input/<br>NPN Driver Mode Select Input   | SPI serial data input                                                                             | When $\overline{CS}/\overline{PP}$ is high, the SPI interface is disabled and UART interface mode is enabled. Drive SDI/TX/NPN to switch C/Q. C/Q is the logic inverse of the SDI/TX/NPN input. | Drive SDI/TX/NPN high to set the C/Q and DO driver outputs in NPN mode. Drive SDI/TX/NPN low to set the driver outputs in PNP mode. SDI/TX/NPN is ignored when the $\overline{CS}/\overline{PP}$ input is high. |  |  |

| EP   | –   | EP             | Exposed pad. Connect to ground. Not intended as the main ground connection. |                                                                                                   |                                                                                                                                                                                                 |                                                                                                                                                                                                                 |  |  |

**Table 1. C/Q and DO Control**

| SPI/PIN | TXEN | TX or LO | CQ_Dis or DO_Dis | CQ_Q or DO_Q | NPN MODE |    | PNP MODE |    | PP MODE |    |

|---------|------|----------|------------------|--------------|----------|----|----------|----|---------|----|

|         |      |          |                  |              | C/Q      | DO | C/Q      | DO | C/Q     | DO |

| L       | L    | L        | -                | -            | Z        | Z  | Z        | H  | Z       | H  |

|         |      | H        | -                | -            | Z        | L  | Z        | Z  | Z       | L  |

|         | H    | L        | -                | -            | Z        | Z  | H        | H  | H       | H  |

|         |      | H        | -                | -            | L        | L  | Z        | Z  | L       | L  |

| H       | L    | L        | 0                | 0            | Z        | Z  | Z        | H  | Z       | H  |

|         |      | L        | 0                | 1            | Z        | Z  | H        | H  | H       | H  |

|         |      | H        | 0                | 0            | Z        | L  | Z        | Z  | Z       | L  |

|         |      | H        | 0                | 1            | Z        | Z  | H        | H  | H       | H  |

|         | H    | L        | 0                | 0            | Z        | Z  | H        | H  | H       | H  |

|         |      | L        | 0                | 1            | Z        | Z  | H        | H  | H       | H  |

|         |      | H        | 0                | 0            | L        | L  | Z        | Z  | L       | L  |

|         |      | H        | 0                | 1            | Z        | Z  | H        | H  | H       | H  |

|         |      | X        | X                | 1            | X        | Z  | Z        | Z  | Z       | Z  |

X = *Don't care*, Z = *High impedance*

**Table 2: LED1 Configuration**

| LED1IN | LED1b BIT | LED1 DRIVER STATUS |

|--------|-----------|--------------------|

| L      | 0         | OFF                |

|        | 1         | ON                 |

| H      | 0         | ON                 |

|        | 1         | ON                 |

**Table 3. Driver NPN, PNP, PP Selection in Pin-Mode**

| SPI/PIN | CS/PP | SDI/TX/NPN | C/Q AND DO DRIVER MODE                          |

|---------|-------|------------|-------------------------------------------------|

| L       | L     | L          | PNP                                             |

| L       | L     | H          | NPN                                             |

| L       | H     | L          | PUSH-PULL                                       |

| L       | H     | H          | PUSH-PULL                                       |

| H       | X     | X          | C/Q and DO Modes are set with the SPI interface |

## Detailed Description

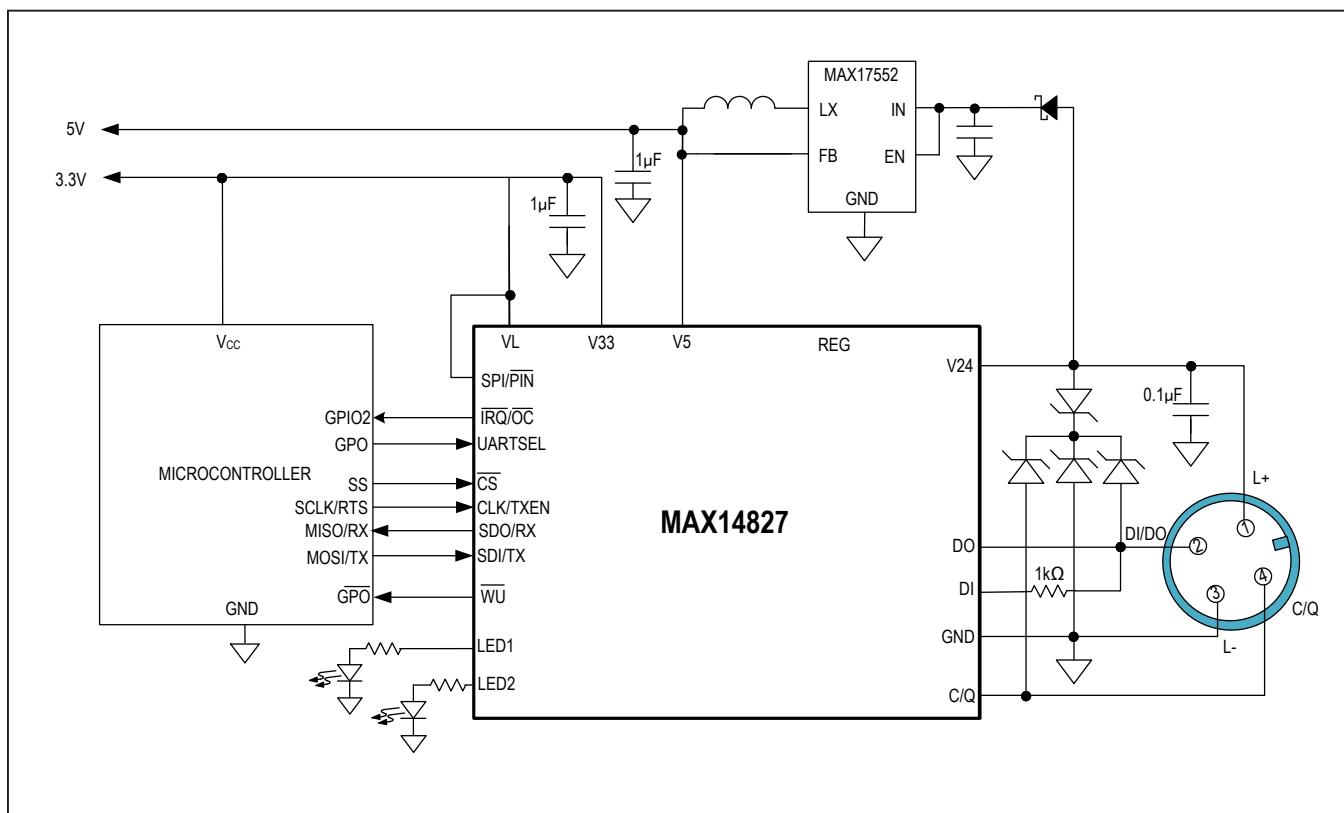

The MAX14827 is an industrial sensor output driver/IO-Link device transceiver. The IC integrates the high voltage functions commonly found in sensors, including two 24V line driver and two on-board linear regulators (LDOs). The MAX14827 can be configured and monitored either through the SPI interface or by setting logic interface pins.

The MAX14827 features multiple programmable functions that allow the user to optimize operation and power dissipation for various loads and application scenarios.

The integrated 3.3V and 5V LDOs provide the power needed for low noise analog and logic supply rails.

## SPI, UART, or Pin-Mode Interface

### Pin-Mode

The MAX14827 provides a selectable SPI or pin interface to configure and monitor device operation. Drive the SPI/PIN input high to use the SPI. Drive SPI/PIN low to use the pin interface (pin-mode control).

When operating in pin mode, the following functionality is set and cannot be changed:

- RX and DI are enabled (cannot be disabled)

- RX deglitch filter is enabled

- Weak pull-ups/pull-downs on C/Q and DO are disabled

- Autoretry functionality is disabled

- The blanking time on C/Q and DO is 128 $\mu$ s

### SPI Operation (Parallel Operating Mode)

When the MAX14827 is operated in SPI mode, an external UART can be connected to separate UART interface pins (TX, RX, TXEN). This is called the parallel SPI/UART operating mode. This is the common approach used when the microcontroller offers a UART and a separate SPI port in the Typical Applications circuit. Drive UARTSEL low for operation in parallel mode.

### SPI Operation (Multiplexed Mode)

In cases where only one microcontroller serial port is available with both SPI and UART functions, the MAX14827 can be operated in multiplexed SPI/UART mode. This is feasible in IO-Link operation due to the defined idle times in the IO-Link cycle time. In multiplexed mode, the UART and SPI pins are shared. Two operating modes are available in multiplexed mode, as selected by the ENMPX bit.

When ENMPX = 0, UART and SPI operation are selected by setting the CS/PP input. In this mode the SPI interface

is active when CS/PP is low and UART operation when CS/PP is high.

When ENMPX = 1, UART and SPI operations are selected by setting the UARTSEL input. To avoid glitches on C/Q, CLK/TXEN/200MA and SDI/TX/NPN are sampled on the falling edge of UARTSEL in this mode. See Mode Selection Table for more information.

When entering multiplexed mode, set TXEN low and TX high to disable the driver.

IRQ/OC is active in both multiplexed modes during UART communication.

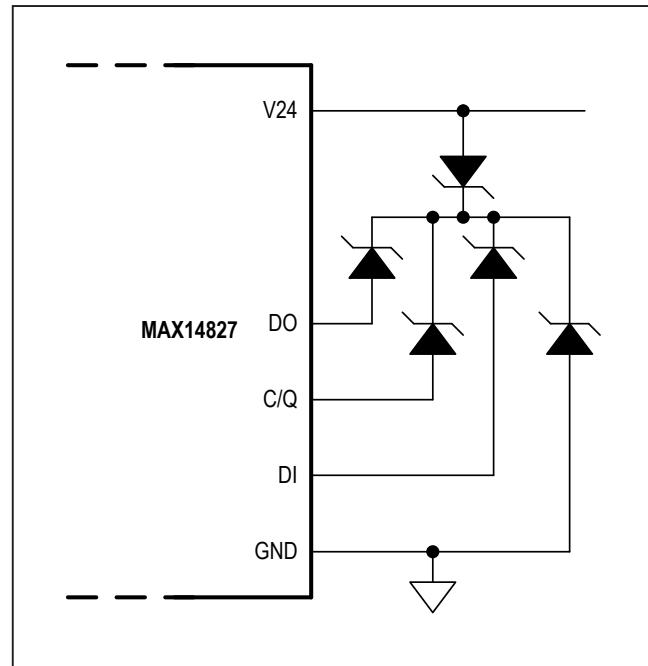

### 24V Interface

The MAX14827 features an IO-Link transceiver interface capable of operating with voltages up to 60V. This is the 24V interface and includes the C/Q input/output, the logic-level digital output (DO), the logic-level digital input (DI), and the V24 supply.

The MAX14827 features selectable push-pull, high-side (PNP), or low-side (NPN) switching drivers at C/Q and DO.

### Configurable Drivers (Pin-Mode)

In pin-mode, use SDI/TX/NPN and CS/PP inputs to configure the C/Q and DO drivers in push-pull, PNP, or NPN modes (Table 3). In this mode, toggle TXEN, TX, and LO to switch the C/Q and DO outputs.

### Configurable Drivers (SPI Mode)