## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| DCIN, BAT, DCOUT, DCDIV, SHDN                                     |

|-------------------------------------------------------------------|

| to GND0.3V to 20V                                                 |

| Input Voltage (CLP, CLN)0.3V to DCIN + 0.3V                       |

| Input Voltage (CSP, CSN)0.3V to BAT + 0.3V                        |

| Input Voltage                                                     |

| (GPI01, GPI02, GPI03, SELC, SELA, TYPE, V <sub>CHG</sub> ,        |

| THA, THB, I <sub>SENSE</sub> , ACPDLY, SDA, SCL) – 0.3V to 7V     |

| Input Voltage (V <sub>CAL</sub> , V <sub>DIS</sub> )0.3V to 1.35V |

| Output Voltage                                                    |

| (ACPb, GPI01, GPI02, GPI03)0.3V to 7V                             |

| CLP-CLN, CSP-CSN±1V                                               |

| Operating Temperature Range (Note 2)40°C to 85°C                  |

| Junction Temperature (Note 3)105°C                                |

| Storage Temperature Range                                         |

| QFN Package65°C to 125°C                                          |

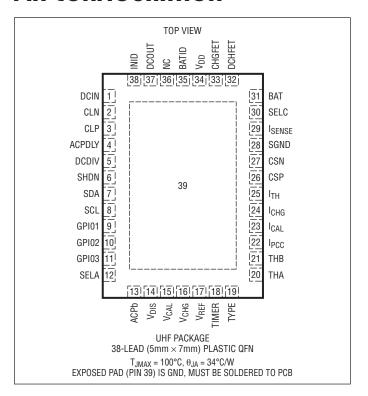

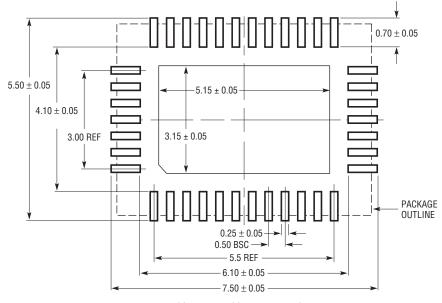

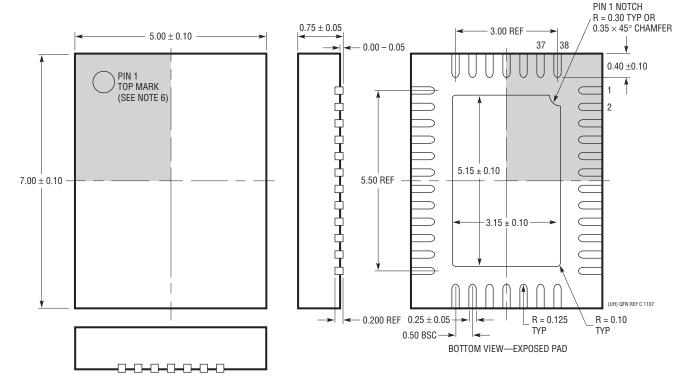

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|-------------------|--------------|---------------------------------|-------------------|

| LTC4110EUHF#PBF   | LTC4110EUHF#TRPBF | 4110         | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

| LTC4110EUHF       | LTC4110EUHF#TR    | 4110         | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Unless otherwise specified,  $V_{DCIN} = V_{DCOUT} = V_{DCDIV} = 12V$ ,  $V_{BAT} = 8.4V$ , GND = SGND = CLP = CLN = SHDN = 0V and  $R_{VREF} = 49.9k$ . All currents into device pins are positive and all currents out of device pins are negative. All voltages are referenced to GND, unless otherwise specified.

| SYMBOL                   | PARAMETER                                                                         | CONDITIONS                                                                                                            |   | MIN             | TYP          | MAX          | UNITS    |

|--------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|-----------------|--------------|--------------|----------|

| Power Inpu               | t                                                                                 | 1                                                                                                                     |   |                 |              |              |          |

| DCIN                     | Operating Voltage Range                                                           | Charge or Calibration Modes                                                                                           | • | 4.5             |              | 19           | V        |

| DCOUT                    | Operating Voltage Range                                                           | Charge or Calibration Modes                                                                                           | • | 4.5             |              | 19           | V        |

|                          |                                                                                   | Backup Mode                                                                                                           | • | 2.7             |              | 19           | V        |

| $\overline{V_{BAT}}$     | Operating Voltage Range                                                           | Backup Mode                                                                                                           | • | 2.7             |              | 19           | V        |

| I <sub>SPLY</sub>        | Supply Current (I <sub>DCIN</sub> + I <sub>DCOUT</sub> ) in Idle Mode (Note 4)    |                                                                                                                       |   |                 | 2            | 3            | mA       |

| I <sub>BIDL</sub>        | Battery Current in Idle Mode (Notes 4 and 5)                                      |                                                                                                                       |   |                 | 30           | 45           | μА       |

| I <sub>BBU</sub>         | Battery Current in Backup Mode (Note 5)                                           | V <sub>DCIN</sub> = 0                                                                                                 |   |                 | 2            | 3            | mA       |

| I <sub>BSD</sub>         | Battery Current in Shutdown (Note 5)                                              | V <sub>SHDN</sub> = V <sub>BAT</sub> , V <sub>DCIN</sub> = 0                                                          |   |                 | 20           | 45           | μА       |

| $V_{UVI}$                | Undervoltage Lockout Exit Threshold                                               | V <sub>DCIN</sub> Increasing                                                                                          | • | 3.7             | 4            | 4.45         | V        |

| $\overline{V_{UVD}}$     | Undervoltage Lockout Entry Threshold                                              | V <sub>DCIN</sub> Decreasing                                                                                          | • | 3.4             | 3.7          | 4.1          | V        |

| $\overline{V_{UVH}}$     | Undervoltage Lockout Hysteresis                                                   |                                                                                                                       |   |                 | 400          |              | mV       |

| V <sub>DD</sub> Regula   | tor                                                                               |                                                                                                                       |   |                 |              |              |          |

| $\overline{V_{DD}}$      | Output Voltage                                                                    | No Load                                                                                                               | • | 4.5             | 4.75         | 5            | V        |

| $\overline{V_{DD(MIN)}}$ | Output Voltage                                                                    | $I_{DD} = -10$ mA                                                                                                     | • | 4.25            |              |              | V        |

| Charging P               | erformance                                                                        |                                                                                                                       |   |                 |              |              |          |

| V <sub>FTOL</sub>        | Charge Float Voltage Accuracy                                                     | 4.20V for Li-Ion. 2.35V for Lead Acid (Note 8) V <sub>CHG</sub> = GND                                                 |   | -0.5            |              | 0.5          | %        |

|                          |                                                                                   | -5°C < T <sub>A</sub> < 85°C (Note10)<br>-40°C < T <sub>A</sub> < 85°C                                                | • | −0.8<br>−1      |              | 0.8<br>1     | %<br>%   |

| V <sub>FATOL</sub>       | Charge Float Voltage Adjust Accuracy                                              | 0.3V and -0.3V for Li-Ion Batteries,<br>0.15V and -0.15V for Lead Acid Batteries<br>(Note 8)                          | • | -2              |              | 2            | %        |

| I <sub>BTOL</sub>        | Bulk Charge Current Accuracy (Note 7)                                             | $V_{CSP} - V_{CSN} = 100 \text{mV}$<br>$V_{BAT} \ge 3.1 \text{V}$<br>$-40^{\circ}\text{C} < T_A < 85^{\circ}\text{C}$ |   | -3<br>-         |              | 3            | %        |

|                          | Preconditioning and Wake-Up Current                                               | $V_{BAT} \ge 3.3V$ (Note 8), $V_{CSP} - V_{CSN} = 10$ mV;                                                             | • | _5<br>_30       |              | 5<br>30      | %        |

| I <sub>PTOL</sub>        | Accuracy (Note 7)                                                                 | Li-Ion and NiMH/NiCd Batteries Only                                                                                   |   | -30             |              | 30           | /0       |

|                          |                                                                                   | $V_{BAT} \le 3.3$ (Note 8), $V_{CSP} - V_{CSN} = 10$ mV; Li-Ion and NiMH/NiCd Batteries Only                          |   | <del>-4</del> 0 |              | 40           | %        |

| I <sub>SKVA</sub>        | Voltage Error Amplifier Sink Current at I <sub>TH</sub> Pin                       | V <sub>ITH</sub> = 2V                                                                                                 |   |                 | 96           |              | μA       |

| I <sub>SRCA</sub>        | Current Error Amplifier Source Current at I <sub>TH</sub><br>Pin                  | V <sub>ITH</sub> = 2V                                                                                                 |   |                 | -24          |              | μА       |

| I <sub>SKCA</sub>        | Current Error Amplifier Sink Current at I <sub>TH</sub> Pin                       | V <sub>ITH</sub> = 2V                                                                                                 |   |                 | 24           |              | μА       |

| I <sub>VCHG</sub>        | V <sub>CHG</sub> Pin Bias Current                                                 | V <sub>CHG</sub> = 1.25V                                                                                              |   | -100            |              | 100          | nA       |

| V <sub>BC</sub>          | Bulk Charge Threshold Voltage;<br>V <sub>BAT</sub> Increasing (Note 8)            | Li-Ion, V <sub>CHG</sub> = GND<br>NiMH/NiCd                                                                           |   | 2.80<br>0.84    | 3.00<br>0.90 | 3.20<br>0.96 | V        |

| V <sub>BCH</sub>         | Bulk Charge Threshold Voltage Hysteresis;<br>V <sub>BAT</sub> Decreasing (Note 8) | Li-Ion, V <sub>CHG</sub> = GND<br>NiMH/NiCd                                                                           |   |                 | 85<br>40     |              | mV<br>mV |

| V <sub>AR</sub>          | Auto Recharge Threshold Voltage;<br>V <sub>BAT</sub> Decreasing                   | Standard Li-Ion Only;<br>Specified as Percentage of Float Voltage                                                     |   | 93              | 95           | 97           | %        |

| V <sub>ARH</sub>         | Auto Recharge Threshold Hysteresis Voltage; V <sub>BAT</sub> Increasing           | Standard Li-Ion Only; Specified as<br>Percentage of Float Voltage                                                     |   |                 | 2            |              | %        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Unless otherwise specified,  $V_{DCIN} = V_{DCOUT} = V_{DCDIV} = 12V$ ,  $V_{BAT} = 8.4V$ , GND = SGND = CLP = CLN = SHDN = 0V and  $R_{VREF} = 49.9k$ . All currents into device pins are positive and all currents out of device pins are negative. All voltages are referenced to GND, unless otherwise specified.

| SYMBOL               | PARAMETER                                                                                           | CONDITIONS                                                                                                |   | MIN          | TYP            | MAX         | UNITS          |

|----------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---|--------------|----------------|-------------|----------------|

| V <sub>BOV</sub>     | Battery Overvoltage Threshold;<br>V <sub>BAT</sub> Increasing                                       | All Li-Ion, Lead Acid as Percentage of Float Voltage<br>NiMH/NiCd (Note 8)                                |   | 105<br>1.80  | 107.5<br>1.85  | 110<br>1.90 | %<br>V         |

| V <sub>BOVH</sub>    | Battery Overvoltage Threshold Hysteresis; V <sub>BAT</sub> Increasing.                              | All Li-Ion, Lead Acid as Percentage of Float Voltage<br>NiMH/NiCd (Note 8)                                |   |              | 2<br>40        |             | %<br>mV        |

| V <sub>REF</sub>     | Reference Pin Voltage Range                                                                         |                                                                                                           | • | 1.208        | 1.220          | 1.232       | V              |

| F <sub>TMR</sub>     | Programmed Timer Accuracy                                                                           | C <sub>TIMER</sub> = 47nF                                                                                 | • | -15          | 0              | 15          | %              |

| t <sub>TIMEOUT</sub> | Time Between Receiving Valid<br>ChargingCurrent() and ChargingVoltage()<br>Commands. Wake-Up Timer. |                                                                                                           | • | 140          | 175            | 210         | sec            |

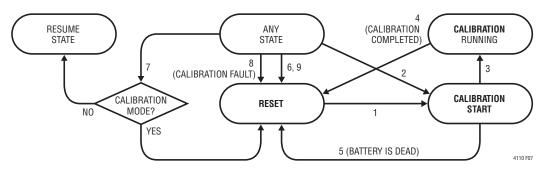

| Calibration          | Performance                                                                                         |                                                                                                           |   |              |                |             |                |

| V <sub>CTOL</sub>    | Calibration Cut-Off Default Voltage Accuracy; V <sub>BAT</sub> Decreasing                           | 2.75V for Li-lon, 1.93V for Lead Acid,<br>V <sub>CAL</sub> = GND (Note 8), 0.95V for NiMH/NiCd            | • | −1.1<br>−1.3 |                | 1.1<br>1.3  | %<br>%         |

| V <sub>CTOLH</sub>   | Calibration Cut-Off Default Voltage Hysteresis; $V_{\text{BAT}}$ Increasing. (Note 8)               | Li-lon<br>Lead Acid<br>NiMH/NiCd                                                                          |   |              | 85<br>50<br>40 |             | mV<br>mV<br>mV |

| V <sub>CATOL</sub>   | Calibration Cut-Off Voltage Adjust Accuracy                                                         | ±400mV for Li-lon, ±300mV for Lead Acid,<br>±200mV for NiMH/NiCd (Note 8)                                 | • | -1.5         |                | 1.5         | %              |

| I <sub>FTOL</sub>    | Calibration Current Accuracy (Note 7)                                                               | $V_{CSP} - V_{CSN} = -100 \text{mV}$                                                                      | • | <b>-</b> 5   |                | 5           | %              |

| I <sub>VCAL</sub>    | V <sub>CAL</sub> Pin Leakage Current                                                                | V <sub>CAL</sub> = 1.25V                                                                                  |   | -100         |                | 100         | nA             |

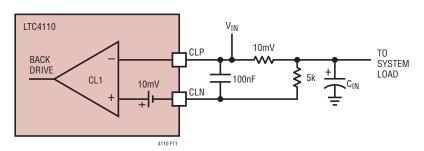

| I <sub>BDT</sub>     | Back-Drive Current Limit Threshold                                                                  | $V_{CLP} - V_{CLN}$ Decreasing $V_{CLN} = V_{DCIN}$                                                       | • | 7            | 10             | 13          | mV             |

| I <sub>BDH</sub>     | Back-Drive Current Limit Threshold Hysteresis                                                       | $V_{CLP} - V_{CLN}$ Increasing $V_{CLN} = V_{DCIN}$                                                       |   |              | 1              |             | mV             |

| V <sub>OVP</sub>     | Calibration Mode Input Overvoltage<br>Comparator DCDIV Pin Threshold                                | V <sub>DCDIV</sub> Rising                                                                                 | • | 1.4          | 1.5            | 1.6         | V              |

| V <sub>OVPH</sub>    | Calibration Mode Input Overvoltage<br>Comparator DCDIV Pin Hysteresis                               | V <sub>DCDIV</sub> Falling                                                                                |   |              | 100            |             | mV             |

| AC Present           | and Discharge Cut-Off Comparators                                                                   |                                                                                                           |   |              |                |             |                |

| V <sub>AC</sub>      | AC Present Comparator DCDIV Pin Threshold                                                           | V <sub>DCDIV</sub> Falling                                                                                | • | 1.196        | 1.22           | 1.244       | V              |

| V <sub>ACH</sub>     | AC Present Comparator DCDIV Pin Hysteresis                                                          | V <sub>DCDIV</sub> Rising                                                                                 |   |              | 50             |             | mV             |

| I <sub>AC</sub>      | AC Present Comparator DCDIV Pin Input Bias<br>Current                                               | V <sub>DCDIV</sub> = 1.25V                                                                                |   |              |                | 100         | nA             |

| t <sub>AC</sub>      | ACPb Pin Externally Programmed Falling Delay                                                        | C <sub>ACPDLY</sub> = 100nF, R <sub>VREF</sub> = 49.9k,<br>V <sub>DCDIV</sub> Stepped From 1.17V to 1.30V |   | 8            | 10             | 12          | ms             |

| V <sub>DTOL</sub>    | Discharge Cut-Off Default Voltage Accuracy; $V_{BAT}$ Decreasing                                    | 2.75V for Li-lon, 1.93V for Lead Acid,<br>V <sub>DIS</sub> = GND, 0.95V for NiMH/NiCd                     | • | -1.5         |                | 1.5         | %              |

| V <sub>DTOLH</sub>   | Discharge Cut-Off Default Voltage Hysteresis; V <sub>BAT</sub> Increasing (Note 8)                  | Li-lon<br>Lead acid<br>NiMH/NiCd                                                                          |   |              | 85<br>50<br>40 |             | mV<br>mV<br>mV |

| V <sub>DATOL</sub>   | Discharge Cut-Off Voltage Adjust Accuracy                                                           | ±400mV for Li-lon, ±300mV for Lead Acid,<br>±200mV for NiMH/NiCd                                          | • | 2            |                | 2           | %              |

| I <sub>VDIS</sub>    | V <sub>DIS</sub> Pin Bias Current                                                                   | V <sub>DIS</sub> = 1.25V                                                                                  |   | -100         | <u></u>        | 100         | nA             |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Unless otherwise specified,  $V_{DCIN} = V_{DCOUT} = V_{DCDIV} = 12V$ ,  $V_{BAT} = 8.4V$ , GND = SGND = CLP = CLN = SHDN = 0V and  $R_{VREF} = 49.9k$ . All currents into device pins are positive and all currents out of device pins are negative. All voltages are referenced to GND, unless otherwise specified.

| SYMBOL                                    | PARAMETER                                                                                                        | CONDITIONS                                                                                                                                                          |   | MIN                        | TYP                        | MAX                               | UNITS    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|----------------------------|-----------------------------------|----------|

| Input and B                               | Battery Ideal Diodes and Switches                                                                                |                                                                                                                                                                     |   |                            |                            |                                   |          |

| V <sub>FR</sub>                           | Forward Regulation Voltage (V <sub>DCIN</sub> -V <sub>DCOUT</sub> , V <sub>BAT</sub> -V <sub>DCOUT</sub> )       | 2.7V ≤ V <sub>DCIN</sub> ≤ 19V                                                                                                                                      | • | 10                         | 20                         | 32                                | mV       |

| V <sub>REV</sub>                          | Reverse Voltage Turn-Off Voltage (V <sub>DCIN</sub> -V <sub>DCOUT</sub> , V <sub>BAT</sub> -V <sub>DCOUT</sub> ) | $2.7V \le V_{DCIN} \le 19V$                                                                                                                                         | • | -30                        | -18                        | -8                                | mV       |

| $V_{GON}$                                 | "ON" Gate Clamping Voltage (V <sub>DCIN</sub> -V <sub>INID</sub> , V <sub>BAT</sub> -V <sub>BATID</sub> )        | $I_{INID}$ , $I_{BATID} = 1\mu A$                                                                                                                                   |   | 7                          | 8.3                        | 9.7                               | V        |

| V <sub>GOFF</sub>                         | "OFF" Gate Voltage (V <sub>DCIN</sub> -V <sub>INID</sub> , V <sub>BAT</sub> -V <sub>BATID</sub> )                | $I_{INID}$ , $I_{BATID} = -10\mu A$<br>$V_{SHDN} = 0V$ and $V_{DCIN}$ (Shutdown)                                                                                    |   |                            |                            | 0.25                              | V        |

| $V_{FO}$                                  | BATID Fast-On Voltage Comparator Threshold                                                                       | I <sub>BATID</sub> > 500μA                                                                                                                                          |   | 45                         |                            | 100                               | mV       |

| t <sub>IIDON</sub><br>t <sub>IIDOFF</sub> | INID Pin Delay Times  Turn "ON" Turn "OFF"                                                                       | C <sub>INID</sub> = 10nF<br>DCIN is Switched Between 12.2V and 11.8V<br>From DCOUT – V <sub>GOFF</sub> to DCOUT –6V<br>From DCOUT – V <sub>GON</sub> to DCOUT –1.5V |   |                            | 450<br>8                   | 700<br>20                         | μs<br>μs |

| t <sub>BIDON</sub>                        | BATID Pin Delay Times  Turn "ON" Turn "OFF"                                                                      | C <sub>BATID</sub> = 2.5nF BAT is Switched Between 12.2V and 11.8V From DCOUT - V <sub>GOFF</sub> to DCOUT -6V From DCOUT - V <sub>GON</sub> to DCOUT -1.5V         |   |                            | 15<br>8                    | 60<br>20                          | μs<br>μs |

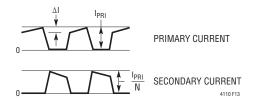

| PWM Flyba                                 | ack Converter                                                                                                    |                                                                                                                                                                     |   |                            |                            |                                   |          |

| V <sub>OHF</sub>                          | CHGFET, DCHFET High                                                                                              | I <sub>CHGFET</sub> , I <sub>DCHFET</sub> = -1mA                                                                                                                    |   | 4.5                        | 4.75                       | 5.25                              | V        |

| $V_{OLF}$                                 | CHGFET, DCHFET Low                                                                                               | I <sub>CHGFET</sub> , I <sub>DCHFET</sub> = 1mA                                                                                                                     |   |                            |                            | 50                                | mV       |

| V <sub>OLFX</sub>                         | CHGFET, DCHFET in Shutdown and Backup<br>Modes                                                                   | $V_{DCIN} = V_{DCDIV} = V_{DCOUT} = 0V$ (Shutdown Mode), $V_{DCIN} = V_{DCDIV} = 0V$ (Backup Mode) $I_{CHGFET}$ , $I_{DCHFET} = 1\mu A$                             |   |                            |                            | 100                               | mV       |

| t <sub>R</sub><br>t <sub>F</sub>          | CHGFET, DCHFET Transition Times Rise Time Fall Time                                                              | C <sub>LOAD</sub> = 1.6nF, 20% to 80%<br>C <sub>LOAD</sub> = 1.6nF, 20% to 80%                                                                                      |   |                            | 35<br>15                   | 65<br>65                          | ns<br>ns |

| F <sub>PWM</sub>                          | PWM Oscillator Switching Frequency                                                                               |                                                                                                                                                                     | • | 255                        | 300                        | 340                               | kHz      |

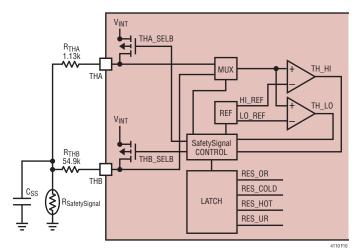

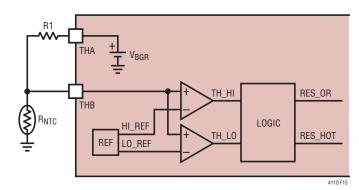

| SafetySign                                | al Decoder and Thermistor Interface                                                                              |                                                                                                                                                                     |   |                            |                            |                                   |          |

| SS <sub>OR</sub>                          | SafetySignal Decoder<br>SafetySignal Trip<br>(RES_COLD/RES_OR)                                                   | $R_{THA}$ = 1130 $\Omega$ ±1%, $C_{TH}$ = 1nF (Note 6) $R_{THB}$ = 54.9k ±1%.<br>Smart Batteries and Li-lon Only                                                    | • | 95                         | 100                        | 105                               | k        |

| SS <sub>CLD</sub>                         | SafetySignal Decoder<br>SafetySignal Trip<br>(RES_IDEAL/RES_COLD)                                                | $R_{THA}$ = 1130 $\Omega$ ±1%, $C_{TH}$ = 1nF (Note 6) $R_{THB}$ = 54.9k ±1% Smart Batteries and Li-lon Only                                                        | • | 28.5                       | 30                         | 31.5                              | k        |

| SS <sub>IDL</sub>                         | SafetySignal Decoder<br>SafetySignal Trip<br>(RES_HOT/RES_IDEAL)                                                 | $R_{THA}$ = 1130 $\Omega$ ±1%, $C_{TH}$ = 1nF (Note 6) $R_{THB}$ = 54.9k ±1% Smart Batteries and Li-lon Only                                                        | • | 2.85                       | 3                          | 3.15                              | k        |

| SS <sub>HOT</sub>                         | SafetySignal Decoder<br>SafetySignal Trip<br>(RES_UR/RES_HOT)                                                    | $R_{THA}$ = 1130 $\Omega$ ±1%, $C_{TH}$ = 1nF (Note 6) $R_{THB}$ = 54.9k ±1% Smart Batteries and Li-Ion Only                                                        | • | 425                        | 500                        | 575                               | Ω        |

| V <sub>HOT</sub>                          | THB Pin Hot Threshold Voltage                                                                                    | V <sub>THB</sub> Decreasing; Lead Acid Only                                                                                                                         | • | 0.28 •<br>V <sub>THA</sub> | 0.30 •<br>V <sub>THA</sub> | 0.36 <b>•</b><br>V <sub>THA</sub> | V        |

| V <sub>HOTH</sub>                         | THB Pin Hot Threshold Hysteresis Voltage                                                                         | V <sub>THB</sub> Increasing; Lead Acid Only                                                                                                                         |   |                            | 50                         |                                   | m۷       |

| V <sub>REM</sub>                          | THB Pin Battery Removal Threshold Voltage                                                                        | V <sub>THB</sub> Increasing; Lead Acid Only                                                                                                                         | • | 0.90 •<br>V <sub>THA</sub> | 0.94 •<br>V <sub>THA</sub> | 0.96 <b>•</b><br>V <sub>THA</sub> | V        |

## LTC4110

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Unless otherwise specified,  $V_{DCIN} = V_{DCOUT} = V_{DCDIV} = 12V$ ,  $V_{BAT} = 8.4V$ , GND = SGND = CLP = CLN = SHDN = OV and  $R_{VREF} = 49.9k$ . All currents into device pins are positive and all currents out of device pins are negative. All voltages are referenced to GND, unless otherwise specified.

| SYMBOL                | PARAMETER                                                    | CONDITIONS                                                                              |   | MIN  | TYP | MAX | UNITS |

|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|---|------|-----|-----|-------|

| V <sub>REMH</sub>     | THB Pin Battery Removal Threshold<br>Hysteresis Voltage      | V <sub>THB</sub> Decreasing; Lead Acid Only                                             |   |      | 25  |     | mV    |

| Logic and             | Status Output Levels                                         |                                                                                         |   |      |     |     |       |

| V <sub>ILS</sub>      | SCL/SDA Input Pins Low Voltage                               |                                                                                         | • |      |     | 0.8 | V     |

| $\overline{V_{IHS}}$  | SCL/SDA Input Pins High Voltage                              |                                                                                         | • | 2.1  |     |     | V     |

| $V_{OLS}$             | SDA Output Pin Low Voltage                                   | I <sub>PULL-UP</sub> = 350μA                                                            | • |      |     | 0.4 | V     |

| $\overline{V_{OLG}}$  | ACPb, GPI01,2,3 Output Pins Low Voltage                      | I <sub>ACPb</sub> , I <sub>GPIO1</sub> , I <sub>GPIO2</sub> , I <sub>GPIO3</sub> = 10mA |   |      |     | 1   | V     |

| I <sub>OHG</sub>      | ACPb, GPI01,2,3 Output Pins Open<br>Leakage Current          | Outputs Open, V <sub>ACPb</sub> , V <sub>GPIO1,2,3</sub> = 5V                           |   | -2   |     | 2   | μА    |

| $V_{ILG}$             | GPIO Input Low Voltage                                       |                                                                                         | • |      |     | 1   | V     |

| $\overline{V_{IHG}}$  | GPIO Input High Voltage                                      |                                                                                         | • | 1.5  |     |     | V     |

| $V_{ILSD}$            | SHDN Input Pin Low Voltage                                   |                                                                                         |   |      |     | 0.5 | V     |

| $\overline{V_{IHSD}}$ | SHDN Input Pin High Voltage                                  |                                                                                         |   | 2.4  |     |     | V     |

| I <sub>ISD</sub>      | SHDN Input Pin Pull-Up Current                               | V <sub>SHDN</sub> = 2.4V                                                                |   | -3.5 | -2  | -1  | μА    |

| T <sub>LR</sub>       | Logic Reset Duration After Power-Up<br>From Zero             | V <sub>DCIN</sub> Transition From 0V to 5V in <1ms;<br>V <sub>BAT</sub> = 0             |   |      |     | 1   | S     |

| SMBus Tim             | ning (Note 9)                                                |                                                                                         |   |      |     |     |       |

| t <sub>HIGH</sub>     | SCL Serial Clock High Period                                 | I <sub>PULL-UP</sub> = 350µA, C <sub>LOAD</sub> = 250pF,<br>R <sub>PU</sub> = 9.31k     | • | 4    |     |     | μs    |

| t <sub>LOW</sub>      | SCL Serial Clock Low Period                                  | I <sub>PULL-UP</sub> = 350µA, C <sub>LOAD</sub> = 250pF,<br>R <sub>PU</sub> = 9.31k     | • | 4.7  |     |     | μs    |

| t <sub>TO</sub>       | Timeout Period                                               |                                                                                         | • | 25   |     |     | ms    |

| t <sub>F</sub>        | SDA/SCL Fall Time                                            | C <sub>LOAD</sub> = 250pF, R <sub>PU</sub> = 9.31k                                      | • |      |     | 300 | ns    |

| t <sub>SU-STA</sub>   | Start Condition Set-Up Time                                  |                                                                                         | • | 4.7  |     |     | μs    |

| t <sub>HD-STA</sub>   | Start Condition Hold Time                                    |                                                                                         | • | 4    |     |     | μs    |

| t <sub>HD-DAT</sub>   | SDA to SCL Falling-Edge Hold Time,<br>Slave Clocking in Data |                                                                                         | • | 300  |     |     | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. Specific functionality or parametric performance of the device beyond the limits expressly given in the Electrical Characteristics table is not implied by these maximum ratings.

**Note 2:** The LTC4110E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Overtemperature protection will become active at a junction temperature greater than the maximum operating junction temperature. Continuous operation above the specified maximum operation temperature may result in device degradation or failure. Operating junction temperature  $T_J$  (in °C) is calculated from the ambient temperature  $T_A$  and the average power dissipation  $P_D$  (in watts) by the formula  $T_J = T_A + \theta_{JA} \cdot P_D$ .

**Note 4:** The LTC4110 is idle with no application load. It is not charging or calibrating the battery and is not in backup or shutdown mode. The internal clock is running and the SMBus is functional.

Note 5: Combined current of CSP, CSN and BAT pins set to  $V_{\text{BAT}}$  with no application load.

**Note 6:**  $C_{TH}$  is defined as the sum of capacitance on THA, THB SafetySignal.

**Note 7:** Does not include tolerance of current sense or current programming resistors.

Note 8: Given as a per cell voltage referred to the BAT pin ( $V_{BAT}$ /number of series cells).

**Note 9:** Refer to System Management Bus Specification, Revision 1.1, section 2.1 for Timing Diagrams and section 8.1, for  $t_{LOW}$  and  $t_{TIMEOUT}$  requirements

**Note 10:** Specifications over the -5°C to 85°C operating ambient temperature range are assured by design, characterization and correlation with statistical process controls.

## TYPICAL PERFORMANCE CHARACTERISTICS

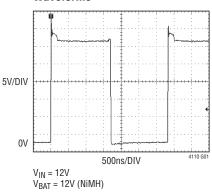

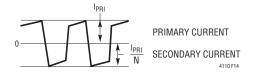

# Typical CHGFET and DCHFET Waveforms

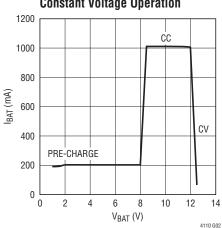

#### Output Charging Characteristics Showing Constant Current and Constant Voltage Operation

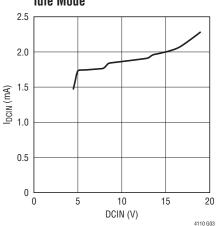

# Supply Current vs DCIN Voltage in Idle Mode

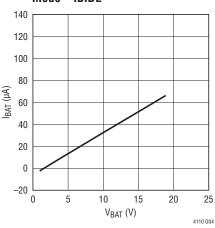

#### Battery Leakage in Idle Mode – IBIDL

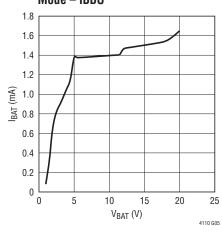

#### Battery Current in Backup Mode – IBBU

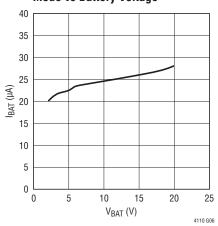

Battery Leakage in Shutdown Mode vs Battery Voltage

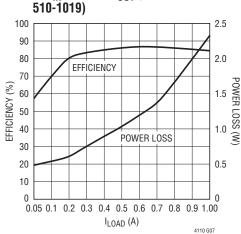

# Charging Efficiency/Power Loss, 12V<sub>IN</sub> and 12.6V<sub>OUT</sub> (Xfmr = BH 510-1019)

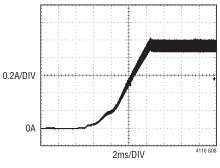

#### **Soft-Start Waveform**

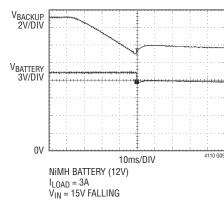

#### Backup Mode On and Off Waveform

## PIN FUNCTIONS

**DCIN (Pin 1):** External DC Power Sense Input. Provides a control input and supply for the main supply ideal diode function.

**CLN (Pin 2):** Current Limit Sense Negative Input. See CLP pin.

**CLP (Pin 3):** Current Limit Sense Positive Input. This pin and the CLN pin form a differential input that senses voltage on an external resistor for reverse current entering the power source while in low loss calibration mode. Should the current approach reversal, this function will terminate calibration. An RC filter may be required to filter out system load noise. Connect both CLP and CLN pins to GND to disable this function. A differential voltage of >1V between the CLP and CLN pins may damage the device.

**ACPDLY (Pin 4):** ACPb Delay Control Pin. A capacitor connected from ACPDLY to GND and a resistor from V<sub>REF</sub> to GND programs delay in the ACPb pin high-to-low transition. Open if minimum delay is desired.

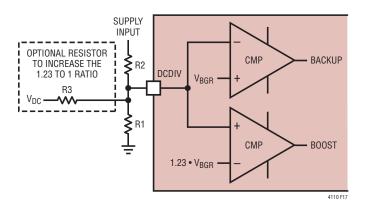

**DCDIV** (**Pin 5**): AC Present Detection Input. Backup operation is invoked when the system power voltage, divided by an external resistor divider, falls below the threshold of this pin.

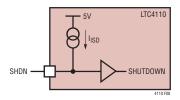

**SHDN (Pin 6):** Active High Shutdown/Reset Control Logic Input. Forces micropower shutdown mode if high when DCIN supply is removed. Forces all registers to reset if high when DCIN supply is present. Normally tied to ground. Internal pin pull-up current.

**SDA (Pin 7):** SMBus Bidirectional Data Signal. Connect to  $V_{DD}$  when not in use.

**SCL (Pin 8):** SMBus Clock Signal Input From SMBus Host. Connect to  $V_{DD}$  when not in use.

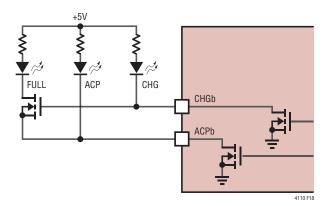

**GPIO1 (Pin 9):** General Purpose I/O or Charge Status Pin. A logic-level I/O bit port that is configurable as a host-driven input/output port or as a battery charge status output (CHGb) with an open-drain N-MOSFET that is asserted low when any

smart battery or Li-Ion battery is in any phase of charging or when lead acid battery charge current is >C/x where:

$$X = \frac{C}{I_{CHG}} \bullet 5$$

(See C/x Charge Termination section for more details). If the No SMBus option is selected with the SELA pin, the GPIO1 pin defaults as battery charge status. Refer to Table 5a.

**GPI02 (Pin 10):** General Purpose I/O Pin. A logic-level I/O bit port that is configurable as a host-driven input/output port or as a battery undervoltage status output (BKUP\_FLTb) with an open-drain N-MOSFET that is asserted low only while in backup mode if the battery's average cell voltage drops below voltage programmed by the V<sub>DIS</sub> pin. If the No SMBus option is selected with the SELA pin, then the GPI02 pin defaults as battery undervoltage status. Refer to Table 5c.

**GPIO3 (Pin 11):** General Purpose I/O Pin. A logic-level I/O bit port that is configurable as a host-driven input/output port or as a calibration complete status output (CAL\_COM-PLETEb) with an open-drain N-MOSFET that is asserted low when calibration has been completed. If the SELA pin is programmed for no SMBus use then the status output is charge fault (CHGFLTb) instead of calibration complete. Refer to Table 5e.

**SELA (Pin 12):** SMBus Address Selection Input. Selects the LTC4110 SMBus address to facilitate redundant backup systems when standard batteries are used. Connect to GND for 12h,  $V_{DD}$  for 28h and the  $V_{REF}$  pin for 20h. When a smart battery is selected by the TYPE pin, the SELA pin must be connected to GND to select address 12h. If the SMBus is not used or to force all GPIOs to status mode upon power-up, connect pin to a typically 0.5 •  $V_{REF}$  voltage from  $V_{REF}$  pin resistor divider. The SMBus address, if used, will be 12h.

## PIN FUNCTIONS

**ACPb (Pin 13):** AC Present Status Digital Output. Open-Drain N-MOSFET output is asserted low when the main supply is present as detected by the DCDIV pin and internal DCIN UVLO.

$m V_{DIS}$  (Pin 14): Battery Discharge Voltage Limit During Backup Program Input. Battery threshold voltage at which backup mode will terminate by turning off the isolation P-MOSFET with the BATID pin. Adjustable from external resistor string biased from  $\rm V_{REF}$  pin. For default threshold connect to GND pin.

**V<sub>CAL</sub>** (**Pin 15**): Battery Voltage Limit During Calibration Program Input. Battery threshold voltage at which calibration will terminate. Adjustable from external resistor string biased from V<sub>REF</sub> pin. For default threshold connect to GND pin.

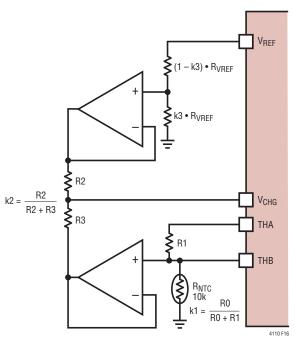

$V_{CHG}$  (Pin 16): Battery Float Voltage Program Input. Trims the float voltage during charging. Programmed from external resistor string biased from  $V_{REF}$  pin. Connect to GND for default float voltage.

$V_{REF}$  (Pin 17): Voltage Reference Output and Timing Programming Input. Provides a typical virtual reference of 1.220V ( $V_{REF}$ ) for an external resistor divider tied between this pin and GND that programs the  $V_{CHG}$ ,  $V_{CAL}$  and  $V_{DIS}$  pin functions. Total resistance from  $V_{REF}$  to GND, along with the capacitor on the timer pin, programs the charge time. Voltage reference output remains active in all modes except shutdown. Load current must be between  $10\mu A$  and  $25\mu A$ .

**TIMER (Pin 18):** Charge Timing Input. A capacitor connected between TIMER and GND along with the resistance connected from  $V_{REF}$  to GND programs the charge time intervals.

TYPE (Pin 19): Refer to Table 8.

**THA (Pin 20):** SafetySignal Force/Sense Pin to Smart Battery and Force Pin to Lead Acid Battery Thermistor. See description of operation for more detail. The maximum allowed combined capacitance on THA, THB and SafetySignal is 1nF. For lead acid battery applications the maximum capacitance on the THA pin is 50pF.

**THB (Pin 21):** SafetySignal Force/Sense Pin to Smart Battery and Sense Pin to Lead Acid Battery Thermistor. See description of operation for more detail. The maximum allowed combined capacitance on THA, THB and SafetySignal is 1nF.

**IPCC** (Pin 22): Battery Preconditioning Charge Current Program Input. Programs the battery current during preconditioning or wakeup charging. Programmed from external resistor to GND.

**I**<sub>CAL</sub> (**Pin 23**): Battery Discharge Current During Calibration Program Input. Programs the constant discharge current at the battery during calibration. Programmed from external resistor to GND.

**I**<sub>CHG</sub> (**Pin 24**): Battery Current During Charge Program Input. Programs the battery current while constant-current bulk charging. Programmed from external resistor to GND.

**I**<sub>TH</sub> (**Pin 25**): Control Signal of the Current Mode PWM. AC compensates control loop. Higher I<sub>TH</sub> voltage corresponds to higher charging current.

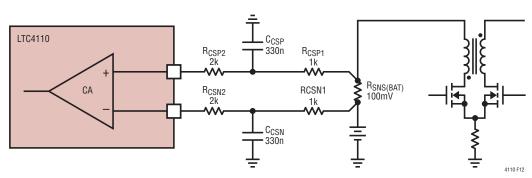

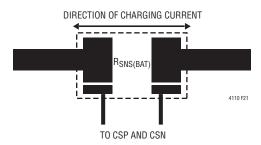

**CSP** (Pin 26): Current Sense Positive Input. This pin and the CSN pin measure voltage across the external current sense resistor to control battery current during charging and calibration.

**CSN (Pin 27):** Current Sense Negative Input. This pin and the CSP pin measure voltage across the external current sense resistor to control battery current during charging and calibration.

**SGND (Pin 28):** Signal Ground Reference Input. This pin should be Kelvin connected to the flyback current sense resistor and to the battery return.

**I**SENSE (Pin 29): Current Sense Input. Senses current in the flyback transformer by monitoring voltage across the external current sense resistor. This pin should be Kelvinconnected to the resistor.

**SELC (Pin 30):** Refer to Table 8.

## PIN FUNCTIONS

**BAT (Pin 31):** Battery Voltage Sense Input. This pin is used to monitor the battery and control charging voltage through an internal resistor divider connected to this pin that is disconnected in shutdown mode. Also provides a control input for battery ideal diode functions. Pin should be Kelvinconnected to battery to avoid voltage drop errors.

**DCHFET (Pin 32):** Drives the Gate of an External N-MOSFET. Used to drive energy into the battery side of the high efficiency switch mode converter during low loss calibration discharge of the battery. Provides synchronous rectification during battery charging.

**CHGFET (Pin 33):** Drives the Gate of an External N-MOSFET. Used to drive energy into the supply side of the high efficiency switch mode converter during battery charging. Provides synchronous rectification during low loss calibration mode.

$V_{DD}$  (Pin 34): Bypass Capacitor Connection for Internal  $V_{DD}$  Regulator. Bypass at pin with 100nF low ESR capacitor to GND.

**BATID (Pin 35):** Drives the Gate of the Battery P-MOSFET Ideal Diode. Controls low loss ideal diode between the battery and backup load when in backup mode. When not in backup mode, the P-MOSFET is turned off to prevent battery power from back driving into main power.

NC (Pin 36): No Connect.

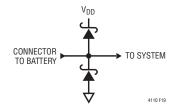

**DCOUT (Pin 37):** System Power Output Voltage Monitor Input. Provides a control input for supply input ideal diode and battery ideal diode functions. Also supplies power to the IC. Bypass at pin with 100nF low ESR capacitor to GND.

**INID (Pin 38):** Drives the Gate of the Supply Input P-MOSFET Ideal Diode. Controls low loss ideal diode between the supply input and backup load when not in backup mode.

**Exposed Pad (Pin 39):** Ground. The Exposed Pad must be soldered to the PCB.

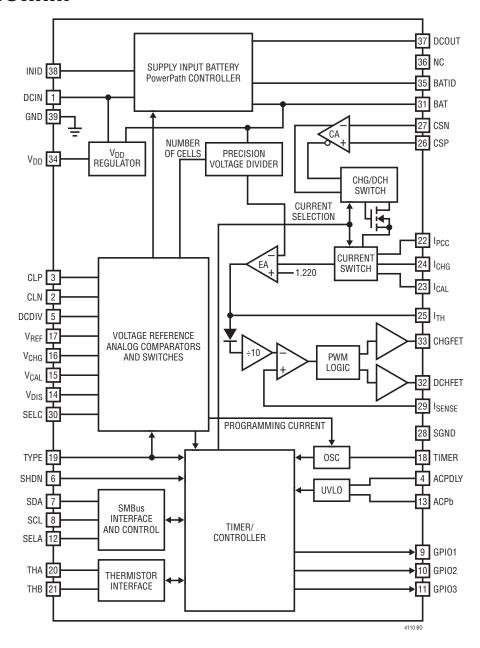

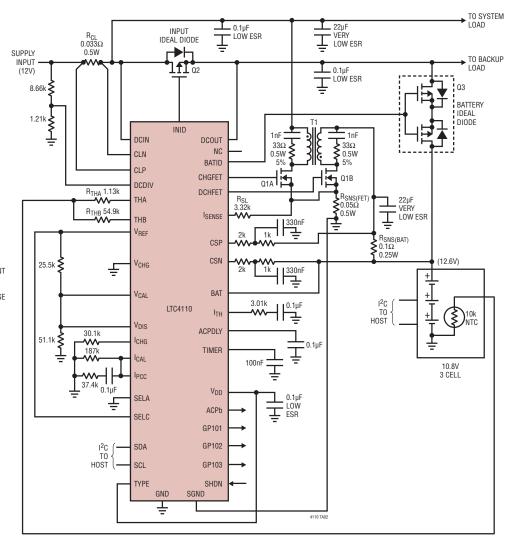

## **BLOCK DIAGRAM**

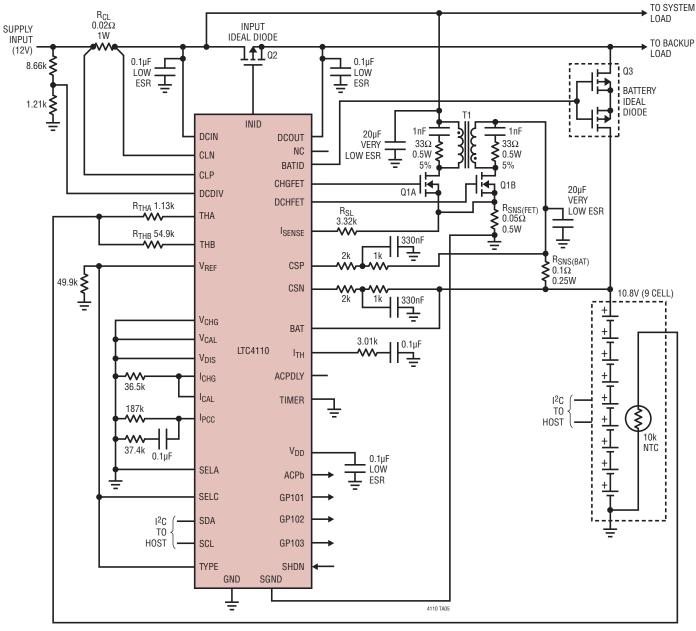

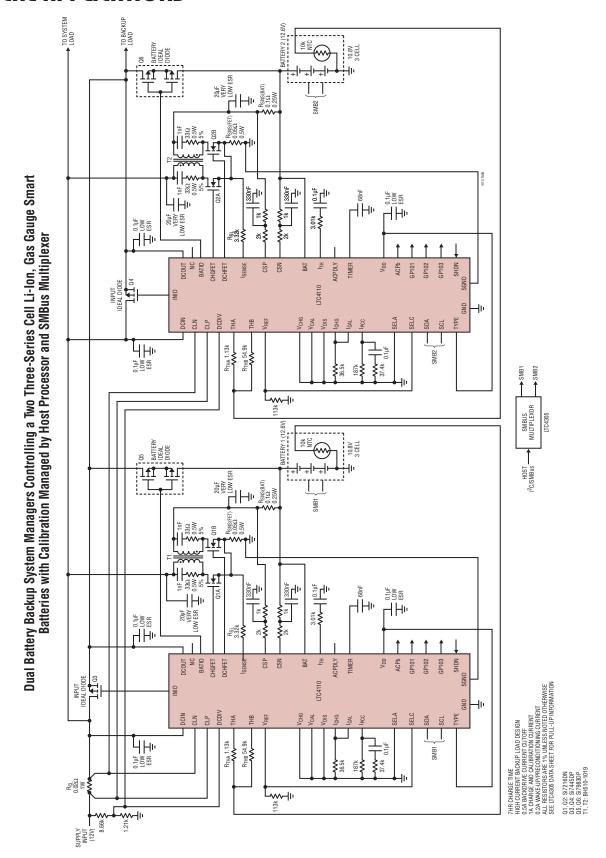

#### **OVERVIEW**

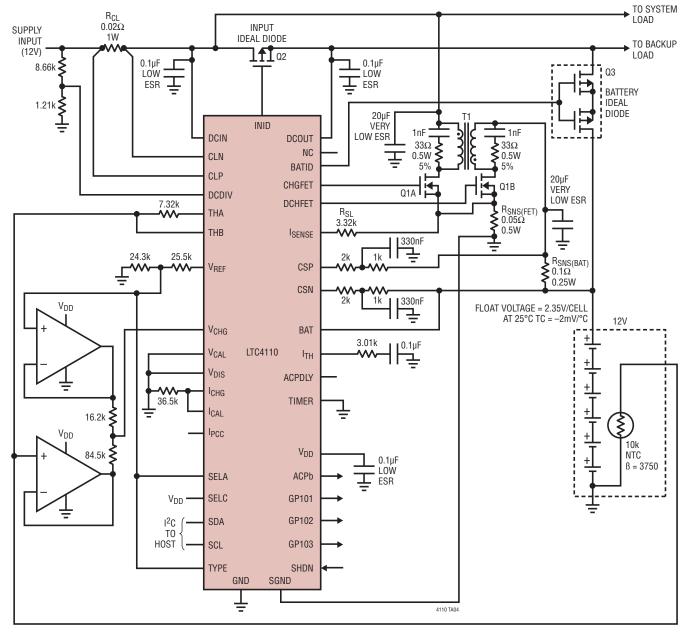

In the typical application, the LTC4110 is placed in series with main power supply that powers all or part of the system, which must include the device(s) or system that needs battery backup.

The LTC4110 has four modes of operation:

- · Battery Backup Mode

- Battery Charge Mode

- Battery Calibration Mode

- Shutdown Mode

The LTC4110 provides complete PowerPath control for the battery backed up load switching automatically from the main power supply to the battery when battery backup mode is required. Low loss ideal diode FET switches are used to connect the main supply or the battery to the backup load which permit multiple LTC4110's to work together in a scalable fashion to permit longer backup times, redundancy and/or higher load currents. In battery charge mode, power is drawn from the main supply by a high efficiency synchronous flyback charger. The LTC4110 maintains the state of charge (SOC) of the battery at all times so the battery is ready at all times. Use of a flyback converter permits charging of batteries who's termination voltage can be greater than the main supply voltage, while at the same time providing high DC isolation to minimize parasitic drain on the battery. Testing, maintenance support and capacity verification of the battery is supported through the LTC4110's calibration mode. In calibration mode, the same synchronous flyback used to charge the battery is also used in reverse to allow safe controlled discharge of the battery back into the main supply eliminating wasted heat and energy. The product will not need to provide any additional thermal management to support this mode. Shutdown mode disconnects the battery from the load to preserve capacity and permits shipping the product with an energized battery installed at the factory, eliminating battery installation at the site. The LTC4110 supports optional control and monitoring of all activities by a host including faults over the industry standard SMBus, which is a variation of the I<sup>2</sup>C bus. However no host is required as the LTC4110 is fully functional in a standalone mode. Combining all these functions into a single IC reduces circuit area compared to presently available solutions.

The LTC4110 is designed to work with both standard battery and smart battery configurations. Smart batteries are standard batteries with industry standard gas gauge electronics built in offering accurate SOC information for the host. Furthermore, being intimate with all aspects of the battery, it also has the ability to control the charge process. Smart batteries use the SMBus as the communication bus for data exchange and charge control. For more information about smart batteries, see www. sbs-forum.org for specifications or contact Linear Technology Applications.

It is important to know that the LTC4110 uses the TYPE pin to learn what type of battery it will be working with. The TYPE pin setting globally affects all of the operating modes, options including GPIO and control ranges. Table 1 and Table 2 give you a complete breakdown of all the battery types supported relative to the TYPE pin settings

Table 1. LTC4110 Battery Pack Charge Mode Capabilities

| BATTERY TYPE     |                | CHEMISTRY |               | MAXIMUM CHARGE TIME (SLA EXCLUDED) |

|------------------|----------------|-----------|---------------|------------------------------------|

|                  | Li-lon/Polymer | Nickel    | SLA/Lead Acid |                                    |

| Standard Battery | Yes            | No        | Yes           | Adj. Up to 12 Hours                |

| Smart Battery    | Yes            | Yes       | Yes           | Unlimited                          |

Table 2. LTC4110 Battery Pack Charge Voltage Capabilities

| CHEMISTRY      | V <sub>CELL</sub> FULL CHARGE | V <sub>CELL</sub> ADJ. RANGE | SERIES CELL COUNT | NOMINAL STACK VOLTAGE (V) |

|----------------|-------------------------------|------------------------------|-------------------|---------------------------|

| Lead Acid      | 2.35V                         | ±0.15V                       | 2, 3, 5 and 6     | 4, 6, 10 and 12           |

| Li-Ion/Polymer | 4.2V                          | ±0.3V                        | 1, 2, 3 and 4     | 3.6, 7.2, 10.8 and 14.4   |

| NiMH/NiCd      | N/A                           | N/A                          | 4, 6, 9 and 10    | 4.8, 7.2, 10.8 and 12     |

| Super Caps     | 2.5V, 2.7V or 3V              | Yes                          | 2 to 7            | 5 to 18                   |

and ranges. It should be noted that even if the LTC4110 TYPE pin is not set to a smart battery mode, any SMBus commands sent by a host or a smart battery are still acted upon. For SuperCap support, see the Applications Information section.

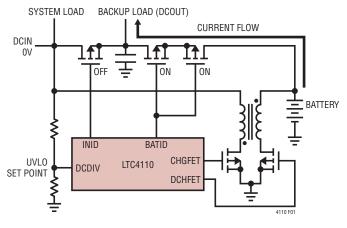

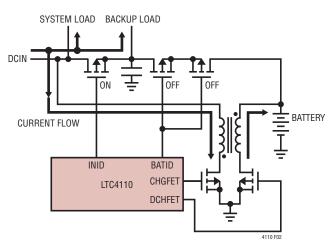

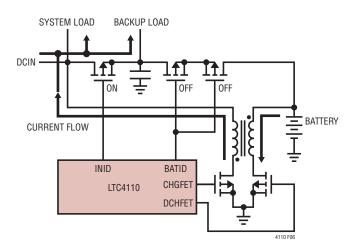

#### **BATTERY BACKUP MODE**

Figure 1 shows the LTC4110 in backup mode and the corresponding PowerPath enabled. The LTC4110 use the DCDIV pin to typically monitor the DCIN voltage through an external resistor divider. The DCDIV pin sets the backup mode threshold voltage and senses the need to enter backup mode. DCDIV can alternately be driven with other signals such as logic. When the DCDIV pin voltage drops below the AC present threshold voltage (see V<sub>AC</sub>) backup mode is entered. Backup mode is also entered whenever the internal undervoltage lockout, UVLO, senses that DCIN  $(V_{UVD})$  or DCOUT has fallen to excessively low voltages. In backup mode the battery P-MOSFET ideal diode is enabled to backup the load from the battery. The supply input P-MOSFET ideal diode isolates the main supply input from the load and the flyback switcher N-MOSFETs are inhibited from turning on. Also, after the threshold is passed, hysteresis (V<sub>ACH</sub>) is switched in. When the supply is returning and the AC present threshold voltage plus the hysteresis voltage is reached on the DCDIV pin, both of the battery P-MOSFETs are rapidly switched off (t<sub>dDOFF</sub>) and the supply input P-MOSFET ideal diode provides the load current. When forward biased, the ideal diodes regulate their forward voltage drop to 20mV typical (V<sub>FR</sub>) when the

Figure 1. Backup Mode Operation

MOSFET is sufficiently sized. If the voltage input falls and results in a forward voltage below 20mV, then the ideal diode will begin turning off at a slow rate. Should the ideal diode see a -18mV typical ( $V_{REV}$ ) or lower reverse voltage, the ideal diode will turn off quickly ( $t_{dDOFE}$ ).

While in backup, the battery's average cell voltage is monitored to protect the battery from excessive discharge. If the cell voltage drops below the value programmed by the V<sub>DIS</sub> pin (Li-Ion default = 2.75V/cell, NiMH/NiCd default = 0.95V/cell, lead acid default = 1.93V/cell), the battery P-MOSFETs are rapidly turned off and the battery is disconnected from the load. If DCIN is above UVLO, the load and the LTC4110 will be powered from the supply input. If DCIN is below UVLO, the LTC4110 enters the micropower shutdown mode (see the Shutdown Mode section for more details). Also, the SMBus accessible BKUP FLT fault bit is set and maintained as long as sufficient battery voltage is present ( $V_{BAT} \ge 2.7V$ ). This fault bit can be read after DCIN returns to a voltage level exceeding the internal UVLO threshold (see V<sub>IIVI</sub>) and DCOUT has regained sufficient voltage (see DCOUT) to provide internal power. If the GPIO2 port is programmed as the BKUP FLTb status output after DCIN returns, it will be forced low to represent an inverted BKUP\_FLT bit. When DCIN returns, as sensed by the UVLO, the shutdown mode is automatically cancelled and normal operation can resume, however, the BKUP\_FLT bit remains set until either the SHDN pin is set high (all registers reset) or register bits POR RESET or BUFLT\_RST are set. See the Shutdown Mode section for details. During backup, the external thermistor network is monitored for battery presence.

#### **BATTERY CHARGE MODE**

Figure 2 shows the charge path to charge a battery. Current is pulled from the supply input to charge the battery. At the same time, the input supply provides power to both the system load and the backup load. The battery is isolated from the load at all times so it cannot affect charger terminations algorithms.

If we ignore battery chemistry for a moment, as far as the LTC4110 charger is concerned, there are only two basic charge modes. When the TYPE pin selects a standard battery mode, charge termination is controlled by the LTC4110

Figure 2. Charge Mode Operation

for the battery chemistry selected. Specifically the TIMER pin becomes active and used to detect faults conditions or terminate the charge cycle itself as needed. Smart battery SMBus charge control commands are still honored if any are sent at any time. A smart battery can safely function in a standard battery mode if identical in chemistry and voltage configuration as the standard battery. When the TYPE pin selects a smart battery mode, this simply disables the TIMER pin and its function in charge termination. The smart battery is able to restart or terminate a charge cycle at any time using charge commands over the SMBus. This mode also enables smart battery wake-up and watchdog functions based on t<sub>TIMEOUT</sub> per the smart battery standards. However it is not recommended to use a standard battery with a LTC4110 configured for smart battery mode operation. You can shorten battery life, damage or destroy the battery. In the extreme case this can cause an explosion since no charge termination mechanisms are active.

The following sections explain detailed operation for each charge mode as selected by the TYPE pin.

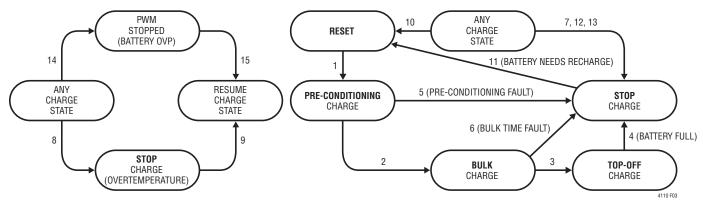

#### STANDARD LI-ION/POLYMER BATTERY CHARGE MODE

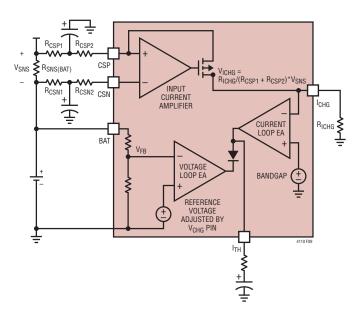

The charger is programmed for standard Li-Ion batteries by connecting the TYPE pin to GND. During Li-Ion charging, the LTC4110 operates as a high efficiency, synchronous, PWM flyback battery charger with constant-current and constant float voltage regions of operation. The constant-charge current is programmed by the combination of a resistor (R<sub>CHG</sub>) from the I<sub>CHG</sub> pin to ground, a battery

current sense resistor ( $R_{SNS(BAT)}$ ) and CSP/CSN pin resistors. The constant voltage (float voltage) is programmed to one of four values (4.2V, 8.4V, 12.6V, 16.8V) depending on the number of series cells using the SELC pin and can be adjusted  $\pm 0.3$ V/cell with the  $V_{CHG}$  pin. If adjusted, the auto recharge threshold and overvoltage threshold will track proportionally.

The charge cycle begins when the supply input is present as sensed by the DCDIV pin and DCIN above UVLO, the battery cell voltage is below the auto recharge threshold (95% of the programmed float voltage; see  $V_{AR}$ ), thermistor temperature is within ideal limits, COLD, under range (see SafetySignal Decoder section) or is optioned out and the register bit CHARGE\_INHIBIT is cleared (see Tables 6 and 7 for register details).

Soft-start ramps the charge current at a rate set by the capacitor on the  $I_{TH}$  pin. When charging begins, the programmable timer initiates timing and the CHGb (GPIO1 pin) status output is pulled LOW. An external capacitor on the TIMER pin, along with the current set by the total series resistance connected to the  $V_{REF}$  pin, sets the total charge time.

If the battery voltage is less than the 3.0V/cell bulk charge threshold (V<sub>BC</sub>), the charger will begin with a preconditioning trickle charge current. The trickle current is programmed by the resistor ( $R_{PCC}$ ) from the  $I_{PCC}$  pin to ground. During preconditioning trickle charging, if the battery voltage stays below the bulk charge threshold (V<sub>BC</sub>) 25% of the programmed bulk charge time, the battery may be defective and the charge sequence will be terminated immediately. To indicate this fault, the CHGb (GPIO1 pin) becomes high impedance, the CHG\_STATE\_0 and CHG\_STATE\_1 register bits will be set low and CHG FLT register bit will be set high. Charge is terminated and the timer reset until the fault is cleared by the RESET\_TO\_ZERO or POR\_RESET SMBus write commands, SHDN pin toggle or the battery removed and replaced. Removing the supply input will not clear the fault if the battery is present.

If the battery voltage exceeds 107.5% ( $V_{BOV}$ ) of the programmed float voltage during any stage of charge, the charger pauses until the voltage drops below the hysteresis ( $V_{BOVH}$ ). The timer is not stopped and no fault is indicated.

Figure 3. Standard Li-Ion Charge State Diagram (Does Not Include Calibration)

| #  | Logic                | Event (T = True, F = False) [Notes]                                                                                                                                                     | Notes and/or Actions (T = True, F = False)                                                                                                        |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  |                      | RES_OR = F & DCDIV pin = T & SHDN pin = F & CHARGE_INHIBITED = F & CHG_FLT = F & V <sub>BAT</sub> < V <sub>BC</sub>                                                                     | I <sub>PPC</sub> & Timer/4(PreCond) = Started & CHG = T & ALARM_INHIBITED = F                                                                     |

|    | Or                   | RES_OR = F & DCDIV pin = T & SHDN pin = F & CHARGE_INHIBITED = F & CHG_FLT=F & ChargingVoltage() \neq 0 & ChargingCurrent() \neq 0                                                      | (RES_OR = F = Bat Inserted -> See ChargeStatus() ) (POR_RESET -> See ChargeMode()                                                                 |

| 2  |                      | V <sub>BAT</sub> > V <sub>BC</sub>                                                                                                                                                      | I <sub>PPC</sub> = Off & I <sub>CHG</sub> = On & Timer/4(PreCond) = Stopped & Timer(Bulk) = Started.                                              |

| 3  |                      | C/5 = T                                                                                                                                                                                 | Timer(Bulk) = Stopped & Timer/4(Top Off) = Started                                                                                                |

| 4  |                      | Timer/4(Top Off = done [Battery is full]                                                                                                                                                | I <sub>CHG</sub> = Off & CHG = F (Typical Full State)                                                                                             |

| 5  |                      | Timer/4(PreCond) = done before $V_{BAT} > V_{BC}$                                                                                                                                       | I <sub>PPC</sub> = Off & CHG_FLT = T & CHG = F                                                                                                    |

| 6  |                      | Timer(Bulk) = done before C/5 = T                                                                                                                                                       | I <sub>CHG</sub> = Off & CHG_FLT = T & CHG = F                                                                                                    |

| 7  | 0r                   | RESET_TO_ZERO = T [See ChargeMode()]<br>CHARGE_INHIBIT=T [See ChargeMode()]                                                                                                             | I <sub>CHG</sub> or IPPC = Off & All Timers = Reset & CHG_FLT = F & CHG = F                                                                       |

| 8  |                      | RES_HOT = T & RES_UR = F [See ChargeStatus()]                                                                                                                                           | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & CHG_FLT = T, Timers paused.                                                                          |

| 9  |                      | RES_HOT = F [See ChargeStatus()]                                                                                                                                                        | $I_{CHG}$ or $I_{PPC} = On \& CHG_{FLT} = F$ , Timers resume.                                                                                     |

| 10 | Or<br>Or<br>Or<br>Or | DCDIV pin = F RES_OR = T [Bat Removed, See ChargeStatus()] SHDN pin = T V <sub>UVD</sub> = T POR_RESET = T [See ChargeMode()]                                                           | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & All Timers = Reset & ALARM_INHIBITED = F & CHG_FLT = F & CHG = F & CHARGE_INHIBITED = F              |

| 11 | Or                   | $V_{AR} = T$ [AutoRestart]<br>ChargingVoltage() & ChargingCurrent() $\neq$ 0                                                                                                            | (The battery needs another charge cycle or Smart Battery has requested to start another cycle.)                                                   |

| 12 | Or<br>Or<br>Or       | AlarmWarning() command is sent by Smart Battery over SMBus with any of the following bits set to True:  OVER_CHARGED_ALARM TERMINATE_CHARGE_ALARM Reserved ALARM OVER_TEMPERATURE_ALARM | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & All Timers = Reset & CHG = F & ALARM_INHIBITED = T  (ALARM_INHIBITED bit is found in ChargeStatus()) |

| 13 |                      | ChargingVoltage() or ChargingCurrent() = 0 sent                                                                                                                                         | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & CHG = F                                                                                              |

| 14 |                      | V <sub>BOV</sub> = T [Battery Overvoltage]                                                                                                                                              | PWM stopped. Timers remain running.                                                                                                               |

| 15 |                      | $V_{BOV} = F$                                                                                                                                                                           | PWM restarted.                                                                                                                                    |

Note: For all charge states,  $\ensuremath{V_{\text{CHG}}}$  is always active.

When the battery voltage exceeds the bulk charge threshold  $(V_{BC})$ , the charger begins the bulk charge portion of the charge cycle. As the battery accepts charge, the voltage increases. Constant-current charge continues until the battery approaches the constant voltage. At this time, the charge current will begin to drop, signaling the beginning of the constant-voltage portion of the charge cycle.

The charger will maintain the constant voltage across the battery until either C/x is reached or 100% of the programmed bulk charge time has elapsed during bulk charge. When the current drops to approximately 20% of the full-scale charge current, an internal C/x comparator will initiate the start of the top-off stage. The top-off stage charges for 25% of the total programmed bulk charge time. When the time elapses, charge is terminated and CHGb (GPIO1 pin) is forced to a high impedance state and CHG STATE 0 and CHG\_STATE\_1 register bits will be set low. Should the total bulk charge time elapse before C/x is reached, charge is terminated and a CHG FLT fault is indicated until cleared by the RESET TO ZERO or POR RESET SMBus write commands, SHDN pin toggle or the battery removed and replaced. Fault conditions are not cleared when the supply input is removed if the battery has sufficient voltage.

An optional external thermistor network is sampled at regular intervals to monitor battery temperature and to detect battery presence. If the thermistor temperature is hot (see the SafetySignal Decoder section), the charge timer is paused, charge current is halted, CHG FLTb (GPIO3) pin) is forced low and the CHG\_FLT bit will be set high. CHGb (GPIO1 pin), CHG\_STATE\_0 and CHG\_STATE\_1 register bits will not be affected. When the thermistor value returns to an acceptable value, charging resumes, CHG FLTb (GPIO3 pin) returns to high impedance and the CHG FLT bit will be reset low. An open thermistor indicates absence of a battery. To defeat the temperature monitoring function, replace the thermistor with a resistor to indicate ideal battery temperature. When a thermistor is not used, the resistor circuit must be routed through the battery connector if battery presence detection is required.

After a charge cycle has ended without fault, the charge cycle is automatically restarted if the average battery cell voltage falls below the auto recharge threshold. At any

time charging can be forced to stop by pulling the SHDN pin high or setting the CHARGE\_INHIBIT bit high through the SMBus.

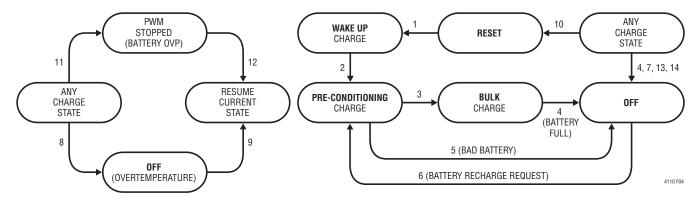

#### **SMART BATTERY CHARGE MODE**

This section explains operation for smart batteries with a SMBus interface. Smart Li-Ion is selected by connecting the TYPE pin to the  $V_{DD}$  pin and smart Nickel (NiMH/NiCd) is selected by connecting the TYPE pin to the  $V_{REF}$  pin. The LTC4110 only implements a subset of smart battery charger commands; the actual charging algorithm is determined by LTC4110 through external resistors even if the battery is "smart."

The LTC4110 operates as a high efficiency, synchronous, PWM flyback battery charger with constant current and constant float voltage regions of operation. The constant-charge current is programmed by the combination of a resistor (R<sub>CHG</sub>) from the  $I_{CHG}$  pin to ground, a battery current sense resistor (R<sub>SNS(BAT)</sub>) and CSP/CSN pin resistors. For Li-Ion the constant voltage (float voltage) is programmed to one of four values (4.2V, 8.4V, 12.6V, 16.8V) depending on the number of series cells using the SELC pin and can be adjusted  $\pm 0.3$ V/cell with the V<sub>CHG</sub> pin. For nickel batteries the constant-voltage function is not used, however, a non-zero value is still required to be written to the ChargingVoltage() register. The internal auto recharge function is inhibited for smart batteries.

If the battery voltage exceeds 107.5%  $(V_{BOV})$  of the programmed float voltage during any stage of charge, the charger pauses until the voltage drops below the hysteresis  $(V_{BOVH})$ . The timer is not stopped and no fault is indicated. This function is disabled when nickel based smart batteries are used.

There are four states associated with smart battery charge mode, namely:

- SMBus Wake-Up Charge State

- SMBus Preconditioning Charge State

- SMBus Bulk Charge State

- SMBus OFF State

These states are explained in the following four sections.

LINEAD

Figure 4. Smart Battery Charge State Diagram (Does Not Include Calibration)

| #  | Logic                | Event (T = True, F = False) [Notes]                                                                                                                                                     | Notes and/or Actions (T = True, F = False)                                                                                                         |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  |                      | RES_OR = F & DCDIV pin = T & SHDN pin = F & CHARGE_INHIBITED = F & CHG_FLT = F & RES_HOT = F                                                                                            | I <sub>PPC</sub> = On (Constant Current only) & TTIMEOUT = Started & CHG = T                                                                       |

|    | Or                   | RES_OR = F & DCDIV pin = T & SHDN pin = F & CHARGE_INHIBITED = F & CHG_FLT = F & RES_HOT = T & RES_UR = T                                                                               |                                                                                                                                                    |

| 2  |                      | ChargingVoltage() & ChargingCurrent() ≠ 0 sent                                                                                                                                          | Timer/4(Pre-Charge) = Started & TTIMEOUT disabled & ALARM_INHIBITED = F                                                                            |

| 3  |                      | V <sub>BAT</sub> > V <sub>BC</sub>                                                                                                                                                      | I <sub>PPC</sub> = Off, I <sub>CHG</sub> = On, Timer/4(Pre-Charge) = Stopped & Timer(SMBus) = Started                                              |

| 4  |                      | ChargingVoltage() or ChargingCurrent() = 0 sent                                                                                                                                         | I <sub>CHG</sub> = Off & All Timers = Reset & CHG = F                                                                                              |

| 5  |                      | Timer/4(Pre-Charge) = Done before V <sub>BAT</sub> > V <sub>BC</sub>                                                                                                                    | I <sub>PPC</sub> = Off & All Timers = Reset & CHG = F                                                                                              |

| 6  |                      | ChargingVoltage() & ChargingCurrent() ≠ 0 sent & RES_OR = F & DCDIV pin = T & SHDN pin = F & CHARGE_INHIBITED = F & CHG_FLT = F                                                         | I <sub>PPC</sub> = On & Timer/4(Pre-Charge) = Started & CHG = T & ALARM_INHIBITED = F                                                              |

| 7  |                      | TTIMEOUT = Done (Dead Battery or Loss of SMBus)                                                                                                                                         | I <sub>CHG</sub> = Off & All Timers Reset & CHG = F                                                                                                |

| 8  |                      | RES_HOT = T & RES_UR = F [See ChargeStatus()]                                                                                                                                           | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & CHG_FLT = T, Timer = Paused.                                                                          |

| 9  |                      | RES_HOT = F [See ChargeStatus()]                                                                                                                                                        | I <sub>CHG</sub> or I <sub>PPC</sub> = On & CHG_FLT = F, Timer = Resume.                                                                           |

| 10 | Or<br>Or<br>Or<br>Or | DCDIV pin = F RES_OR = T [Bat Removed, See ChargeStatus()] SHDN pin = T V <sub>UVD</sub> = T POR_RESET = T [See ChargeMode()]                                                           | I <sub>CHG</sub> or I <sub>PPC</sub> = Off & All Timers = Reset & CHG_FLT = F & CHG = F & ALARM_INHIBITED = F & CHARGE_INHIBITED = F               |

| 11 |                      | V <sub>BOV</sub> = T [Battery Overvoltage]                                                                                                                                              | PWM stopped. Timers remain running.                                                                                                                |

| 12 |                      | $V_{BOV} = F$                                                                                                                                                                           | PWM restarted.                                                                                                                                     |