## L4947PD

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                        | Parameter                                                                                                                                                                                                                                                                | Value            | Unit        |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|--|--|

| Vi                                                            | DC Input Voltage<br>DC Reverse Input Voltage<br>Transient Input Overvoltages :<br>Load Dump :<br>$5ms \le t_{rise} \le 10ms$                                                                                                                                             | 35<br>- 18<br>80 | V<br>V<br>V |  |  |

|                                                               | $ \begin{aligned} \tau_f \text{ Fall Time Constant} &= 100\text{ms} \\ R_{\text{SOURCE}} &\geq 0.5\Omega \\ \text{Field Decay}: \end{aligned} $                                                                                                                          | - 80             | V           |  |  |

|                                                               | $\begin{array}{l} 5ms \leq t_{fall} \leq 10ms, \ R_{SOURCE} \geq 10\Omega \\ \tau_r \ Rise \ Time \ Constant = 33ms \\ Low \ Energy \ Spike : \\ t_{rise} = 1\mu s, \ t_{fall} = 500\mu s, \ R_{SOURCE} \geq 10\Omega \\ f_r \ Repetition \ Frequency = 5Hz \end{array}$ | ± 100            | v           |  |  |

| V <sub>R</sub>                                                | Reset Output Voltage                                                                                                                                                                                                                                                     | 35               | v           |  |  |

| T <sub>J</sub> , T <sub>stg</sub>                             | Junction and Storage Temperature Range                                                                                                                                                                                                                                   | - 55 to 150      | °C          |  |  |

| Note: The circuit is ESD protected according to MIL-STD-883C. |                                                                                                                                                                                                                                                                          |                  |             |  |  |

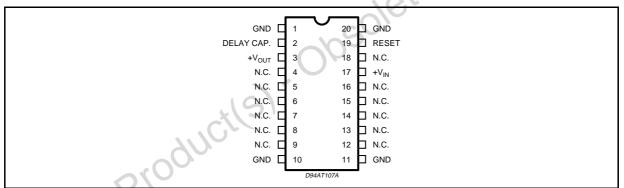

| PIN CONNECTION (Top view)                                     |                                                                                                                                                                                                                                                                          |                  |             |  |  |

|                                                               |                                                                                                                                                                                                                                                                          |                  |             |  |  |

## **PIN CONNECTION** (Top view)

## THERMAL DATA

| Symbol                 | Parameter                            | Value | Unit |

|------------------------|--------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max | 3     | °C/W |

# **TEST CIRCUIT**

| Symbol                 | Parameter                              | Test Conditions                                                                                                             | Min. | Тур.                            | Max.                     | Unit           |

|------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|---------------------------------|--------------------------|----------------|

| Vo                     | Output Voltage                         | l₀ = 0mA to 500mA<br>Over Full T Range                                                                                      | 4.80 | 5.00                            | 5.20                     | V              |

|                        |                                        | $T_{\rm J} = 25^{\circ} \rm C$                                                                                              | 4.90 | 5.00                            | 5.10                     | V              |

| Vi                     | Operating Input Voltage                | $I_0 = 0mA \text{ to } (*) 500mA$                                                                                           | 6    | _                               | 26                       | V              |

| $\Delta V_o$           | Line Regulation                        | $V_i = 6V \text{ to } 26V \text{ ;}$<br>$I_o = 5mA$                                                                         |      | 5                               | 50                       | mV             |

| $\Delta V_{o}$         | Load Regulation                        | $I_o = 5mA$ to 500mA                                                                                                        |      | 15                              | 60                       | mV             |

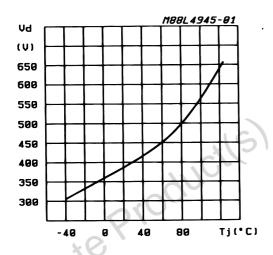

| $V_i - V_o$            | Dropout Voltage                        | $I_o = 500$ mA, $T_J = 25$ °C<br>Over Full T Range                                                                          |      | 0.40                            | 0.55<br>0.75             | V<br>V         |

| Ιq                     | Quiescent Current                      | $\begin{array}{l} I_{o}=0mA, \ T_{J}=25^{\circ}C\\ I_{o}=0mA \ Over \ Full \ T\\ I_{o}=500mA \ Over \ Full \ T \end{array}$ |      | 5<br>6.5<br>110                 | 10<br>13<br>180          | mA<br>mA<br>mA |

| $\frac{\Delta V_o}{T}$ | Temperature Output Voltage<br>Drift    |                                                                                                                             |      | - 0.5                           | 5                        | mV/°C          |

| SVR                    | Supply Volt. Rej.                      | $\begin{array}{l} I_{o} = 350 mA \; ; \; f = 120 Hz \\ C_{o} = 100 \mu F \; ; \\ V_{i} = 12 V \pm 5 V_{pp} \end{array}$     | 50   | 60                              |                          | dB             |

| I <sub>sc</sub>        | Output Short Circuit Current           | *6                                                                                                                          | 0.50 | 0.80                            | 1.50                     | А              |

| V <sub>R</sub>         | Reset Output Saturation Voltage        | $1.5V < V_o < V_{RT (off)},$<br>$I_R = 1.6mA$                                                                               |      |                                 | 0.40                     | V              |

|                        |                                        | $3.0V < V_o < V_{RT (off)},$<br>$I_R = 8mA$                                                                                 |      |                                 | 0.40                     | V              |

| I <sub>R</sub>         | Reset Output Leakage Current           | $V_0$ in Regulation, $V_R = 5V$                                                                                             |      |                                 | 50                       | μA             |

| $V_{RTpeak}$           | Power On-Off Reset out Peak<br>Voltage | $1K\Omega$ Reset Pull-up to $V_o$                                                                                           |      | 0.65                            | 1.0                      | V              |

| V <sub>RT (off)</sub>  | Power OFF V <sub>0</sub> Threshold     | V <sub>o</sub> @ Reset Out H to L<br>Transition                                                                             | 4.75 | Vo –<br>0.15                    |                          | v              |

| V <sub>RT (on)</sub>   | Power ON V <sub>o</sub> Threshold      | V <sub>o</sub> @ Reset Out L to H<br>Transition                                                                             |      | V <sub>RT (off)</sub><br>+ 0.05 | V <sub>o</sub> –<br>0.04 | V              |

| V <sub>Hyst</sub>      | Power ON-Off Hysteresis                | V <sub>RT (on)</sub> –V <sub>RT (off)</sub>                                                                                 |      | 0.05                            |                          | V              |

| Vd                     | Delay Comparator Threshold             | V <sub>d</sub> @ Reset Out L to H<br>Transition                                                                             | 3.65 | 4.00                            | 4.35                     | V              |

|                        |                                        | V <sub>d</sub> @ Reset Out H to L<br>Transition                                                                             | 3.20 | 3.55                            | 3.90                     | V              |

| V <sub>dH</sub>        | Delay Comparator Hysteresis            |                                                                                                                             |      | 0.45                            |                          | V              |

| , d                    | Delay Capacitor Charging<br>Current    | $V_d = 3V, T_J = 25^{\circ}C$                                                                                               |      | 20                              |                          | /μΑ            |

| V <sub>disch</sub>     | Delay Capacitor Discharge<br>Voltage   | V <sub>o</sub> < V <sub>RT (off)</sub>                                                                                      |      | 0.55                            | 1.20                     | V              |

| T <sub>d</sub>         | Power on Reset Delay Time              | $C_{d} = 100 nF, T_{J} = 25^{\circ}C$                                                                                       | 10   | 20                              | 30                       | ms             |

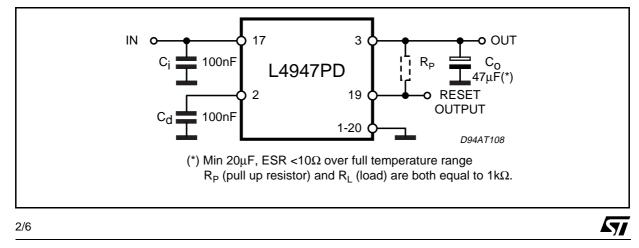

**ELECTRICAL CHARACTERISTICS** (refer to the test circuit,  $V_i = 14.4V$ ,  $C_o = 47\mu$ F, ESR <  $10\Omega$ ,  $R_p = 1K\Omega$ ,  $R_L = 1K\Omega$ ,  $-40^{\circ}C \le T_J \le 125^{\circ}C$ , unless otherwise specified)

(\*) For a DC voltage 26 < Vi < 37V the device is not operating

### **FUNCTIONAL DESCRIPTION**

The L4947PD is a very low drop 5V/0.5A voltage regulator provided with a reset function and therefore particularly suited to meet the requirements of supplying the microprocessor systems used in automotive and industrial applications.

The block diagram shows the basic structure of the device : the reference, the error amplifier, the driver, the power PNP, the protection and reset

# 57

### functions.

The power stage is a Lateral PNP transistor which allows a very low dropout voltage (typ. 400mV at  $T_J = 25^{\circ}$ C, max. 750mV over the full temperature range @ Io = 500mA). The typical curve of the dropout voltage as a function of the junction temperature is shown in Fig. 1 : that is the worst case, where Io = 500mA.

The current consumption of the device (quiescent

## L4947PD

current) is maximum 13mA - over full T - when no load current is required.

The internal antisaturation circuit allows a drastic reduction in the current peak which takes place during the start up.

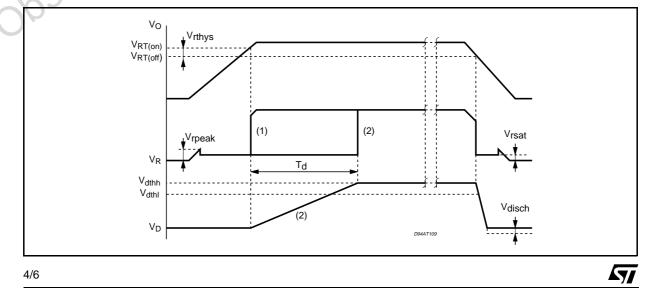

The reset function supervises the regulator output voltage inhibiting the microprocessor when the device is out of regulation and resetting it at the power-on after a settable delay. The reset is LOW when the output voltage value is lower than the reset threshold voltage. At the power-on phase the output voltage increases (see Fig. 2) and - when it reaches the power-on V<sub>O</sub> threshold V<sub>RT</sub> (On) - the reset output becomes HIGH after a delay time set by the external capacitor C<sub>d</sub>. At the power-off the output voltage decreases : at the V<sub>RT(Off)</sub> threshold value (Vo-0.15V typ. value) the reset output instantaneously goes down (LOW status) inhibiting the microprocessor. The typical

Figure 2: Reset Waveforms: (1) Without External Capacitor C<sub>d</sub>. (2) With External Capacitor C<sub>d</sub>. power on-off hysteresis is 50mV.

The three gain stages (operational amplifier, driver and power PNP) require the external capacitor ( $C_{omin} = 20\mu F$ ) to guarantee the global stability of the system.

Load dump and field decay protections ( $\pm$  80V), reverse voltage (– 18V) and short circuit protection, thermal shutdown are the main features that make the L4947PD specially suitable for applications in the automotive environment.

### EXTERNAL COMPENSATION

Since the purpose of a voltage regulator is to supply and load variations, the open loop gain of the regulator must be very high at low frequencies. This may cause instability as a result of the various poles present in the loop. To avoid this instability dominant pole compensation is used to reduce phase shift due to other poles at the unity gain frequency. The lower the frequency of these others poles at the unity gain frequency. The lower the frequency of these other poles, the greater must be capacitor esed to create the dominant pole for the same DC gain.

Where the output transistor is a lateral PNP type there is a pole in the regulation loop at a frequencybtoo low to be compensated by a capacitor which can be integrated. An external compensation is therefore necessary so a very high value capacitor must be connected from the output to ground.

The paeassitic equivalent series resistance of the capacitor used adds a zero to the regulation loop. This zero may compromise the stability of the system since its effect tends to cancel the effect of the pole added. In regulators this ESR must be less than  $3\Omega$  and the minimum capacitor value is  $47\mu$ F.

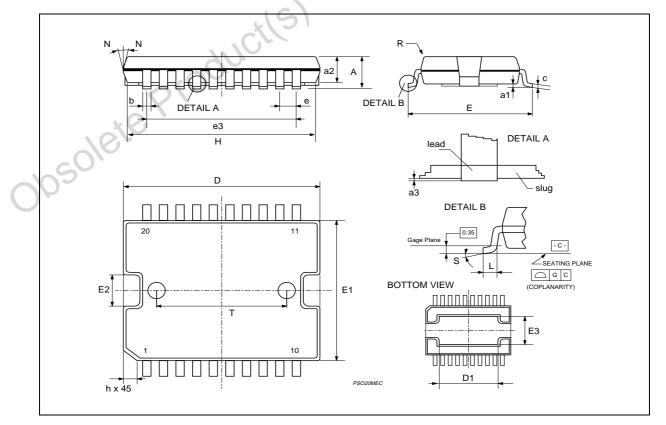

| DIM.   | mm         |       |      | inch  |       |       |

|--------|------------|-------|------|-------|-------|-------|

| DIN.   | MIN.       | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| А      |            |       | 3.6  |       |       | 0.142 |

| a1     | 0.1        |       | 0.3  | 0.004 |       | 0.012 |

| a2     |            |       | 3.3  |       |       | 0.130 |

| a3     | 0          |       | 0.1  | 0.000 |       | 0.004 |

| b      | 0.4        |       | 0.53 | 0.016 |       | 0.021 |

| с      | 0.23       |       | 0.32 | 0.009 |       | 0.013 |

| D (1)  | 15.8       |       | 16   | 0.622 |       | 0.630 |

| D1     | 9.4        |       | 9.8  | 0.370 |       | 0.386 |

| Е      | 13.9       |       | 14.5 | 0.547 |       | 0.570 |

| е      |            | 1.27  |      |       | 0.050 |       |

| e3     |            | 11.43 |      |       | 0.450 |       |

| E1 (1) | 10.9       |       | 11.1 | 0.429 |       | 0.437 |

| E2     |            |       | 2.9  |       |       | 0.114 |

| E3     | 5.8        |       | 6.2  | 0.228 |       | 0.244 |

| G      | 0          |       | 0.1  | 0.000 |       | 0.004 |

| Н      | 15.5       |       | 15.9 | 0.610 |       | 0.626 |

| h      |            |       | 1.1  |       |       | 0.043 |

| L      | 0.8        |       | 1.1  | 0.031 |       | 0.043 |

| Ν      | 10° (max.) |       |      |       |       |       |

| S      | 8° (max.)  |       |      |       |       |       |

| Т      |            | 10    |      |       | 0.394 |       |

"D and F" do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.15 mm (0.006").

Critical dimensions: "E", "G" and "a3"

57

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

6/6

DocID4055 Rev 4