### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                                              | Definition           |                       | Max.                  | Units |

|-------------------|-------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-------|

| VB                | High side floating supply voltage                                       | -0.3                 | 625                   |                       |       |

| Vs                | High side floating supply offset voltage                                | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  |                       |       |

| V <sub>HO</sub>   | High side floating output voltage                                       | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  | V                     |       |

| V <sub>LO</sub>   | Low side output voltage                                                 | -0.3                 | V <sub>CC</sub> + 0.3 |                       |       |

| VPFC              | PFC gate driver output voltage                                          | -0.3                 | Vcc + 0.3             |                       |       |

| I <sub>OMAX</sub> | Max. allowable output current (HO,LO,PFC power transistor miller effect | -500                 | 500                   | mA                    |       |

| I <sub>RT</sub>   | RT pin current                                                          | -5                   | 5                     |                       |       |

| V <sub>CT</sub>   | C <sub>T</sub> pin voltage                                              | -0.3                 | 6.5                   | .,                    |       |

| $V_{DC}$          | VDC pin voltage                                                         |                      | -0.3                  | V <sub>CC</sub> + 0.3 | V     |

| I <sub>CPH</sub>  | CPH pin current                                                         | -5                   | 5                     |                       |       |

| I <sub>RPH</sub>  | RPH pin current                                                         | -5                   | 5                     | •                     |       |

| I <sub>RUN</sub>  | RUN pin current                                                         | -5                   | 5                     | mA                    |       |

| I <sub>DT</sub>   | Deadtime pin current                                                    | -5                   | 5                     |                       |       |

| V <sub>CS</sub>   | Current sense pin voltage                                               | -0.3                 | 6.5                   | V                     |       |

| I <sub>CS</sub>   | Current sense pin current                                               | -5                   | 5                     |                       |       |

| loc               | Over-current threshold pin current                                      | -5                   | 5                     | mA                    |       |

| $I_{SD}$          | Shutdown pin current                                                    | -5                   | 5                     |                       |       |

| $V_{BUS}$         | DC bus sensing input voltage                                            |                      | -0.3                  | V <sub>CC</sub>       | V     |

| $I_{ZX}$          | PFC inductor current, zero crossing detect                              | ion input            | -5                    | 5                     |       |

| I <sub>COMP</sub> | PFC error amplifier compensation current                                |                      | -5                    | 5                     | mA    |

| Icc               | Supply current (note 1)                                                 |                      | -20                   | 20                    |       |

| dV/dt             | Allowable offset supply voltage slew ratet                              | slew ratet           |                       | 50                    | V/ns  |

| $P_{D}$           | Package power dissipation @ T <sub>A</sub> ≤ +25°C                      | (20 lead PDIP)       | _                     | 1.50                  | W     |

|                   |                                                                         | (20 lead SOIC)       | _                     | 1.25                  |       |

| $Rth_JA$          | Thermal resistance, junction to ambient                                 | (20 lead PDIP)       | _                     | 85                    | °C/W  |

|                   |                                                                         | (20 lead SOIC)       |                       | 90                    | C/VV  |

| TJ                | Junction temperature                                                    |                      | -55                   | 150                   |       |

| T <sub>S</sub>    | Storage temperature                                                     | -55                  | 150                   | °C                    |       |

| TL                | Lead temperature (soldering, 10 seconds)                                | _                    | 300                   |                       |       |

### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead

| Symbol           | Definition                                            | Min.                  | Max.               | Units |  |

|------------------|-------------------------------------------------------|-----------------------|--------------------|-------|--|

| V <sub>BS</sub>  | High side floating supply voltage                     | V <sub>CC</sub> - 0.7 | V <sub>CLAMP</sub> |       |  |

| Vs               | Steady state high side floating supply offset voltage | -3.0                  | 600                | V     |  |

| Vcc              | Supply voltage                                        | V <sub>CCUV+</sub>    | V <sub>CLAMP</sub> | 1     |  |

| Icc              | Supply current                                        | Note 2                | 10                 | mA    |  |

| V <sub>DC</sub>  | V <sub>DC</sub> lead voltage                          | 0                     | VCC                | V     |  |

| I <sub>SD</sub>  | Shutdown lead current                                 | -1                    | 1                  |       |  |

| Ics              | Current sense lead current                            | -1                    | 1                  | mA    |  |

| C <sub>T</sub>   | C <sub>T</sub> lead capacitance                       | 220                   | _                  | pF    |  |

| R <sub>DT</sub>  | Deadtime resistance                                   | 1.0                   | _                  | kΩ    |  |

| I <sub>RT</sub>  | R <sub>T</sub> lead current (Note 3)                  | -500                  | -50                |       |  |

| I <sub>RPH</sub> | RPH lead current (Note 3)                             | 0                     | 450                | uA    |  |

| I <sub>RUN</sub> | RUN lead current (Note 3)                             | 0                     | 450                |       |  |

| I <sub>ZX</sub>  | Zero crossing detection lead current                  | -1                    | 1                  | mA    |  |

| TJ               | Junction temperature                                  | -40                   | 125                | °C    |  |

#### **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, R_T = 16.9k\Omega, C_T = 470 \ pF, RPH \ and RUN \ leads \ no \ connection, V_{CPH} = 0.0V, R_{DT} = 6.1k\Omega, R_{OC} = 20.0k\Omega, V_{CS} = 0.5V, V_{SD} = 2.0V, C_L = 1000pF, T_A = 25^{\circ}C \ unless \ otherwise \ specified.$

| Supply Characteristics |                                                              |      |      |      |       |                                              |

|------------------------|--------------------------------------------------------------|------|------|------|-------|----------------------------------------------|

| Symbol                 | Definition                                                   | Min. | Тур. | Max. | Units | Test Conditions                              |

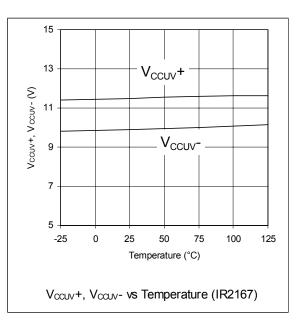

| V <sub>CCUV+</sub>     | V <sub>CC</sub> supply undervoltage positive going threshold | 10.4 | 11.4 | 12.5 | V     | V <sub>CC</sub> rising from 0V               |

| V <sub>UVHYS</sub>     | V <sub>CC</sub> supply undervoltage lockout hysteresis       | 2.0  | 2.1  | 2.1  |       |                                              |

| IQCCUV                 | UVLO mode quiescent current                                  | _    | 250  | 400  |       | V <sub>CC</sub> < V <sub>CCUV</sub> -        |

| IQCCFLT                | Fault-mode quiescent current                                 |      | 100  | 350  | μΑ    | SD = 5V, CS = 2V or                          |

|                        |                                                              |      |      |      |       | Tj > T <sub>SD</sub>                         |

| Iqcc                   | Quiescent V <sub>CC</sub> supply current                     | 1.9  | 3.3  | 4.5  | 1     | R <sub>T</sub> no connection, C <sub>T</sub> |

|                        |                                                              |      |      |      | mA    | connected to COM                             |

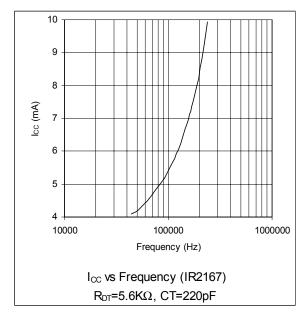

| I <sub>CC50K</sub>     | V <sub>CC</sub> supply current, f = 48kHz                    | 4.0  | 5.0  | 6.0  |       |                                              |

| VCLAMP                 | V <sub>CC</sub> zener clamp voltage                          | 14.0 | 15.6 | 16.5 | V     | ICC = 10mA                                   |

Note 2: Sufficient current should be supplied to the VCC pin to keep the internal 15.6V zener clamp diode on this pin regulating its voltage.

Note 3: Due to the fact that the RT pin is a voltage-controlled current source, the total RT pin current is the sum of all of the parallel current sources connected to that pin. During the preheat mode, the total current flowing out of the RT pin consists of the RPH pin current plus the current due to the RT resistor. During the run mode, the total RT pin current consists of the RUN pin current plus the current due to the RT resistor.

International IOR Rectifier

### **Electrical Characteristics (cont.)**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, R_T = 16.9k\Omega, C_T = 470 \text{ pF, RPH and RUN leads no connection, } \\ V_{CPH} = 0.0V, R_{DT} = 6.1k\Omega, R_{OC} = 20.0k\Omega, V_{CS} = 0.5V, V_{SD} = 2.0V, C_L = 1000\text{pF, } \\ T_A = 25^{\circ}\text{C unless otherwise specified.}$

| Symbol                | Definition                                      | Min.     | Tvn  | Max. | Units  | Test Conditions                                                    |

|-----------------------|-------------------------------------------------|----------|------|------|--------|--------------------------------------------------------------------|

|                       |                                                 | IVIIII.  | Тур. |      | UIIIIS |                                                                    |

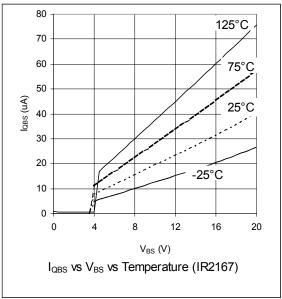

| IQBS0                 | Quiescent V <sub>BS</sub> supply current        |          | 0    | 10.0 | μΑ     | V <sub>HO</sub> = V <sub>S</sub>                                   |

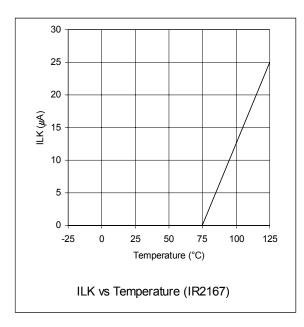

| I <sub>LK</sub>       | Offset supply leakage current                   |          | 0    | 50   | ,      | $V_B = V_S = 600V$                                                 |

| PFC Er                | ror Amplifier Characteristics                   |          |      |      |        |                                                                    |

| Symbol                | Definition                                      | Min.     | Тур. | Max. | Units  | Test Conditions                                                    |

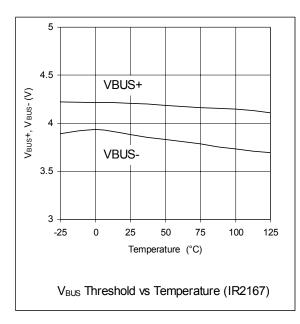

| V <sub>BUS</sub>      | VBUS sense input threshold                      | 3.7      | 4.0  | 4.3  |        | V                                                                  |

| I <sub>VBUS</sub>     | VBUS sense input bias current                   | _        | _    | 0.1  |        | μΑ                                                                 |

| gm                    | Error amplifier transconductance                | 40       | 90   | 130  | μmho   | RUN mode operation                                                 |

| ISOURCE               | Error amplifier output current sourcing         | 15       | 30   | 50   |        | V <sub>BUS</sub> = 3V                                              |

| I <sub>SINK</sub>     | Error amplifier output current sinking          | 5        | 30   | 50   | μA     | V <sub>BUS</sub> = 5V                                              |

| V <sub>OH(EA)</sub>   | Error amplifier output voltage swing (Hi state) | 12.5     | 13.5 | 14.5 | .,     | V <sub>BUS</sub> = 3V                                              |

| V <sub>0</sub> L(EA)  | Error amplifier output voltage swing (Lo state) | _        | 0.25 | 0.4  | V      | V <sub>BUS</sub> = 5V                                              |

| PFC O                 | ver Voltage Comparator                          |          |      |      |        |                                                                    |

|                       | Definition .                                    | Min.     | Тур. | Max. | Units  | Test Conditions                                                    |

| V <sub>OV</sub>       | Over voltage comparator threshold               | 4.0      | 4.3  | 4.5  | V      |                                                                    |

|                       |                                                 | 1        |      |      |        |                                                                    |

|                       | ro Current Detector                             |          |      |      |        |                                                                    |

| $V_{ZX}$              | ZX lead comparator threshold voltage            | 1.7      | 2.0  | 2.3  | V      |                                                                    |

| $V_{ZXhys}$           | ZX lead comparator hysterisis                   | 400      | 300  | 300  | mV     |                                                                    |

| V <sub>ZXclamp+</sub> | ZX lead clamp voltage (high state)              | 6.0      | 7.5  | 9.0  | V      | I <sub>ZX</sub> = 1mA                                              |

| Oscilla               | tor, Ballast Control, I/O Characte              | eristics | ;    |      |        |                                                                    |

| Symbol                | Definition                                      | Min.     | Тур. | Max. | Units  | Test Conditions                                                    |

| fosc                  | Oscillator frequency                            | 41       | 44   | 47   | kHz    | RT = $16.9k\Omega$ , RDT = $6.1k\Omega$ , C <sub>T</sub> = $470pF$ |

| VCT+                  | Upper CT ramp voltage threshold                 | 3.6      | 4.0  | 4.4  |        | 0.1K22, O   -47 Opi                                                |

| VCT-                  | Lower C <sub>T</sub> ramp voltage threshold     | 1.8      | 2.0  | 2.2  | l v    |                                                                    |

| V <sub>RT</sub>       | RT lead voltage                                 | 1.8      | 2.0  | 2.2  | 1      |                                                                    |

| tDLO                  | LO output deadtime                              | 2.0      | 2.4  | 2.6  |        |                                                                    |

| tDHO                  | HO output deadtime                              | 2.0      | 2.4  | 2.6  | μsec   |                                                                    |

| DITO                  | •                                               |          |      |      |        |                                                                    |

| Prehea                | t Characteristics                               |          |      |      |        |                                                                    |

| Symbol                | Definition                                      | Min.     | Тур. | Max. | Units  | Test Conditions                                                    |

| I <sub>CPH+</sub>     | CPH lead charging current                       | 2.5      | 2.8  | 3.2  | μА     | V <sub>CPH</sub> = 0V                                              |

| I <sub>CPH</sub> -    | CPH lead discharge current                      | 50       | 175  | 350  | nA     | V <sub>CPH</sub> = 0V                                              |

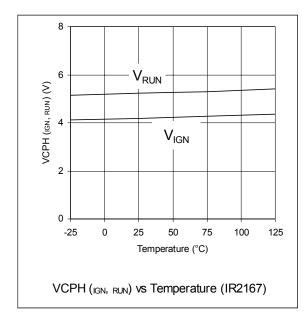

| VCPHIGN               | CPH lead Ignition mode threshold voltage        | 3.6      | 4.1  | 4.4  |        |                                                                    |

| VCPHRUN               | CPH lead run mode threshold voltage             | 4.7      | 5.1  | 5.5  | V      |                                                                    |

| * CEUKUN              | 1                                               |          |      |      |        |                                                                    |

### **Electrical Characteristics (cont.)**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, R_T = 16.9k\Omega, C_T = 470 \ pF, RPH \ and RUN \ leads \ no \ connection, V_{CPH} = 0.0V, R_{DT} = 6.1k\Omega, R_{OC} = 20.0k\Omega, V_{CS} = 0.5V, V_{SD} = 2.0V, C_L = 1000pF, T_A = 25^{\circ}C \ unless \ otherwise \ specified.$

| RPH Ch               | aracteristics                                              |      |      |      |        |                                           |

|----------------------|------------------------------------------------------------|------|------|------|--------|-------------------------------------------|

| Symbol               | Definition                                                 | Min. | Тур. | Max. | Units  | Test Conditions                           |

| I <sub>RPHLK</sub>   | Open circuit RPH lead leakage current                      | _    | 0.1  | _    | μА     | V <sub>RPH</sub> =5V,V <sub>RPH</sub> =6V |

| RUN Ch               | naracteristics                                             |      | •    |      |        |                                           |

| Symbol               | Definition                                                 | Min. | Тур. | Max. | Units  | Test Conditions                           |

| I <sub>RUNLK</sub>   | Open circuit RUN lead leakage current                      | _    | 0.1  | _    | μА     | V <sub>RUN</sub> = 5V                     |

| Protect              | ion Circuitry Characteristics                              |      |      |      |        |                                           |

| Symbol               | Definition                                                 | Min. | Тур. | Max. | Units  | Test Conditions                           |

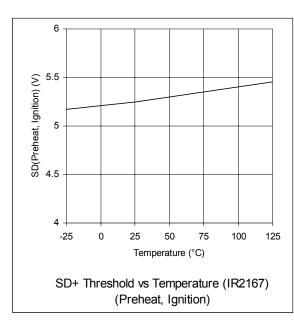

| V <sub>SDTH+</sub>   | Rising shutdown lead threshold voltage                     | 4.8  | 5.25 | 5.4  | V      |                                           |

| V <sub>SDHYS</sub>   | Shutdown lead threshold hysteresis                         | 300  | 150  | 100  | mV     |                                           |

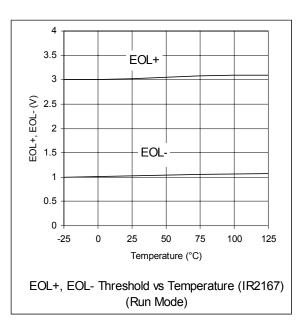

| V <sub>SDEOL+</sub>  | Rising shutdown lead end-of-life threshold voltage         | 2.6  | 3.0  | 3.4  |        |                                           |

| V <sub>SDEOL</sub> - | Falling shutdown lead end-of-life threshold voltage        | 0.7  | 1.0  | 1.3  | V      |                                           |

| V <sub>CSTH+</sub>   | Over-current sense threshold voltage                       | 1.05 | 1.2  | 1.35 |        |                                           |

| V <sub>CSTH</sub> -  | Under-current sense threshold voltage                      | 0.14 | 0.23 | 0.28 | Ť      |                                           |

| T <sub>CS</sub>      | Over-current sense propogation delay                       | 50   | 350  | 550  | nsec   | Delay from CS to LC                       |

| #FAULT               | Number of sequential over-current Fault                    |      |      |      |        | 4V < V <sub>CPH</sub> <5.1V,              |

| cycles               | cycles before IC shuts down (IGN Mode)                     | 25   | 50   | 75   | cycles | cycles @CS > 1.3V                         |

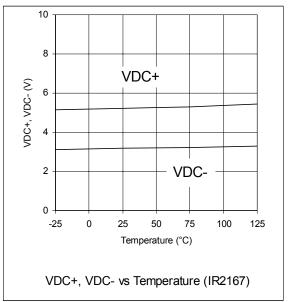

| V <sub>VDC+</sub>    | Low V <sub>BUS</sub> /rectified line input upper threshold | 4.8  | 5.2  | 5.7  | .,     |                                           |

| V <sub>VDC</sub> -   | Low V <sub>BUS</sub> /rectified line input lower threshold | 2.7  | 3.1  | 3.5  | † V    |                                           |

| T <sub>SD</sub>      | Thermal shutdown junction temperature                      | _    | 160  | _    | °C     | Note 4                                    |

| Gate Dr              | iver Output Characteristics                                |      |      |      |        |                                           |

| Symbol               | Definition                                                 | Min. | Тур. | Max. | Units  | Test Conditions                           |

| VOL                  | Low level output voltage (PFC, LO or HO)                   | _    | 0    | 100  | mV -   | I <sub>O</sub> = 0                        |

| Voн                  | High level output voltage (PFC, LO or HO)                  | _    | 0    | 100  |        | $V_{BIAS} - V_{O, I_0} = 0$               |

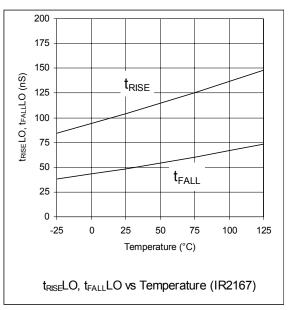

| tr                   | Turn-on rise time (PFC, LO or HO)                          | 50   | 85   | 200  | nsec   | , -                                       |

| tf                   | Turn-off fall time (PFC, LO or HO)                         | 25   | 45   | 100  |        |                                           |

Note 4: When the IC senses an overtemperature condition (Tj > 160°C), the IC is latched off. In order to reset this Fault Latch, the SD lead must be cycled high and then low, or the V<sub>CC</sub> supply to the IC must be cycled below the falling undervoltage lockout threshold (V<sub>CCUV</sub>-).

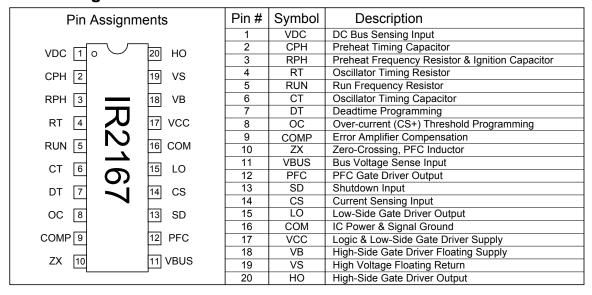

### **Lead Assignments**

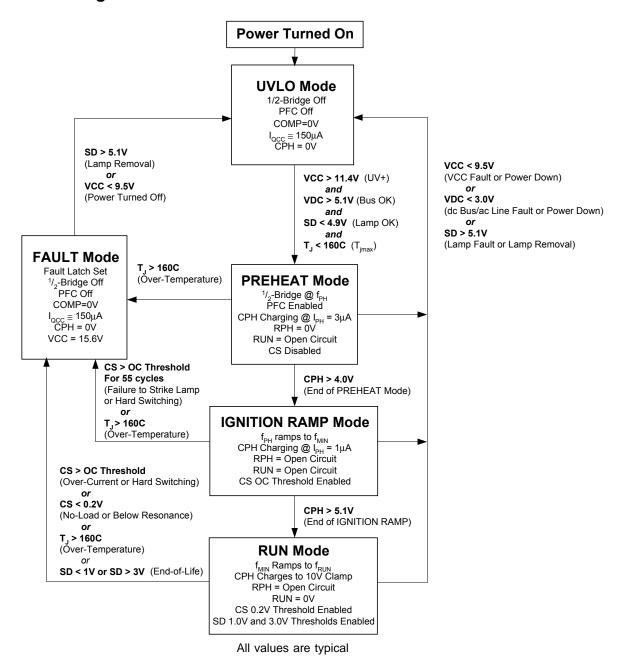

### **State Diagram**

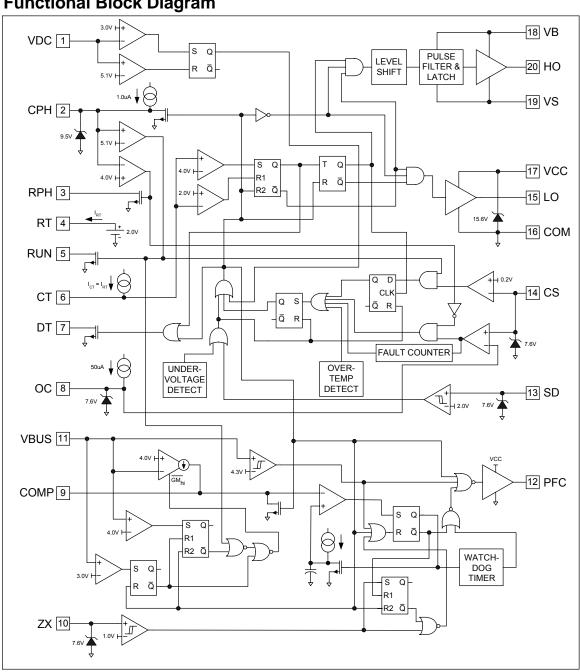

### **Functional Block Diagram**

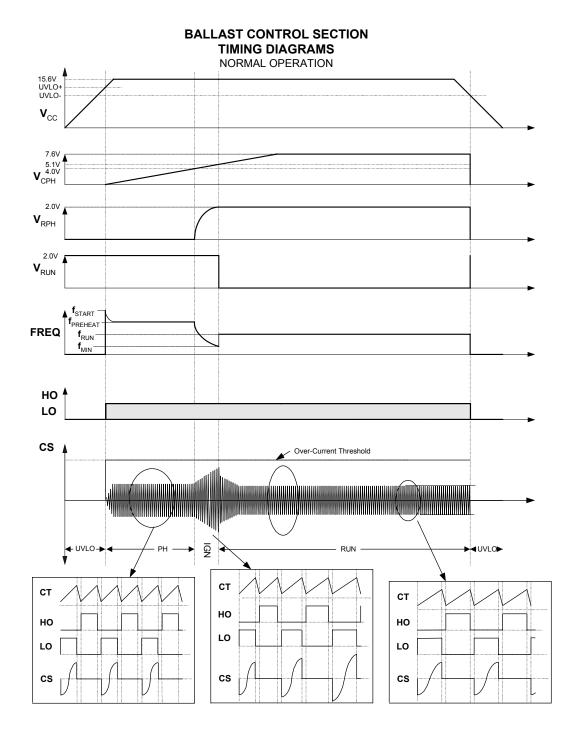

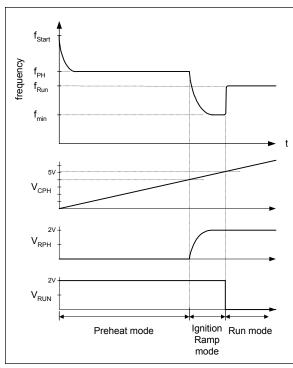

### **BALLAST CONTROL SECTION TIMING DIAGRAMS** FAULT CONDITION 2.0V $\mathbf{V}_{\mathsf{RPH}}$ 2.0V $\mathbf{V}_{\mathrm{RUN}}$ f<sub>START</sub> f<sub>PH</sub> **FREQ** SD & 5.2V 2V но 🕯 LO CS A ■UVLO► СТ СТ но но но LO LO LO cs cs

#### **Functional Description**

#### Under-voltage Lock-Out Mode (UVLO)

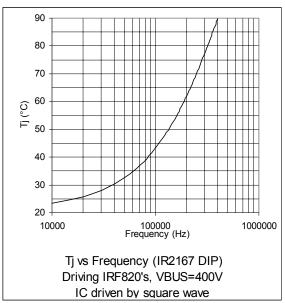

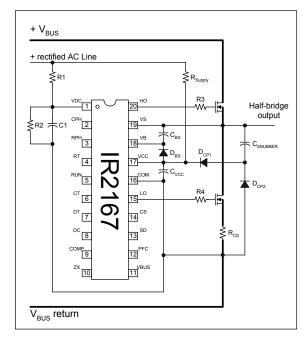

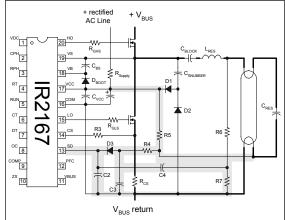

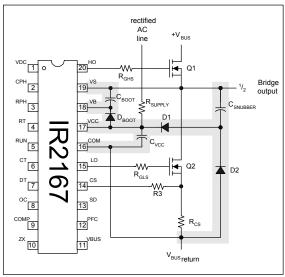

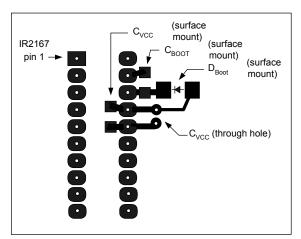

The under-voltage lock-out mode is defined as the state the IC is in when VCC is below the turn-on threshold of the IC. (To identify the different modes of the IC, refer to the State Diagram shown on page 7 of this document). During undervoltage lock-out mode, the HO, LO and PFC driver outputs are low and the CT pin is connected to COM through resistor R<sub>DT</sub> to disable the oscillator. Also, the internal supply to the RT pin circuitry is shut off and pins CPH, RUN, DT and COMP are internally pulled to COM. The IR2167 undervoltage lock-out mode is designed to maintain a very low supply current of less than 200µA, and to guarantee the IC is fully functional before the high side, low side and PFC drivers are activated. Figure 1 shows an efficient supply using the start-up current of the IR2167 together with a charge pump from the ballast stage (RSUPPLY, CVCC, DCP1 and DCP2).

Figure 1: Start-up and supply circuitry

The Vcc capacitor (C<sub>VCC</sub>) is charged by current through supply resistor (R<sub>SUPPLY</sub>) minus the start-up current drawn

by the IC. The value of (RSUPPLY) is chosen to provide 2X the maximum start-up current to guarantee ballast start-up at low line input voltage. Once the capacitor voltage on the VCC pin reaches the start-up threshold, the SD lead is below 5.1 volts and  $V_{VDC}$  is greater than 5.1V, the IC turns on and LO and HO begin to oscillate. PFC does not begin to oscillate until the IC reaches Preheat Mode.

#### **Preheat Mode Startup Mode**

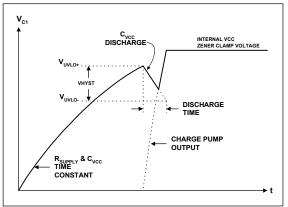

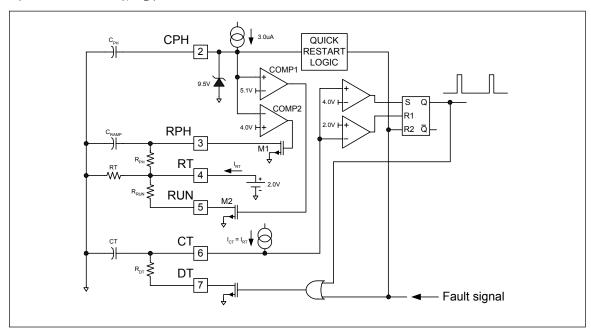

The IR2167 enters Preheat mode when VCC exceeds the UVLO positive-going threshold. Before Preheat mode begins, the CPH and RPH pins are connected to COM. (See Figure 3). As Preheat begins, the external capacitor CPH is charged up by an internal 3µA current source. CPH determines the preheat time which continues until the voltage on the CPH pin charges to 4.0V. Preheat mode is defined as the state the IC is in when the lamp filaments are being heated to their correct emission temperature. This is necessary for maximizing lamp life and reducing the required ignition voltage. At the onset of Preheat Mode, CVCC begins to discharge due to the increase in IC operating current (Figure 2) above the available current through resistor RSUPPLY. However, the half-bridge output also begins to oscillate and the charge pump, consisting of C<sub>SNUBBER</sub>, DCP1 and DCP2, supply the current to charge capacitor CVCC and thus the voltage to the IC. The VCC voltage supplied to the IC is

Figure 2: Supply Capacitor (CVCC) voltage

limited by the internal 15.6V zener clamp. CVCC and C<sub>SNUBBER</sub> must be selected such that enough supply current

is available over all ballast operating conditions. Bootstrap diode (DBS) and supply capacitor (CBS) comprise the supply voltage for the high-side driver circuitry. To guarantee that the high-side supply is charged up before the first pulse on HO, the first pulse from the output drivers comes from the LO pin.

The Preheat mode oscillation frequency of the half-bridge output is determined by the parallel combination of RPH and RT with the values of CT, RDT and an internal circuit as

turns off and CRAMP begins to charge. CRAMP determines the time it takes for the oscillator to ramp down from the Preheat frequency to the Ignition Mode frequency. Once the voltage on the RPH lead reaches 2.0V, external resistor RPH has no effect on the frequency that is now determined by external components RT, CT and RDT. This is the minimum frequency. By this time, the oscillator will have ramped down toward the resonance of the load circuit causing the lamp to ignite.

Figure 3: Oscillator section block diagram with external component connection

shown in Figure 3. Note that at the onset of Preheat mode the initial startup frequency is much higher than the preheat frequency. The half-bridge output frequency then ramps down from this initial start-up frequency to the Preheat mode frequency. This is to ensure that the instantaneous voltage across the lamp during the first few cycles of operation does not exceed the strike potential of the lamp.

#### **Ignition Mode**

When the CPH pin charges up to 4.0V, ignition mode begins. At this time, the output of COMP2 (figure 3) goes low, M1

#### Run Mode

When the voltage on the CPH pin reaches 5.1V, the IC enters Run mode. At this time, the output of COMP1 (figure 3) goes high which turns M2 on and pulls the RUN pin to COM. The frequency is now controlled by external components RT, RRUN, CT and RDT. In certain cases it is necessary to have the run frequency higher than the ignition frequency to control the power used by the load. Figure 4 shows the ballast control sequence explained in the previous paragraphs.

Figure 4: IR2167 Ballast Control Sequence

The control sequence used in the IR2167 allows the Run mode operating frequency of the ballast to be higher than the ignition frequency (i.e., fstart > fph > frun > fign). This control sequence is recommended for lamp types where the ignition frequency is too close to the run frequency to ensure proper lamp striking for all production resonant LC component tolerances (please note that it is possible to use the IR2167 in systems where fstart > fph > fign > frun, simply by leaving the RUN pin open).

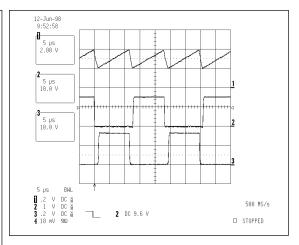

The heart of this controller is an oscillator that resembles those found in many popular PWM voltage regulator ICs. In its simplest form, this oscillator consists of a timing resistor and capacitor connected to ground. The voltage across the timing capacitor  $C_T$  is a sawtooth, where the rising portion of the ramp is determined by the current in the RT lead, and the falling portion of the ramp is determined by an external deadtime resistor  $R_{DT}$ . The oscillograph in Figure 5 illustrates the relationship between the oscillator capacitor waveform and the gate driver outputs.

Figure 5: Oscillator Waveforms

This falling portion of the sawtooth waveform is referred to as deadtime, during which both HO and LO outputs are low. The deadtime can be programmed by means of the external  $R_{\mbox{\scriptsize DT}}$  resistor.

The RT input is a voltage-controlled current source, where the voltage is regulated to be approximately 2.0V. In order to maintain proper linearity between the RT pin current and the CT capacitor charging current, the value of the RT pin current should be kept between  $50\mu A$  and  $500\mu A$ . The RT pin can also be used as a feedback point for closed loop control.

#### **PFC Section**

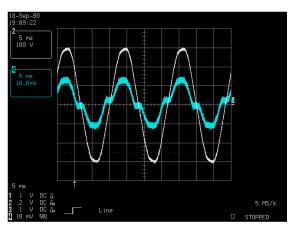

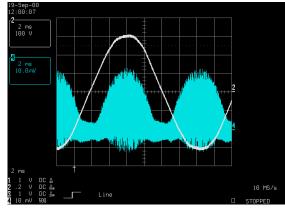

In most AC to DC power converters it is necessary to have the circuit act as a pure resistive load to the AC input line voltage. To achieve this, active power factor correction (PFC) can be implimented which, for an AC input line voltage, produces an AC input line current. It is also important to produce a sinusoidal input current which has a low total harmonic distortion (THD) and a high power factor (PF) (See Figure 6).

**Figure 6:** Input Voltage & Current PF=0.96, THD=22%

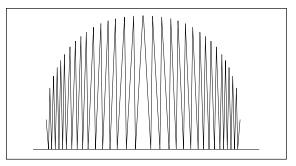

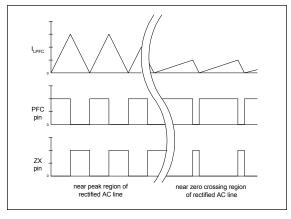

The approach used in the IR2167 is classified as running in critical conduction mode, in which the inductor current discharges to zero with each switching cycle. There is no need to sense the rectified AC line input voltage because it is already sinusoidal. Therefore, the inductor current will naturally follow the sinusoidal voltage envelope as the PFC MOSFET is turned on and off at a much higher frequency (>10KHz) than the line input frequency (50 to 60Hz). The circuit compares the DC Bus voltage to a fixed reference voltage to determine the on-time of the PFC MOSFET. The off-time is determined by the time it takes the LPFC current to drop to zero. This zero current level is detected by a secondary winding in LPFC that is connected to the ZX pin. The result is a system where the switching frequency is freerunning and constantly changing from a high frequency near the zero crossing of the AC input line voltage, to a lower frequency at the peaks. (See Figures 7, 8 & 9).

Figure 7: Inductor Current

Figure 8: Boost Inductor Envelope & Line Voltage

Figure 9: Boost FET On Time vs Line Input

International

TOR Rectifier

### IR2167(S) & PbF

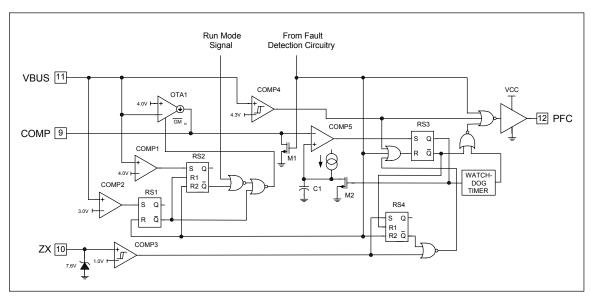

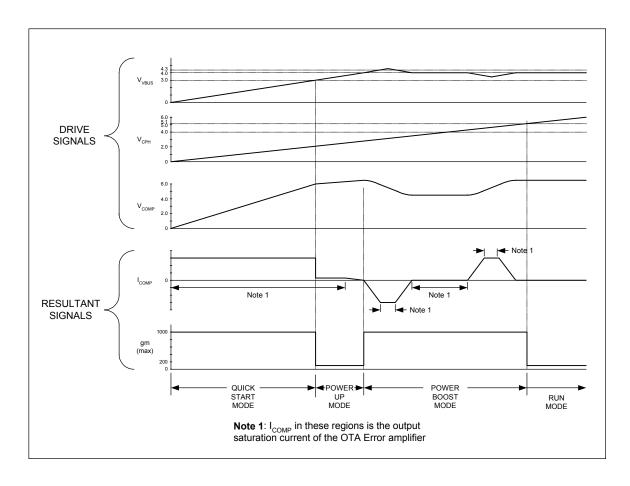

As the external capacitor on the COMP pin begins to charge, the PFC MOSFET on time duration increases. The gain of OTA1 is at its maximum value (See Figures 10 & 11). Maximum gain is desireable to raise the Bus voltage to its nominal value as quickly as possible. When the voltage at the VBUS pin reaches 3V, the gain of OTA1 decreases to its

MOSFET is turned on with minimum on time and LpFC is shorted to ground and begins charging. The PFC MOSFET then turns off and LpFC begins to discharge into the DC BUS capacitor.

COMP4 has a 4.3V threshold with hysteresis so that if the voltage at the VBUS pin overshoots the 4.3V threshold,

Figure 10: PFC Section

nominal value. The BUS voltage continues to increase to its nominal value at which time the voltage measured at the VBUS pin equals 4V. The gain of OTA1 now increases to its maximum value and remains there until the Run mode. This is necessary because if VBUS overshoots its nominal value, the circuit can react quickly to correct the error. Also, during ignition, there is a sudden increase in load current which can cause the Bus voltage to sag. With maximum gain, OTA1 can quickly restore the DC Bus voltage to its nominal value.

When the AC line voltage is applied to the ballast,  $V_{CC}$  rises to 15V. The PFC section is not enabled until the beginning of the Preheat mode of operation. By not enabling the PFC section until the beginning of the Preheat mode, the DC Bus voltage in the ballast is not yet boosted to its nominal running value. This helps alleviate the initial flash of the lamp when the half-bridge driver section first begins to switch.

When the PFC circuit is first enabled, (See Figure 10), the voltage at the VBUS and COMP pins is low. The PFC

the PFC MOSFET will not turn on again until the voltage at the VBUS pin drops to approximately 4.0V. This effectively limits ths maximum bus voltage to approximately 8% greater than the regulated level.

In some instances, the line voltage may be too high. This causes the AC rectified line current to directly charge the DC Bus capacitor without being boosted. Since the current never drops to zero, the ZX pin never goes high and the PFC MOSFET never turns on. The Watch Dog Timer circuit provides a pulse to turn on the PFC MOSFET if no pulse is detected at the ZX pin for 500mS. This enables the PFC circuitry to regulate the DC Bus voltage at its nominal value

Figure 11: PFC Timing Sequence

#### **PFC Over-Current Protection (optional)**

In case of fast on/off interruptions of the mains input voltage or during normal lamp ignition, the DC bus voltage level can decrease below the instantaneous rectified line voltage. Should this occur, the PFC inductor current and PFC MOSFET current can increase to high levels causing the PFC inductor to saturate and/or the PFC MOSFET to become damaged. During fast on/off interruptions of the input mains voltage, the DC bus can drop during the time when the mains voltage is interrupted (off). Since VCC is still above UVLO-, the IC will continue to operate and will increase the COMP pin voltage to increase the PFC MOSFET on-time due to the dropping of the DC bus. When the mains voltage returns again quickly, (before VCC reaches UVLO-), the on-time of the PFC MOSFET is too long for the given mains voltage level resulting in high PFC inductor and MOSFET currents that can saturate the inductor and/or damage the PFC MOSFET (Figure 12).

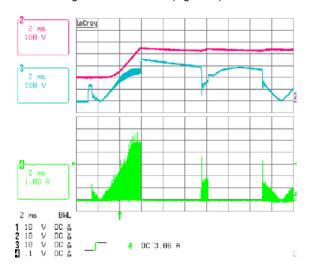

Figure 12, High PFC inductor current during fast mains on/off (upper trace: DC Bus, 100V/div; middle trace: AC line input voltage, 100V/div; lower trace: PFC inductor current 1A/div).

During lamp ignition, the DC bus can drop below the rectified AC line voltage causing current to conduct directly from the output of the rectifier, through the PFC inductor and diode, to the DC bus capacitor. This results in a low-frequency offset of current in the PFC inductor. Since the zero-crossing detection circuit only detects the high-frequency zero-crossing of the inductor current, the PFC MOSFET will turn on again each cycle before the inductor current has reached zero. This causes the PFC to work in a continuous conduction mode and the sum of the low-frequency and high-frequency components of current can saturate the PFC inductor and/ or damage the PFC MOSFET.

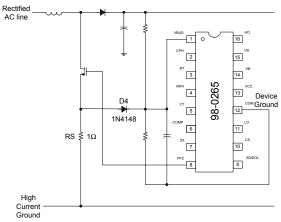

To protect against these conditions, a current sense resistor (RS) can be inserted between the source on the PFC MOSFET and ground, and a diode (D4) connected from the top of this current-sensing resistor to the VBUS pin (Figure 13).

13, External over-current protection circuit

Should high currents occur, the voltage across the currentsensing resistor (RS) will exceed the 4.3V over-voltage protection threshold at the VBUS pin and the PFC MOSFET will turn off safely limiting the current. The watch-dog timer will then restart the PFC as normal (Figure 14). The current sensing resistor value should be selected such that the over-current protection does not false trip during normal operation over the entire line voltage range and load range. A current-sensing resistor value, for example, of 1.0 W will set the over-current protection threshold to about 5 A peak. when the DC bus drops during ignition (the 3V reset on the VBUS pin does not become active until RUN mode). For these reasons, the ballast designer should perform these mains interrupt and ignition tests carefully to determine the robustness of their final design and to decide if this additional over-current protection circuit is necessary.

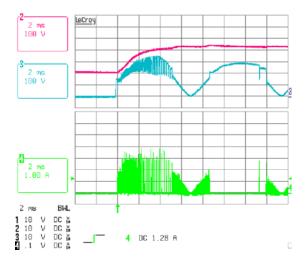

Figure 14, PFC inductor current limited using over-current protection circuit (upper trace: DC Bus, 100V/div; middle trace: AC line input voltage, 100V/div; lower trace: PFC inductor current 1A/div).

The effect that these line and load conditions have on the performance of the ballast depends on the saturation level of the PFC inductor, the selection of the PFC MOSFET, the DC bus capacitor value, the maximum on-time limit set by DZCOMP, and, how fast VCC decreases below UVLO-

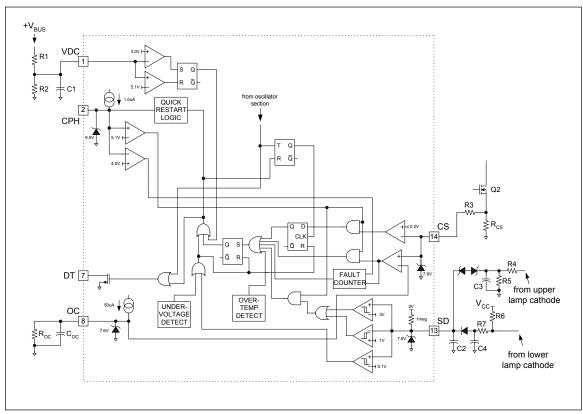

#### **Lamp Protection & Automatic Restart Circuitry Operation**

Figure 15: Lamp Protection & Automatic Restart circuitry block diagram with external component connection

#### Sensing the AC Line Voltage

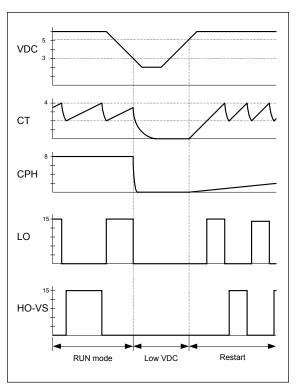

The first of these protection pins senses the voltage on the AC line by means of an external resistor divider (R1, R2 and capacitor C1) and an internal comparator with hysterisis. When power is first supplied to the IC at system startup, three conditions are required before oscillation is initiated: 1.) the voltage on the VCC pin must exceed the rising undervoltage lockout threshold (11.5V), 2.) the voltage at the VDC pin must exceed 5.1V, and 3.) the voltage on the SD pin must be below approximately 4.85V. If a low ac line condition occurs during normal operation, or if power to the ballast is shut off, the ac line will collapse prior to the VCC of

the chip (assuming the VCC is derived from a charge pump off of the output of the half-bridge). In this case, the voltage on the VDC pin will shut the oscillator off, thereby protecting the power transistors from potentially hazardous hard switching. Approximately 2V of hysterisis has been designed into the internal comparator sensing the VDC pin, in order to account for variations in the ac line voltage under varying load conditions. When the ac line recovers, the chip restarts from the beginning of the control sequence, as shown in timing diagram (See Figure 16).

Figure 16: VDC lead fault and auto restart

#### Lamp Presence and End-of-Life Detection

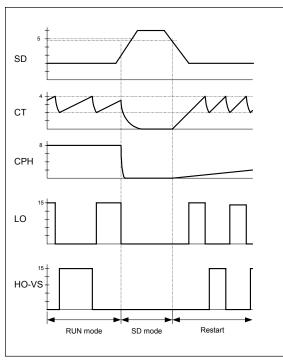

The second protection pin, SD, is used for both shutdown and end-of-life detection. The SD pin would normally be connected to an external circuit that senses the presence of the lamp(s) and the voltage appearing across the lamp(s). An example circuit for a single lamp is shown in Figure 17. During all modes of operation if the SD pin exceeds 5.1V (approximately 150mV of hysterisis is included to increase noise immunity), signaling either a lamp fault or lamp removal, the oscillator is disabled, both gate driver outputs are pulled low, and the chip is put into the micropower mode. Since a lamp fault would normally lead to a lamp exchange, when a new lamp is inserted in the fixture, the SD pin would be pulled back to near ground potential. Under these conditions a reset signal would restart the chip from the beginning of the control sequence, as shown in the timing diagram in Figure 18. Thus, for a lamp removal and replacement, the ballast automatically restarts the lamp in the proper manner.

In the Run mode there are two additional thresholds enabled on the SD pin: 1V and 3V. These thresholds form a window and during normal lamp running the voltage appearing at the SD pin is maintained within these two levels. As a lamp nears its end-of-life, its running voltage will increase and the signal applied to the SD pin detects this by exceeding the window threshold width. The oscillator is disabled, both gate driver outputs are pulled low, and the chip is put into the micropower mode.

Figure 17: Lamp presence detection circuit connection (shaded area)

Figure 18: SD lead fault and auto restart

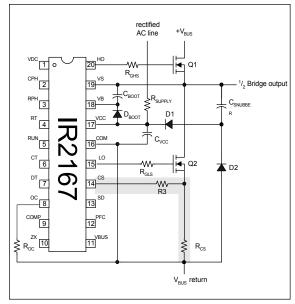

#### **Half-Bridge Current Sensing and Protection**

The third pin used for protection is the CS pin, which is normally connected to a resistor in the source of the lower power MOSFET, as shown in Figure 19. The CS pin is used to sense fault conditions such as failure of a lamp to strike, over-current during normal operation, hard switching, no load, and operation below resonance. If any one of these conditions is sensed, the fault latch is set, the oscillator is disabled, the gate driver outputs go low, and the chip is put into the micropower mode. The CS lead performs its sensing functions on a cycle-by-cycle basis in order to maximize ballast reliability.

For the over-current, failure-to-strike, and hard switching fault conditions, an externally programmable, positive-going CS+ threshold is enabled at the end of the preheat time. The level of this positive-going threshold is determined by the value of the resistor  $R_{\mbox{\scriptsize OC}}$ . The value of the resistor  $R_{\mbox{\scriptsize OC}}$  is determined by the following formula:

$$R_{OC} = \frac{V_{CS^+}}{55E - 6}$$

, or

$$V_{CS} = 55E - 6 \cdot Roc$$

Figure 19: Half-bridge current sensing circuit connection (shaded area)

For the under-current and under-resonance conditions, there is a negative-going CS- threshold of 0.2V which is enabled at the onset of the run mode. The sensing of this CS-threshold is synchronized with the falling edge of the LO outout.

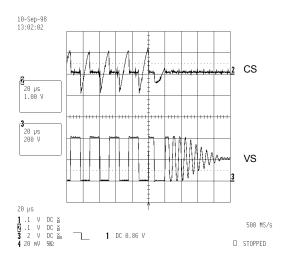

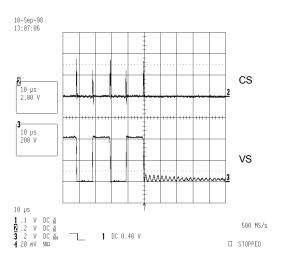

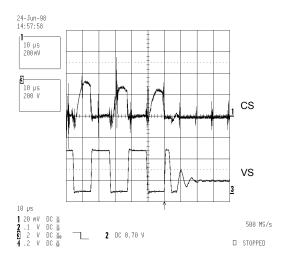

Figures 20, 21 and 22 are oscillographs of fault conditions. Figure 20 shows a failure of the lamp to strike, Figure 21 shows a hard switching condition and Figure 22 shows an under-current condition.

Figure 20: Failure of lamp to strike upper trace CS 1V/div lower trace VS 200V/div

Figure 21: Hard switching condition upper trace CS 2V/div lower trace VS 200V/div

Figure 22: Operation below resonance upper trace CS 200 mV/div lower trace VS 200V/div

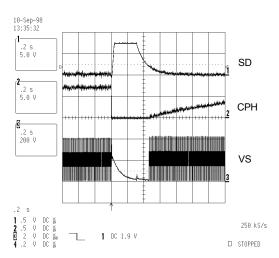

Figure 23: Auto restart for lamp replacement upper trace SD/EOL 5V/div middle trace CPH 5V/div lower trace VS 200V/div

# International TOR Rectifier

### IR2167(S) & PbF

Recovery from such a fault condition is accomplished by cycling either the SD pin or the VCC pin. (See Figure 23). When a lamp is removed, the SD pin goes high, the fault latch is reset, and the chip is held off in an unlatched state. Lamp replacement causes the SD pin to go low again, reinitiating the startup sequence. The fault latch can also be reset by the undervoltage lockout signal, if VCC falls below the lower undervoltage threshold.

#### **Bootstrap Supply Considerations**

Power is normally supplied to the high-side circuitry by means of a simple charge pump from VCC, as shown in Figure 24.

Figure 24 : Typical bootstrap supply connection with VCC charge pump from half-bridge output (shaded area)

A high voltage, fast recovery diode  $D_{BOOT}$  (the so-called bootstrap diode) is connected between VCC (anode) and VB (cathode), and a capacitor  $C_{BOOT}$  (the so-called bootstrap capacitor) is connected between the VB and VS leads. During half-bridge switching, when MOSFET Q2 is on and Q1 is off, the bootstrap capacitor  $C_{BOOT}$  is charged from the VCC decoupling capacitor, through the bootstrap diode  $D_{BOOT}$ , and through Q2. Alternately, when Q2 is off and Q1 is on, the bootstrap diode is reverse-biased, and the bootstrap capacitor (which 'floats' on the source of the upper power MOSFET) serves as the power supply to the upper gate driver CMOS circuitry. Since the quiescent current in

this CMOS circuitry is very low (typically 45 $\mu$ A in the onstate), the majority of the drop in the VBS voltage when Q1 is on occurs due to the transfer of charge from the bootstrap capacitor to the gate of the power MOSFET.

#### **Design Equations**

Note: The results from the following design equations can differ slightly from experimental measurements due to IC tolerances, component tolerances, and oscillator over- and under-shoot due to internal comparator response time.

#### Step 1: Program Maximum Ignition Voltage

Maximum lamp voltage is required during ignition. This will vary depending on the type of lamp, but 1600V is typical for a T8 lamp. As the frequency decreases from the preheat frequency to the resonant frequency, the voltage across the lamp increases. During ignition, only  $R_T$  along with  $C_T$  and  $D_T$  determine the frequency.  $R_{PH}$  and  $R_{RUN}$  are not connected to COM at this time. The value of  $R_T$  should be chosen so that the desired ignition voltage is reached. The RT pin current and timing capacitor charging current are both approximately:

$$I_{CT} = I_{RT} = \frac{2.0V}{R_T}$$

The value of this current should be kept between 50  $\mu$ A and 500  $\mu$ A. The value for C<sub>T</sub> is computed as follows:

$$C_T = \frac{1}{R_T} \left( \frac{1}{2f_{ign}} - td \right)$$

And the ignition mode frequency is:

$$f_{IGN} = \frac{1}{2(R_T C_T + td)}$$

$$R_T = \frac{1}{C_T} \left( \frac{1}{2f_{ign}} - td \right)$$

Deadtime is equal to:

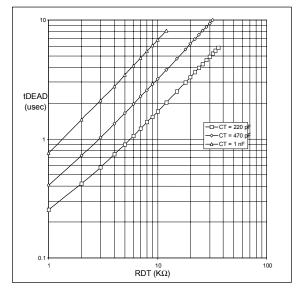

$$td = 0.69 \cdot R_{DT} \cdot C_T$$

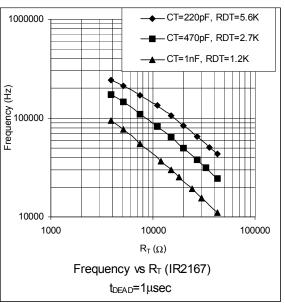

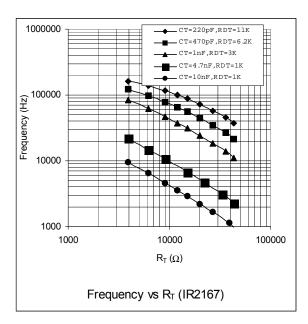

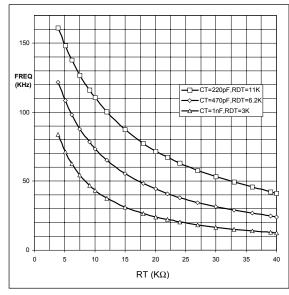

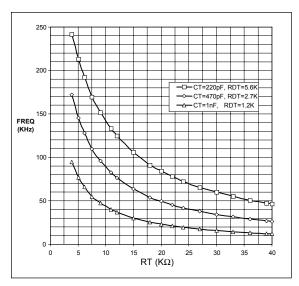

The following graphs, figures 25 and 26, illustrate the relationship between the effective resistance (i.e. the parallel combination of resistors which programs the CT capacitor charging current) and the operating frequency.

Figure 25: f<sub>OSC</sub> vs effective R<sub>T</sub> (t<sub>DEAD</sub>=2.0µsec)

Figure 26:  $f_{OSC}$  vs effective  $R_T$   $(t_{DEAD}$ =1.0 $\mu$ sec)

Figure 27 illustrates the relationship between deadtime vs  $\ensuremath{\mathsf{RDT}}.$

Figure 27: Deadtime vs RDT

# International TOR Rectifier

### IR2167(S) & PbF

#### Step 2: Program Maximum Ignition Current

The ignition current should be limited to the rating of the lamp resonant inductor and the half-bridge MOSFETS. The saturation current of the lamp resonant inductor should be much lower than the current rating of the MOSFETS. Under worst case conditions, the lamp resonant inductor should not be allowed to saturate. This current is controlled by the CS pin and the OC pin. The OC lead has an internal  $50\mu A$  current source. This current through external resistor  $R_{\mbox{OC}}$  determines the threshold on the CS pin.

$$R_{OC} = \frac{V_{CS} + }{55E - 6} or$$

$$V_{cs} + = 55E - 6 -$$

If the current through external resistor R<sub>CS</sub> exceeds a predetermined value, the IC shuts off.

#### Step 3: Program Preheat Frequency

The preheat frequency is determined by the parallel combination of  $R_{PH}$  and  $R_{T}$  along with  $C_{T}$  and  $R_{DT}$ . The frequency should be chosen so that the voltage across the lamp is much lower than the ignition voltage but still provides adequate heating of the filaments. During preheat, the current through the filaments is constant. However, as the filaments heat up, their resistance increases. This results in an increase in the voltage measured across the filaments, which indicates the hot to cold ratio.

$$f_{PH} = \frac{1}{2 \cdot \left(\frac{R_T \cdot R_{PH}}{R_T + R_{PH}} \cdot C_T + td\right)}$$

$$R_{PH} = \frac{\frac{1}{C_T} \left( \frac{1}{2f_{ph}} - td \right)}{1 - \frac{1}{R_T \cdot C_T} \left( \frac{1}{2f_{ph}} - td \right)}$$

4:1 is an acceptable ratio for proper heating

#### Step 4: Program preheat time

The preheat time is determined by external capacitor  $C_{PH}$ . The preheat time required for a 4:1 hot to cold ratio can be observed by measuring the voltage across the filaments. The preheat time is calculated as follows:

$$t_{PH} = 4.0E6 \cdot C_{PH}$$

The IR2167 is held in preheat until CPH is charged to 4.0V.

#### Step 5: Program the ignition mode time

The difference in time between the preheat mode and the run mode is the ignition mode. The rate at which the frequency changes from preheat to run is determined by external resistor RRAMP.

#### Step 6. Program the run frequency

The run mode begins when external resistor  $R_{PH}$  is charged to 5.1V. At this time, the run frequency is determined by the parallel combination of RT and  $R_{RUN}$  along with  $R_{DT}$  and  $C_{T}$ . The run frequency can be programmed above or below the ignition frequency.  $f_{RUN}$  is determined by the following equation:

$$f_{RUN} = \frac{1}{2 \cdot \left(\frac{R_T \cdot R_{RUN}}{R_T + R_{RUN}} \cdot C_T + td\right)}$$

$$R_{RUN} = \frac{\frac{1}{C_T} \left( \frac{1}{2f_{RUN}} - td \right)}{1 - \frac{1}{R_T \cdot C_T} \left( \frac{1}{2f_{RUN}} - td \right)}$$

#### **Component Selection Tips**

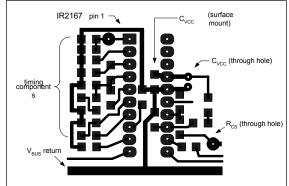

#### Supply Bypassing and pc Board Layout Rules

Component selection and placement on the pc board is extremely important when using power control ICs. VCC should be bypassed to COM as close to the IC terminals as possible with a low ESR/ESL capacitor, as shown in Figure 28.

Figure 28: Supply bypassing PCB layout example

A rule of thumb for the value of this bypass capacitor is to keep its minimum value at least 2500 times the value of the total input capacitance (Ciss) of the power transistors being driven. This decoupling capacitor can be split between a higher valued electrolytic type and a lower valued ceramic type connected in parallel, although a good quality electrolytic (e.g.,  $10\mu F$ ) placed immediately adjacent to the VCC and COM terminals will work well.

In a typical application circuit, the supply voltage to the IC is normally derived by means of a high value startup resistor (1/4W) from the rectified line voltage, in combination with a charge pump from the output of the half-bridge. With this type of supply arrangement, the internal 15.6V zener clamp diode from VCC to COM will determine the steady state IC supply voltage.

#### Connecting the IC Ground (COM) to the Power Ground

Both the low power control circuitry and low side gate driver output stage grounds return to this lead within the IC. The COM lead should be connected to the bottom terminal of the current sense resistor in the source of the low side power MOSFET using an individual pc board trace, as shown in Figure 29. In addition, the ground return path of the timing components and VCC decoupling capacitor should be connected directly to the IC COM lead, and not via separate traces or jumpers to other ground traces on the board.

Figure 29: COM lead connection PCB layout example

These connection techniques prevent high current ground loops from interfering with sensitive timing component operation, and allows the entire control circuit to reject common-mode noise due to output switching.

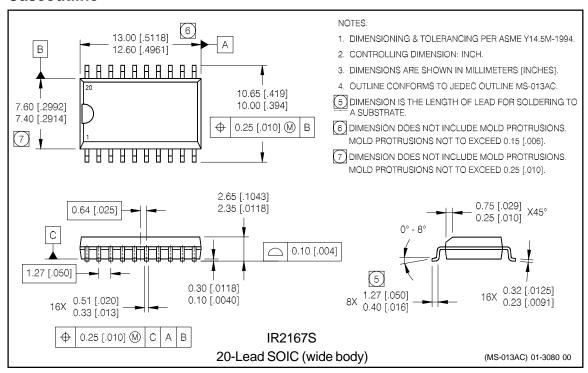

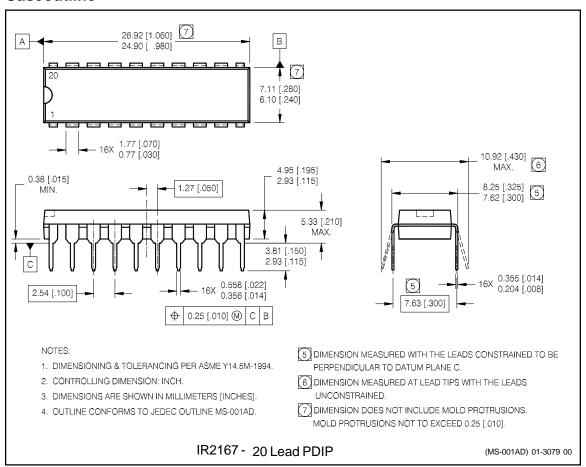

#### Caseoutline

#### Caseoutline

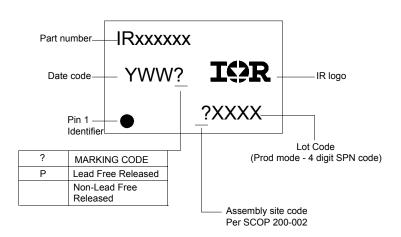

### LEADFREE PART MARKING INFORMATION

### **ORDER INFORMATION**

#### **Basic Part (Non-Lead Free)**

20-Lead SOIC IR2167 order IR2167S 20-Lead PDIP IR2167 order IR2167

#### **Leadfree Part**

20-Lead SOIC IR2167 order IR2167SPbF 20-Lead PDIP IR2167 order IR2167PbF

International

IOR Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 1/29/2006