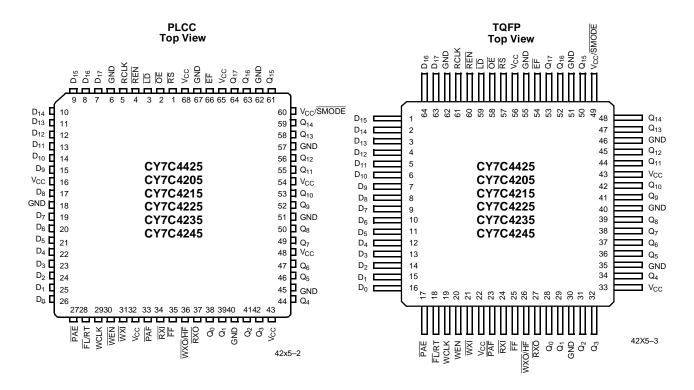

### **Pin Configurations**

### **Selection Guide**

|                                       |             | CY7C42X5-10 | CY7C42X5-15 | CY7C42X5-25 | CY7C42X5-35 |

|---------------------------------------|-------------|-------------|-------------|-------------|-------------|

| Maximum Frequency (MHz)               |             | 100         | 66.7        | 40          | 28.6        |

| Maximum Access Time (n                | s)          | 8           | 10          | 15          | 20          |

| Minimum Cycle Time (ns)               |             | 10          | 15          | 25          | 35          |

| Minimum Data or Enable S              | Set-Up (ns) | 3           | 4           | 6           | 7           |

| Minimum Data or Enable I              | Hold (ns)   | 0.5         | 1           | 1           | 2           |

| Maximum Flag Delay (ns)               |             | 8           | 10          | 15          | 20          |

| Operating Current (I <sub>CC2</sub> ) | Commercial  | 45          | 45          | 45          | 45          |

| (mA) @ freq=20MHz                     | Industrial  | 50          | 50          | 50          | 50          |

|          | CY7C4425                                    | CY7C4205                                    | CY7C4215                                    | CY7C4225                                    | CY7C4235                                    | CY7C4245                                    |

|----------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|

| Density  | 64 x 18                                     | 256 x 18                                    | 512 x 18                                    | 1K x 18                                     | 2K x 18                                     | 4K x 18                                     |

| Packages | 68-pin PLCC<br>64-pin TQFP<br>(10x10/14x14) |

### **Pin Definitions**

| Signal Name       | Description                           | I/O | Function                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0-17</sub> | Data Inputs                           | I   | Data inputs for an 18-bit bus                                                                                                                                                                                                                                                                                                                                                 |

| Q <sub>0-17</sub> | Data Outputs                          | 0   | Data outputs for an 18-bit bus                                                                                                                                                                                                                                                                                                                                                |

| WEN               | Write Enable                          | I   | Enables the WCLK input                                                                                                                                                                                                                                                                                                                                                        |

| REN               | Read Enable                           | I   | Enables the RCLK input                                                                                                                                                                                                                                                                                                                                                        |

| WCLK              | Write Clock                           | I   | The rising edge clocks data into the FIFO when WEN is LOW and the FIFO is not Full. When LD is asserted, WCLK writes data into the programmable flag-offset register.                                                                                                                                                                                                         |

| RCLK              | Read Clock                            | I   | The rising edge clocks data out of the FIFO when REN is LOW and the FIFO is not Empty. When LD is asserted, RCLK reads data out of the programmable flag-off-set register.                                                                                                                                                                                                    |

| WXO/HF            | Write Expansion<br>Out/Half Full Flag | 0   | Dual-Mode Pin: Single device or width expansion - Half Full status flag. Cascaded - Write Expansion Out signal, connected to WXI of next device.                                                                                                                                                                                                                              |

| ĒF                | Empty Flag                            | 0   | When EF is LOW, the FIFO is empty. EF is synchronized to RCLK.                                                                                                                                                                                                                                                                                                                |

| FF                | Full Flag                             | 0   | When FF is LOW, the FIFO is full. FF is synchronized to WCLK.                                                                                                                                                                                                                                                                                                                 |

| PAE               | Programmable<br>Almost Empty          | 0   | When $\overline{\text{PAE}}$ is LOW, the FIFO is almost empty based on the almost-empty offset value programmed into the FIFO. $\overline{\text{PAE}}$ is asynchronous when $V_{CC}/\overline{\text{SMODE}}$ is tied to $V_{CC}$ ; it is synchronized to RCLK when $V_{CC}/\overline{\text{SMODE}}$ is tied to $V_{SS}$ .                                                     |

| PAF               | Programmable<br>Almost Full           | 0   | When $\overline{PAF}$ is LOW, the FIFO is almost full based on the almost full offset value programmed into the FIFO. $\overline{PAF}$ is asynchronous when $V_{CC}/\overline{SMODE}$ is tied to $V_{CC}$ ; it is synchronized to WCLK when $V_{CC}/\overline{SMODE}$ is tied to $V_{SS}$ .                                                                                   |

| LD                | Load                                  | I   | When $\overline{LD}$ is LOW, D <sub>0-17</sub> (O <sub>0-17</sub> ) are written (read) into (from) the programmable-flag-offset register.                                                                                                                                                                                                                                     |

| FL/RT             | First Load/<br>Retransmit             | I   | Dual-Mode Pin: Cascaded - The first device in the daisy chain will have $\overline{FL}$ tied to $V_{SS}$ ; all other devices will have $\overline{FL}$ tied to $V_{CC}$ . In standard mode of width expansion, $\overline{FL}$ is tied to $V_{SS}$ on all devices. Not Cascaded - Tied to $V_{SS}$ . Retransmit function is also available in standalone mode by strobing RT. |

| WXI               | Write Expansion Input                 | I   | Cascaded - Connected to $\overline{WXO}$ of previous device. Not Cascaded - Tied to $V_{SS}$ .                                                                                                                                                                                                                                                                                |

#### Pin Definitions (continued)

| Signal Name            | Description                                       | I/O | Function                                                                                                                                                                                                                            |

|------------------------|---------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXI                    | Read Expansion Input                              | I   | Cascaded - Connected to RXO of previous device.  Not Cascaded - Tied to V <sub>SS</sub> .                                                                                                                                           |

| RXO                    | Read Expansion<br>Output                          | 0   | Cascaded - Connected to RXI of next device.                                                                                                                                                                                         |

| RS                     | Reset                                             | I   | Resets device to empty condition. A reset is required before an initial read or write operation after power-up.                                                                                                                     |

| ŌĒ                     | Output Enable                                     | I   | When $\overline{\text{OE}}$ is LOW, the FIFO's data outputs drive the bus to which they are connected. If $\overline{\text{OE}}$ is HIGH, the FIFO's outputs are in High Z (high-impedance) state.                                  |

| V <sub>CC</sub> /SMODE | Synchronous<br>Almost Empty/<br>Almost Full Flags | I   | Dual-Mode Pin Asynchronous Almost Empty/Almost Full flags - tied to V <sub>CC</sub> . Synchronous Almost Empty/Almost Full flags - tied to V <sub>SS</sub> . (Almost Empty synchronized to RCLK, Almost Full synchronized to WCLK.) |

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature .....-65°C to +150°C Ambient Temperature with Power Applied.....-55°C to +125°C

Supply Voltage to Ground Potential.....-0.5V to +7.0V DC Voltage Applied to Outputs

in High Z State.....-0.5V to +7.0V

DC Input Voltage .....-3.0V to +7.0V

| Output Current into Outputs (LOW)                      | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001V  |

| Latch-Up Current                                       | >200 mA |

### **Operating Range**

| Range                     | Ambient<br>Temperature | v <sub>cc</sub> |

|---------------------------|------------------------|-----------------|

| Commercial                | 0°C to +70°C           | 5V ± 10%        |

| Industrial <sup>[1]</sup> | -40°C to +85°C         | 5V ± 10%        |

### Electrical Characteristics Over the Operating Range<sup>[2]</sup>

|                                      |                                 |                                                     |                                             |      | X5-10           | 7C42 | X5-15           | 7C42 | X5-25    | 7C42X5-35 |          |      |

|--------------------------------------|---------------------------------|-----------------------------------------------------|---------------------------------------------|------|-----------------|------|-----------------|------|----------|-----------|----------|------|

| Parameter                            | Description                     | Test Condit                                         | ions                                        | Min. | Max.            | Min. | Max.            | Min. | Max.     | Min.      | Max.     | Unit |

| V <sub>OH</sub>                      | Output HIGH Voltage             | $V_{CC} = Min.,$<br>$I_{OH} = -2.0 \text{ mA}$      | $V_{CC} = Min.,$ $I_{OH} = -2.0 \text{ mA}$ |      |                 | 2.4  |                 | 2.4  |          | 2.4       |          | V    |

| V <sub>OL</sub>                      | Output LOW Voltage              | $V_{CC} = Min.,$<br>$I_{OL} = 8.0 \text{ mA}$       |                                             |      | 0.4             |      | 0.4             |      | 0.4      |           | 0.4      | V    |

| V <sub>IH</sub> [3]                  | Input HIGH Voltage              |                                                     |                                             | 2.2  | V <sub>CC</sub> | 2.2  | V <sub>CC</sub> | 2.2  | $V_{CC}$ | 2.2       | $V_{CC}$ | V    |

| V <sub>IL</sub> [3]                  | Input LOW Voltage               |                                                     |                                             |      | 0.8             | -3.0 | 0.8             | -3.0 | 0.8      | -3.0      | 0.8      | V    |

| I <sub>IX</sub>                      | Input Leakage<br>Current        | V <sub>CC</sub> = Max.                              | V <sub>CC</sub> = Max.                      |      | +10             | -10  | +10             | -10  | +10      | -10       | +10      | μΑ   |

| l <sub>OS</sub> <sup>[4]</sup>       | Output Short<br>Circuit Current | $V_{CC} = Max.,$<br>$V_{OUT} = GND$                 |                                             | -90  |                 | -90  |                 | -90  |          | -90       |          | mA   |

| I <sub>OZL</sub><br>I <sub>OZH</sub> | Output OFF,<br>High Z Current   | $\overline{OE} \ge V_{IH},$<br>$V_{SS} < V_O < V_C$ | С                                           | -10  | +10             | -10  | +10             | -10  | +10      | -10       | +10      | μА   |

| I <sub>CC2</sub> <sup>[5]</sup>      | Operating Current               | V <sub>CC</sub> = Max.,                             | Com'l                                       |      | 45              |      | 45              |      | 45       |           | 45       | mA   |

|                                      |                                 | $I_{OUT} = 0 \text{ mA}$                            | Ind                                         |      | 50              |      | 50              |      | 50       |           | 50       | mA   |

| I <sub>SB</sub> <sup>[6]</sup>       | Standby Current                 | V <sub>CC</sub> = Max.,                             | Com'l                                       |      | 10              |      | 10              |      | 10       |           | 10       | mA   |

|                                      |                                 | $I_{OUT} = 0 \text{ mA}$                            | Ind                                         |      | 15              |      | 15              |      | 15       |           | 15       | mA   |

- T<sub>A</sub> is the "instant on" case temperature.

See the last page of this specification for Group A subgroup testing information.

The V<sub>IH</sub> and V<sub>IL</sub> specifications apply for all inputs except WXI, RXI. The WXI, RXI pin is not a TTL input. It is connected to either RXO, WXO of the previous device or V<sub>SS</sub>.

Test no more than one output at a time for not more than one second.

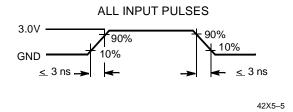

Input signals switch from 0V to 3V with a rise/fall time less than 3 ns, clocks and clock enables switch at 20 MHz, while the data inputs switch at 10 MHz.

Outputs are unloaded.

- Outputs are unloaded.

All input signals are connected to V<sub>CC</sub>. All outputs are unloaded.

## Capacitance<sup>[7]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 5    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 7    | pF   |

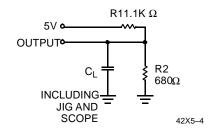

## AC Test Loads and Waveforms<sup>[8, 9]</sup>

THÉVENIN EQUIVALENT Equivalent to:

> $410\Omega$ OUTPUT -**-•** 1.91V

### Switching Characteristics Over the Operating Range

|                   |                                                   | 7C42 | 7C42X5-10 |      | 7C42X5-15 |      | 7C42X5-25 |      | 7C42X5-35 |      |

|-------------------|---------------------------------------------------|------|-----------|------|-----------|------|-----------|------|-----------|------|

| Parameter         | Description                                       | Min. | Max.      | Min. | Max.      | Min. | Max.      | Min. | Max.      | Unit |

| t <sub>S</sub>    | Clock Cycle Frequency                             |      | 100       |      | 66.7      |      | 40        |      | 28.6      | MHz  |

| t <sub>A</sub>    | Data Access Time                                  | 2    | 8         | 2    | 10        | 2    | 15        | 2    | 20        | ns   |

| t <sub>CLK</sub>  | Clock Cycle Time                                  | 10   |           | 15   |           | 25   |           | 35   |           | ns   |

| t <sub>CLKH</sub> | Clock HIGH Time                                   | 4.5  |           | 6    |           | 10   |           | 14   |           | ns   |

| t <sub>CLKL</sub> | Clock LOW Time                                    | 4.5  |           | 6    |           | 10   |           | 14   |           | ns   |

| t <sub>DS</sub>   | Data Set-Up Time                                  | 3    |           | 4    |           | 6    |           | 7    |           | ns   |

| t <sub>DH</sub>   | Data Hold Time                                    | 0.5  |           | 1    |           | 1    |           | 2    |           | ns   |

| t <sub>ENS</sub>  | Enable Set-Up Time                                | 3    |           | 4    |           | 6    |           | 7    |           | ns   |

| t <sub>ENH</sub>  | Enable Hold Time                                  | 0.5  |           | 1    |           | 1    |           | 2    |           | ns   |

| t <sub>RS</sub>   | Reset Pulse Width <sup>[10]</sup>                 | 10   |           | 15   |           | 25   |           | 35   |           | ns   |

| t <sub>RSR</sub>  | Reset Recovery Time                               | 8    |           | 10   |           | 15   |           | 20   |           | ns   |

| t <sub>RSF</sub>  | Reset to Flag and Output Time                     |      | 10        |      | 15        |      | 25        |      | 35        | ns   |

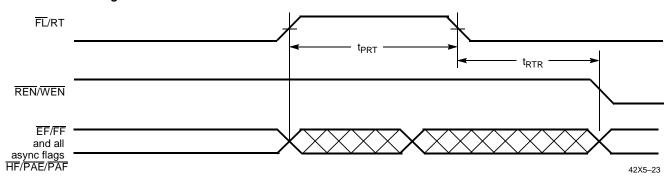

| t <sub>PRT</sub>  | Retransmit Pulse Width                            | 12   |           | 15   |           | 25   |           | 35   |           | ns   |

| t <sub>RTR</sub>  | Retransmit Recovery Time                          | 12   |           | 15   |           | 25   |           | 35   |           | ns   |

| t <sub>OLZ</sub>  | Output Enable to Output in Low Z <sup>[11]</sup>  | 0    |           | 0    |           | 0    |           | 0    |           | ns   |

| t <sub>OE</sub>   | Output Enable to Output Valid                     | 3    | 7         | 3    | 8         | 3    | 12        | 3    | 15        | ns   |

| t <sub>OHZ</sub>  | Output Enable to Output in High Z <sup>[11]</sup> | 3    | 7         | 3    | 8         | 3    | 12        | 3    | 15        | ns   |

| t <sub>WFF</sub>  | Write Clock to Full Flag                          |      | 8         |      | 10        |      | 15        |      | 20        | ns   |

| t <sub>REF</sub>  | Read Clock to Empty Flag                          |      | 8         |      | 10        |      | 15        |      | 20        | ns   |

- Tested initially and after any design or process changes that may affect these parameters.

C<sub>L</sub> = 30 pF for all AC parameters except for t<sub>OHZ</sub>.

C<sub>L</sub> = 5 pF for t<sub>OHZ</sub>.

Pulse widths less than minimum values are not allowed.

Values guaranteed by design, not currently tested.

### Switching Characteristics Over the Operating Range (continued)

|                        |                                                                                                                              | 7C42 | X5-10 | 7C42X5-15 |      | 7C42X5-25 |      | 7C42X5-35 |      |      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------|------|-----------|------|-----------|------|------|

| Parameter              | Description                                                                                                                  | Min. | Max.  | Min.      | Max. | Min.      | Max. | Min.      | Max. | Unit |

| t <sub>PAFasynch</sub> | Clock to Programmable Almost-Full Flag <sup>[12]</sup> (Asynchronous mode, V <sub>CC</sub> /SMODE tied to V <sub>CC</sub> )  |      | 12    |           | 16   |           | 20   |           | 25   | ns   |

| t <sub>PAFsynch</sub>  | Clock to Programmable Almost-Full Flag (Synchronous mode, V <sub>CC</sub> /SMODE tied to V <sub>SS</sub> )                   |      | 8     |           | 10   |           | 15   |           | 20   | ns   |

| <sup>t</sup> PAEasynch | Clock to Programmable Almost-Empty Flag <sup>[12]</sup> (Asynchronous mode, V <sub>CC</sub> /SMODE tied to V <sub>CC</sub> ) |      | 12    |           | 16   |           | 20   |           | 25   | ns   |

| t <sub>PAEsynch</sub>  | Clock to Programmable Almost-Full Flag (Synchronous mode, V <sub>CC</sub> /SMODE tied to V <sub>SS</sub> )                   |      | 8     |           | 10   |           | 15   |           | 20   | ns   |

| t <sub>HF</sub>        | Clock to Half-Full Flag                                                                                                      |      | 12    |           | 16   |           | 20   |           | 25   | ns   |

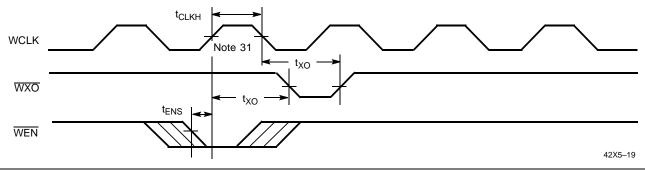

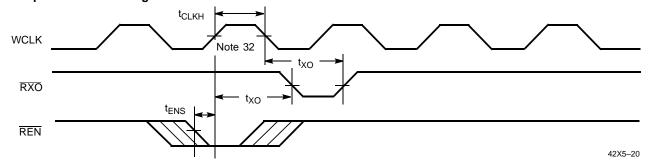

| t <sub>XO</sub>        | Clock to Expansion Out                                                                                                       |      | 7     |           | 10   |           | 15   |           | 20   | ns   |

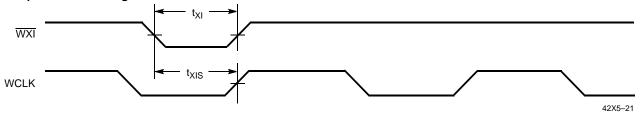

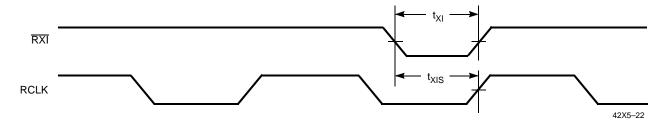

| t <sub>XI</sub>        | Expansion in Pulse Width                                                                                                     | 3    |       | 6.5       |      | 10        |      | 14        |      | ns   |

| t <sub>XIS</sub>       | Expansion in Set-Up Time                                                                                                     | 4.5  |       | 5         |      | 10        |      | 15        |      | ns   |

| t <sub>SKEW1</sub>     | Skew Time between Read Clock and Write Clock for Full Flag                                                                   | 5    |       | 6         |      | 10        |      | 12        |      | ns   |

| t <sub>SKEW2</sub>     | Skew Time between Read Clock and Write Clock for Empty Flag                                                                  | 5    |       | 6         |      | 10        |      | 12        |      | ns   |

| t <sub>SKEW3</sub>     | Skew Time between Read Clock and Write Clock for Programmable Almost Empty and Programmable Almost Full Flags.               | 10   |       | 15        |      | 18        |      | 20        |      | ns   |

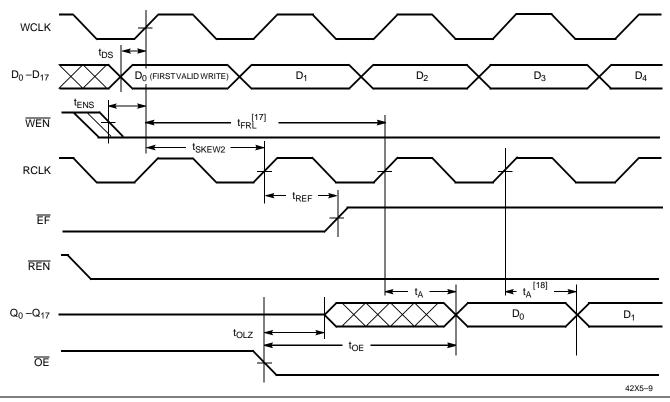

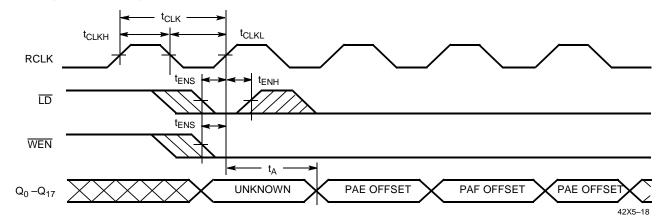

### **Switching Waveforms**

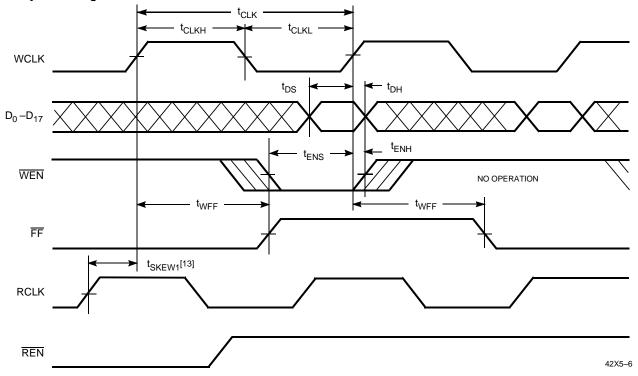

### Write Cycle Timing

PAFasynch, tpaEasynch, after program register write will not be valid until 5 ns + tpAF(E).

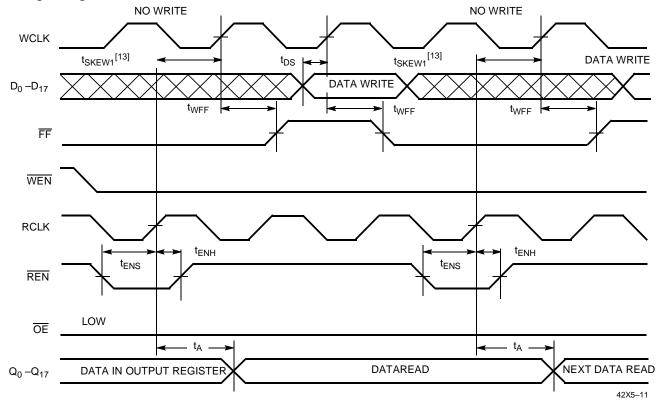

t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, then FF may not change state until the next WCLK edge.

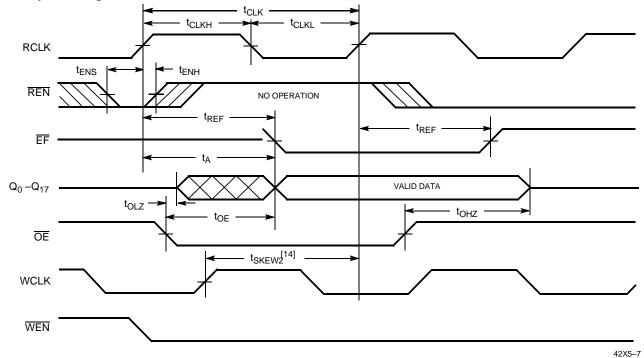

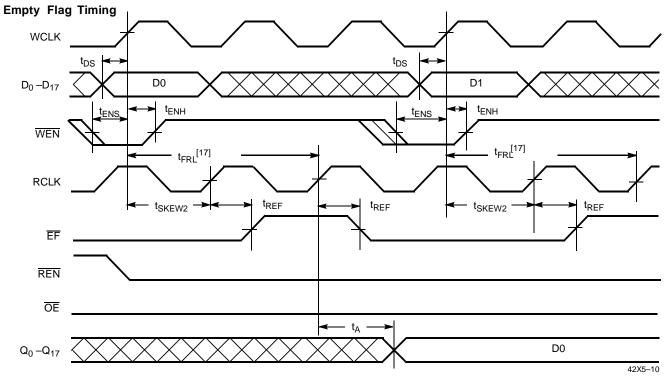

### **Read Cycle Timing**

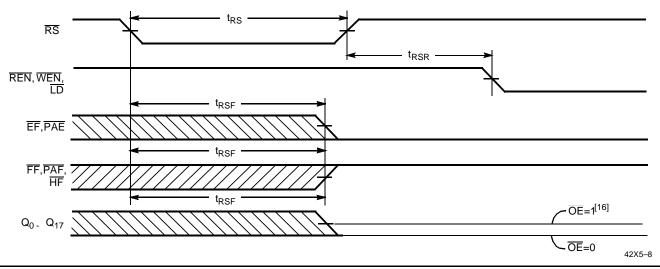

### Reset Timing<sup>[15]</sup>

- 14. .t<sub>SKEW2</sub> is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that EF will go HIGH during the current clock cycle. It the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW2</sub>, then EF may not change state until the next RCLK edge.

15. The clocks (RCLK, WCLK) can be free-running during reset.

16. After reset, the outputs will be LOW if OE = 0 and three-state if OE = 1.

#### First Data Word Latency after Reset with Simultaneous Read and Write

<sup>17.</sup> When t<sub>SKEW2</sub> ≥ minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW2</sub>. When t<sub>SKEW2</sub> < minimum specification, t<sub>FRL</sub> (maximum) = either 2\*t<sub>CLK</sub> + t<sub>SKEW2</sub> or t<sub>CLK</sub> + t<sub>SKEW2</sub>. The Latency Timing applies only at the Empty Boundary (EF = LOW).

18. The first word is available the cycle after EF goes HIGH, always.

#### **Full Flag Timing**

### **Half-Full Flag Timing**

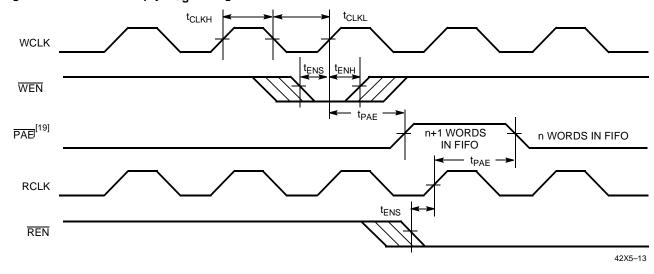

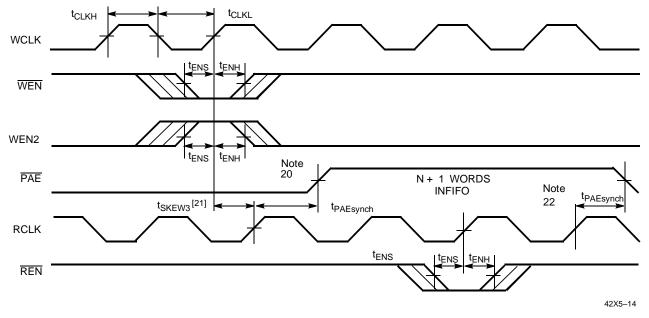

#### **Programmable Almost Empty Flag Timing**

### Programmable Almost Empty Flag Timing (applies only in SMODE (SMODE is LOW)

- 19. PAE offset n. Number of data words into FIFO already = n.

- PAE offset n.

PAE offset n.

PAE offset n.

t<sub>SKEW3</sub> is the minimum time between <u>a rising</u> WCLK and a rising RCLK edge for <u>PAE</u> to change state during that clock cycle. If the time between the edge of WCLK and the rising RCLK is less than t<sub>SKEW3</sub>, then <u>PAE</u> may not change state until the next RCLK.

If a read is performed on this rising edge of the read clock, there will be Empty + (n 1) words in the FIFO when <u>PAE</u> goes LOW.

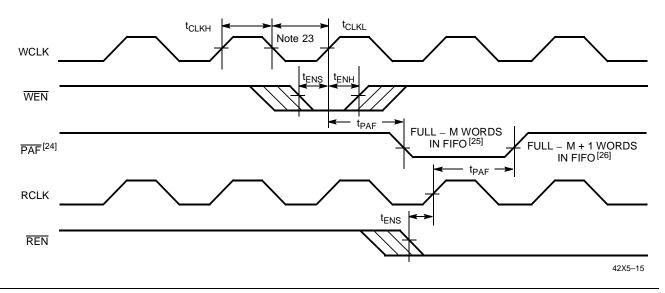

#### **Programmable Almost Full Flag Timing**

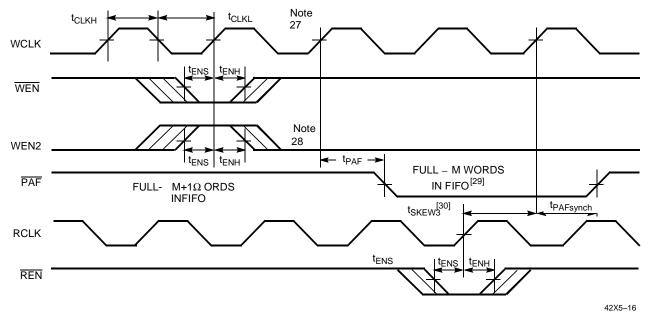

### Programmable Almost Full Flag Timing (applies only in SMODE (SMODE in LOW))

- 23. PAF offset = m. Number of data words written into FIFO already = 64 m + 1 for the CY7C425, 256 m + 1 for the CY7C4205, 512 m + 1 for the CY7C4215. 1024 m + 1 for the CY7C4225, 2048 m + 1 for the CY7C4235, and 4096 m + 1 for the CY7C4245.

- 24. PAF is offset = m. 25. 64 m words in CY7C4225, 256 m words in CY7C4205, 512 m word in CY7C4215. 1024 m words in CY7C4225, 2048 m words in CY7C4235, and 4096 m words in CY7C4245

- 4096 m words in CY7C4245.

26. 64 m + 1 words in CY7C425, 256 m + 1 words in CY7C4205, 512 m +1 words in CY7C4215, 1024 m + 1 CY7C4225, 2048 m + 1 in CY74235, and 4096 m + 1 words in CY7C4245.

- 27. If a write is performed on this rising edge of the write clock, there will be Full (m 1) words of the FIFO when PAF goes LOW.

- 28. PAF offset = m.

- 20. 14 oilset = 111. 29. 64 - m words in CY7C425, 256 - m words in FIFO for CY7C4205, 512 - m word in CY7C4215. 1024 - m words in CY7C4225, 2048 - m words in CY7C4235, and 4096 - m words in CY7C4245

- and 4096 m words in CY7C4245.

t<sub>SKEW3</sub> is the minimum time between a rising RCLK and a rising WCLK edge for PAF to change state during that clock cycle. If the time between the edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW3</sub>, then PAF may not change state until the next WCLK rising edge.

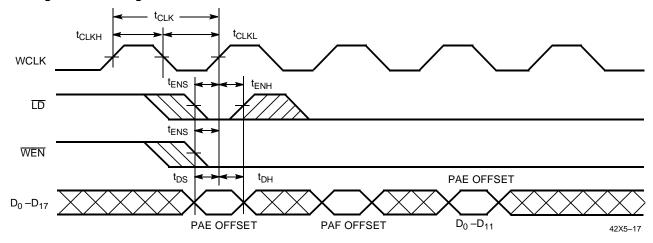

### Write Programmable Registers

### Read Programmable Registers

### Write Expansion Out Timing

### Note:

31. Write to Last Physical Location.

#### **Read Expansion Out Timing**

#### Write Expansion In Timing

#### **Read Expansion In Timing**

## $\textbf{Retransmit Timing}^{[33,\ 34,\ 35]}$

- Read from Last Physical Location.

Clocks are free running in this case.

The flags may change state during Retransmit as a result of the offset of the read and write pointers, but flags will be valid at t<sub>RTR</sub>. For the synchronous PAE and PAF flags (SMODE), an appropriate clock cycle is necessary after t<sub>RTR</sub> to update these flags.

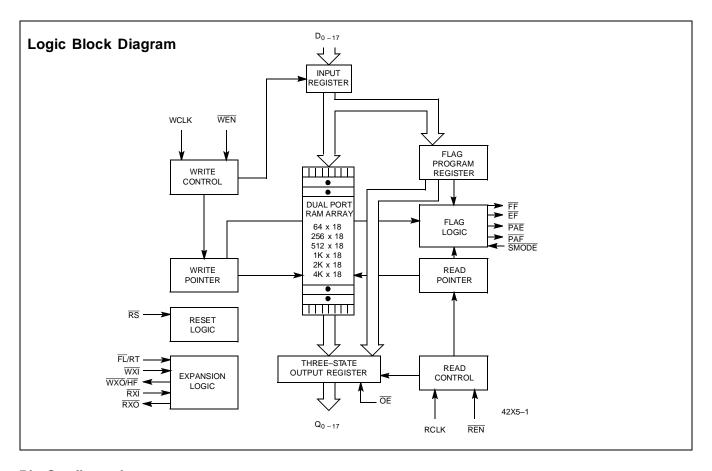

#### **Architecture**

The CY7C42X5 consists of an array of 64 to 4K words of 18 bits each (implemented by a dual-port array of SRAM cells), a read pointer, a write pointer, control signals (RCLK, WCLK, REN, WEN, RS), and flags (EF, PAE, HF, PAF, FF). The CY7C42X5 also includes the control signals WXI, RXI, WXO, RXO for depth expansion.

#### Resetting the FIFO

Upon power-up, the FIFO must be reset with a Reset  $(\overline{RS})$  cycle. This causes the FIFO to enter the Empty condition signified by  $\overline{EF}$  being LOW. All data outputs go LOW after the falling edge of  $\overline{RS}$  only if  $\overline{OE}$  is asserted. In order for the FIFO to reset to its default state, a falling edge must occur on  $\overline{RS}$  and the user must not read or write while  $\overline{RS}$  is LOW.

#### **FIFO Operation**

When the  $\overline{WEN}$  signal is active (LOW), data present on the D<sub>0-17</sub> pins is written into the FIFO on each rising edge of the WCLK signal. Similarly, when the  $\overline{REN}$  signal is active LOW, data in the FIFO memory will be presented on the Q<sub>0-17</sub> outputs. New data will be presented on each rising edge of RCLK while  $\overline{REN}$  is active LOW and  $\overline{OE}$  is LOW.  $\overline{REN}$  must set up t<sub>ENS</sub> before RCLK for it to be a valid read function.  $\overline{WEN}$  must occur tENS before WCLK for it to be a valid write function.

An output enable  $(\overline{OE})$  pin is provided to three-state the  $Q_{0-17}$  outputs when  $\overline{OE}$  is deasserted. When  $\overline{OE}$  is enabled (LOW), data in the output register will be available to the  $Q_{0-17}$  outputs after  $t_{OE}$ . If devices are cascaded, the  $\overline{OE}$  function will only output data on the FIFO that is read enabled.

The FIFO contains overflow circuitry to disallow additional writes when the FIFO is full, and underflow circuitry to disallow additional reads when the FIFO is empty. An empty FIFO maintains the data of the last valid read on its  $Q_{0-17}$  outputs even after additional reads occur.

#### **Programming**

The CY7C42X5 devices contain two 12-bit offset registers. Data present on D<sub>0-11</sub> during a program write will determine the distance from Empty (Full) that the Almost Empty (Almost Full) flags become active. If the user elects not to program the FIFO's flags, the default offset values are used (see *Table 2*). When the Load  $\overline{LD}$  pin is set LOW and  $\overline{WEN}$  is set LOW, data on the inputs  $D_{0-11}$  is written into the Empty offset register on the first LOW-to-HIGH transition of the write clock (WCLK). When the  $\overline{LD}$  pin and  $\overline{WEN}$  are held LOW then data is written into the Full offset register on the second LOW-to-HIGH transition of the write clock (WCLK). The third transition of the write clock (WCLK) again writes to the Empty offset register (see Table 1). Writing all offset registers does not have to occur at one time. One or two offset registers can be written and then, by bringing the  $\overline{LD}$  pin HIGH, the FIFO is returned to normal read/write operation. When the LD pin is set LOW, and WEN is LOW, the next offset register in sequence is written.

The contents of the offset registers can be read on the output lines when the  $\overline{LD}$  pin is set LOW and  $\overline{REN}$  is set LOW; then, data can be read on the LOW-to-HIGH transition of the read clock (RCLK).

Table 1. Write Offset Register

| LD | WEN | WCLK <sup>[36]</sup> | Selection                                             |

|----|-----|----------------------|-------------------------------------------------------|

| 0  | 0   |                      | Writing to offset registers: Empty Offset Full Offset |

| 0  | 1   |                      | No Operation                                          |

| 1  | 0   |                      | Write Into FIFO                                       |

| 1  | 1   |                      | No Operation                                          |

Note:

#### **Flag Operation**

The CY7C42X5 devices provide five flag pins to indicate the condition of the FIFO contents. Empty and Full are synchronous.  $\overline{\text{PAE}}$  and  $\overline{\text{PAF}}$  are synchronous if  $V_{CC}/\overline{\text{SMODE}}$  is tied to  $V_{SS}$ .

#### **Full Flag**

The Full Flag (FF) will go LOW when device is Full. Write operations are inhibited whenever FF is LOW regardless of the state of WEN. FF is synchronized to WCLK, i.e., it is exclusively updated by each rising edge of WCLK.

#### **Empty Flag**

The Empty Flag ( $\overline{\text{EF}}$ ) will go LOW when the device is empty. Read operations are inhibited whenever  $\overline{\text{EF}}$  is LOW, regardless of the state of  $\overline{\text{REN}}$ .  $\overline{\text{EF}}$  is synchronized to RCLK, i.e., it is exclusively updated by each rising edge of RCLK.

#### Programmable Almost Empty/Almost Full Flag

The CY7C42X5 features programmable Almost Empty and Almost Full Flags. Each flag can be programmed (described in the Programming section) a specific distance from the corresponding boundary flags (Empty or Full). When the FIFO contains the number of words or fewer for which the flags have been programmed, the PAF or PAE will be asserted, signifying that the FIFO is either Almost Full or Almost Empty. See *Table 2* for a description of programmable flags.

When the SMODE pin is tied LOW, the PAF flag signal transition is caused by the rising edge of the write clock and the PAE flag transition is caused by the rising edge of the read clock.

#### Retransmit

The retransmit feature is beneficial when transferring packets of data. It enables the receipt of data to be acknowledged by the receiver and retransmitted if necessary.

The Retransmit (RT) input is active in the standalone and width expansion modes. The retransmit feature is intended for use when a number of writes equal to or less than the depth of the FIFO have occurred since the last  $\overline{\text{RS}}$  cycle. A HIGH pulse on RT resets the internal read pointer to the first physical location of the FIFO. WCLK and RCLK may be free running but must be disabled during and  $t_{\text{RTR}}$  after the retransmit pulse. With

The same selection sequence applies to reading from the registers. REN is enabled and read is performed on the LOW-to-HIGH transition of RCLK.

every valid read cycle after retransmit, previously accessed data is read and the read pointer is incremented until it is equal to the write pointer. Flags are governed by the relative locations of the read and write pointers and are updated during a retransmit cycle. Data written to the FIFO after activation of RT are transmitted also.

The full depth of the FIFO can be repeatedly retransmitted.

Table 2. Flag Truth Table.

|                         | Number of Words in FIFO          |                                  |    |     |    |     |    |

|-------------------------|----------------------------------|----------------------------------|----|-----|----|-----|----|

| 7C4425 - 64 x 18        | 7C4205 - 256 x 18                | 7C4215 - 512 x 18                | FF | PAF | HF | PAE | EF |

| 0                       | 0                                | 0                                | Н  | Н   | Н  | L   | L  |

| 1 to n <sup>[37</sup>   | 1 to n <sup>[37]</sup>           | 1 to n <sup>[37]</sup>           | Н  | Н   | Н  | L   | Н  |

| (n+1) to 32             | (n+1) to 128                     | (n+1) to 256                     | Н  | Н   | Н  | Н   | Н  |

| 33 to (64 – (m+1))      | 129 to (256 – (m+1))             | 257 to (512 – (m+1))             | Н  | Н   | L  | Н   | Н  |

| $(64 - m)^{[38]}$ to 63 | (256 – m) <sup>[38]</sup> to 255 | (512 – m) <sup>[38]</sup> to 511 | Н  | L   | L  | Н   | Н  |

| 64                      | 256                              | 512                              | L  | L   | L  | Н   | Н  |

| Number of Words in FIFO            |                                    |                             |    |     |    |     |    |

|------------------------------------|------------------------------------|-----------------------------|----|-----|----|-----|----|

| 7C4225 - 1K x 18                   | 7C4235 - 2K x 18                   | 7C4245 - 4K x 18            | FF | PAF | HF | PAE | EF |

| 0                                  | 0                                  | 0                           | Н  | Н   | Н  | L   | L  |

| 1 to n <sup>[37]</sup>             | 1 to n <sup>[37]</sup>             | 1 to n <sup>[37]</sup>      | Н  | Н   | Н  | L   | Н  |

| (n+1) to 512                       | (n+1) to 1024                      | (n+1) to 2048               | Н  | Н   | Н  | Н   | Н  |

| 513 to (1024 – (m+1))              | 1025 to (2048 – (m+1))             | 2049 to (4096 – (m+1))      | Н  | Н   | L  | Н   | Н  |

| (1024 – m) <sup>[38]</sup> to 1023 | (2048 – m) <sup>[38]</sup> to 2047 | $(4096 - m)^{[38]}$ to 4095 | Н  | L   | L  | Н   | Н  |

| 1024                               | 2048                               | 4096                        | L  | L   | L  | Н   | Н  |

#### Notes:

37. n = Empty Offset (Default Values: CY7C4425 n = 7, CY7C4205 n = 31, CY7C4215 n = 63, CY7C4225/7C4235/7C4245 n = 127).

38. m = Full Óffset (Default Values: CY7C4425 n = 7, CY7C4205 n = 31, CY7C4215 n = 63, CY7C4225/7C4235/7C4245 n = 127).

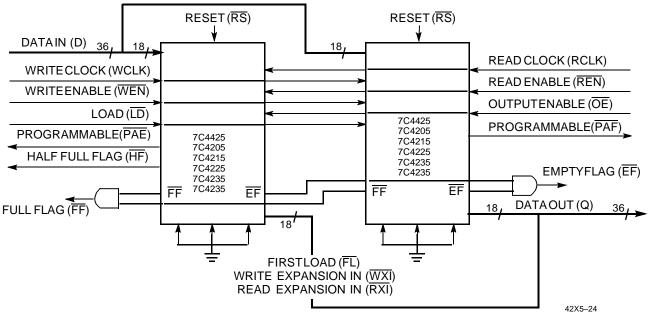

#### **Width Expansion Configuration**

The CY7C42X5 can be expanded in width to provide word widths greater than 18 in increments of 18. During width expansion mode all control line inputs are common and all flags

are available. Empty (Full) flags should be created by ANDing the Empty (Full) flags of every FIFO. This technique will avoid ready data from the FIFO that is "staggered" by one clock cycle due to the variations in skew between RCLK and WCLK. Figure 1 demonstrates a 36-word width by using two CY7C42X5.

Figure 1. Block Diagram of 64x36/256 x 36/512 x 36/1024 x 36/2048 x 36/4096 x 36 Synchronous FIFO Memory Used in a Width Expansion Configuration

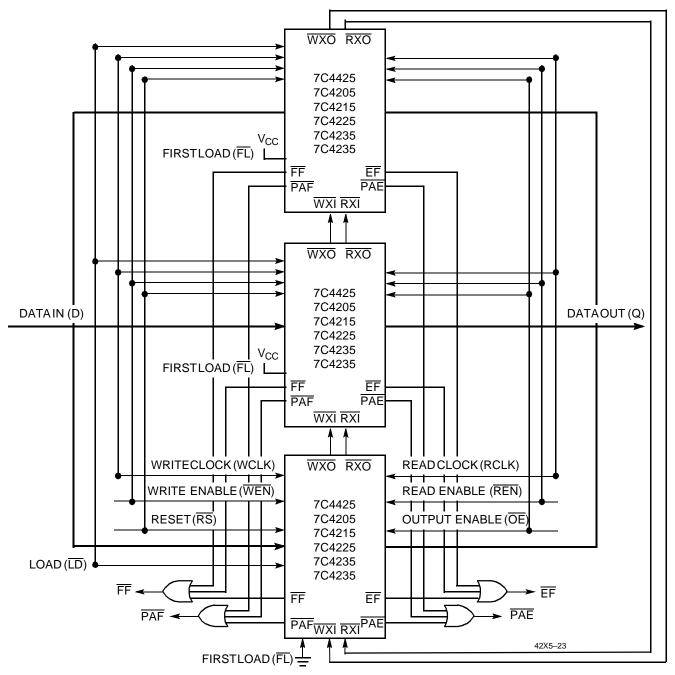

# Depth Expansion Configuration (with Programmable Flags)

The CY7C42X5 can easily be adapted to applications requiring more than 64/256/512/1024/2048/4096 words of buffering. *Figure 2* shows Depth Expansion using three CY7C42X5s. Maximum depth is limited only by signal loading. Follow these steps:

- The first device must be designated by grounding the First Load (FL) control input.

- 2. All other devices must have FL in the HIGH state.

- 3. The Write Expansion Out (WXO) pin of each device must be tied to the Write Expansion In (WXI) pin of the next device.

- 4. The Read Expansion Out (RXO) pin of each device must be tied to the Read Expansion In (RXI) pin of the next device.

- 5. All Load (LD) pins are tied together.

- The Half-Full Flag (HF) is not available in the Depth Expansion Configuration.

- 7. EF, FF, PAE, and PAF are created with composite flags by ORing together these respective flags for monitoring. The composite PAE and PAF flags are not precise.

Figure 2. Block Diagram of 192 x 18/768 x 18/1536 x 18/3072 x 18/12288 x 18 Synchronous FIFO Memory with Programmable Flags used in Depth Expansion Configuration

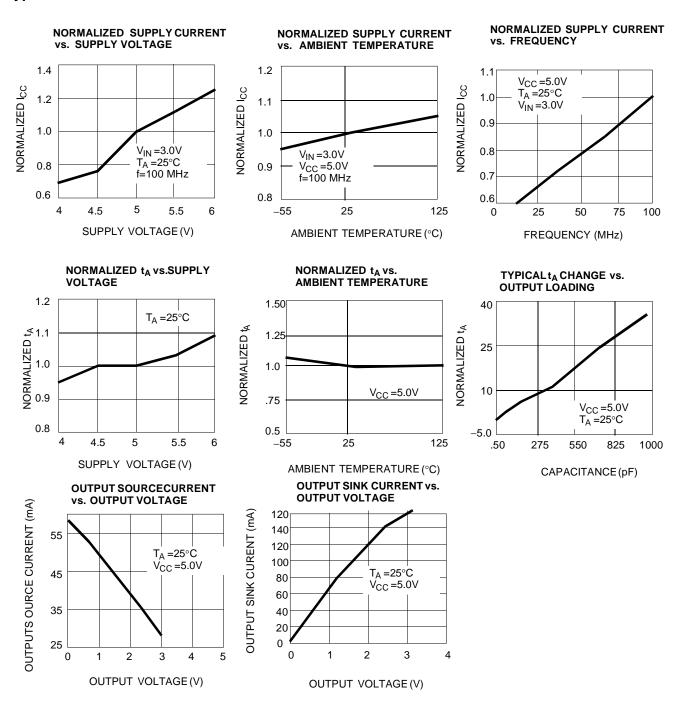

### Typical AC and DC Characteristics

## **Ordering Information**

### 64 x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4425-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4425-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4425-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4425-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4425-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4425-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 15            | CY7C4425-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4425-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4425-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4425-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4425-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4425-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 25            | CY7C4425-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4425-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4425-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

|               | CY7C4425-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4425-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4425-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

| 35            | CY7C4425-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4425-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4425-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4425-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4425-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4425-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

### 256 x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4205-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4205-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4205-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4205-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 15            | CY7C4205-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4205-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4205-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4205-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 25            | CY7C4205-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4205-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4205-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4205-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 35            | CY7C4205-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4205-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4205-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4205-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4205-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

### 512 x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4215-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4215-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4215-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4215-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 15            | CY7C4215-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4215-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4215-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4215-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 25            | CY7C4215-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4215-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4215-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4215-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4215-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 35            | CY7C4215-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4215-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4215-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

|               | CY7C4215-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4215-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4215-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

### 1K x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4225-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4225-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4225-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4225-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4225-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4225-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 15            | CY7C4225-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4225-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4225-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4225-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4225-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4225-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 25            | CY7C4225-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4225-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4225-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4225-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4225-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4225-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 35            | CY7C4225-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4225-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4225-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

|               | CY7C4225-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4225-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4225-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

### 2K x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4235-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4235-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4235-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4235-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 15            | CY7C4235-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4235-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4235-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4235-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 25            | CY7C4235-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4235-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

|               | CY7C4235-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4235-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | ]                  |  |

|               | CY7C4235-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | ]                  |  |

| 35            | CY7C4235-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4235-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4235-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

|               | CY7C4235-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4235-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    | 1                  |  |

|               | CY7C4235-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier | 1                  |  |

### 4K x 18 Synchronous FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package<br>Type                     | Operating<br>Range |  |

|---------------|----------------|-----------------|-------------------------------------|--------------------|--|

| 10            | CY7C4245-10AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4245-10ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-10JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4245-10AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4245-10ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-10JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 15            | CY7C4245-15AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4245-15ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-15JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4245-15AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4245-15ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-15JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 25            | CY7C4245-25AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4245-25ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-25JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4245-25AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4245-25ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-25JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

| 35            | CY7C4245-35AC  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Commercial         |  |

|               | CY7C4245-35ASC | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-35JC  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

|               | CY7C4245-35AI  | A65             | 64-Lead 14x14 Thin Quad Flatpack    | Industrial         |  |

|               | CY7C4245-35ASI | A64             | 64-Lead 10x10 Thin Quad Flatpack    |                    |  |

|               | CY7C4245-35JI  | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |  |

Document #: 38-00540

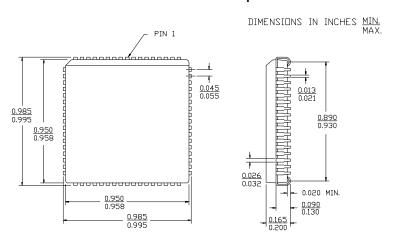

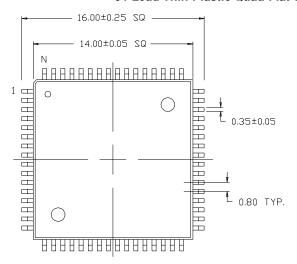

### **Package Diagrams**

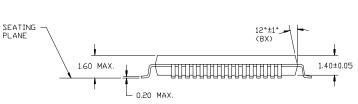

#### 64-Lead Thin Plastic Quad Flat Pack A65

DIMENSIONS IN MILLIMETERS LEAD COPLANARITY 0.100 MAX.

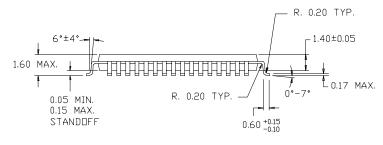

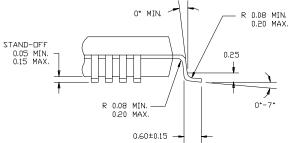

#### 64-Pin Thin Quad Flat Pack A64

DIMENSIONS IN MILLIMETERS LEAD COPLANARITY 0.080 MAX.

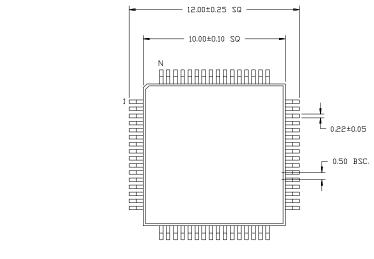

### Package Diagrams (continued)

#### 68-Lead Plastic Leaded Chip Carrier J81