# **Specifications**

## **Maximum Ratings** at $Tc = 25^{\circ}C$

| Parameter                       | Symbol                | Conditions                      | Ratings      | Unit |

|---------------------------------|-----------------------|---------------------------------|--------------|------|

| Maximum supply voltage 1        | V <sub>CC</sub> 1 max | $V_{CC}2 = 0V$                  | 36           | V    |

| Maximum supply voltage 2        | V <sub>CC</sub> 2 max | No signal                       | -0.3 to +7.0 | V    |

| Input voltage                   | V <sub>IN</sub> max   | Logic input pins                | -0.3 to +7.0 | V    |

| Phase output current            | I <sub>O</sub> max    | $V_{CC}2 = 0V, CLOCK \ge 100Hz$ | 4.0          | А    |

| Operating substrate temperature | Tc max                |                                 | 105          | °C   |

| Junction temperature            | Tj max                |                                 | 150          | °C   |

| Storage temperature             | Tstg                  |                                 | -40 to +125  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

| Parameter                  | Symbol            | Conditions             | Ratings                | Unit |

|----------------------------|-------------------|------------------------|------------------------|------|

| Operating supply voltage 1 | V <sub>CC</sub> 1 | With signal            | 16 to 30               | V    |

| Operating supply voltage 2 | V <sub>CC</sub> 2 | With signal            | $5.0V\pm5\%$           | V    |

| Input voltage              | VIH               |                        | 0 to V <sub>CC</sub> 2 | V    |

| Phase output current 1     | I <sub>O</sub> 1  | Without heat sink      | 1.7                    | А    |

| Phase output current 2     | I <sub>O</sub> 2  | Tc = 105°C             | 2.4                    | А    |

| Clock frequency            | fCL               | Pin 11 input frequency | 0 to 50                | kHz  |

## Allowable Operating Ranges at $Ta = 25^{\circ}C$

### **Electrical Characteristics 1** at $Tc = 25^{\circ}C$ , $V_{CC}1 = 24V$ , $V_{CC}2 = 5V$

| Parameters                       | Symbol          | Conditions                                                            |      | Rating |                     |      |

|----------------------------------|-----------------|-----------------------------------------------------------------------|------|--------|---------------------|------|

| Parameters                       |                 |                                                                       | min  | typ    | max                 | unit |

| V <sub>CC</sub> 2 supply current | Icco            | Enable=Low                                                            |      | 6.1    | 12                  | mA   |

| Effective output current         | loave           | Each phase R/L=2 $\Omega$ /6mH<br>2W2-3-phase excitation Vref = 0.61V | 0.62 | 0.69   | 0.76                | Arms |

| FET diode forward voltage        | Vdf             | lf= 1A (R <sub>L</sub> =23Ω)                                          |      | 1.0    | 1.6                 | V    |

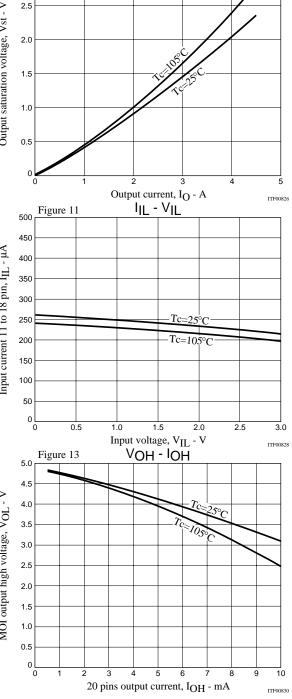

| Output saturation voltage        | Vsat            | $R_L = 23\Omega$                                                      |      | 0.45   | 0.56                | V    |

| Output leakage current IOL RI    |                 | $R_L = 23\Omega$                                                      |      |        | 0.1                 | mA   |

| Input high voltage               | VIH             | 9 terminals, Pins 11 to 18, 22                                        | 4.0  |        |                     | V    |

| Input low voltage                | VIL             | 9 terminals, Pins 11 to 18, 22                                        |      |        | 1.0                 | V    |

| Input current                    | Ι <sub>ΙL</sub> | Pins 11 to 18 pin = GND level pull-up resistance $20k\Omega$ (typ)    | 115  | 250    | 550                 | μΑ   |

| Vref input voltage               | VrH             | Pin 10                                                                | 0    |        | V <sub>CC</sub> 2/2 | V    |

| Vref input current               | lr              | Pin 10, pin 10 = 2.5V                                                 | 440  | 625    | 810                 | μΑ   |

| MOI output high voltage          | VOH             | Pin 20, pin 20 to 19 = 820Ω                                           | 2.5  |        |                     | V    |

| MOI output low voltage           | V <sub>OL</sub> | Pin 20, pin 21 to $20 = 1.6 k\Omega$                                  |      |        | 0.4                 | V    |

| PWM frequency                    | fc              |                                                                       |      | 63     |                     | kHz  |

Note: Constant voltage supply is used as power supply.

Current division ratio at phase current of 1/4 electrorotation, in each excitation mode (unit = %, typ.) Number of current division is put in parentheses.

| Current division | 2 phase (1) | 2-3 phase (3) | W2-3 phase (6) | 2W2-3 phase (12) |    |

|------------------|-------------|---------------|----------------|------------------|----|

| 1/96             |             | 0             |                | 0                |    |

| 2/96             |             |               | 0              | - 13             |    |

| 3/96             |             |               |                |                  |    |

| 4/96             | 0           |               | 20             | 00               |    |

| 5/96             | 0           |               | 26             | 26               |    |

| 6/96             |             |               |                | 20               |    |

| 7/96             |             |               |                | - 38             |    |

| 8/96             |             | 50            | 50             | 50               |    |

| 9/96             | 100         | 50            | 50             |                  |    |

| 10/96            |             |               |                | - 61             |    |

| 11/96            |             |               |                |                  |    |

| 12/96            |             |               | 71             | 71               |    |

| 13/96            |             |               |                | 71               | /1 |

| 14/96            |             |               |                | 79               |    |

| 15/96            |             |               | 87             |                  |    |

| 16/96            |             | 87            |                | 87               |    |

| 17/96            | 100         | 87            | 07             | 07               |    |

| 18/96            |             |               |                | 92               |    |

| 19/96            | -           |               |                | 92               |    |

| 20/96            |             |               | 96             | 96               |    |

| 21/96            |             | 100           |                |                  |    |

| 22/96            |             |               |                | - 98             |    |

| 23/96            |             |               | 100            |                  |    |

| 24/96            |             |               | 100            | 100              |    |

Note: Constant voltage supply is used as power supply.

Electrical Characteristic 2 represents design values. Measurement for controlling the standard value is not conducted.

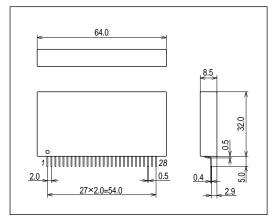

# Package Dimensions

unit:mm (typ)

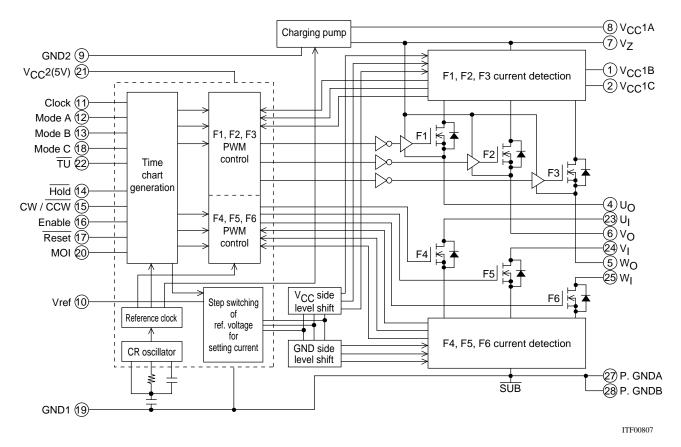

## **Equivalent Block Diagram**

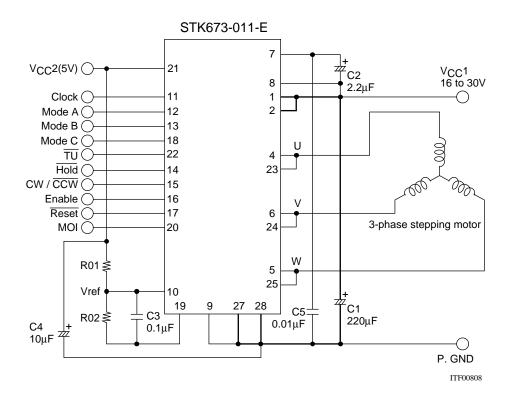

# **Sample Application Circuit**

#### Set Equation of Output Current IO Peak Value

$\begin{array}{ll} I_{O} \mbox{ peak} = Vref \div K & K = 0.63 \ (V/A) \\ Wref \leq 0.5 \times V_{CC2} \\ Vref = V_{CC}2 \times Rox \div (R01 + Rox) \\ Rox = (R02 \times 4.0 k\Omega) \div (R02 + 4.0 k\Omega) \end{array}$

• R02 is preferably set to be 100 $\Omega$  in order to minimize the effect of the internal impedance (4.0k $\Omega \pm 30\%$ ) of STK673-011-E

- For noise reduction in 5V system, put the GND side of bypass capacitor  $(220\mu F)$  of V<sub>CC</sub>1 (shown in a thick line in the above Sample Application Circuit) in the vicinity of pins 27 and 28 of the hybrid IC.

- Set the capacitance value of the bypass capacitor C1 such that a ripple current of a capacitance, which varies in accordance with the increase of motor current, lies in an allowable range.

- K in the above-mentioned set equation varies within  $\pm 5$  to  $\pm 10\%$  depending on the inductance L and resistance value R of the used motor. Check the peak value setting of I<sub>O</sub> upon actual setting.

| Terminal name | No. | Function                                                                | Conditions upon Functioning<br>0 = Low, 1 = High                         |

|---------------|-----|-------------------------------------------------------------------------|--------------------------------------------------------------------------|

|               |     | Basic clock for switching phase current of motor                        | Rising edge in Mode C = 1                                                |

| Clock         | 11  | Input frequency range: DC to 50kHz                                      | Rising and falling edge in Mode C = 0                                    |

| CIOCK         | 11  | Minimum pulse width: 10µs                                               |                                                                          |

|               |     | High level duty: 40 to 60%                                              |                                                                          |

| Mode A        | 12  | Sets excitation mode                                                    | See table listed below                                                   |

| Mode B        | 13  | Sets excitation mode                                                    | See table listed below                                                   |

| Mode C        | 18  | Sets excitation mode                                                    | See table listed below                                                   |

|               |     | Sets excitation mode                                                    | See table listed below                                                   |

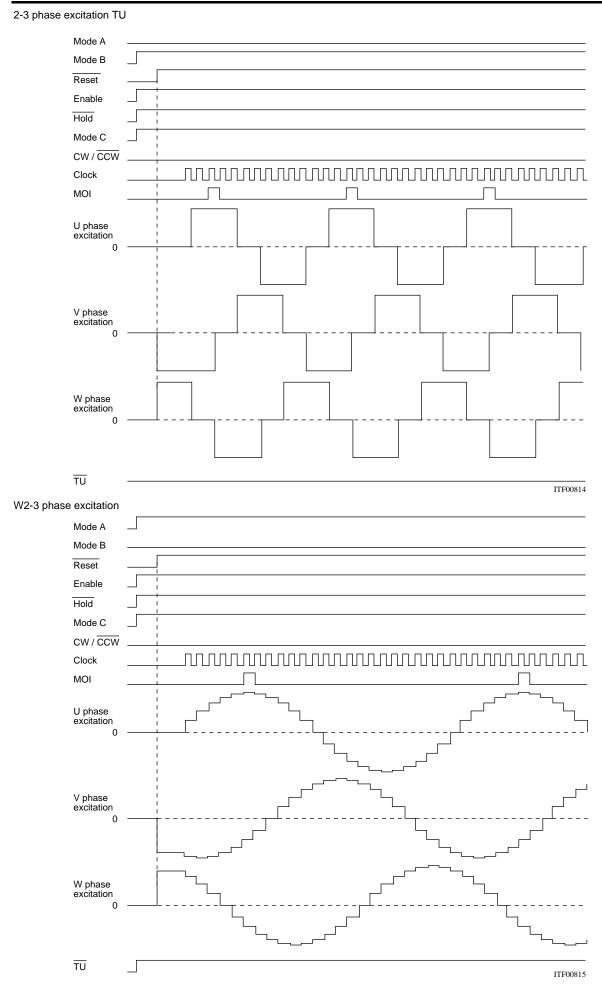

| TU            | 22  | Switches 2-3 phase excitation of step current to rectangular current    |                                                                          |

|               |     | More effective in increasing torque than in lowering vibration of motor |                                                                          |

| Hold          | 14  | Temporarily holds the motor in a state                                  | 0                                                                        |

| CW/CCW        | 15  | Switches the rotational direction of the motor                          | $1 = CW, 0 = \overline{CCW}$                                             |

| Enable        | 16  | Turns OFF all of the driving MOSFET                                     | 0                                                                        |

| Reset         | 17  | System reset Make sure to input a reset signal of 10µs or more          | 0                                                                        |

| MOI           | 20  | Monitors the number of revolution of the motor                          | Outputs 1 pulse of a high level signal per<br>one cycle of phase current |

| Vref          | 10  | Sets the peak value of the motor current set at 0.63V per 1A            | Maximum value $0.5 \times V_{CC}^2$ (4A max)                             |

#### Input/Output Terminals Functions of 5V System

#### **Excitation Mode Table**

| Input condition |        |        |    | Excitation No. | Excitation Mode | Number of current | Number of clock pulse<br>per one cycle of |

|-----------------|--------|--------|----|----------------|-----------------|-------------------|-------------------------------------------|

| Mode A          | Mode B | Mode C | TU | Excitation No. | Excitation mode | steps             | phase current                             |

| 0               | 0      | 1      | 1  | (1)            | 2-phase         | 1                 | 6                                         |

| 0               | 1      | 1      | 1  | (2)            | 2-3-phase       | 3                 | 12                                        |

| 0               | 1      | 1      | 0  | (3)            | 2-3-phase TU    | 1                 | 12                                        |

| 1               | 0      | 1      | 1  | (4)            | W2-3-phase      | 6                 | 24                                        |

| 1               | 1      | 1      | 1  | (5)            | 2W2-3-phase     | 12                | 48                                        |

| 0               | 0      | 0      | 1  | (6)            | 2-3-phase       | 3                 | 6                                         |

| 0               | 0      | 0      | 0  | (7)            | 2-3-phase TU    | 1                 | 6                                         |

| 0               | 1      | 0      | 1  | (8)            | W2-3-phase      | 6                 | 12                                        |

| 1               | 0      | 0      | 1  | (9)            | 2W2-3-phase     | 12                | 24                                        |

As shown in the table, TU terminal is only effective for Excitation Nos. (3) and (7).

Although the present hybrid IC is not damaged even when TU = 0 is mistakenly input in Excitation, other than Excitation Nos. (3) and (7), motor vibration or motor current may increase.

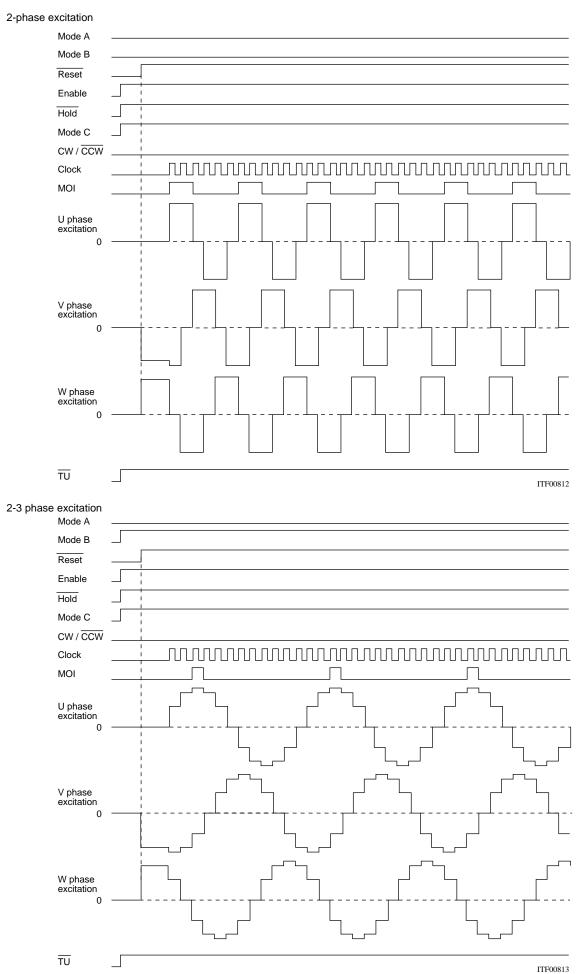

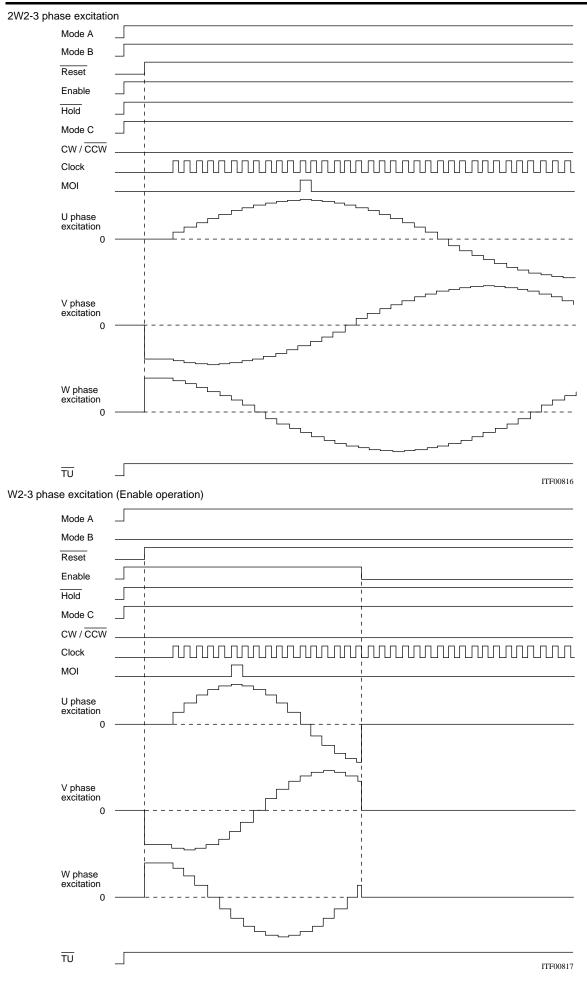

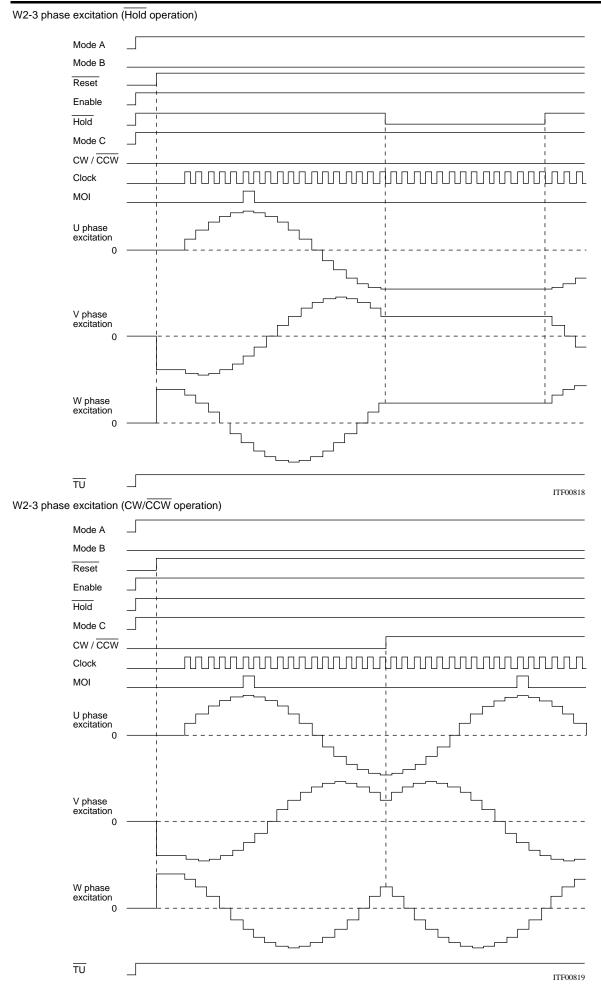

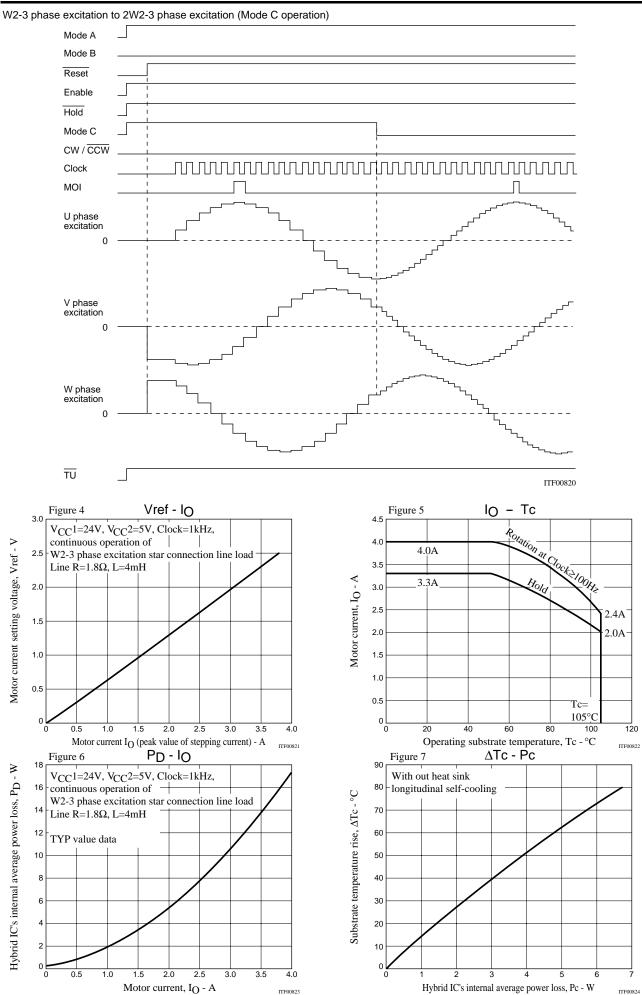

\* Timing charts for 3-phase stepping motor driver is illustrated on pages 9 to 13 for exemplary operations of Enable Hold, CW/CCW for Excitation Nos. (1), (2), (3), (4), (5) and (9), and Excitation No. (4).

## Notes On Use

(1) Input terminal use of 5V system

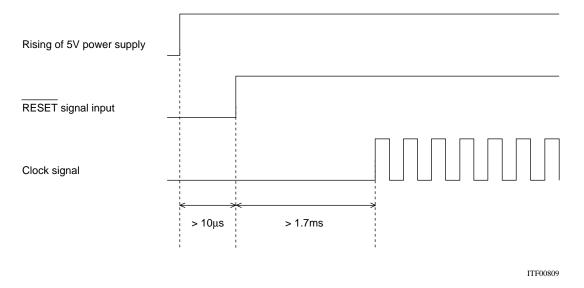

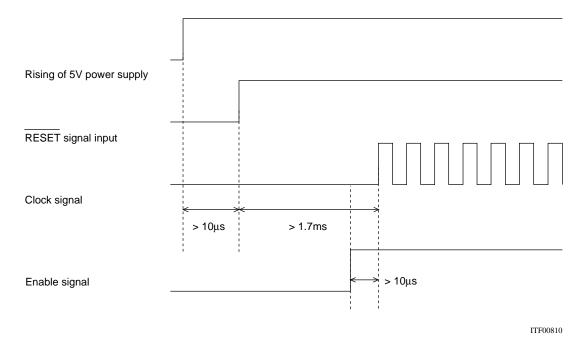

[RESET and Clock (timing of input signal upon rising of power supply)]

The driver is configured to include a 5V system logic section and a 24V MOSFETs section. The MOSFETs on both  $V_{CC1}$  side and GND side are N-channels. Thus, the MOSFETs on the  $V_{CC1}$  side is provided with a charging pump circuit for generating a voltage higher than that of  $V_{CC1}$ . When a Low signal is input to a RESET terminal for operating the RESET, the charging pump is stopped. After the release of the RESET (High input), it requires a period of 1.7ms to rise the charging pump. Accordingly, even when a Clock signal is input during the rising of the charging pump circuit, the MOSFET cannot be operated. Such a timing needs to be taken into consideration for inputting a Clock signal. An example of timing is shown in Figure 1.

Figure 1. Timing chart of RESET signal and Clock signal

When the RESET terminal switches from Low to High where a High period is 1.7ms or longer and the Clock input is conducted in a Low state, each phase current of the motor is maintained at the following values.

| Phase   | Current in the case where the initial Clock signal is maintained | Current in the case where the initial Clock signal is maintained |

|---------|------------------------------------------------------------------|------------------------------------------------------------------|

| FlidSe  | at Low level (Other than 2-3-phase TU excitation)                | at Low level (2-3-phase TU excitation)                           |

| U phase | 0                                                                | 0                                                                |

| V phase | -87% of peak current during normal rotation                      | -100% of peak current during normal rotation                     |

| W phase | +87% of peak current during normal rotation                      | +100% of peak current during normal rotation                     |

Refer to the timing charts for operations.

[Clock]

Clock signals should be input under the following conditions so that all 9 types of excitation modes shown in the Excitation Mode Table.

| Input frequency range | DC to 50kHz |

|-----------------------|-------------|

| Minimum pulse width   | 10µs        |

| High level duty       | 40 to 60%   |

When Mode C is not used, it is an operation based on rising of the Clock and thus the above-mentioned condition of high level duty is negligible. A minimum pulse width of 10µs or more allows excitation operation by Mode A and Mode B. Since the operation is based on rising and falling of the Clock under the use of Mode C, it is most preferable to set the high level duty to 50% so as to obtain uniform step-wise current widths.

#### [Mode A, Mode B, Mode C and $\overline{TU}$ ]

These 4 terminals allow selection of excitation modes. For specific operations, refer to Excitation Mode Table and Timing Charts.

### $[\overline{\text{Hold}}, \text{CW}/\overline{\text{CCW}}]$

Hold temporary holds the motor while a phase current of the motor is conducted, even when there are clock inputs of Low input.

High input releases the hold, and the motor current changes again synchronizing with the rising of Clock signals. Refer to Timing Chart for exemplary operations.

$CW/\overline{CCW}$  switches the rotational direction of the motor. Switching to High gives a rotational operation of CW, and Low gives a rotation operation of CCW. The timing of switching the rotation is synchronizes the rising of the clock signals. Refer to Timing Chart for exemplary operations.

#### [Enable]

High input renders a normal operation and Low input forcibly renders a gate signal of MOSFETs Low, thereby cutting a motor current. Once again High input renders a current to conduct in the motor. The timing of the current does not synchronize with the clock.

Since Low input of Enable forcibly cuts the motor current, it can be used to cut a V-phase or W-phase while Clock is maintained in a Low level state after the RESET operation.

Figure 2. Input timings of RESET signal, Enable signal and Clock signal

[Vref (Setting motor current peak value)]

A peak value of a motor current I<sub>O</sub> is determined by R01, R02,  $V_{CC}2$  (5V) and the following set equation (I). Set equation of peak value of motor current I<sub>O</sub>

$I_{O} \text{ peak} = \text{Vref} \div \text{K}$  (I)

```

where Vref \le 0.5 \times V_{CC2} K = 0.63 (V/A)

Vref = V_{CC2} \times Rox \div (R01 + Rox)

Rox = (R02 \times 4.0k\Omega) \div (R02 + 4.0k\Omega)

```

- R02 is preferably set to be 100 $\Omega$  in order to minimize the effect of the internal impedance (4.0k $\Omega \pm 30\%$ ) of STK673-011-E

- K in the above-mentioned set equation varies with in  $\pm 5$  to  $\pm 10\%$  depending on the inductance L and resistance value R of the used motor. Check the peak value setting of IO upon actual setting.

- \* Refer to Figure 4 for an example of Vref-IO characteristics

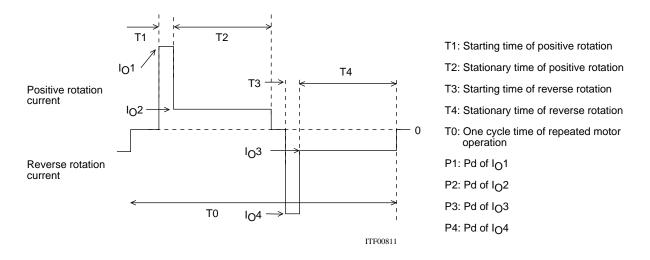

- (2) Allowable operating ranges of motor current

Set the peak value of the motor current  $I_O$  so as to lie within a region below the curve shown in Figure 5 on page 13. When the operation substrate temperature Tc is set to 105°C,  $I_O$  max should be 2.4A or lower and a Hold operation should be conducted where  $I_O$  max is 2.0A or lower.

For operation where  $Tc = 50^{\circ}C$ ,  $I_O$  max should be 4.0A or lower and a Hold operation should be conducted where  $I_O$  max is 3.3A or lower.

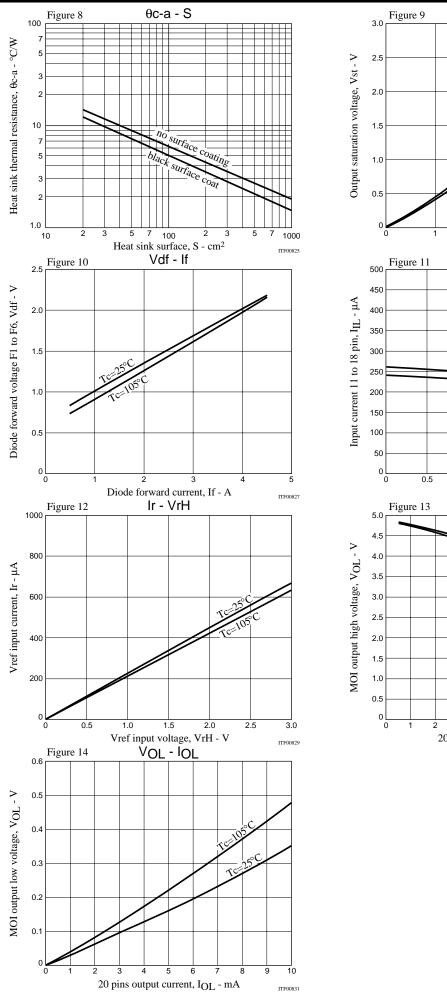

#### (3) Heat Radiation Design

Heat radiation design for reducing the operation substrate temperature of the hybrid IC is effective in enhancing the quality of the hybrid IC.

The size of a heat sink varies depending on the average power loss Pd in the hybrid IC. As shown in Figure 6 on page 13, Pd increases in accordance with the increase of the output current.

Since the starting current and the stationary current coexist in an actual motor operation, Pd cannot be obtained only from the data shown in Figure 6. Therefore, Pd is obtained assuming that the timing of the actual motor operation is a repeated operation shown in the following Figure 3.

Figure 3. Timing Chart of Motor Operation

The average power loss Pd in the hybrid IC upon an operation shown in Figure 3 can be obtained by the following equation (II):

$Pd = (T1 \times P1 + T1 \times P2 + T3 \times P3 + T4 \times P4) \div T0 \quad (II)$

When the value obtained by the above equation (II) is equal to or less than 3.4W and the ambient temperature Ta is equal to or lower than  $60^{\circ}$ C, there is no need of providing a heat sink.

Refer to Figure 7 for data of the operation substrate temperature when no heat sink is used.

The size of the heat sink can be decided depending on  $\theta$ c-a obtained by the following equation (III) and from Figure 8.  $\theta$ c-a = (Tc max - Ta) ÷ Pd (III)

where Tc max: Maximum operation substrate temperature =  $105^{\circ}$ C

Ta: Ambient temperature of hybrid IC

Although heat radiation design can be realized by following the above equations (II) and (III), make sure to check that the substrate temperature Tc is equal to or lower than 105°C after mounting the hybrid IC into a set.

#### **Timing Chart of 3-phase Stepping Motor Driver**

Vst - IO

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employeer. This literature is subject to all applicable copyright aws and is not for resale in any manner.