## 4A Ultra-Low-Input-Voltage LDO Regulators

### **Absolute Maximum Ratings**

| IN, EN, POK, POR to GND0.3V to +4V                    | Operating Temperature Range40°C to +85°C |

|-------------------------------------------------------|------------------------------------------|

| FB, OUT to GND0.3V to (V <sub>IN</sub> + 0.3V)        | Junction Temperature+150°C               |

| Output Short-Circuit Duration                         | Storage Temperature Range65°C to +150°C  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) | Lead Temperature (soldering, 10s)+300°C  |

| 16-Pin TQFN (derate 33.3mW/°C                         |                                          |

| above +70°C) (Note 1) 2666.7mW                        |                                          |

Note 1: Maximum power dissipation is obtained using JEDEC JESD51-5 and JESD51-7 standards.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| PACKAGE TYPE: 16 TQFN |         |  |  |

|-----------------------|---------|--|--|

| Package Code          | T1655+3 |  |  |

| Outline Number        | 21-0140 |  |  |

| Land Pattern Number   | 90-0072 |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

#### **Electrical Characteristics**

$(V_{EN} = V_{IN} = 1.8V, V_{OUT} = 1.5V, I_{OUT} = 2mA, T_A = -40^{\circ}C$  to +105°C (MAX8556ETE+) and  $T_A = -40^{\circ}C$  to +85°C (MAX8557ETE+), typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                              | CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNITS |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| IN                                     | IN                                                                                   |       |       |       |       |  |  |

| Input Voltage Range                    |                                                                                      | 1.425 |       | 3.600 | V     |  |  |

| Input Undervoltage Lockout             | V <sub>IN</sub> rising, 70mV hysteresis                                              | 1.30  | 1.35  | 1.40  | V     |  |  |

|                                        | V <sub>IN</sub> falling                                                              | 1.23  | 1.28  | 1.33  |       |  |  |

| ОИТ                                    |                                                                                      |       |       |       |       |  |  |

| Output Voltage Range                   |                                                                                      | 0.5   |       | 3.4   | V     |  |  |

| Load Regulation                        | I <sub>OUT</sub> = 2mA to 4A                                                         |       | 0.1   |       | %/A   |  |  |

| Line Regulation                        | V <sub>IN</sub> = 1.425V to 3.6V, V <sub>OUT</sub> = 1.225V                          | -0.15 | 0     | +0.15 | %/V   |  |  |

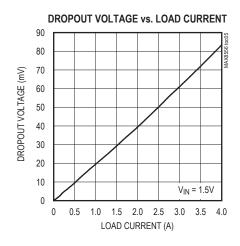

| Dropout Voltage                        | V <sub>IN</sub> = 1.425V, I <sub>OUT</sub> = 4A, V <sub>FB</sub> = 480mV             |       | 100   | 200   | mV    |  |  |

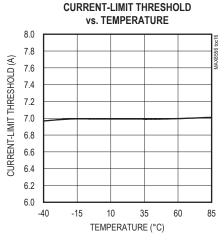

| Regulated Output-Voltage Current Limit | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3V, V <sub>FB</sub> = 460mV               | 5     | 7     | 9     | А     |  |  |

| Load Capacitance                       | ESR < 50mA (Note 3)                                                                  | 16    |       | 120   | μF    |  |  |

| FB                                     |                                                                                      |       |       |       |       |  |  |

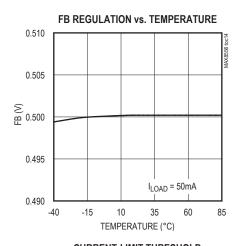

| FB Threshold Accuracy<br>(Note 4)      | $V_{OUT}$ = 1.225V to 3V, $V_{IN}$ = $V_{OUT}$ + 0.2V to 3.6V, $I_{OUT}$ = 2mA to 4A | 495   | 500   | 505   | mV    |  |  |

| FB Input Bias Current                  | V <sub>FB</sub> = 0.5V, V <sub>IN</sub> = 3.6V                                       |       | 0.001 | 1     | μA    |  |  |

## 4A Ultra-Low-Input-Voltage LDO Regulators

## **Electrical Characteristics (continued)**

$(V_{EN} = V_{IN} = 1.8V, \ V_{OUT} = 1.5V, \ I_{OUT} = 2mA, \ T_A = -40^{\circ}C \ to \ +105^{\circ}C \ (MAX8556ETE+) \ and \ T_A = -40^{\circ}C \ to \ +85^{\circ}C \ (MAX8557ETE+), \ typical values are at T_A = +25^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 2)$

| PARAMETER                            | CONDITIONS                                                    |                                                          | MIN | TYP   | MAX  | UNITS |

|--------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-----|-------|------|-------|

| GND                                  |                                                               |                                                          |     |       |      |       |

| CND Cumply Cumpent                   | V <sub>IN</sub> = 1.425V to 3.6V, V <sub>OUT</sub> = 1.225V   |                                                          |     | 800   | 1600 |       |

| GND Supply Current                   | Dropout, V <sub>IN</sub> = 3.6V, V <sub>FB</sub> = 480mV      | Dropout, V <sub>IN</sub> = 3.6V, V <sub>FB</sub> = 480mV |     | 1000  | 2000 | μΑ    |

| GND Shutdown Current                 | V <sub>IN</sub> = 3.6V, EN = GND                              |                                                          |     |       | 150  | μA    |

| РОК                                  |                                                               |                                                          | •   |       |      |       |

| FB Power-OK Fault Threshold          | FB moving out of regulation,                                  | FB high                                                  | 540 | 550   | 560  | .,    |

| FB Power-OK Fault Threshold          | $V_{IN}$ = 1.425V to 3.6V, 10mV hysteresis                    | FB low                                                   | 440 | 450   | 460  | - mV  |

| POK Output Voltage, Low              | V <sub>FB</sub> = 0.4V or 0.6V, I <sub>POK</sub> = 2mA        | V <sub>FB</sub> = 0.4V or 0.6V, I <sub>POK</sub> = 2mA   |     | 25    | 200  | mV    |

| POK Output Current, High             | V <sub>POK</sub> = 3.6V V <sub>FB</sub> = 0.5                 | V <sub>POK</sub> = 3.6V V <sub>FB</sub> = 0.5            |     | 0.001 | 1    | μA    |

| POK Delay Time                       | From FB rising to POK high                                    |                                                          | 25  | 50    | 100  | μs    |

| EN                                   |                                                               |                                                          | •   |       |      |       |

| Enable Input Threshold               | V <sub>INI</sub> = 1.425V to 3.6V                             | EN rising                                                |     |       | 1.25 | V     |

|                                      |                                                               | EN falling                                               | 0.4 |       |      |       |

| Enable Input Bias Current            | V <sub>EN</sub> = 0V or 3.6V                                  |                                                          | -1  |       | +1   | μA    |

| THERMAL SHUTDOWN                     |                                                               |                                                          |     |       |      |       |

| Thermal-Shutdown Threshold           | Output on and off                                             | T <sub>J</sub> rising                                    |     | +160  |      | °C    |

| Thermal-Shutdown Threshold           |                                                               | T <sub>J</sub> falling                                   |     | +115  |      |       |

| POR                                  |                                                               |                                                          | •   |       |      |       |

| FB Power-On Reset Fault<br>Threshold | FB falling, V <sub>IN</sub> = 1.425V to 3.6V, 10mV hysteresis |                                                          | 440 | 450   | 460  | mV    |

| POR Output Voltage, Low              | V <sub>FB</sub> = 0.4V, I <sub>POR</sub> = 2mA                |                                                          |     | 25    | 200  | mV    |

| POR Output Current, High             | V <sub>POR</sub> = 3.6V, V <sub>FB</sub> = 0.5V               |                                                          |     | 0.001 | 1    | μA    |

| POR Rising Delay Time                | FB rising to POR high impedance                               |                                                          | 100 | 140   | 200  | ms    |

| SOFT-START                           |                                                               |                                                          |     |       |      |       |

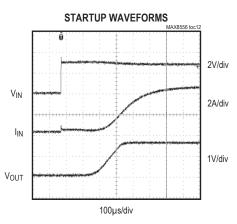

| Soft-Start Time                      |                                                               |                                                          |     | 100   |      | μs    |

**Note 2:** Specifications to  $T_A = -40^{\circ}C$  are guaranteed by design and not production tested.

Note 3: Guaranteed by design, not production tested.

Note 4: Minimum supply voltage for output accuracy must be at least 1.425V.

## 4A Ultra-Low-Input-Voltage **LDO Regulators**

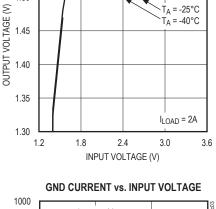

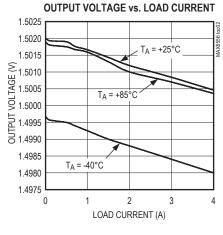

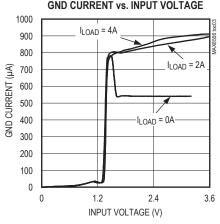

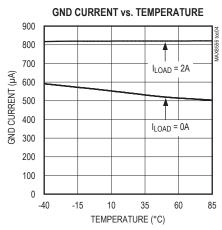

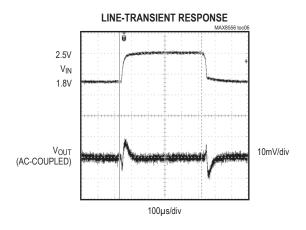

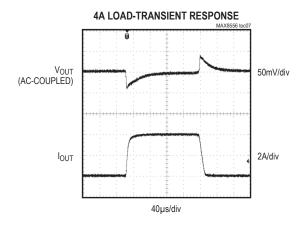

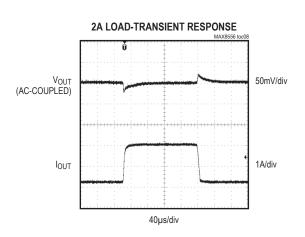

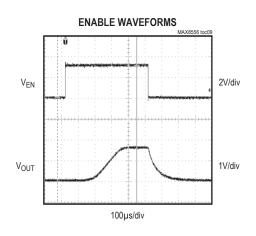

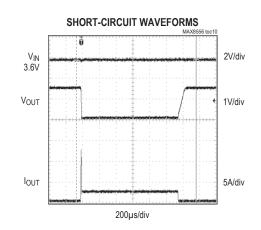

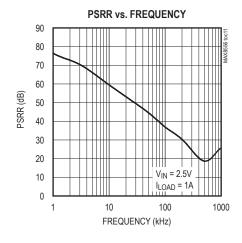

## **Typical Operating Characteristics**

$(V_{EN} = V_{IN} = +1.8V, V_{OUT} = +1.5V, I_{OUT} = 4A, C_{OUT} = 20\mu F, C_{IN} = 20\mu F, and T_A = +25^{\circ}C, unless otherwise noted.)$

Maxim Integrated | 4 www.maximintegrated.com

## 4A Ultra-Low-Input-Voltage **LDO Regulators**

# 4A Ultra-Low-Input-Voltage LDO Regulators

## **Typical Operating Characteristics (continued)**

$(V_{EN} = V_{IN} = +1.8V, V_{OUT} = +1.5V, I_{OUT} = 4A, C_{OUT} = 20\mu\text{F}, C_{IN} = 20\mu\text{F}, and T_{A} = +25^{\circ}\text{C}, unless otherwise noted.})$

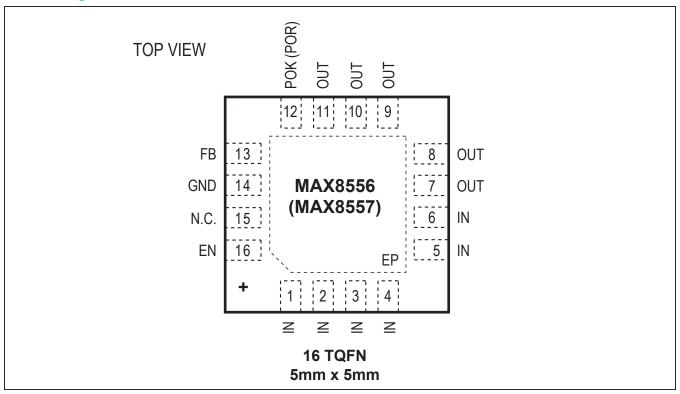

## **Pin Configuration**

## **Pin Description**

| PIN  | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                 |  |  |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1–6  | IN               | LDO Input. Connect to a 1.425V to 3.6V input voltage. Bypass with a 22µF ceramic capacitor to GND.                                                                                                                                                                                                       |  |  |

| 7–11 | OUT              | LDO Output. Bypass with 2 x $10\mu F$ ceramic capacitors to GND. A smaller capacitance can be used in the maximum load current is less than 4A.                                                                                                                                                          |  |  |

| 12   | POK<br>(MAX8556) | Power-OK Output. Open-drain output that pulls low when V <sub>OUT</sub> is outside ±10% of the expected regulation voltage or when EN is low. POK is high impedance when V <sub>OUT</sub> is within ±10% of the nominal output voltage. Connect a resistor from POK to a logic supply of less than 3.6V. |  |  |

| 12   | POR<br>(MAX8557) | Power-On Reset. Open-drain output goes high impedance 140ms after the output is above 90% of its nominal regulation voltage. POR pulls low immediately after an output fault or when EN is low. Connect a resistor from POR to a logic supply of less than 3.6V.                                         |  |  |

| 13   | FB               | Feedback Input. $V_{FB}$ is regulated to 0.5V. Connect to the center tap of a resistor-divider from output to GND to set the desired output voltage.                                                                                                                                                     |  |  |

| 14   | GND              | Ground                                                                                                                                                                                                                                                                                                   |  |  |

| 15   | N.C.             | Connect to GND or Leave Unconnected                                                                                                                                                                                                                                                                      |  |  |

| 16   | EN               | Enable Input. Connect to GND or a logic low to shut down the device. Connect to IN or a logic high for normal operation.                                                                                                                                                                                 |  |  |

| _    | EP               | Exposed Paddle. Connect to GND and to a ground plane for heatsinking.                                                                                                                                                                                                                                    |  |  |

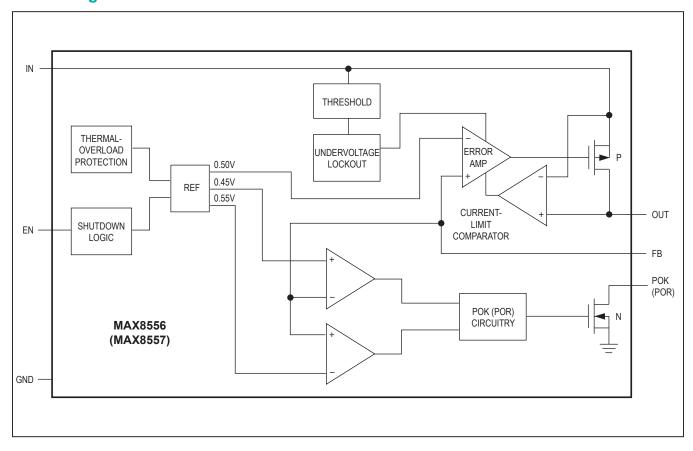

## **Block Diagram**

#### **Detailed Description**

The MAX8556/MAX8557 low-dropout linear regulators are capable of delivering up to 4A from low-input voltage supplies ranging from 1.425V to 3.6V with only 200mV of dropout (max). The pMOS output stage can be driven from input voltages down to 1.425V without sacrificing stability or transient performance. Supply current is not a significant function of load or input headroom because this regulator has a pMOS output device.

The MAX8556/MAX8557 are fully protected from an output short circuit by current-limiting and thermal-overload circuitry. The low-power shutdown mode reduces supply current to  $0.2\mu A$  (typ) to maximize battery life in portable applications. The MAX8556 includes an open-drain power-OK signal (POK) that goes high when the regulator output is within  $\pm 10\%$  of its nominal output voltage. The MAX8557 includes an open-drain power-on-reset output (POR) that goes high 140ms after the output has risen above 90% of its nominal value.

#### **Internal p-Channel Pass Transistor**

The MAX8556/MAX8557 feature a 25m $\Omega$  p-channel MOSFET pass transistor. Unlike similar designs using pnp pass transistors, p-channel MOSFETs require no base drive, which reduces quiescent current; pnp-based regulators also waste considerable current in dropout when the pass transistor saturates, and use high base-drive currents under large loads. The MAX8556/MAX8557 do not suffer from these problems and consume only 800 $\mu$ A (typ) of quiescent current under heavy loads, as well as in dropout.

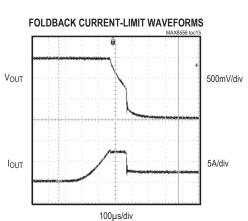

#### **Short-Circuit/Thermal Fault Protection**

The MAX8556/MAX8557 are fully protected from output short circuits through current-limiting and thermal-overload circuitry. When the output is shorted to ground, the output current is foldback limited to 3A (max). Under these conditions, the device quickly heats up. When the junction temperature reaches +160°C, the thermal-overload circuitry turns off the output, allowing the device to cool. When the junction cools to +115°C, the output turns back on and attempts to establish regulation. Current limiting and thermal protection continue until the fault is removed.

#### **Shutdown Mode**

The MAX8556/MAX8557 feature a low-power shutdown mode that reduces quiescent current to 0.2 $\mu$ A (typ). Drive EN low to disable the voltage reference, error amplifier, gate-drive circuitry, and pass transistor, and pull the output low with 5 $\mu$ C impedance. Drive EN high or connect to IN for normal operation.

#### Power-OK Output (POK, MAX8556 Only)

The MAX8556 features a power-OK (POK) output to indicate the status of the output. POK is high impedance when the regulator output is within  $\pm 10\%$  of its nominal output voltage. If the output voltage falls/rises outside this range or the IC experiences thermal fault, POK is internally pulled low. This open-drain output requires an external pullup resistor to  $V_{IN}$  or another logic supply below 3.6V. For glitch immunity, an internal delay circuit prevents the output from switching for 50µs (typ) after the trip threshold is initially reached. POK is low when the IC is in shutdown mode.

#### Power-On Reset (POR, MAX8557 Only)

The MAX8557 features a power-on reset output that goes high impedance 140ms (typ) after the output reaches 90% of its nominal value. This open-drain output requires an external pullup resistor to  $V_{IN}$  or another logic supply less than 3.6V. When the output falls below 90% of the nominal output voltage or the IC experiences a thermal fault, POR immediately transitions low. POR is low when the IC is in shutdown mode.

#### **Operating Region and Power Dissipation**

The maximum power dissipation depends on the thermal resistance of the IC package and the circuit board, the temperature difference between the die junction and ambient air, and the rate of ambient airflow. The power dissipated by the IC is  $P = I_{OUT} \times (V_{IN} - V_{OUT})$ . Proper PCB layout can increase the allowed power dissipation by dissipating heat in the board instead of the package. See the <u>Thermal Considerations in PCB Layout</u> section for more details.

www.maximintegrated.com Maxim Integrated | 9

### **Applications Information**

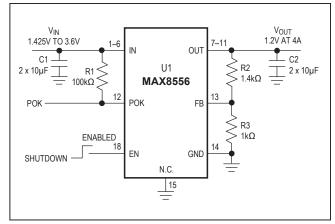

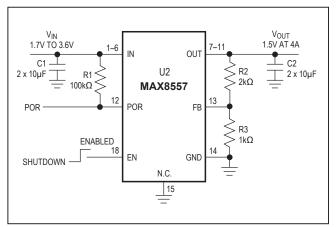

#### **Output Voltage Selection**

The MAX8556/MAX8557 feature an adjustable output voltage from 0.5V to 3.4V. Set the output voltage using an external resistor-divider from the output to GND with FB connected to the center tap as shown in <u>Figures 1</u> and <u>2</u>. Choose R3  $\leq$  1k $\Omega$  for light-load stability. Determine R2 using the following equation:

$$R2 = R3 x \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

where V<sub>OUT</sub> is the desired output voltage and V<sub>FB</sub> is 0.5V.

## Capacitor Selection and Regulator Stability

Capacitors are required at the MAX8556/MAX8557 inputs and outputs for stable operation over the full temperature range and with load currents up to 4A. Connect 2 x 10µF capacitors between IN and GND and 2 x 10µF low equivalent-series-resistance (ESR) capacitors between OUT and GND. The input capacitor (C1N) lowers the source impedance of the input supply. If the MAX8556/MAX8557s' input is close to the output of the source supply, a smaller input capacitance can be used. Otherwise, 2 x 10µF ceramic input capacitors are recommended. The output capacitor's (COUT) ESR affects output noise and can affect output stability. Use output capacitors with an ESR of 0.05 $\Omega$  or less to ensure stability and optimum transient dropout. For good output transient performance, use the following formula to select a minimum output capacitance:

$$C_{OUT} = I_{OUT(MAX)} \times 1\mu F/200mA$$

#### Noise, PSRR, and Transient Response

The MAX8556/MAX8557 are designed to operate with low-dropout voltages and low quiescent currents while still maintaining low noise, good transient response, and high AC rejection (see the *Typical Operating Characteristics* for a plot of Power-Supply Rejection Ratio (PSRR) vs. Frequency). When operating from noisy sources, improved supply-noise rejection and transient response can be achieved by increasing the values of the input and output

Figure 1. MAX8556 Typical Application Circuit

Figure 2. MAX8557 Typical Application Circuit

bypass capacitors and through passive filtering techniques. The MAX8556/MAX8557 load-transient response graphs (see the *Typical Operating Characteristics*) show two components of the output response: a DC shift from the output impedance due to the load current change, and the transient response. A typical transient overshoot for a step change in the load current from 40mA to 4A is 40mV. Use an output capacitance from  $20\mu\text{F}$  to  $120\mu\text{F}$  to attenuate the overshoot.

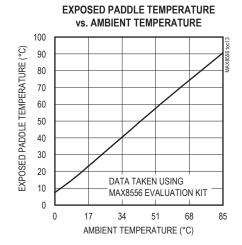

#### **Thermal Considerations in PCB Layout**

How much power the package can dissipate strongly depends on the mounting method of the IC to the PCB and the copper area for cooling. Using the JEDEC test standard, the maximum power dissipation allowed in the package is 2667mW. This data is obtained with +70°C ambient temperature and +150°C maximum junction temperature. The test board has dimensions of 7.62cm x 7.62cm (3in x 3in) with four layers of 2oz copper and FR-4 material with 62mil finished thickness. Nine thermal vias are used under the thermal paddle with a diameter of 12mil and 1mil plated copper thickness. Top and bottom layers are used to route the traces. Two middle layers are solid copper and isolated from the nine thermal vias.

More power dissipation can be handled by the package if great attention is given during PCB layout. For example, using the top and bottom copper as a heatsink and connecting the thermal vias to one of the middle layers (GND) transfers the heat from the package into the board more efficiently, resulting in lower junction temperature at high power dissipation in some MAX8556/MAX8557 applications. Furthermore, the solder mask around the IC area on both top and bottom layers can be removed to radiate the heat directly into the air. The maximum allowable power dissipation in the IC is as follows:

$$P_{MAX} = \frac{(T_{J(MAX)} - T_{A})}{\theta_{JC} + \theta_{CA}}$$

#### where:

$T_{J(MAX)}$  = the maximum junction temperature (+150°C)  $T_A$  = the ambient air temperature

$\theta_{JC}$  = the thermal resistance from the junction to the case (1.7°C/W for the 16-pin TQFN)

$\theta_{CA}$  = the thermal resistance from the case to the surrounding air through the PCB, copper traces, and the package materials.  $\theta_{CA}$  is directly related to system level variables and can be modified to increase the maximum power dissipation.

The TQFN package has an exposed thermal pad on its underside. This pad provides a low thermal resistance path for heat transfer into the PCB. This low thermally resistive path carries a majority of the heat away from the IC. The PCB is effectively a heatsink for the IC.

The exposed paddle should be connected to a large ground plane for proper thermal and electrical performance. The minimum size of the ground plane is dependent upon many system variables. To create an efficient path, the exposed paddle should be soldered to a thermal landing, which is connected to the ground plane by thermal vias. The thermal landing should be at least as large as the exposed paddle and can be made larger depending on the amount of free space from the exposed paddle to the other pin landings.

A sample layout is available on the MAX8556 evaluation kit to speed designs.

## **Ordering Information**

| PART          | TEMP RANGE      | PIN-<br>PACKAGE | FEATURE |

|---------------|-----------------|-----------------|---------|

| MAX8556ETE+   | -40°C to +105°C | 16 TQFN-EP*     | POK     |

| MAX8556ETE/V+ | -40°C to +85°C  | 16 TQFN-EP*     | POK     |

| MAX8557ETE+   | -40°C to +85°C  | 16 TQFN-EP*     | POR     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Chip Information**

TRANSISTOR COUNT: 3137

PROCESS: BICMOS

N Denotes an automotive qualified part.

<sup>\*</sup>EP = Exposed pad.

### MAX8556/MAX8557

## 4A Ultra-Low-Input-Voltage **LDO Regulators**

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                            | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 4/04             | Initial release                                                                                                                                                        | _                |

| 1                  | 8/08             | Revised Pin Configuration                                                                                                                                              | 1                |

| 2                  | 8/09             | Added automotive version of the MAX8556                                                                                                                                | 1                |

| 3                  | 4/17             | Updated MAX8556ETE+ operating temperature range in <i>Electrical Characteristics</i> and <i>Ordering Information</i> tables. Updated <i>Package Information</i> table. | 1–3, 11          |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.