## Allowable Operating Ratings at Ta = 25°C

| Parameter                             | Symbol           | Conditions | Ratings      | Unit |

|---------------------------------------|------------------|------------|--------------|------|

| Supply voltage                        | VM               |            | 10 to 35     | V    |

| Logic input voltage                   | VIN              |            | 0 to 5       | V    |

| VREF input voltage                    | VREF             |            | 0 to 3       | V    |

| Regulator output voltage              | Vo               |            | VM-5 to VM   | V    |

| Regulator output current              | IO               |            | 0 to 200     | mA   |

| Error amplifier input voltage         | V <sub>O</sub> A |            | 0 to 3       | V    |

| Timing capacity                       | СТ               |            | 100 to 15000 | pF   |

| Timing resistance                     | RT               |            | 5 to 50      | kΩ   |

| Triangular wave oscillation frequency | Fosc             |            | 10 to 800    | kHz  |

# **Electrical Characteristics** at Ta = 25°C, VM = 24V, VREF = 1.5V

| Parameter                            | Symbol Conditions    | Ratings                              |          |          | Unit    |       |

|--------------------------------------|----------------------|--------------------------------------|----------|----------|---------|-------|

| Faranielei                           | Symbol               | Conditions                           | min      | typ      | max     | Offic |

| General                              |                      |                                      |          |          |         |       |

| VM current drain                     | IM                   | PS = "H", no load                    |          | 6        | 8       | mA    |

| Thermal shutdown temperature         | TSD                  | Design guarantee                     |          | 180      |         | °C    |

| Thermal hysteresis width             | ΔTSD                 | Design guarantee                     |          | 40       |         | °C    |

| REG5 output voltage                  | Vreg5                | Ireg5 = -1mA                         | 4.5      | 5.0      | 5.5     | V     |

| Motor Drivers [Charge pump block]    |                      |                                      |          |          |         |       |

| Boost voltage                        | VGH                  | VM = 24V                             | 28.0     | 28.7     | 29.8    | V     |

| Rise time                            | tONG                 | VG = 10μF                            |          | 50       | 100     | ms    |

| Oscillation frequency                | Fcp                  | CHOP = 20kΩ                          | 90       | 120      | 150     | kHz   |

| Output block (OUT1/OUT2)             |                      |                                      |          |          |         |       |

| Output on resistance                 | RonU1                | I <sub>O</sub> = -1.5A, source side  |          | 0.5      | 0.8     | Ω     |

|                                      | RonD2                | I <sub>O</sub> = 1.5A, sink side     |          | 0.5      | 0.8     | Ω     |

| Output leak current                  | l <sub>O</sub> leak1 | V <sub>O</sub> = 35V                 |          |          | 50      | μΑ    |

| Diode forward voltage                | VD1                  | ID = -1.5A                           |          | 1.0      | 1.3     | V     |

| Output block (OUT3/OUT4)             |                      | •                                    | <u> </u> |          |         |       |

| Output on resistance                 | RonU2                | I <sub>O</sub> = -500mA, source side |          | 1.5      | 1.8     | Ω     |

|                                      | RonD2                | I <sub>O</sub> = 500mA, sink side    |          | 1.1      | 1.4     | Ω     |

| Output leak current                  | l <sub>O</sub> leak2 | V <sub>O</sub> = 35V                 |          |          | 50      | μА    |

| Diode forward voltage                | VD2                  | ID = -500mA                          |          | 1.0      | 1.3     | V     |

| Logic input block                    | JI.                  |                                      | <u>'</u> | <u> </u> | <u></u> |       |

| Logic pin input current              | I <sub>IN</sub> L    | V <sub>IN</sub> = 0.8V               | 3        | 8        | 15      | μΑ    |

|                                      | I <sub>IN</sub> H    | V <sub>IN</sub> = 5V                 | 30       | 50       | 70      | μΑ    |

| Logic high-level input voltage       | V <sub>IN</sub> H    |                                      | 2.0      |          |         | V     |

| Logic low-level input voltage        | V <sub>IN</sub> L    |                                      |          |          | 0.8     | V     |

| Current control block                |                      |                                      | <u>'</u> |          |         |       |

| VREF input current                   | IREF                 | VREF = 1.5V                          | -0.5     |          |         | μΑ    |

| Chopping frequency                   | Fchop                | CHOP = 20kΩ                          | 45       | 62.5     | 75      | kHz   |

| Threshold voltage of current setting | VHH                  | VREF = 1.5V, I0 = H, I1 = H          | 0.291    | 0.300    | 0.309   | V     |

| comparator                           | VLH                  | VREF = 1.5V, I0 = L, I1 = H          | 0.191    | 0.200    | 0.209   | V     |

|                                      | VHL                  | VREF = 1.5V, I0 = H, I1 = L          | 0.093    | 0.100    | 0.107   | V     |

| Output short-circuit protection circ | cuit                 |                                      | 1        | ı        |         |       |

| Charge current                       | IOCP                 | VOCP = 0V                            | 15       | 20       | 25      | μА    |

| Threshold voltage                    | VthOCP               |                                      | 0.8      | 1.0      | 1.2     | V     |

| Switching regulator Controller [Ref  | ference voltage      | block]                               | l l      | ı        | I       |       |

| REG25 output voltage                 | Vreg25               | Ireg25 = -1mA                        | 2.475    | 2.500    | 2.525   | V     |

| Input stability                      | V <sub>DL</sub> I    | VM = 10 to 35V                       |          |          | 10      | mV    |

| Load stability                       | V <sub>DL</sub> O    | Ireg25 = 0 to -3mA                   |          |          | 10      | mV    |

| Internal regulator block             |                      | -                                    |          | <u> </u> |         |       |

| REGVM5 output voltage                | VregVM5              | VregVM5 = 1mA                        | VM-6.0   |          | VM-5.0  | V     |

| Parameter                                        | Symbol           | Conditions                            | Ratings |      |          | Unit  |

|--------------------------------------------------|------------------|---------------------------------------|---------|------|----------|-------|

| Falanielei                                       | Symbol           |                                       | min     | typ  | max      | Offic |

| Triangular wave oscillator block                 | 1                |                                       |         |      | ,        |       |

| Oscillation frequency                            | FOSC             | RT = $20k\Omega$ , CT = $620pF$       | 72      | 80   | 88       | kHz   |

| Frequency fluctuation                            | FDV              | VM = 10 to 35V                        |         | 1    | 5        | %     |

| Current setting pin voltage                      | VRT              | $RT = 20k\Omega$                      | 0.91    | 0.98 | 1.05     | V     |

| Protective circuit block                         |                  |                                       |         |      |          |       |

| Threshold voltage of comparator                  | VthFB            | FB5, FB6                              | 1.40    | 1.55 | 1.70     | V     |

| Standby voltage                                  | VstSCP           | ISCP = 40μA                           |         |      | 100      | mV    |

| Source current                                   | ISCP             | VSCP = 0V                             | 1.6     | 2.5  | 3.4      | μΑ    |

| Threshold voltage                                | VthSCP           |                                       | 1.65    | 1.8  | 1.95     | V     |

| Latch voltage                                    | VItSCP           | ISCP = 40μA                           |         |      | 100      | mV    |

| Soft start circuit block                         |                  |                                       |         |      |          |       |

| Source current                                   | ISOFT            | VSOFT = 0V                            | 1.3     | 1.6  | 1.9      | μΑ    |

| Latch voltage                                    | VItSOFT          | ISOFT = 40μA                          |         |      | 100      | mV    |

| Low-input malfunction preventive                 | circuit block    |                                       |         |      | •        |       |

| Threshold voltage                                | VUT              |                                       | 8.3     | 8.7  | 9.1      | V     |

| Hysteresis voltage                               | VHIS             |                                       | 240     | 340  | 440      | mV    |

| Error amplifier block                            | ı                | •                                     | - '     |      | <u> </u> |       |

| Input offset voltage                             | V <sub>i</sub> O |                                       |         |      | 6        | mV    |

| Input offset current                             | Ι <sub>i</sub> O |                                       |         |      | 30       | nA    |

| Input bias current                               | l <sub>i</sub> b |                                       |         |      | 100      | nA    |

| OPEN open gain                                   | AV               |                                       |         | 85   |          | dB    |

| Common-phase input voltage range                 | VCM              | VM = 10 to 35V                        |         |      | 3.0      | V     |

| Common phase removal ratio                       | CMRR             |                                       |         | 80   |          | dB    |

| Max output voltage                               | V <sub>O</sub> H |                                       | 4.5     | 5.0  |          | V     |

| Min output voltage                               | V <sub>O</sub> L |                                       |         | 0.2  | 0.5      | V     |

| Output sink current                              | Isi              | FB = 2.5V                             | 300     | 600  | 1000     | μА    |

| Output source current                            | Iso              | FB = 2.5V                             | 45      | 75   | 105      | μA    |

| PWM comparator block                             | l                |                                       | I       |      |          |       |

| Input threshold voltage                          | VT100            | Duty cycle = 100%                     | 0.95    | 1.01 | 1.07     | V     |

| (Fosc = 10kHz)                                   | VT0              | Duty cycle = 0%                       | 0.49    | 0.52 | 0.55     | V     |

| Input bias current                               | IBDT             | DT6 = 0.4V                            |         |      | 1        | μА    |

| MAX duty cycle 1                                 | Don1             | 5ch<br>Internally fixed               | 94      |      |          | %     |

| (Fosc = 80kHz)  MAX duty cycle 2 (Fosc = 160kHz) | Don2             | 5ch<br>Internally fixed               | 92      |      |          | %     |

| MAX duty cycle 3 (Fosc = 10kHz)                  | Don3             | 6ch<br>VREG25 divided by 17kΩ and 8kΩ | 56      | 65   | 74       | %     |

| Output block                                     | 1                |                                       |         |      |          |       |

| Output ON resistance                             | RonU3            | I <sub>O</sub> = -200mA, source side  |         | 10   | 12       | Ω     |

| Carpat Ort resistance                            | RonD3            | $I_O = 200$ mA, sink side             |         | 6    | 8        | Ω     |

| Leak current                                     | ILEAK            | -                                     |         | 0    | 5        |       |

| LEAN CUITEIIL                                    | ILEAN            | $V_O = 35V$                           |         |      | ວ        | μΑ    |

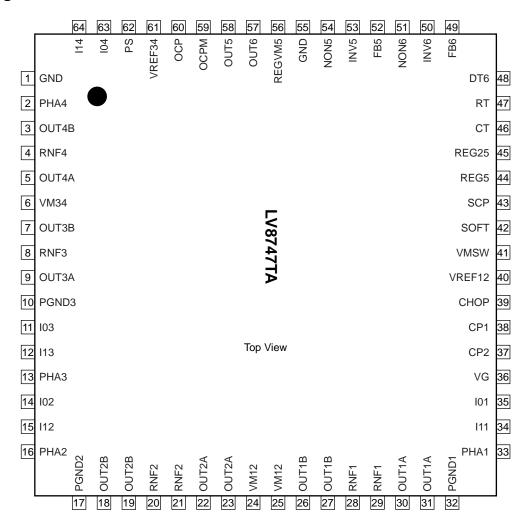

### **Pin Assignment**

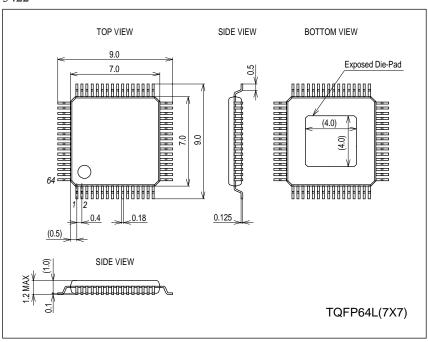

## **Package Dimensions**

unit: mm (typ)

3422

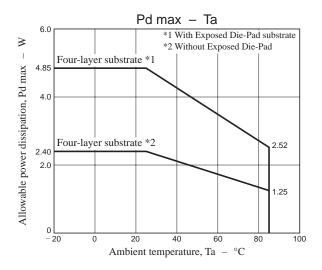

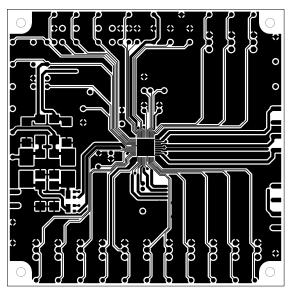

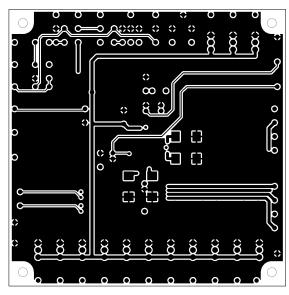

**Substrate Specifications** (Substrate recommended for operation of LV8747TA)

Size :  $100 \text{mm} \times 100 \text{mm} \times 1.6 \text{mm}$  (four-layer substrate [2S2P])

Material : Glass epoxy

Copper wiring density : L1 = 85% / L4 = 90%

L1: Copper wiring pattern diagram

L4 : Copper wiring pattern diagram

### **Cautions**

- 1) The data for the case with the Exposed Die-Pad substrate mounted shows the values when 80% or more of the Exposed Die-Pad is wet.

- 2) For the set design, employ the derating design with sufficient margin.

Stresses to be derated include the voltage, current, junction temperature, power loss, and mechanical stresses such as vibration, impact, and tension.

Accordingly, the design must ensure these stresses to be as low or small as possible.

The guideline for ordinary derating is shown below:

- (1)Maximum value 80% or less for the voltage rating

- (2)Maximum value 80% or less for the current rating

- (3) Maximum value 80% or less for the temperature rating

- 3) After the set design, be sure to verify the design with the actual product.

Confirm the solder joint state and verify also the reliability of solder joint for the Exposed Die-Pad, etc.

Any void or deterioration, if observed in the solder joint of these parts, causes deteriorated thermal conduction,

possibly resulting in thermal destruction of IC.

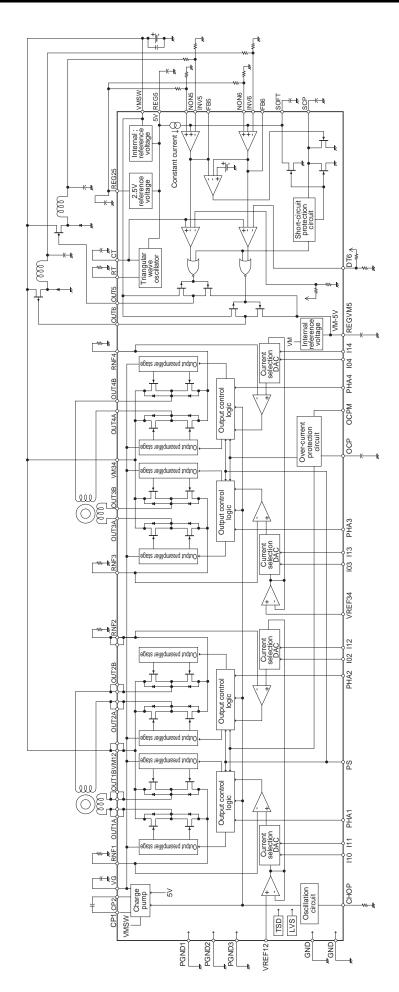

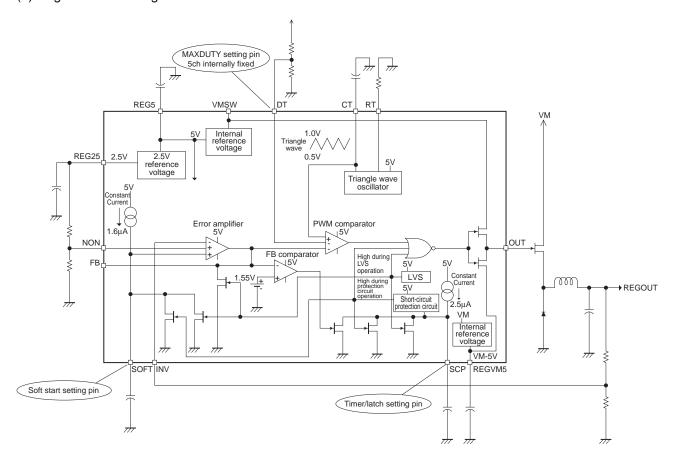

## **Block Diagram**

## **Pin Functions**

| Pin No | Pin      | Description                                                                       |

|--------|----------|-----------------------------------------------------------------------------------|

| 24     | VM12     | Driver 1/2ch Pin to connect to power supply                                       |

| 25     |          |                                                                                   |

| 30     | OUT1A    | Driver 1ch OUTA output pin                                                        |

| 31     |          |                                                                                   |

| 26     | OUT1B    | Driver 1ch OUTB output pin                                                        |

| 27     |          |                                                                                   |

| 28     | RNF1     | Driver 1ch Current sense resistor connection pin                                  |

| 29     |          |                                                                                   |

| 22     | OUT2A    | Driver 2ch OUTA output pin                                                        |

| 23     |          |                                                                                   |

| 18     | OUT2B    | Driver 2ch OUTB output pin                                                        |

| 19     |          |                                                                                   |

| 20     | RNF2     | Driver 2ch Current sense resistor connection pin                                  |

| 21     |          |                                                                                   |

| 35     | I01      | Driver 1ch Output current setting input pin                                       |

| 34     | I11      |                                                                                   |

| 33     | PHA1     | Driver 1ch Output phase shift input pin                                           |

| 14     | 102      | Driver 2ch Output current setting input pin                                       |

| 15     | l12      |                                                                                   |

| 16     | PHA2     | Driver 2ch Output phase shift input pin                                           |

| 40     | VREF12   | Driver 1/2ch Output current setting reference voltage input pin                   |

| 32     | PGND1    | Driver output Power GND                                                           |

| 17     | PGND2    | Driver output Power GND                                                           |

| 6      | VM34     | Driver 3/4ch Power connection pin                                                 |

| 9      | OUT3A    | Driver 3ch OUTA output pin                                                        |

| 7      | OUT3B    | Driver 3ch OUTB output pin                                                        |

| 8      | RNF3     | Driver 3ch Current sense resistor connection pin                                  |

| 5      | OUT4A    | Driver 4ch OUTA output pin                                                        |

| 3      | OUT4B    | Driver 4ch OUTB output pin                                                        |

| 4      | RNF4     | Driver 4ch Current sense resistor connection pin                                  |

| 11     | 103      | Driver 3ch Output current setting input pin                                       |

| 12     | I13      |                                                                                   |

| 13     | PHA3     | Driver 3ch Output phase shift input pin                                           |

| 63     | 104      | Driver 4ch Output current setting input pin                                       |

| 64     | 114      |                                                                                   |

| 2      | PHA4     | Driver 4ch Output phase shift input pin                                           |

| 61     | VREF34   | Driver 3/4ch Output current setting reference voltage input pin                   |

| 10     | PGND3    | Driver output Power GND                                                           |

| 60     | OCP      | Pin to connect to the output short-circuit state detection time setting capacitor |

| 59     | OCPM     | Over-current mode changeover pin                                                  |

| 39     | CHOP     | Pin to connect to the resistor to set the chopping frequency                      |

| 62     | PS       | Driver Power save input pin                                                       |

| 36     | VG       | Charge pump capacitor connection pin                                              |

| 38     | CP1      | Charge pump capacitor connection pin                                              |

| 37     | CP2      | Charge pump capacitor connection pin                                              |

| 41     | VMSW     | Power connection pin                                                              |

| 44     | REG5     | Internal regulator output pin                                                     |

| 56     | REGVM5   | Internal regulator output pin                                                     |

| 45     | REG25    | Regulator Reference voltage output pin                                            |

|        | CT REG25 |                                                                                   |

| 46     | RT       | Regulator Timing capacity external pin                                            |

| 47     |          | Regulator Timing resistor external pin  Regulator Soft start setting pin          |

| 42     | SOFT     | Regulator Soft start setting pin                                                  |

| 43     | SCP      | Regulator Timer and latch setting pin                                             |

| 54     | NON5     | Regulator Error amplifier 5 input + pin                                           |

| Continued | from | preceding page  |

|-----------|------|-----------------|

| Continued | irom | preceding bage. |

| Pin No | Pin  | Description                             |  |

|--------|------|-----------------------------------------|--|

| 53     | INV5 | Regulator Error amplifier 5 input – pin |  |

| 52     | FB5  | Regulator Error amplifier 5 output pin  |  |

| 58     | OUT5 | Regulator Output 5                      |  |

| 51     | NON6 | Regulator Error amplifier 6 input + pin |  |

| 50     | INV6 | Regulator Error amplifier 6 input – pin |  |

| 49     | FB6  | Regulator Error amplifier 6 output pin  |  |

| 57     | OUT6 | Regulator Output 6                      |  |

| 48     | DT6  | Regulator Output 6 MAX DUTY setting pin |  |

| 55     | GND  | GROUND                                  |  |

| 1      | GND  | GROUND                                  |  |

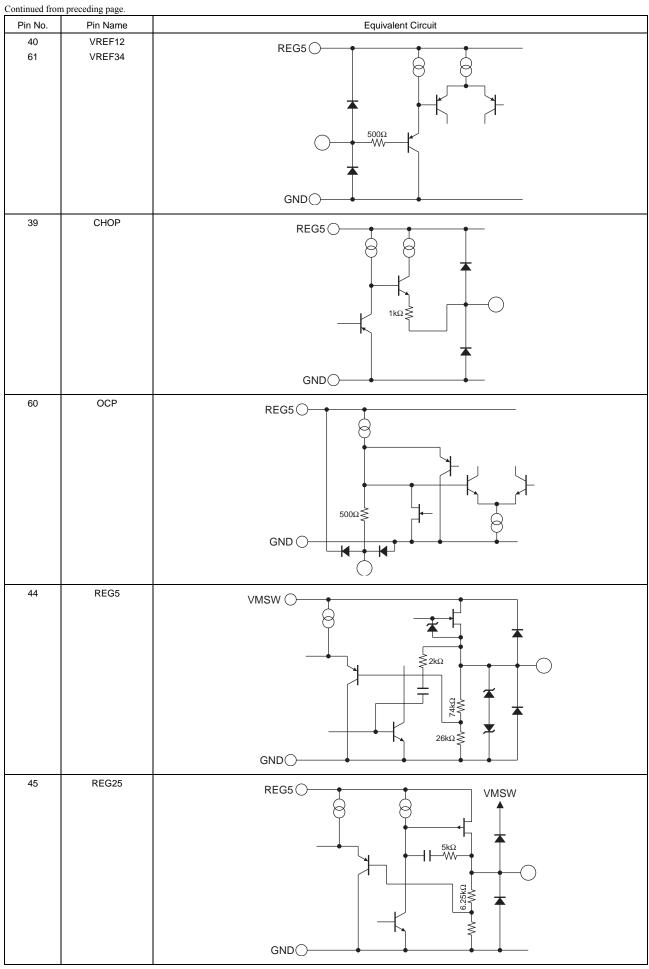

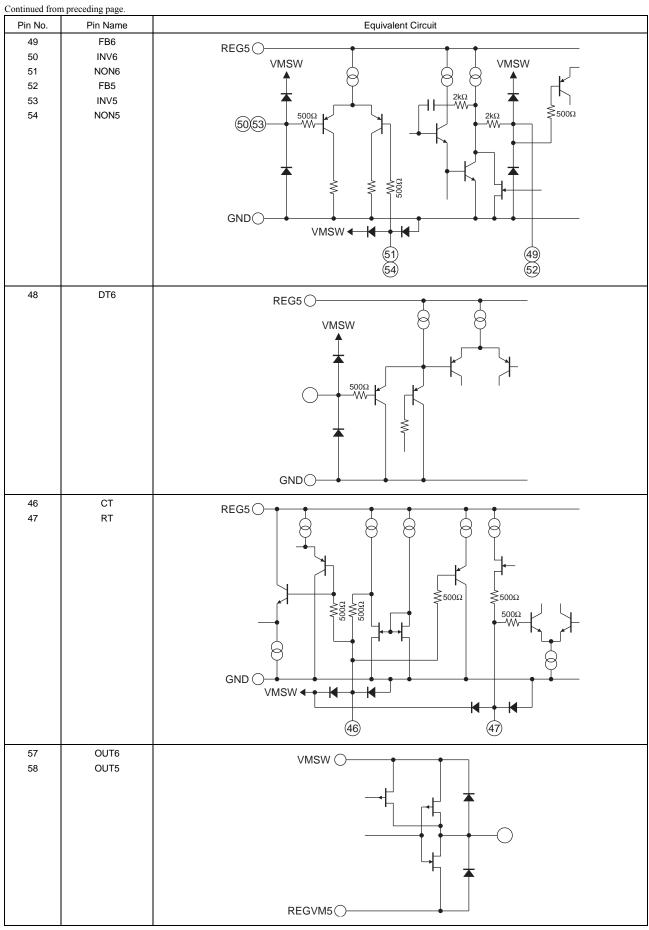

### **Equivalent Circuits**

| _94.74.0                                                                                              | nt Circuits                                                                             |                                                                                              |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Pin No.                                                                                               | Pin Name                                                                                | Equivalent Circuit                                                                           |

| 2                                                                                                     | PHA4                                                                                    | REG5 🔷 🕴                                                                                     |

| 11                                                                                                    | 103                                                                                     | KEG5 O                                                                                       |

| 12                                                                                                    | l13                                                                                     |                                                                                              |

| 13                                                                                                    | PHA3                                                                                    |                                                                                              |

| 14                                                                                                    | 102                                                                                     | <b>★</b>   <del>                                  </del>                                     |

| 15                                                                                                    | l12                                                                                     |                                                                                              |

| 16                                                                                                    | PHA2                                                                                    | 400                                                                                          |

| 33                                                                                                    | PHA1                                                                                    | 10kΩ                                                                                         |

| 34                                                                                                    | I11                                                                                     |                                                                                              |

| 35                                                                                                    | l01                                                                                     |                                                                                              |

| 59                                                                                                    | OCPM                                                                                    | <b>★</b> \$100kΩ                                                                             |

|                                                                                                       |                                                                                         | A > 100m2                                                                                    |

| 62                                                                                                    | PS                                                                                      |                                                                                              |

| 63                                                                                                    | 104                                                                                     |                                                                                              |

| 64                                                                                                    | l14                                                                                     | GND                                                                                          |

| 36                                                                                                    | VG                                                                                      |                                                                                              |

| 37                                                                                                    | CP2                                                                                     | (38) VMSW (37) (36)                                                                          |

| 38                                                                                                    | CP1                                                                                     | lacksquare                                                                                   |

|                                                                                                       | <b>O.</b> .                                                                             |                                                                                              |

|                                                                                                       |                                                                                         | •                                                                                            |

|                                                                                                       |                                                                                         | REG5 ◯                                                                                       |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         | 그                                                                                            |

|                                                                                                       |                                                                                         | <b>├</b>                                                                                     |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         | → 1 → 1 → 1 → 1                                                                              |

|                                                                                                       |                                                                                         |                                                                                              |

|                                                                                                       |                                                                                         | GND                                                                                          |

| 2                                                                                                     | OUT 4D                                                                                  |                                                                                              |

| 3<br>4                                                                                                | OUT4B<br>RNF4                                                                           | 6                                                                                            |

|                                                                                                       |                                                                                         |                                                                                              |

| 5                                                                                                     | OUT4A                                                                                   |                                                                                              |

| 6                                                                                                     | 1/1/10/4                                                                                |                                                                                              |

|                                                                                                       | VM34                                                                                    | REG5 ()                                                                                      |

| 7                                                                                                     | OUT3B                                                                                   | REG5 O                                                                                       |

| 7<br>8                                                                                                | OUT3B<br>RNF3                                                                           |                                                                                              |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  |                                                                                              |

| 7<br>8                                                                                                | OUT3B<br>RNF3                                                                           | REG5 (59) (37)                                                                               |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  | 59 37                                                                                        |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  |                                                                                              |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  | 59 37                                                                                        |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  | 5 9 3 7<br>\$500Ω                                                                            |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  | 5 9<br>3 7                                                                                   |

| 7<br>8<br>9                                                                                           | OUT3B<br>RNF3<br>OUT3A                                                                  | SOND (4)                                                                                     |

| 7<br>8<br>9<br>10                                                                                     | OUT3B<br>RNF3<br>OUT3A<br>PGND3                                                         | 5 9<br>3 7                                                                                   |

| 7<br>8<br>9<br>10                                                                                     | OUT3B<br>RNF3<br>OUT3A<br>PGND3                                                         | GND () (4) (8) (10) (8) (10) (10) (10) (10) (10) (10) (10) (10                               |

| 7<br>8<br>9<br>10                                                                                     | OUT3B<br>RNF3<br>OUT3A<br>PGND3<br>PGND2<br>OUT2B                                       | GND () (4) (8) (24)                                                                          |

| 7<br>8<br>9<br>10<br>17<br>18<br>19                                                                   | OUT3B RNF3 OUT3A PGND3  PGND2 OUT2B OUT2B                                               | GND () (4) (8) (10) (8) (10) (10) (10) (10) (10) (10) (10) (10                               |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20                                                             | OUT3B RNF3 OUT3A PGND3  PGND2 OUT2B OUT2B RNF2                                          | GND () (4) (8) (24)                                                                          |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21                                                       | OUT3B RNF3 OUT3A PGND3  PGND2 OUT2B OUT2B RNF2 RNF2 RNF2                                | GND () (24) (25)                                                                             |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22                                                 | OUT3B RNF3 OUT3A PGND3  PGND2 OUT2B OUT2B RNF2 RNF2 RNF2 OUT2A                          | GND () (4) (8) (24)                                                                          |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23                                           | PGND2 OUT2B OUT2B OUT2B RNF2 RNF2 CUT2A OUT2A                                           | GND (3) 7) (4) (24) (25) (24) (25) (7) (10) (10) (10) (10) (10) (10) (10) (10                |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22                                                 | PGND2 OUT2B OUT2B OUT2B RNF2 RNF2 RNF2 OUT2A OUT2A VM12                                 | GND (10) (18)(19)                                                                            |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23                                           | PGND2 OUT2B OUT2B OUT2B RNF2 RNF2 CUT2A OUT2A                                           | GND (3) 7) (4) (24) (25) (24) (25) (7) (10) (10) (10) (10) (10) (10) (10) (10                |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24                                     | PGND2 OUT2B OUT2B OUT2B RNF2 RNF2 RNF2 OUT2A OUT2A VM12                                 | GND (10) (18)(19)                                                                            |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25                               | PGND2 OUT2B OUT2B OUT2B CUT2B OUT2B CUT2B CUT2B CUT2A VM12 VM12                         | GND (3) 7) (3) (3) (3) (3) (3) (3) (3) (3) (3) (3                                            |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26                         | PGND2 OUT2B OUT2B OUT2B OUT2B OUT2B OUT2B VM12 VM12 VM12 OUT1B                          | GND (10) (18)(19)                                                                            |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28             | PGND2 OUT2B OUT2B OUT2B OUT2B OUT2B VM12 VM12 VM12 VM12 OUT1B OUT1B RNF1                | GND (3) 7 (3) 7 (4) (8) (8) (9) (2) (2) (3) (1) (1) (1) (1) (1) (1) (1) (1) (1) (1           |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29       | PGND2 OUT2B OUT2B OUT2B OUT2B OUT2B VM12 VM12 VM12 VM12 OUT1B OUT1B RNF1 RNF1           | GND (3) 7 (24) (25) (22) (23) (18) (9) (26) (27) (26) (27) (27) (27) (27) (27) (27) (27) (27 |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 | PGND2 OUT2B OUT2B OUT2B OUT2B OUT2B VM12 VM12 VM12 VM12 VM11 OUT1B RNF1 RNF1 RNF1 OUT1A | S 9 3 7 3 7 3 7 3 7 3 7 3 7 3 7 3 7 3 7 3                                                    |

| 7<br>8<br>9<br>10<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29       | PGND2 OUT2B OUT2B OUT2B OUT2B OUT2B VM12 VM12 VM12 VM12 OUT1B OUT1B RNF1 RNF1           | GND (3) 7 (24) (25) (22) (23) (18) (9) (26) (27) (26) (27) (27) (27) (27) (27) (27) (27) (27 |

| Pin No. | n preceding page.<br>Pin Name | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56      | REGVM5                        | VMSW O 150KΩ \$ 65KΩ \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 42      | SOFT                          | REG5 ○  Soon Soon Soon Soon Soon Soon Soon Soo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 43      | SCP                           | REG5 ○  SOUNT IN THE SOUNT IN |

### **Stepping Motor Driver OUT1/OUT2**(OUT3/OUT4)

### (1) Output control logic

| Parallel input (Note) |      | Output |      | 0                 |

|-----------------------|------|--------|------|-------------------|

| PS                    | PHA  | OUTA   | OUTB | Current direction |

| Low                   | *    | Off    | Off  | Standby           |

| High                  | Low  | Low    | High | OUTB→OUTA         |

| High                  | High | High   | Low  | OUTA→OUTB         |

(Note): Enter either "H" or "L" externally for the logic input pin. Never use the input pin in the OPEN state.

### (2) Constant-current setting

| I0 (Note) | I1 (Note) | Output current                      |

|-----------|-----------|-------------------------------------|

| High      | High      | $I_O = (VREF/5) / RNF$              |

| Low       | High      | $I_O = ((VREF/5) / RNF) \times 2/3$ |

| High      | Low       | $I_O = ((VREF/5) / RNF) \times 1/3$ |

| Low       | Low       | I <sub>O</sub> = 0                  |

(Note): Enter either "H" or "L" externally for the logic input pin. Never use the input pin in the OPEN state.

### Set current calculation method

The constant-current control setting of STM driver is determined as follows from the setting of VREF voltage, and I0 and I1, and resistor (RNF) connected between RNF and GND:

Iconst [A] =

$$((VREF [V] / 5) / RNF [\Omega]) \times attenuation factor$$

(Example) For VREF = 1.5V, I0 = I1 = "H" and RNF =

$$1\Omega$$

;

Iconst =  $1.5V/5/1\Omega \times 1 = 0.3A$

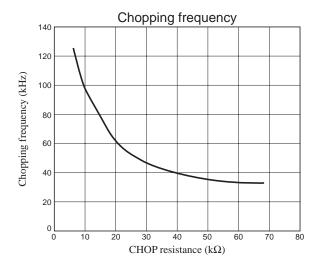

### (3) Setting the chopping frequency

For constant-current control, chopping operation is made with the frequency determined by the external resistor (connected to the CHOP pin).

The chopping frequency to be set with the resistance connected to the CHOP pin (pin 39) is as shown below.

The recommended chopping frequency ranges from 30kHz to 120kHz.

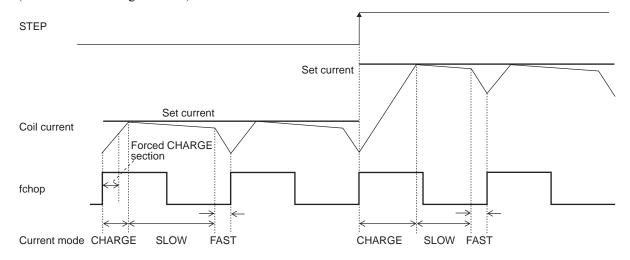

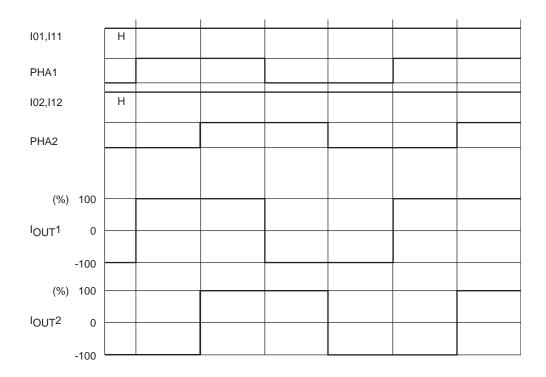

# (4) Constant-current control time chart (chopping operation) (Sine wave increasing direction)

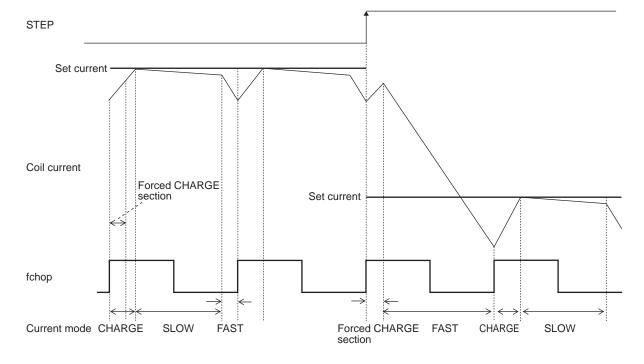

### (Sine wave decreasing direction)

In each current mode, the operation sequence is as described below:

- At rise of chopping frequency, the CHARGTE mode begins. (The section in which the CHARGE mode is forced regardless of the magnitude of the coil current (ICOIL) and set current (IREF) exists for 1/16 of one chopping cycle.)

- The coil current (ICOIL) and set current (IREF) are compared in this forced CHARGE section.

When (ICOIL<IREF) state exists in the forced CHARGE section;

CHARGE mode up to ICOIL  $\geq$  IREF, then followed by changeover to the SLOW DECAY mode, and finally by the FAST DECAY mode for the 1/16 portion of one chopping cycle.

When (ICOIL<IREF) state does not exist in the forced CHARGE section;

The FAST DECAY mode begins. The coil current is attenuated in the FAST DECAY mode till one cycle of chopping is over.

Above operations are repeated. Normally, the SLOW (+FAST) DECAY mode continues in the sine wave increasing direction, then entering the FAST DECAY mode till the current is attenuated to the set level and followed by the SLOW DECAY mode.

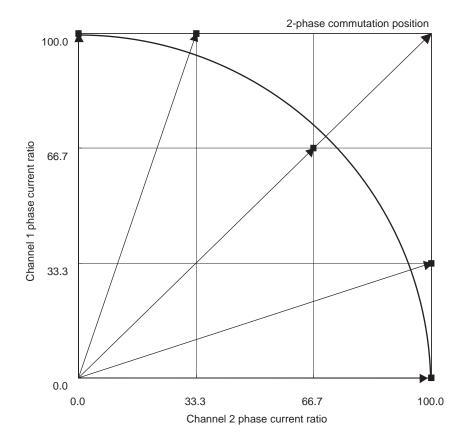

## (5) Output current vector locus (one step is normalized to 90 degrees)

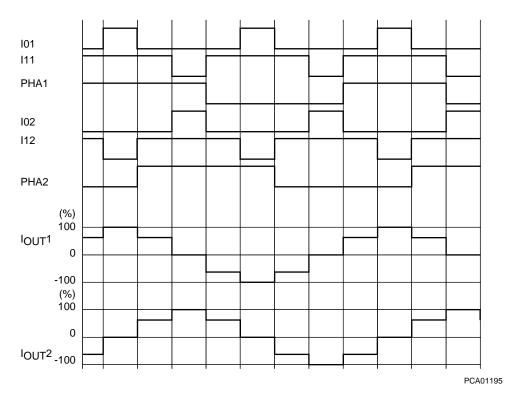

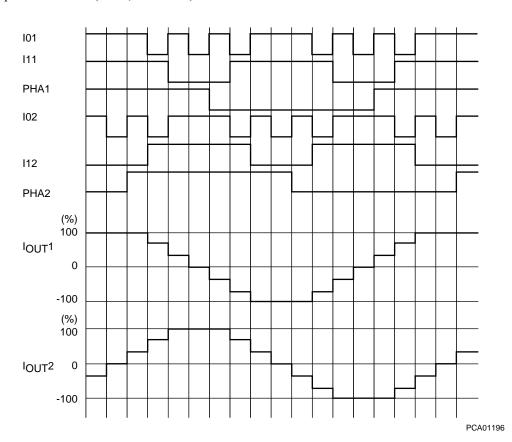

# (6) Typical current waveform in each excitation mode Two-phase excitation (1/2ch, CW mode)

## 1-2 phase excitation (1/2ch, CW mode)

W1-2 phase excitation (1/2ch, CW mode)

### **Output short-circuit protection circuit**

To protect IC from damage due to short-circuit of the output caused by lightening or ground fault, the output short-circuit protection circuit to put the output in the standby mode is incorporated.

### (1) Output short-circuit protection operation changeover function

Changeover to the output short-circuit protection of IC is made by the setting of OCPM pin.

| ОСРМ   | State             |

|--------|-------------------|

| "Low"  | Auto reset method |

| "High" | Latch method      |

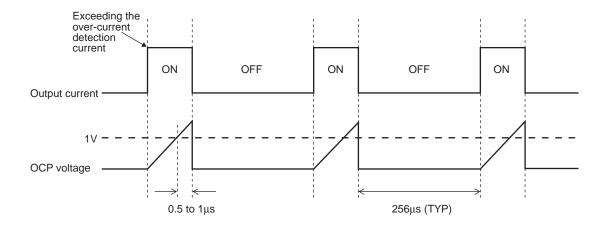

### (Auto reset method)

When the output current is below the output short-circuit protection current, the output is controlled by the input signal. When the output current exceeds the detection current, the switching waveform as shown below appears instead.

When detecting the output short-circuit state, the short-circuit detection circuit is activated.

When the short-circuit detection circuit operation exceeds the timer latch time described later, the output is changed over to the standby mode and reset to the ON mode again in  $256\mu s$  (TYP). In this event, if the over-current mode still continues, the above switching mode is repeated till the over-current mode is canceled.

### (Latch method)

Similarly to the case of automatic reset method, the short-circuit detection circuit is activated when it detects the output short-circuit state.

When the short-circuit detection circuit operation exceeds the timer latch time described later, the output is changed over to the standby mode.

In this method, latch is released by setting PS = "L"

### (2) OCP pin constant setting method (timer latch setting)

Connect C between the OCP pin and GND, and the time up to the output OFF can be set in case of output short-circuit. The C value can be determined as follows:

Timer latch : Tocp  $Tocp \approx C \times V/I[s]$

V : Threshold voltage TYP 1V I : OCP charge current TYP 20μA

(C: Recommended constant value 100pF to 200pF)

No.A2019-17/20

### **Switching Regulator Controller**

### (1) Regulator block diagram

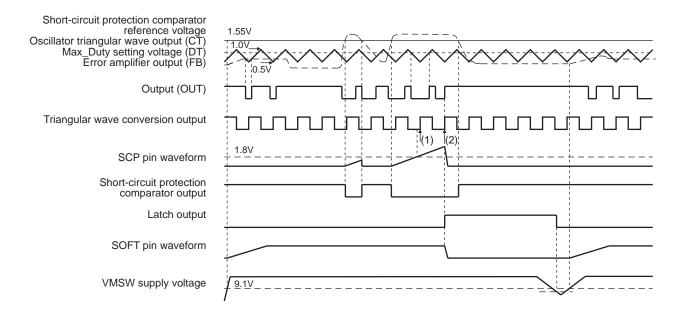

### (2) Timing chart

### (3) SOFT pin constant setting method (Soft start setting)

The switching regulator can be set to soft-start by connecting C between the SOFT pin and GND. Determine the C value as follows:

Soft start time : Tsoft  $Tsoft \approx C \times V/I[s]$

V : Error amplifier input + pin voltage (NON5/NON6)

I: SOFT charge current TYP 1.6μA

### (4). SCP pin constant setting method (Timer latch setting)

The time up to the output OFF in case of regulator output short-circuit can be set by connecting C between the SCP pin and GND.

Determine the C value as follows:

Timer latch : Tscp  $Tscp \approx C \times V/I[s]$

V : Threshold voltage TYP 1.8V I : SCP charge current TYP 2.5μA

### (5) RT pin constant setting method (Capacitor charge/discharge current setting)

The CT pin capacitor charge/discharge current can be set for triangular wave generation by connecting R between the RT pin and GND.

Determine the R value as follows:

Charge/discharge current : Irt Irt  $\approx V/R$  [A]

V: R pin voltage TYP 0.98V

### (6) CT pin constant setting method (Triangular wave oscillation frequency setting)

The triangular wave oscillation can be set (together with the setting of charge/discharge current setting of RT pin) by connecting C between the CT pin and GND.

Determine the C value as follows:

Triangular wave oscillation frequency : Fosc Fosc  $\approx 1/\{2\times C\times V/I\}$  [Hz]

V: Triangle wave amplitude TYP 0.5V (Fosc = 10kHz)

\*Note that the amplitude increases with the frequency.

I: Capacitor charge/discharge current. See the RT pin constant

setting method of (5).

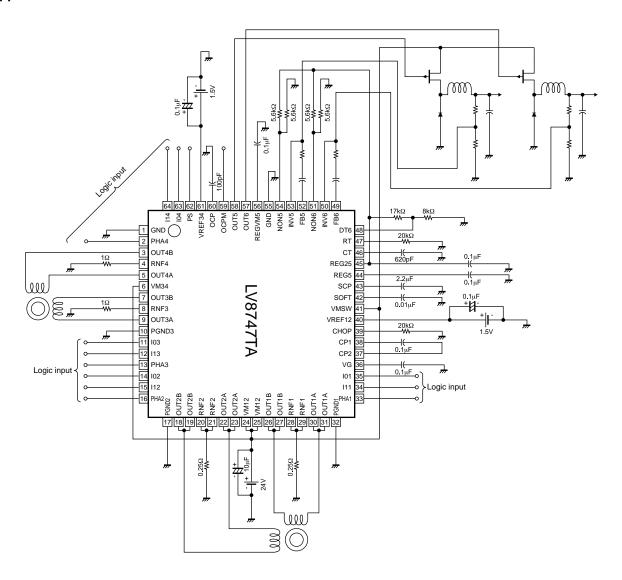

### **Application Circuit**

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa