# LV8013T

#### Allowable Operating Conditions at $Ta = 25^{\circ}C$ , SGND = PGND = 0V

| Parameter                    | Symbol          | Conditions | Ratings              | Unit |

|------------------------------|-----------------|------------|----------------------|------|

| Supply voltage (For load)    | VM              |            | 2.0 to 15.0          | V    |

| Supply voltage (For control) | V <sub>CC</sub> |            | 2.7 to 5.5           | V    |

| Input signal voltage         | VIN             |            | 0 to V <sub>CC</sub> | V    |

| Input signal frequency       | f max           | Duty = 50% | 200                  | kHz  |

| Capacitor for charge pump    | C1, C2,         |            | 0.001 to 0.1         | μF   |

|                              | CVG1, CVG2      |            |                      |      |

# **Electrical Characteristics** at $Ta = 25^{\circ}C$ , $V_{CC} = 5.0V$ , VM = 12.0V, SGND = PGND = 0V, unless especially specified.

| Parameter                                |                  | Symbol Conditions |                                           | Re-   |                     | Ratings |                     | Unit |

|------------------------------------------|------------------|-------------------|-------------------------------------------|-------|---------------------|---------|---------------------|------|

|                                          |                  |                   |                                           | marks | min                 | typ     | max                 | Unit |

| Supply current for load at standby 1     |                  | IM1               | EN = 0V                                   | 1     |                     |         | 1.0                 | μΑ   |

| Supply current for load at standby 2     |                  | IM2               | V <sub>CC</sub> = 0V, Each input = 0V     | 1     |                     |         | 1.0                 | μΑ   |

| Supply current for standby               | or control at    | ICO               | EN = 0V, IN1 = IN2 = 0V                   | 2     | 12.5                | 25      | 50                  | μA   |

| Current drain du                         | ring operation 1 | IC1               | $V_{CC}$ = 3.3V, EN = 3.3V, VG at no load | 3     |                     | 0.6     | 1.0                 | mA   |

| Current drain du                         | ring operation 2 | IC2               | $V_{CC}$ = 5.0V, EN = 5V, VG at no load   | 3     |                     | 0.7     | 1.2                 | mA   |

| H-level input vol                        | tage             | VIH               | $2.7V \le V_{CC} \le 5.5V$                |       | 0.6×V <sub>CC</sub> |         | VCC                 | V    |

| L-level input volt                       | age              | VIL               | $2.7V \le V_{CC} \le 5.5V$                |       | 0                   |         | 0.2×V <sub>CC</sub> | V    |

| H-level input cur<br>(IN1, IN2, TIN)     | rrent            | ЧН                | V <sub>IN</sub> = 5V                      | 4     | 12.5                | 25      | 50                  | μΑ   |

| L-level input current<br>(IN1, IN2, TIN) |                  | ΙIL               | V <sub>IN</sub> = 0V                      | 4     | -1.0                |         |                     | μΑ   |

| Pull-up resistance (EN)                  |                  | RUP               |                                           | 4     | 100                 | 200     | 400                 | kΩ   |

| Pull-down resista<br>(EN)                | ance             | RDN               |                                           | 4     | 100                 | 200     | 400                 | kΩ   |

| Output ON resistance                     |                  | RON               | Sum of ON resistances at top and bottom   | 5     |                     | 0.3     | 0.5                 | Ω    |

| Charge pump voltage1                     |                  | VG1               | V <sub>CC</sub> ×2 - 5.4V CLAMP circuit   | 6     | 5.15                | 5.4     | 5.65                | V    |

| Charge pump vo                           | oltage2          | VG2               | VM + VG1 Voltage raising circuit          | 6     | 17.1                | 17.4    | 17.6                | V    |

| Low-voltage dete<br>voltage              | ection operation | VCS               | V <sub>CC</sub> voltage                   | 7     | 2.1                 | 2.25    | 2.4                 | V    |

| Thermal shutdov<br>temperature           | wn operation     | Tth               | Design guarantee                          | 8     | 150                 | 180     | 210                 | °C   |

| Charge pump ca                           | apacity 1        | VG1LOAD           | IG1 = 500μA                               | 9     | 5.0                 | 5.3     |                     | V    |

| Charge pump ca                           | apacity 2        | VG2LOAD           | IG2 = 500μA                               | 9     | 16.0                | 16.5    |                     | V    |

| IG current dissip<br>(Fin = 20kHz)       | pation           | IG                |                                           | 10    |                     |         | 350                 | μΑ   |

| Charge pump st                           | art time         | TVG               | CVG = 0.1µF                               | 11    |                     |         | 1.0                 | ms   |

| Output 1                                 | Furn on time     | TPLH              |                                           | 12    |                     | 0.5     | 1.0                 | μS   |

| block T                                  | Furn off time    | TPHL              |                                           | 12    |                     | 0.5     | 1.0                 | μS   |

| TOUT 1                                   | Furn on time     | TON               | C = 500pF                                 | 12    |                     | 0.5     | 20                  | μS   |

| 1                                        | Furn off time    | TOFF              | C = 500pF                                 | 12    |                     | 0.5     | 20                  | μS   |

| TOUT output vo                           | Itage H          | ТОН               | C = 500pF                                 |       | VG2-0.1             | VG2     |                     | V    |

| TOUT output voltage L                    |                  | TOL               | C = 500pF                                 |       |                     | 0.05    | 0.1                 | V    |

\* Design guarantee : This characteristics is not measured.

Refer to next page for remarks.

#### Remarks

- 1. It shows current dissipation of VM pin in output OFF state.

- 2. It shows current dissipation of  $V_{CC}$  pin in stand-by state.

- (The standard current depends on EN pin pull-down resistor.)

- 3. It shows current dissipation of  $V_{CC}$  pin in state of EN = 5V (stand-by), including current dissipation of VG pin.

- 4. IN1, IN2 and TIN pin are built-in pull-down resistor, EN pin is built-in pull-up resistor.

- 5. It shows sum of upper and lower saturation voltages of OUT pin.

- 6. It controls charge-pump oscillation and makes specified voltage.

- 7. When low voltage is detected, the lower output is turned OFF.

- 8. When thermal protection circuit is activated, the lower output is turned OFF. When the heat temperature is fallen, it is turned ON again.

- 9. IG (VG pin load current) =  $500\mu$ A

- 10. It shows VG pin current dissipation in state of PWM input for IN pin.

- 11. It specifies start-up time from 10% to 90% when VG is in non-load state (when setting the capacitor between VG and GND to  $0.1\mu$ F and V<sub>CC</sub> is 5V).

- 12. It specifies 10% to 90% for start-up and 90% to 10% for shut-down.

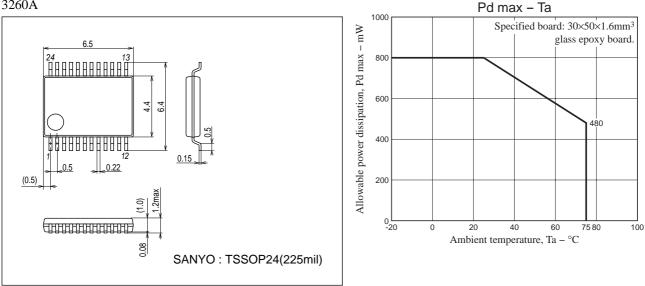

# **Package Dimensions**

unit : mm (typ) 3260A

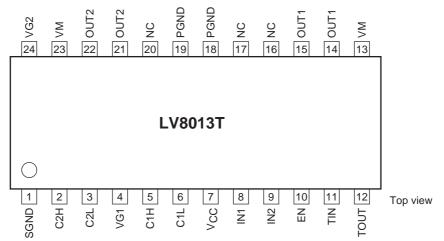

# **Pin Assignment**

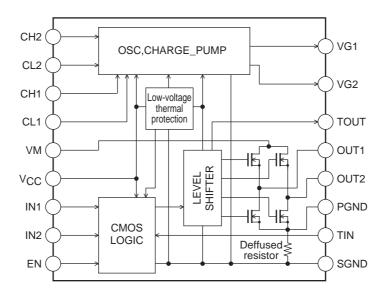

# **Block Diagram**

#### **Truth Table**

| EN | IN1 | IN2 | TIN | OUT1 | OUT2 | TOUT | Charge Pump | Mode                     |

|----|-----|-----|-----|------|------|------|-------------|--------------------------|

|    | н   | Н   | -   | L    | L    | -    | ON -        | Brake                    |

|    | н   | L   | -   | Н    | L    | -    |             | Forward                  |

| н  | L   | Н   | -   | L    | н    | -    |             | Reverse                  |

| п  | L   | L   | -   | Z    | Z    | -    |             | Standby                  |

|    | -   | -   | L   | -    | -    | L    |             | Tr-OFF                   |

|    | -   | -   | н   | -    | -    | н    |             | Tr-ON                    |

| L  | -   | -   | -   | L    | L    | L    | OFF         | Standby                  |

|    |     |     |     |      |      |      | - : Don't   | care, Z : High-Impedance |

• Current drain becomes zero in the standby mode. (Leak current from EN pin is excluded)

• The output side becomes OFF, with motor drive stopped, during voltage reduction and thermal protection.

Also, the charge of VG2 is discharged with an internal circuit at decreasing voltage.

#### Pin No. Pin name Function Equivalent circuit 6 C1L Voltage raising capacitor connection pin. ∨сс C1L ( 5 C1H Voltage raising capacitor connection pin. ) VG1 Ş C1H ( IN1 8 · Driver output changeover. Vcc 9 IN2 TIN 11 · TOUT output control pin. ★ (Built-in pull-down resistor) ≷200kΩ ₩

#### Pin Function

Continued on next page.

| Pin No.                          | Pin name                             | Function                                                                                                                                                    | Equivalent circuit                                                 |

|----------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 10                               | EN                                   | Logic enable pin.<br>(Built-in pull-up resistor)                                                                                                            |                                                                    |

| 14<br>15<br>21<br>22<br>18<br>19 | OUT1<br>OUT2<br>OUT2<br>PGND<br>PGND | Driver output pin.                                                                                                                                          | OUT1<br>OUT1<br>OUT2<br>OUT2<br>PGND                               |

| 12                               | TOUT                                 | Voltage raising output pin.                                                                                                                                 | VG2                                                                |

| 13<br>23                         | VM<br>VM                             | Motor power supply.<br>(both terminals to be connected)                                                                                                     |                                                                    |

| 7                                | V <sub>CC</sub>                      | Logic power supply.                                                                                                                                         |                                                                    |

| 4                                | VG1                                  | Voltage raising circuit 1.<br>V <sub>CC</sub> × 2<br>Clamped to 5.4V                                                                                        | C1H<br>C1H<br>C1L<br>C1L<br>C1L<br>C1L<br>C1L<br>C1L<br>C1L<br>C1L |

| 24<br>2<br>3                     | VG2<br>C2H<br>C2L                    | <ul> <li>Voltage raising circuit 2.</li> <li>VM + VG1</li> <li>Voltage raising capacitor connection pin.</li> <li>VG2 is discharged in abnormal.</li> </ul> | VM<br>VG2<br>0.1µF<br>C2H<br>0.01µF<br>C2L<br>0.1µF                |

| 1                                | SGND                                 | Logic GND                                                                                                                                                   |                                                                    |

| 18                               | PGND                                 | Driver GND                                                                                                                                                  |                                                                    |

| 19                               | PGND                                 | (both terminals to be connected)                                                                                                                            |                                                                    |

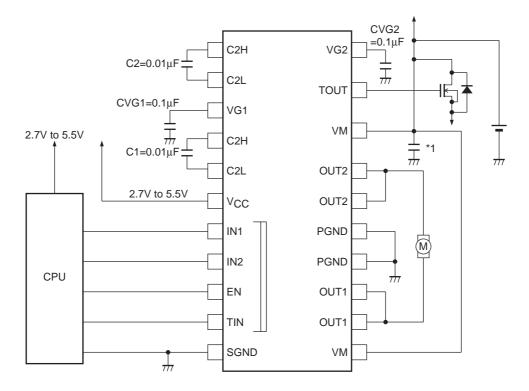

### **Application Circuit Example**

- \*1 : Connect a kickback absorption capacitor directly near IC. Coil kick-back may cause rise of the voltage of VM line, and the voltage exceeding the maximum rating may be applied momentarily, resulting in deterioration or damage of IC.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of November, 2008. Specifications and information herein are subject to change without notice.