### TABLE OF CONTENTS

| Features                            | 1 |

|-------------------------------------|---|

| Applications                        | 1 |

| Typical Application                 |   |

| Description                         |   |

| Absolute Maximum Ratings            |   |

| Order Information                   |   |

| Pin Configuration                   |   |

| Electrical Characteristics          |   |

| Typical Performance Characteristics |   |

| Pin Functions                       |   |

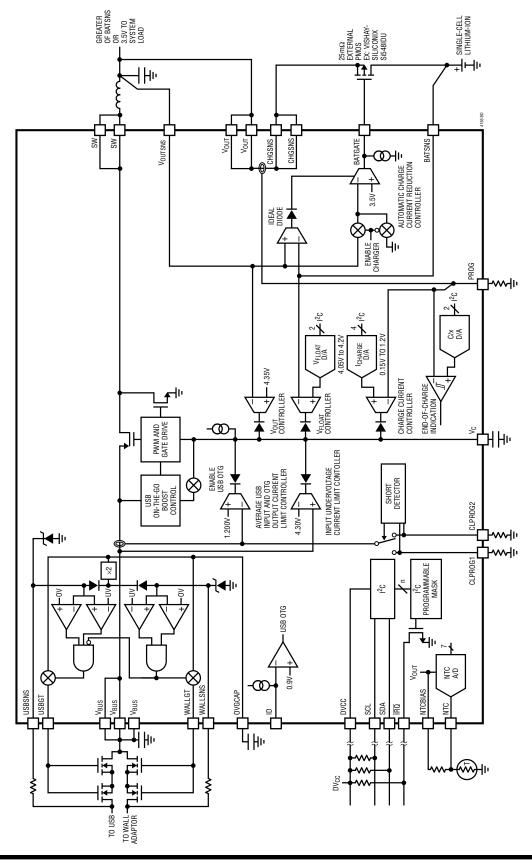

| Block Diagram                       |   |

| Timing Diagrams                     |   |

| Operation                           |   |

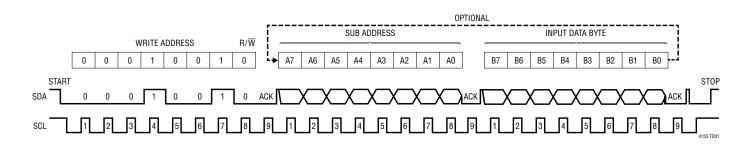

| I <sup>2</sup> C                    |   |

| Applications Information            |   |

| Typical Applications                |   |

| Package Description                 |   |

| Typical Application                 |   |

| Related Parts                       |   |

|                                     |   |

### ABSOLUTE MAXIMUM RATINGS

(Notes 1, 2)

| $V_{BUS}$ (Transient) t < 1ms, Duty Cycle < 1% –0.3V to 7V $V_{BUS}$ (Steady State), BATSNS, $\overline{IRQ}$ , NTC –0.3V to 6V |

|---------------------------------------------------------------------------------------------------------------------------------|

| DVCC, SDA, SCL (Note 3)0.3V to $V_{\mbox{MAX}}$                                                                                 |

| I <sub>WALLSNS</sub> , I <sub>USBSNS</sub> ±20mA                                                                                |

| I <sub>NTCBIAS</sub> , I <sub>IRQ</sub> 10mA                                                                                    |

| I <sub>SW</sub> , I <sub>VOUT</sub> , I <sub>CHGSNS</sub> (Both Pins in Each Case)4A                                            |

| Operating Junction Temperature Range –40°C to 125°C                                                                             |

| Storage Temperature Range65°C to 150°C                                                                                          |

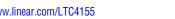

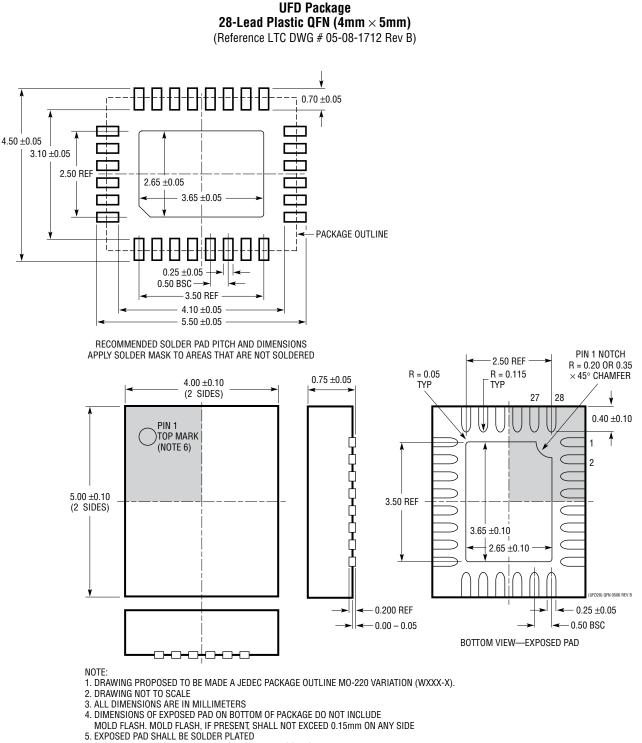

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION                      | TEMPERATURE RANGE |

|------------------|-------------------|---------------|------------------------------------------|-------------------|

| LTC4155EUFD#PBF  | LTC4155EUFD#TRPBF | 4155          | 28-Lead (4mm × 5mm × 0.75mm) Plastic QFN | -40°C to 125°C    |

| LTC4155IUFD#PBF  | LTC4155IUFD#TRPBF | 4155          | 28-Lead (4mm × 5mm × 0.75mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

| SYMBOL                   | PARAMETER                                                                                   | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | MIN                                                                                                             | TYP                                                                                                                  | MAX                                                                                                                   | UNITS                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Switching Ba             | ttery Charger                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                                                                                 |                                                                                                                      |                                                                                                                       |                                                                                 |

| V <sub>BUS</sub>         | Input Supply Voltage                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 4.35                                                                                                            |                                                                                                                      | 5.5                                                                                                                   | V                                                                               |

| V <sub>BUSREG</sub>      | Undervoltage Current Reduction                                                              | Input Undervoltage Current Limit Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                                                                 | 4.30                                                                                                                 |                                                                                                                       | V                                                                               |

| I <sub>VBUSQ</sub>       | Input Quiescent Current                                                                     | USB Suspend Mode<br>100mA I <sub>VBUS</sub> Mode, I <sub>VOUT</sub> = 0µA, Charger Off<br>500mA – 3A I <sub>VBUS</sub> Modes, I <sub>VOUT</sub> = 0µA, Charger Off                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                                                                 | 0.060<br>0.560<br>17                                                                                                 |                                                                                                                       | mA<br>mA<br>mA                                                                  |

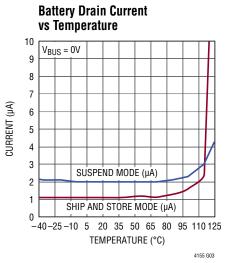

| I <sub>BATQ</sub>        | Battery Drain Current                                                                       | $V_{BUS} > V_{UVLO}$ , Battery Charger Off, $I_{VOUT} = 0\mu A$<br>$V_{BUS} = 0V$ , $I_{VOUT} = 0\mu A$<br>Storage and Shipment Mode, DVCC = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                                                                                 | 7.0<br>2.0<br>0.6                                                                                                    | 3.0<br>1.25                                                                                                           | μΑ<br>μΑ<br>μΑ                                                                  |

| Ivbuslim                 | Total Input Current When Load<br>Exceeds Power Limit                                        | 100mA I <sub>VBUS</sub> Mode (USB Lo Power) (Default)<br>500mA I <sub>VBUS</sub> Mode (USB Hi Power)<br>600mA I <sub>VBUS</sub> Mode<br>700mA I <sub>VBUS</sub> Mode<br>800mA I <sub>VBUS</sub> Mode<br>900mA I <sub>VBUS</sub> Mode (USB 3.0)<br>1.00A I <sub>VBUS</sub> Mode<br>1.25A I <sub>VBUS</sub> Mode<br>1.50A I <sub>VBUS</sub> Mode<br>1.50A I <sub>VBUS</sub> Mode<br>2.00A I <sub>VBUS</sub> Mode<br>2.25A I <sub>VBUS</sub> Mode<br>2.50A I <sub>VBUS</sub> Mode<br>2.50A I <sub>VBUS</sub> Mode<br>3.00A I <sub>VBUS</sub> Mode (Default)<br>2.5mA I <sub>VBUS</sub> Mode (USB Suspend) | • | 65<br>460<br>550<br>650<br>745<br>800<br>950<br>1150<br>1425<br>1650<br>1900<br>2050<br>2350<br>2550<br>2800    | 80<br>480<br>570<br>670<br>770<br>850<br>1000<br>1230<br>1500<br>1750<br>2000<br>2175<br>2475<br>2725<br>2950<br>1.8 | 100<br>500<br>600<br>700<br>800<br>900<br>1025<br>1300<br>1575<br>1875<br>2125<br>2300<br>2600<br>2900<br>3100<br>2.5 | MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>MA<br>M |

| V <sub>FLOAT</sub>       | BATSNS Regulated Output Voltage<br>Selected by I <sup>2</sup> C Control.<br>Switching Modes | 4.05V Setting (Default)<br>4.10V Setting<br>4.15V Setting<br>4.20V Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 4.02<br>4.07<br>4.12<br>4.17                                                                                    | 4.05<br>4.10<br>4.15<br>4.20                                                                                         | 4.08<br>4.13<br>4.18<br>4.23                                                                                          | V<br>V<br>V<br>V                                                                |

| Icharge                  | Regulated Battery Charge Current<br>Selected by I <sup>2</sup> C Control                    | 12.50% Charge Current Mode<br>18.75% Charge Current Mode<br>25.00% Charge Current Mode<br>31.25% Charge Current Mode<br>37.50% Charge Current Mode<br>43.75% Charge Current Mode<br>50.00% Charge Current Mode<br>56.25% Charge Current Mode<br>62.50% Charge Current Mode<br>68.75% Charge Current Mode<br>81.25% Charge Current Mode<br>81.25% Charge Current Mode<br>87.50% Charge Current Mode<br>93.75% Charge Current Mode<br>100.0% Charge Current Mode (Default)                                                                                                                               |   | 290<br>430<br>577<br>720<br>870<br>1013<br>1162<br>1316<br>1458<br>1601<br>1743<br>1881<br>2024<br>2166<br>2309 | 315<br>465<br>620<br>770<br>925<br>1075<br>1230<br>1385<br>1535<br>1685<br>1835<br>1980<br>2130<br>2280<br>2430      | 340<br>500<br>663<br>820<br>981<br>1137<br>1298<br>1454<br>1612<br>1769<br>1927<br>2079<br>2237<br>2394<br>2552       | mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>m |

| I <sub>CHARGE(MAX)</sub> | Regulated Battery Charge Current                                                            | 100.0% Charge Current Mode, $R_{PROG}$ = 340 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 3.44                                                                                                            | 3.57                                                                                                                 | 3.70                                                                                                                  | A                                                                               |

| V <sub>OUT</sub>         | PowerPath Regulated Output<br>Voltage (V <sub>BUS</sub> Power Available)                    | Suspend Mode, $I_{VOUT}$ = 1mA<br>Battery Charger Enabled, Charging, BATSNS $\geq$ 3.5V<br>Battery Charger Terminated or Battery Charger<br>Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                                                                                 | 4.35<br>BATSNS<br>4.35                                                                                               | 4.5<br>4.5                                                                                                            | V<br>V<br>V                                                                     |

| V <sub>OUT(MIN)</sub>    | Low Battery Instant-On Output<br>Voltage (V <sub>BUS</sub> Power Available)                 | Battery Charger Enabled, Charging, BATSNS $\leq$ 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 3.40                                                                                                            | 3.50                                                                                                                 |                                                                                                                       | V                                                                               |

| SYMBOL                           | PARAMETER                                                                                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MIN                          | ТҮР                                                                                                                    | МАХ                          | UNITS                                                                           |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------|

| I <sub>VOUT</sub>                | V <sub>OUT</sub> Current Available Before<br>Loading Battery                                                             | 2.5mA I <sub>VBUS</sub> Mode (USB Suspend)<br>100mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>500mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>600mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>700mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>800mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>900mA I <sub>VBUS</sub> Mode, BAT = 3.3V<br>1.00A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>1.25A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>1.50A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>1.50A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.00A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.00A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.25A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.50A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.50A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>2.50A I <sub>VBUS</sub> Mode, BAT = 3.3V<br>3.00A I <sub>VBUS</sub> Mode, BAT = 3.3V | 1                            | 1.3<br>76<br>673<br>810<br>944<br>1093<br>1200<br>1397<br>1728<br>2072<br>2411<br>2700<br>2846<br>3154<br>3408<br>3657 |                              | mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>m |

| VPROG                            | PROG Pin Servo Voltage                                                                                                   | 12.50% Charge Current Mode<br>18.75% Charge Current Mode<br>25.00% Charge Current Mode<br>31.25% Charge Current Mode<br>37.50% Charge Current Mode<br>43.75% Charge Current Mode<br>50.00% Charge Current Mode<br>56.25% Charge Current Mode<br>62.50% Charge Current Mode<br>68.75% Charge Current Mode<br>81.25% Charge Current Mode<br>87.50% Charge Current Mode<br>93.75% Charge Current Mode<br>100.0% Charge Current Mode (Default)                                                                                                                                                                                                                                                     |                              | 150<br>225<br>300<br>375<br>450<br>525<br>600<br>675<br>750<br>825<br>900<br>975<br>1050<br>1125<br>1200               |                              | mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>m |

| V <sub>RECHRG</sub>              | Recharge Battery Threshold<br>Voltage                                                                                    | Threshold Voltage Relative to V <sub>FLOAT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96.6                         | 97.6                                                                                                                   | 98.4                         | %                                                                               |

| t <sub>terminate</sub>           | Safety Timer Termination Period Selected by I <sup>2</sup> C Control. Timer Starts When BATSNS $\geq$ V <sub>FLOAT</sub> | 1-Hour Mode<br>2-Hour Mode<br>4-Hour Mode (Default)<br>8-Hour Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.95<br>1.90<br>3.81<br>7.63 | 1.06<br>2.12<br>4.24<br>8.48                                                                                           | 1.17<br>2.33<br>4.66<br>9.32 | Hours<br>Hours<br>Hours<br>Hours                                                |

| V <sub>LOWBAT</sub>              | Threshold Voltage                                                                                                        | Rising Threshold<br>Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.65                         | 2.8<br>130                                                                                                             | 2.95                         | V<br>mV                                                                         |

| t <sub>BADBAT</sub>              | Bad Battery Termination Time                                                                                             | BATSNS < $(V_{LOWBAT} - \Delta V_{LOWBAT})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.47                         | 0.53                                                                                                                   | 0.59                         | Hours                                                                           |

| V <sub>C/x</sub>                 | Full Capacity Charge Indication<br>PROG Voltage Selected by I <sup>2</sup> C<br>Control                                  | $\begin{array}{l} C/10 \mbox{ Mode } (I_{CHARGE} = 10\%FS) \mbox{ (Default)} \\ C/5 \mbox{ Mode } (I_{CHARGE} = 20\%FS) \\ C/20 \mbox{ Mode } (I_{CHARGE} = 5\%FS) \\ C/50 \mbox{ Mode } (I_{CHARGE} = 2\%FS) \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 110<br>230<br>15<br>50       | 120<br>240<br>24<br>60                                                                                                 | 130<br>250<br>33<br>70       | mV<br>mV<br>mV<br>mV                                                            |

| h <sub>PROG</sub>                | Ratio of I <sub>CHGSNS</sub> to PROG Pin<br>Current                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              | 1000                                                                                                                   |                              | mA/mA                                                                           |

| h <sub>CLPROG1</sub><br>(Note 4) | Ratio of Measured V <sub>BUS</sub> Current to CLPROG1 Sense Current                                                      | CLPROG1 I <sub>VBUS</sub> Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              | 990                                                                                                                    |                              | mA/mA                                                                           |

| SYMBOL                           | PARAMETER                                                               | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN               | ТҮР                                                                                                         | MAX          | UNITS                                                                                                             |

|----------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| h <sub>CLPROG2</sub><br>(Note 4) | Ratio of Measured V <sub>BUS</sub> Current to<br>CLPROG2 Sense Current  | 2.5mA I <sub>VBUS</sub> Mode (USB Suspend)<br>100mA I <sub>VBUS</sub> Mode<br>500mA I <sub>VBUS</sub> Mode<br>600mA I <sub>VBUS</sub> Mode<br>700mA I <sub>VBUS</sub> Mode<br>800mA I <sub>VBUS</sub> Mode<br>900mA I <sub>VBUS</sub> Mode<br>1.00A I <sub>VBUS</sub> Mode<br>1.25A I <sub>VBUS</sub> Mode<br>1.50A I <sub>VBUS</sub> Mode<br>2.00A I <sub>VBUS</sub> Mode<br>2.25A I <sub>VBUS</sub> Mode<br>2.50A I <sub>VBUS</sub> Mode<br>2.50A I <sub>VBUS</sub> Mode<br>2.75A I <sub>VBUS</sub> Mode<br>3.00A I <sub>VBUS</sub> Mode |                   | 19<br>79<br>466<br>557<br>758<br>839<br>990<br>1222<br>1494<br>1746<br>1999<br>2175<br>2477<br>2730<br>2956 |              | mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA<br>mA/mA |

| V <sub>CLPROG1</sub>             | CLPROG1 Servo Voltage in<br>Current Limit                               | CLPROG1 I <sub>VBUS</sub> Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | 1.2                                                                                                         |              | V                                                                                                                 |

| V <sub>CLPROG2</sub>             | CLPROG2 Servo Voltage in<br>Current Limit                               | 2.5mA I <sub>VBUS</sub> Mode (USB Suspend)<br>100mA – 3A I <sub>VBUS</sub> Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   | 103<br>1.2                                                                                                  |              | mV<br>V                                                                                                           |

| f <sub>OSC</sub>                 | Switching Frequency                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.05              | 2.25                                                                                                        | 2.50         | MHz                                                                                                               |

| R <sub>PMOS</sub>                | High Side Switch On Resistance                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 0.090                                                                                                       |              | Ω                                                                                                                 |

| R <sub>NMOS</sub>                | Low Side Switch On Resistance                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 0.080                                                                                                       |              | Ω                                                                                                                 |

| R <sub>CHG</sub>                 | Battery Charger Current Sense<br>Resistance                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 0.040                                                                                                       |              | Ω                                                                                                                 |

| I <sub>PEAK</sub>                | Peak Inductor Current Clamp                                             | 500mA – 3A I <sub>VBUS</sub> Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   | 6.7                                                                                                         |              | A                                                                                                                 |

| Step-Up Mod                      | e PowerPath Switching Regulator (US                                     | SB On-The-Go)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                                                                                                             |              |                                                                                                                   |

| V <sub>BUS</sub>                 | Output Voltage                                                          | $0mA \le I_{VBUS} \le 500mA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.75              |                                                                                                             | 5.25         | V                                                                                                                 |

| V <sub>OUT</sub>                 | Input Voltage                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.9               |                                                                                                             |              | V                                                                                                                 |

| IVBUSOTG                         | Output Current Limit                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 1.4                                                                                                         |              | A                                                                                                                 |

| Ivoutotgq                        | V <sub>OUT</sub> Quiescent Current                                      | I <sub>VBUS</sub> = 0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | 1.96                                                                                                        |              | mA                                                                                                                |

| V <sub>CLPROG2</sub>             | Output Current Limit Servo Voltage                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | 1.2                                                                                                         |              | V                                                                                                                 |

| VBATSNSUVLO                      | V <sub>BATSNS</sub> Undervoltage Lockout                                | V <sub>BATSNS</sub> Falling<br>Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.65              | 2.8<br>130                                                                                                  | 2.95         | V<br>mV                                                                                                           |

| t <sub>SCFAULT</sub>             | Short-Circuit Fault Delay                                               | V <sub>BUS</sub> < 4V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   | 7.2                                                                                                         |              | ms                                                                                                                |

|                                  | Protection, Priority Multiplexer and U<br>WALLSNS Through 3.6k Resistor | ndervoltage Lockout; USB Input Connected to US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BSNS Through 3.6k | Resistor;                                                                                                   | WALL Inpu    | t                                                                                                                 |

| V <sub>UVLO</sub>                | USB Input, Wall Input<br>Undervoltage Lockout                           | Rising Threshold<br>Falling Threshold<br>Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.05<br>3.90      | 100                                                                                                         | 4.45<br>4.25 | V<br>V<br>mV                                                                                                      |

| V <sub>DUVLO</sub>               | USB Input, Wall Input to BATSNS<br>Differential Undervoltage Lockout    | Rising Threshold<br>Falling Threshold<br>Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100<br>50         | 70                                                                                                          | 425<br>375   | mV<br>mV<br>mV                                                                                                    |

| V <sub>OVLO</sub>                | USB Input, Wall Input Overvoltage<br>Protection Threshold               | Rising Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.75              | 6.0                                                                                                         | 6.3          | V                                                                                                                 |

| VUSBGTACTV                       | USBGT Output Voltage Active                                             | USBSNS < V <sub>USBOVLO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | 2 • V <sub>USBSN</sub>                                                                                      | S            | V                                                                                                                 |

| VWALLGTACTV                      | WALLGT Output Voltage Active                                            | WALLSNS < V <sub>WALLOVLO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                 | 2∙V <sub>WALLSN</sub>                                                                                       | S            | V                                                                                                                 |

| VUSBGTPROT                       | USBGT Output Voltage Protected                                          | USBSNS > V <sub>USBOVLO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | 0                                                                                                           |              | V                                                                                                                 |

| SYMBOL                                  | PARAMETER                                                      | CONDITIONS                                                                                                                                     | MIN       | ТҮР         | MAX              | UNITS          |

|-----------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|------------------|----------------|

| V <sub>WALLGTPROT</sub>                 | WALLGT Output Voltage Protected                                | WALLSNS > V <sub>WALLOVLO</sub>                                                                                                                |           | 0           |                  | V              |

| V <sub>USBGTLOAD</sub> ,<br>Vwallgtload | USBGT, WALLGT Voltage Under<br>Load                            | 5V Through 3.6k into WALLSNS, USBSNS, $I_{USBGT}$ , $I_{WALLGT} = 1\mu A$                                                                      | 8.4       | 8.9         |                  | V              |

| IUSBSNSQ                                | USBSNS Quiescent Current                                       | V <sub>USBSNS</sub> = 5V, V <sub>USBSNS</sub> > V <sub>WALLSNS</sub><br>V <sub>USBSNS</sub> = 5V, V <sub>WALLSNS</sub> > V <sub>USBSNS</sub>   |           | 27<br>54    |                  | μA<br>μA       |

| IWALLSNSQ                               | WALLSNS Quiescent Current                                      | V <sub>WALLSNS</sub> = 5V, V <sub>WALLSNS</sub> > V <sub>USBSNS</sub><br>V <sub>WALLSNS</sub> = 5V, V <sub>USBSNS</sub> > V <sub>WALLSNS</sub> |           | 27<br>54    |                  | μA<br>μA       |

| t <sub>RISE</sub>                       | OVGCAP Time to Reach Regulation                                | C <sub>OVGCAP</sub> = 1nF                                                                                                                      |           | 1.2         |                  | ms             |

| IRQ Pin Chara                           | cteristics                                                     |                                                                                                                                                |           |             |                  | ·              |

| IIRQ                                    | IRQ Pin Leakage Current                                        | $V_{\overline{IRQ}} = 5V$                                                                                                                      |           |             | 1                | μA             |

| VIRQ                                    | IRQ Pin Output Low Voltage                                     | I <sub>ĪRQ</sub> = 5mA                                                                                                                         |           | 75          | 100              | mV             |

| ID Pin Charact                          | teristics                                                      |                                                                                                                                                | <u> </u>  |             |                  | ·              |

| I <sub>ID</sub>                         | ID Pin Pull-Up Current                                         | V <sub>ID</sub> = 0V                                                                                                                           | 35        | 55          | 85               | μA             |

| V <sub>ID_OTG</sub>                     | ID Pin Threshold Voltage                                       | ID Pin Falling<br>Hysteresis                                                                                                                   | 0.5       | 0.86<br>0.2 | 0.95             | V<br>V         |

| Overtemperate                           | ure Battery Conditioner                                        | 1                                                                                                                                              | 11        |             |                  | · · ·          |

| BATOVERTEMP                             | Overtemp Battery Discharge<br>Current                          | Only When Enabled via I <sup>2</sup> C Control                                                                                                 |           | 125         |                  | mA             |

| VBATOVERTEMP                            | Overtemp Battery Voltage Target                                | Only When Enabled via I <sup>2</sup> C Control                                                                                                 |           | 3.85        |                  | V              |

|                                         | easurement System                                              |                                                                                                                                                | 11        |             |                  | <u> </u>       |

| $\kappa_{0FFSET}$                       | V <sub>NTC</sub> / V <sub>NTCBIAS</sub> A/D Lower Range        | V <sub>NTC</sub> / V <sub>NTCBIAS</sub> Ratio Below Which Only 0x00<br>Is Returned                                                             |           | 0.113       |                  | V/V            |

| $\kappa_{HIGH}$                         | V <sub>NTC</sub> / V <sub>NTCBIAS</sub> A/D Upper Range<br>End | V <sub>NTC</sub> / V <sub>NTCBIAS</sub> Ratio Above Which Only 0x7F<br>Is Returned                                                             |           | 0.895       |                  | V/V            |

| $\kappa_{\text{SPAN}}$                  | A/D Span Coefficient<br>(Decimal Format)                       |                                                                                                                                                | 6.091     | 6.162       | 6.191            | mV/V/LSB       |

| d <sub>TOO_COLD</sub>                   | NTCVAL at NTC_TOO_COLD<br>(Decimal Format)                     | Warning Threshold<br>Reset Threshold                                                                                                           | 102<br>98 | 102<br>98   | 102<br>98        | Count<br>Count |

| d <sub>TOO_WARM</sub>                   | NTCVAL at NTC_TOO_WARM<br>(Decimal Format)                     | Warning Threshold<br>Reset Threshold                                                                                                           | 41<br>45  | 41<br>45    | 41<br>45         | Count<br>Count |

| d <sub>HOT_FAULT</sub>                  | NTCVAL at HOT_FAULT<br>(Decimal Format)                        | Fault Threshold<br>Reset Threshold                                                                                                             | 19<br>23  | 19<br>23    | 19<br>23         | Count<br>Count |

| I <sub>NTC</sub>                        | NTC Leakage Current                                            |                                                                                                                                                | -100      |             | 100              | nA             |

| ldeal Diode                             |                                                                |                                                                                                                                                | <u> </u>  |             |                  | -              |

| V <sub>FWD</sub>                        | Forward Voltage Detection                                      | Input Power Available, Battery Charger Off                                                                                                     |           | 15          |                  | mV             |

| I <sup>2</sup> C Port                   | l                                                              | I                                                                                                                                              |           |             |                  | <u> </u>       |

| DVCC                                    | I <sup>2</sup> C Logic Reference Level                         | (Note 3)                                                                                                                                       | 1.7       |             | V <sub>MAX</sub> | V              |

| IDVCCQ                                  | DVCC Current                                                   | SCL/SDA = 0kHz                                                                                                                                 |           | 0.25        |                  | μA             |

| V <sub>DVCC_UVL0</sub>                  | DVCC UVLO                                                      |                                                                                                                                                |           | 1.0         |                  | V              |

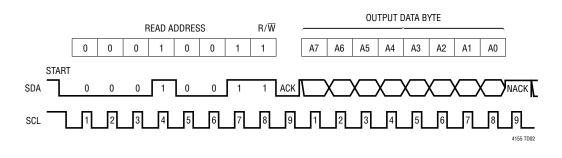

| ADDRESS                                 | I <sup>2</sup> C Address                                       |                                                                                                                                                | 00        | 01_001[R/\  | W]b              |                |

| V <sub>IH</sub> , <sub>SDA,SCL</sub>    | Input High Threshold                                           |                                                                                                                                                | 70        |             | -                | % DVCC         |

| V <sub>IL</sub> , <sub>SDA,SCL</sub>    | Input Low Threshold                                            |                                                                                                                                                |           |             | 30               | % DVCC         |

| IIH,SDA,SCL                             | Input Leakage High                                             | SDA, SCL = DVCC                                                                                                                                | -1        |             | 1                | μA             |

|                                         |                                                                | 1                                                                                                                                              | 11        |             |                  | · ·            |

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A \approx T_J = 25^{\circ}C$  (Note 2).  $V_{BUS} = 5V$ , BATSNS = 3.7V, DVCC = 3.3V,  $R_{CLPROG1} = R_{CLPROG2} = 1.21k$ ,  $R_{PROG} = 499\Omega$ , unless otherwise noted.

| SYMBOL                   | PARAMETER                                      | CONDITIONS             | MIN | I TYP | MAX | UNITS |

|--------------------------|------------------------------------------------|------------------------|-----|-------|-----|-------|

| I <sub>IL</sub> ,SDA,SCL | Input Leakage Low                              | SDA, SCL = 0V          | -1  |       | 1   | μA    |

| V <sub>OL</sub>          | Digital Output Low (SDA)                       | I <sub>SDA</sub> = 3mA |     |       | 0.4 | V     |

| f <sub>SCL</sub>         | Clock Operating Frequency                      |                        |     |       | 400 | kHz   |

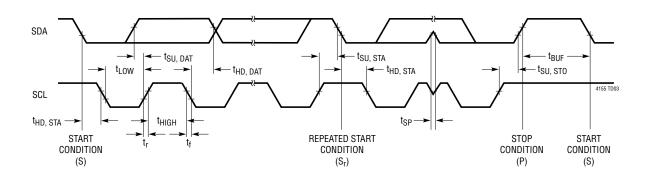

| t <sub>BUF</sub>         | Bus Free Time Between STOP and START Condition |                        | 1.3 |       |     | μs    |

| t <sub>HD_SDA</sub>      | Hold Time After (Repeated) START Condition     |                        | 0.6 |       |     | μs    |

| t <sub>SU_SDA</sub>      | Repeated START Condition Set-Up Time           |                        | 0.6 |       |     | μs    |

| t <sub>SU_STO</sub>      | STOP Condition Time                            |                        | 0.6 |       |     | μs    |

| t <sub>HD_DAT(OUT)</sub> | Data Hold Time                                 |                        | 0   |       | 900 | ns    |

| t <sub>HD_DAT(IN)</sub>  | Input Data Hold Time                           |                        | 0   |       |     | ns    |

| t <sub>SU_DAT</sub>      | Data Set-Up Time                               |                        | 100 | )     |     | ns    |

| t <sub>LOW</sub>         | Clock LOW Period                               |                        | 1.3 |       |     | μs    |

| t <sub>HIGH</sub>        | Clock HIGH Period                              |                        | 0.6 |       |     | μs    |

| t <sub>f</sub>           | Clock Data Fall Time                           |                        | 20  |       | 300 | ns    |

| t <sub>r</sub>           | Clock Data Rise Time                           |                        | 20  |       | 300 | ns    |

| t <sub>SP</sub>          | Spike Suppression Time                         |                        |     |       | 50  | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4155E is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC4155E is guaranteed to meet performance specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC4155I is guaranteed over the full -40°C to 125°C operating junction temperature ( $T_J$ , in °C) is

calculated from the ambient temperature (T\_A, in °C) and power dissipation (P\_D, in watts) according to the formula:

$T_J$  =  $T_A$  + (P\_D •  $\theta_{JA}),$  where the package thermal impedance  $\theta_{JA}$  = 43°C/W)

Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

Note 3.  $V_{MAX}$  is the maximum of  $V_{BUS}$  or BATSNS

Note 4. Total input current is  $I_{VBUSQ} + V_{CLPROG}/R_{CLPROG} \bullet (h_{CLPROG} + 1)$ .

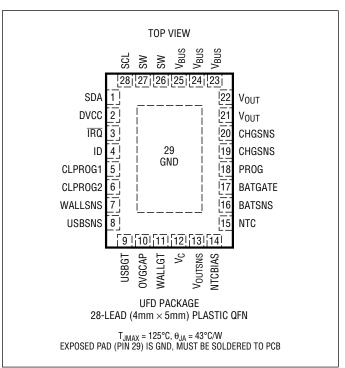

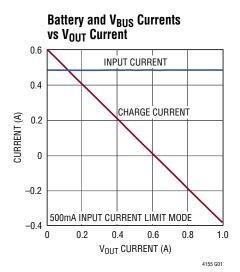

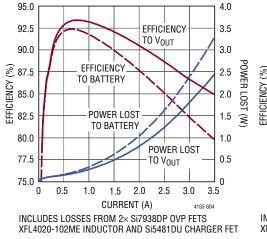

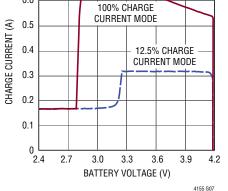

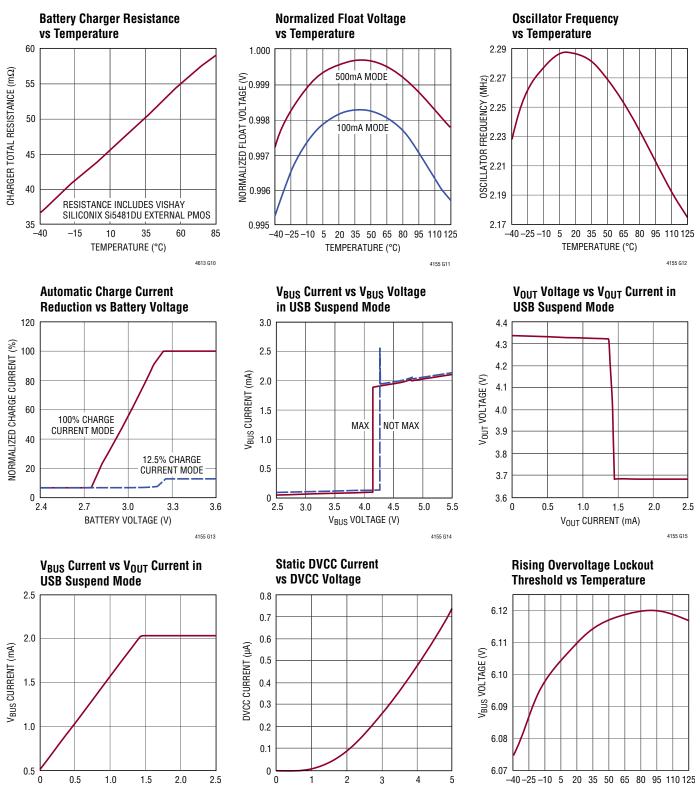

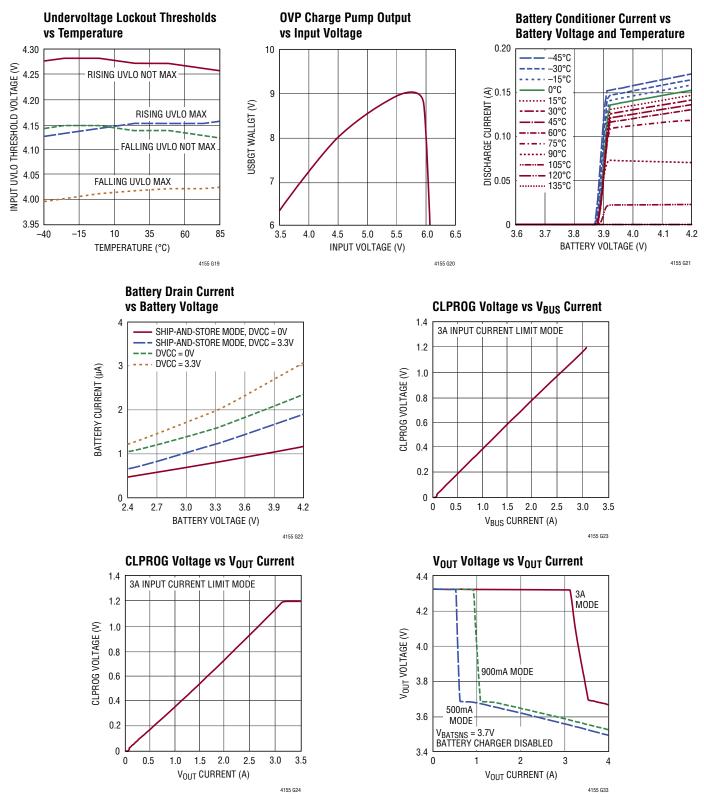

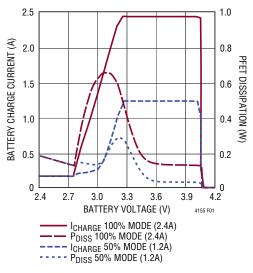

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ (Note 2). $V_{BUS} = 5V$ , BATSNS = 3.7V, DVCC = 3.3V, $R_{CLPROG1} = R_{CLPROG2} = 1.21k$ , $R_{PROG} = 499\Omega$ , unless otherwise noted.

**Battery Charger Total Efficiency**

vs Battery Voltage

100

95

90

85

80

75

70

65

60

55

24

2.7

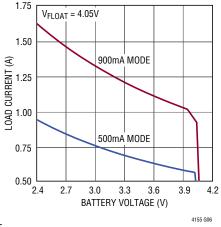

#### **USB Compliant Load Current** Available Before Discharging **Battery**

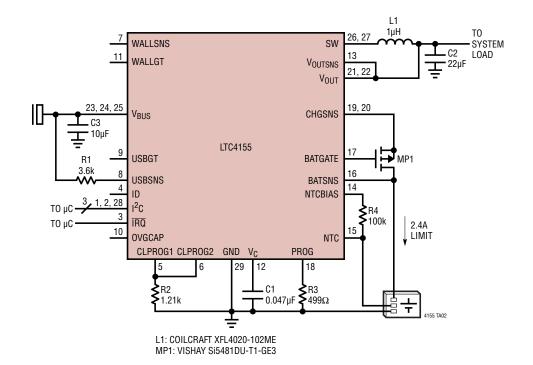

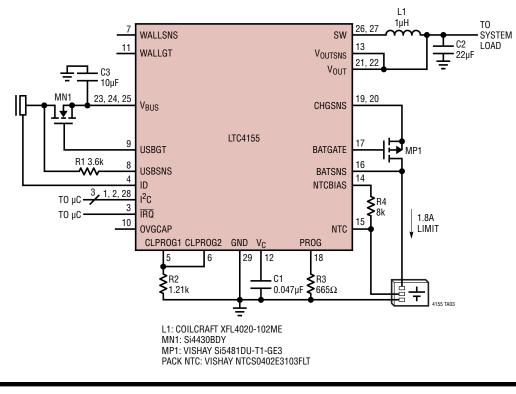

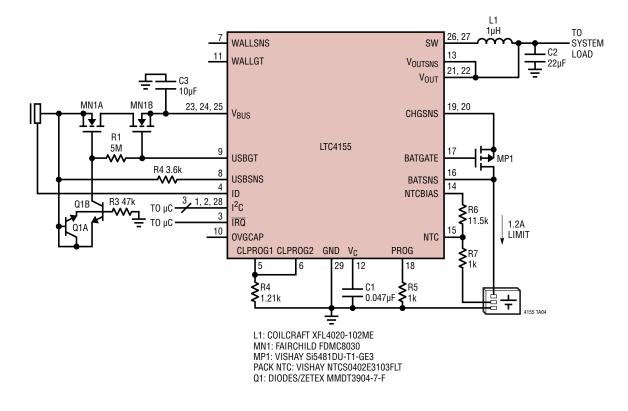

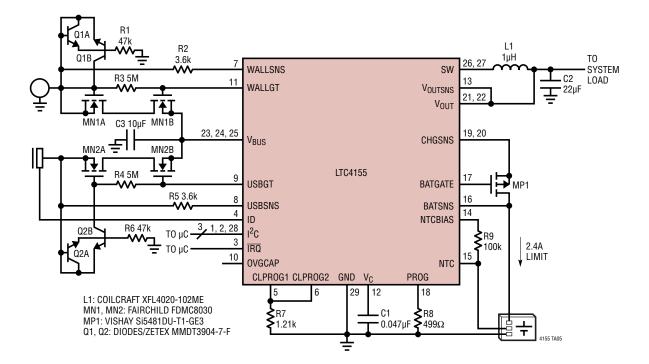

BATTERY VOLTAGE (V) 4155 G05 INCLUDES LOSSES FROM 2× Si7938DP OVP FETS XFL4020-102ME INDUCTOR AND Si5481DU CHARGER FET

3.3

3.6

3.9

4.2

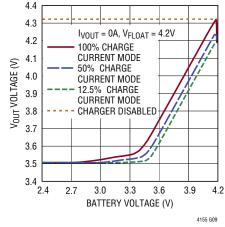

#### V<sub>OUT</sub> Voltage vs Battery Voltage

4155fd

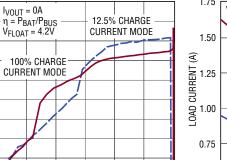

Switching Regulator Efficiency

Downloaded from Arrow.com

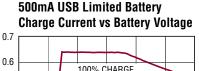

**100mA USB Limited Battery Charge Current vs Battery Voltage**

3.0

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ (Note 2). $V_{BUS} = 5V$ , BATSNS = 3.7V, DVCC = 3.3V, $R_{CLPROG1} = R_{CLPROG2} = 1.21k$ , $R_{PROG} = 499\Omega$ , unless otherwise noted.

4155fd

4155 G18

V<sub>OUT</sub> CURRENT (mA)

4155 G16

DVCC VOLTAGE (V)

4155 G17

TEMPERATURE (°C)

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ (Note 2). $V_{BUS} = 5V$ , BATSNS = 3.7V, DVCC = 3.3V, $R_{CLPROG1} = R_{CLPROG2} = 1.21k$ , $R_{PROG} = 499\Omega$ , unless otherwise noted.

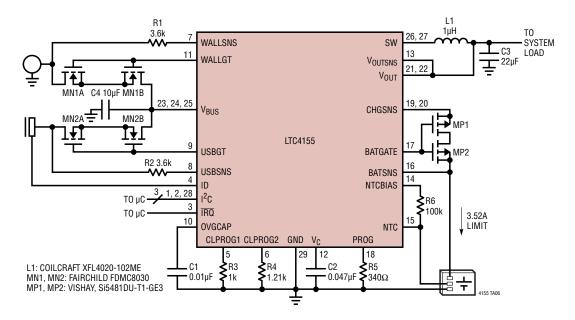

### **PIN FUNCTIONS**

**SDA (Pin 1):** Data Input/Output for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C input levels are scaled with respect to DVCC for I<sup>2</sup>C compliance.

**DVCC (Pin 2):** Logic Supply for the I<sup>2</sup>C Serial Port. DVCC sets the reference level of the SDA and SCL pins for I<sup>2</sup>C compliance. It should be connected to the same power supply used to power the I<sup>2</sup>C pull-up resistors.

**IRQ** (Pin 3): Open-Drain Interrupt Output. The IRQ pin can be used to generate an interrupt due to a variety of maskable status change events within the LTC4155.

ID (Pin 4): USB A-Device Detection Pin. When wired to a mini- or micro-USB connector, the ID pin detects when the "A" side of a mini or micro-USB cable is connected to the product. If the ID pin is pulled down, and the LOCKOUT\_ID\_PIN bit is not set in the I<sup>2</sup>C port, the switching PowerPath operates in reverse providing USB power to the V<sub>BUS</sub> pin from the battery. USB On-The-Go power can only be delivered from the USB multiplexer path.

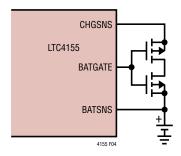

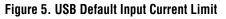

CLPROG1 (Pin 5): Primary V<sub>BUS</sub> Current Limit Programming Pin. A resistor from CLPROG1 to ground determines the upper limit of the current drawn from the V<sub>BUS</sub> pin when CLPROG1 is selected. A precise measure of V<sub>BUS</sub> current, h<sub>CLPROG1</sub><sup>-1</sup>, is sent to the CLPROG1 pin. The switching regulator increases power delivery until CLPROG1 reaches 1.2V. Therefore, the current drawn from V<sub>BUS</sub> will be limited to an amount given by the 1.2V reference voltage, h<sub>CLPROG1</sub> and R<sub>CLPROG1</sub>.

Typically CLPROG1 is used to override the USB compliant input current control pin, CLPROG2, in applications where USB compliance is not a requirement. This would be useful for applications that use a dedicated wall adapter and would rather not be limited to the 500mW start-up value required by USB specifications. If USB compliance is a requirement at start-up, CLPROG1 should be connected to CLPROG2 and a single resistor should be used. See the CLPROG2 pin description.

In USB noncompliant designs, the user is encouraged to use an R<sub>CLPROG1</sub> value that best suits their application for start-up current limit. See the Operation section for more details.

**CLPROG2 (Pin 6):** Secondary V<sub>BUS</sub> Current Limit Program Pin. CLPROG2 controls the V<sub>BUS</sub> current limit when either selected via I<sup>2</sup>C command or when CLPROG1 and CLPROG2 are shorted together. When selected, a resistor from CLPROG2 to ground determines the upper limit of the current drawn from the V<sub>BUS</sub> pin. Like CLPROG1, a precise fraction of  $V_{BUS}$  current,  $h_{CLPROG2}^{-1}$ , is sent to the CLPROG2 pin. The switching regulator increases power delivery until CLPROG2 reaches 1.2V. Therefore, the current drawn from V<sub>BUS</sub> will be limited to an amount given by the 1.2V reference voltage, h<sub>CLPROG2</sub> and R<sub>CLPROG2</sub>.

There are a multitude of ratios for  $h_{CLPBOG2}$  available by  $I^2C$ control, three of which correspond to the 100mA, 500mA and 900mA USB specifications. CLPROG2 is also used to regulate maximum input current in the USB suspend mode and maximum output current in USB On-The-Go mode.

If CLPROG1 and CLPROG2 are shorted together at the onset of available input power, the LTC4155 selects CLPROG2 in the 100mA USB mode to limit input current. This ensures USB compliance if so desired. For USB compliance in all modes, the user is encouraged to make R<sub>CLPB0G2</sub> equal to the value declared in the Electrical Characteristics.

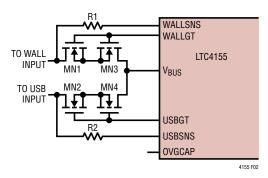

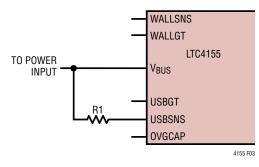

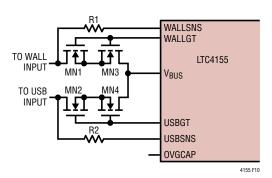

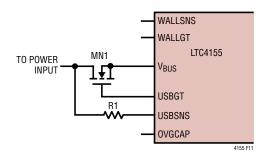

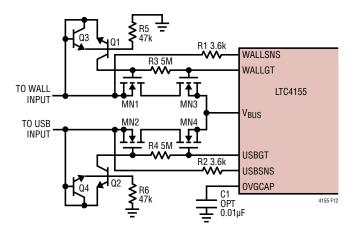

WALLSNS (Pin 7): Highest Priority Multiplexer Input and Overvoltage Protection Sense Input. WALLSNS should be connected through a 3.6k resistor to a high priority input power connector and one drain of two source-connected N-channel MOSFET pass transistors. When voltage is detected on WALLSNS, it draws a small amount of current to power a charge pump which then provides gate drive to WALLGT to energize the external transistors. If the input voltage exceeds V<sub>OVLO</sub>, WALLGT will be pulled to GND to disable the pass transistors and protect the LTC4155 from high voltage.

**USBSNS (Pin 8):** Lowest Priority Multiplexer Input and Overvoltage Protection Sense Input. USBSNS should be connected through a 3.6k resistor to a low priority input power connector and one drain of two source-connected N-channel MOSFET pass transistors. When voltage is detected on USBSNS, and no voltage is detected on WALLSNS, USBSNS draws a small amount of current to power a charge pump which then provides gate drive to

### PIN FUNCTIONS

USBGT to energize the external transistors. If the input voltage exceeds  $V_{OVLO}$ , USBGT will be pulled to GND to disable the pass transistors and protect the LTC4155 from high voltage.

Power detected on WALLSNS is prioritized over USBSNS. If power is detected on both WALLSNS and USBSNS, by default, only WALLGT will receive drive for its pass transistors. See the Operations section for further information about programmable priority.

**USBGT (Pin 9):** Overvoltage Protection and Priority Multiplexer Gate Output. Connect USBGT to the gate pins of two source-connected external N-channel MOSFET pass transistors. One drain of the transistors should be connected to  $V_{BUS}$  and the other drain should be connected to a low priority DC input connector. In the absence of an overvoltage condition, this pin is driven from an internal charge pump capable of creating sufficient overdrive to fully enhance the pass transistors. If an overvoltage condition is detected, USBGT is brought rapidly to GND to prevent damage to the LTC4155. USBGT works in conjunction with USBSNS to provide this protection. USBGT also works in conjunction with WALLSNS to determine power source prioritization. See the Operation section.

**OVGCAP (Pin 10):** Overvoltage Protection Capacitor Output. A  $0.1\mu$ F capacitor should be connected from OVGCAP to GND. OVGCAP is used to store charge so that it can be rapidly moved to WALLGT or USBGT. This feature provides faster power switchover when multiple inputs are supported by the end product.

**WALLGT (Pin 11):** Overvoltage Protection and Priority Multiplexer Gate Output. Connect WALLGT to the gate pins of two source-connected external N-channel MOSFET pass transistors. One drain of the transistors should be connected to  $V_{BUS}$  and the other drain should be connected to a high priority input connector. In the absence of an overvoltage condition, this pin is driven from an internal charge pump capable of creating sufficient gate drive to fully enhance the pass transistors. If an overvoltage condition is detected, WALLGT is brought rapidly to GND to prevent damage to the LTC4155. WALLGT works in conjunction with WALLSNS to provide this protection. WALLGT also works in conjunction with USBSNS to determine power source prioritization. See the Operation section.  $V_C$  (Pin 12): Compensation Pin. A 0.047 $\mu$ F ceramic capacitor on this pin compensates the switching regulator control loops.

$V_{OUTSNS}$  (Pin 13): Output Voltage Sense Input. Connecting  $V_{OUTSNS}$  directly to the  $V_{OUT}$  bypass capacitor ensures that  $V_{OUT}$  regulates at the correct level.

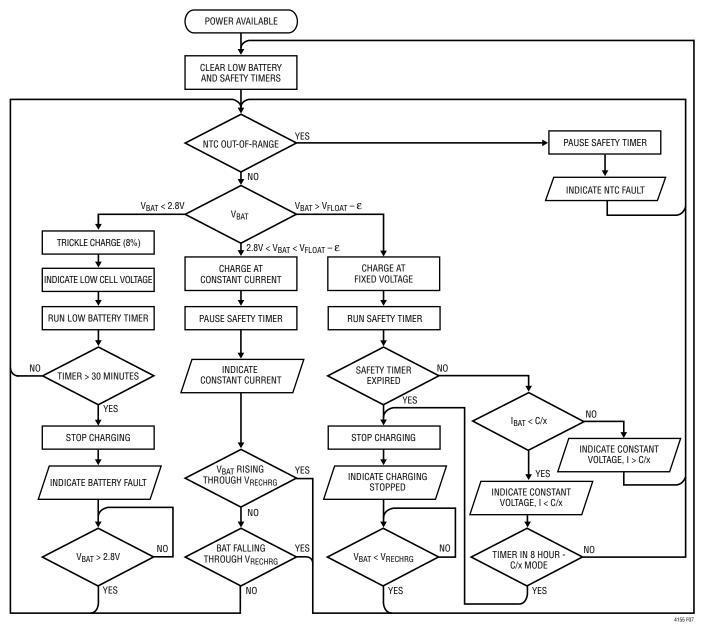

**NTCBIAS (Pin 14):** NTC Thermistor Bias Output. Connect a bias resistor between NTCBIAS and NTC, and a thermistor between NTC and GND. The value of the bias resistor should usually be equal to the nominal value of the thermistor.

**NTC (Pin 15):** Input to the Negative Temperature Coefficient Thermistor Monitoring Circuit. The NTC pin connects to a negative temperature coefficient thermistor, which is typically copackaged with the battery, to determine if the battery is too warm or too cold to charge or if the battery is dangerously hot. If the battery's temperature is out of range, charging is paused until the battery temperature reenters the valid range. A low drift bias resistor is required from NTCBIAS to NTC and a thermistor is required from NTC to ground. The thermistor's temperature reading is continually digitized by an analog to digital converter and may be read back at any time via the I<sup>2</sup>C port.

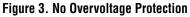

**BATSNS (Pin 16):** Battery Voltage Sense Input. For proper operation, this pin must always be connected to the battery. For fastest charging, connect BATSNS physically close to the Lithium-Ion cell's positive terminal. Depending upon available power and load, a Li-Ion battery connected to the BATSNS pin will either be charged from  $V_{OUT}$  or will deliver system power to  $V_{OUT}$  via the required external P-channel MOSFET transistor.

**BATGATE (Pin 17):** Battery Charger and Ideal Diode Amplifier Control Output. This pin controls the gate of an external P-channel MOSFET transistor used to charge the Lithium-Ion cell and to provide power to  $V_{OUT}$  when the system load exceeds available input power. The source of the P-channel MOSFET should be connected to CHGSNS and the drain should be connected to BATSNS and the battery.

4155fc