### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )<br>+IN, –IN, IOUT, IMON to V <sup>-</sup> Voltage |            |

|------------------------------------------------------------------------------------------------------------|------------|

|                                                                                                            |            |

| +IN, -IN, IOUT, IMON Current                                                                               | 10mA       |

| IOUT to IMON Voltage                                                                                       | 36V, –0.6V |

| V <sup>+</sup> , +IN to IOUT Voltage                                                                       | 36V        |

| Differential Input Voltage                                                                                 | V+         |

| R <sub>SENSE</sub> Current (Note 2)                                                                        |            |

| Continuous                                                                                                 | 3A         |

| Transient (<0.1 Second)                                                                                    | 5A         |

| Specified Temperature Range (Note 3) |                 |

|--------------------------------------|-----------------|

| LT6110I                              | 40°C to 85°C    |

| LT6110H                              | .–40°C to 125°C |

| Junction Temperature                 | 150°C           |

| Storage Temperature Range            | .–65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |                 |

| TS8                                  | 300°C           |

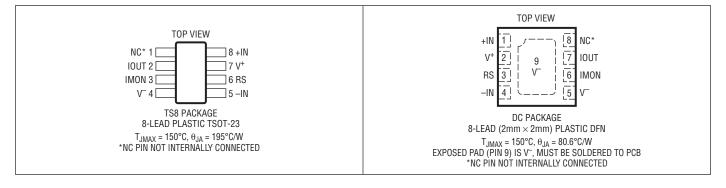

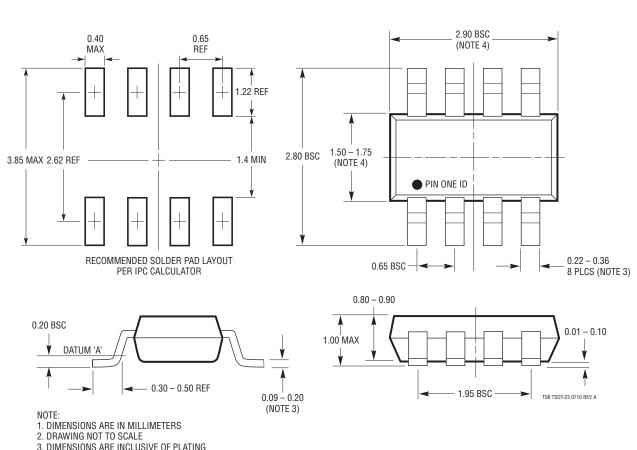

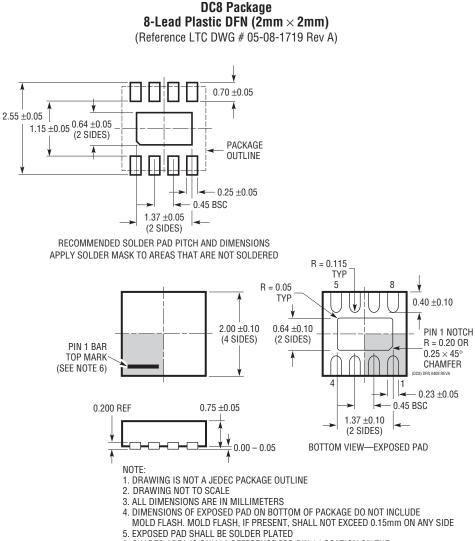

### PIN CONFIGURATION

# ORDER INFORMATION

| Lead Free Finish | Lead | Free | Finish |

|------------------|------|------|--------|

|------------------|------|------|--------|

| TAPE AND REEL (MINI) | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION            | SPECIFIED TEMPERATURE RANGE |

|----------------------|------------------|---------------|--------------------------------|-----------------------------|

| LT6110ITS8#TRMPBF    | LT6110ITS8#TRPBF | LTGCQ         | 8-Lead Plastic TSOT-23         | –40°C to 85°C               |

| LT6110HTS8#TRMPBF    | LT6110HTS8#TRPBF | LTGCQ         | 8-Lead Plastic TSOT-23         | -40°C to 125°C              |

| LT6110IDC#TRMPBF     | LT6110IDC#TRPBF  | LGCP          | 8-Lead (2mm × 2mm) Plastic DFN | –40°C to 85°C               |

| LT6110HDC#TRMPBF     | LT6110HDC#TRPBF  | LGCP          | 8-Lead (2mm × 2mm) Plastic DFN | -40°C to 125°C              |

TRM = 500 pieces. \*Temperature grades are identified by a label on the shipping container.

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. V<sup>+</sup> = 5V, V<sup>-</sup> = V<sub>IMON</sub> = 0V, I<sub>+IN</sub> = 100µA, V<sub>IOUT</sub> - V<sub>IMON</sub> = 1.2V, unless otherwise noted.

| SYMBOL                             | PARAMETER                                                      | CONDITIONS                                                                                                                                         |   | MIN      | TYP        | MAX                      | UNITS                   |

|------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------|--------------------------|-------------------------|

| V <sup>+</sup>                     | Supply Range                                                   |                                                                                                                                                    |   | 2.0      |            | 50                       | V                       |

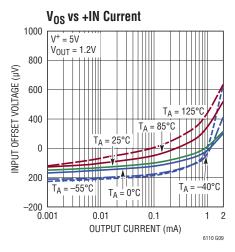

| V <sub>OS</sub>                    | Amplifier Input Offset Voltage                                 | $0^{\circ}C \le T_A \le 85^{\circ}C$ (Note 5)<br>$85^{\circ}C \le T_A \le 125^{\circ}C$ (Note 5)<br>$-40^{\circ}C \le T_A \le 0^{\circ}C$ (Note 5) | • |          | 100        | 300<br>400<br>500<br>550 | μV<br>μV<br>μV<br>μV    |

| $\Delta V_{0S} / \Delta I_{+IN}$   | Amplifier Input Offset Voltage Change with $\rm I_{+IN}$       | $ I_{+IN} = 10 \mu A \text{ to } 1mA \\ 0^{\circ}C \leq T_A \leq 85^{\circ}C \text{ (Note 6)} $                                                    | • |          | 0.15       | 0.3<br>0.5<br>1.5        | mV/mA<br>mV/mA<br>mV/mA |

| $\Delta V_{OS} / \Delta V_{IOUT}$  | Amplifier Input Offset Voltage Change with IOUT Voltage        | $V_{IOUT} = 0.4V$ to 5V                                                                                                                            | • |          | 0.005      | 0.02                     | mV/V                    |

| $\Delta V_{OS} / \Delta V_{IMON}$  | Amplifier Input Offset Voltage Change with IMON Voltage        | V <sub>IMON</sub> = 0V to 1V                                                                                                                       | • |          | 0.3        | 1                        | mV/V                    |

| $\Delta V_{0S}/\Delta T$           | Amplifier Input Offset Voltage Drift                           |                                                                                                                                                    | • |          | 1          |                          | μV/°C                   |

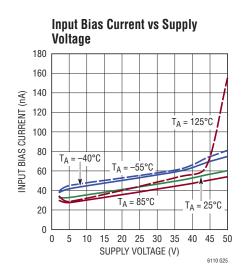

| I <sub>B</sub>                     | Amplifer Input Bias Current (–IN)                              | V <sup>+</sup> = 5V                                                                                                                                | • |          | 35         | 70<br>100                | nA<br>nA                |

| I <sub>OS</sub>                    | Amplifier Input Offset Current                                 | V <sup>+</sup> = 5V                                                                                                                                |   |          | 1          |                          | nA                      |

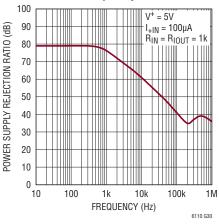

| PSRR                               | Power Supply Rejection Ratio                                   | V <sup>+</sup> = 2.0V to 36V<br>V <sup>+</sup> = 36V to 50V                                                                                        | • | 96<br>90 | 110<br>100 |                          | dB<br>dB                |

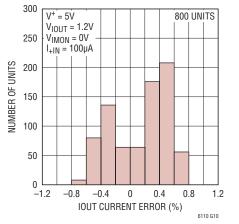

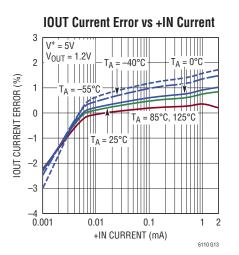

|                                    | IOUT Current Error (Note 4)<br>(Referred to I <sub>+IN</sub> ) | $ \begin{array}{l} I_{+IN} = 10 \mu A \\ 0^{\circ}C \leq T_A \leq 85^{\circ}C, \mbox{ (Note 6)} \end{array} \end{array} $                          | • |          | 0.6        | 1.6<br>2<br>2.5          | %<br>%<br>%             |

|                                    |                                                                | $ \begin{array}{l} I_{+IN} = 100 \mu A \\ 0^{\circ}C \leq T_A \leq 85^{\circ}C, \mbox{ (Note 6)} \end{array} \end{array} $                         | • |          | 0.5        | 1<br>1.5<br>2.3          | %<br>%<br>%             |

|                                    |                                                                | $ I_{+IN} = 1mA 0°C \le T_A \le 85°C, (Note 6) $                                                                                                   | • |          | 0.75       | 2.5<br>3<br>4            | %<br>%<br>%             |

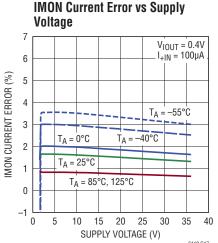

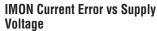

|                                    | IMON Current Error (Note 4)<br>(Referred to I <sub>+IN</sub> ) | $ \begin{array}{l} I_{+IN} = 10 \mu A \\ 0^{\circ}C \leq T_A \leq 85^{\circ}C, \mbox{ (Note 6)} \end{array} \end{array} $                          | • |          | 1.5        | 3<br>3.5<br>5            | %<br>%<br>%             |

|                                    |                                                                | $ \begin{array}{l} I_{+IN} = 100 \mu A \\ 0^{\circ}C \leq T_A \leq 85^{\circ}C, \mbox{ (Note 6)} \end{array} \end{array} $                         | • |          | 1.5        | 3<br>3.5<br>5            | %<br>%<br>%             |

|                                    |                                                                | $ I_{+IN} = 1mA  0°C \le T_A \le 85°C, (Note 6) $                                                                                                  | • |          | 1.7        | 4<br>5<br>6              | %<br>%<br>%             |

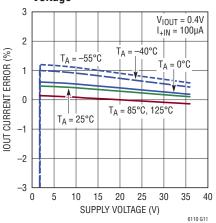

| $\Delta I_{IOUT} / V_{IOUT}$       | IOUT Current Error Change with<br>IOUT Voltage (Note 4)        | $V_{IOUT} = 0.4V$ to 3.5V<br>$V_{IOUT} = 0.4V$ to 5V                                                                                               | • |          |            | 0.2<br>0.4               | %/V<br>%/V              |

| $\Delta I_{\rm IMON}/V_{\rm IMON}$ | IMON Current Error Change with<br>IMON Voltage (Note 4)        | $V_{IMON} = 0V$ to 3.1V, $V_{IOUT} = 5V$                                                                                                           | • |          |            | 0.2                      | %/V                     |

|                                    | +IN Current Range                                              |                                                                                                                                                    | • | 0.01     |            | 1                        | mA                      |

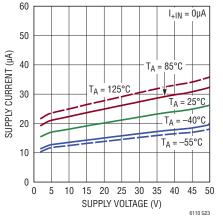

| I <sub>S</sub>                     | Supply Current                                                 | $V^{+} = 5V, I_{+1N} = 0\mu A$                                                                                                                     | • |          | 16         | 30<br>50                 | μΑ<br>μΑ                |

|                                    |                                                                | V <sup>+</sup> = 50V, I <sub>+IN</sub> = 0μA, V <sub>IOUT</sub> = 25V                                                                              | • |          | 30         | 50<br>100                | μA<br>μA                |

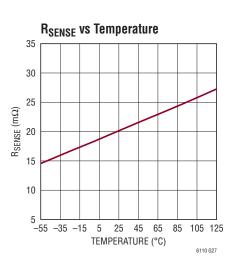

| R <sub>SENSE</sub>                 | R <sub>SENSE</sub> Resistance                                  | (Note 2)                                                                                                                                           |   | 0.0165   | 0.02       | 0.0225                   | Ω                       |

| BW                                 | Signal Bandwidth (–3dB)                                        | $I_{+IN} = 100 \mu A, R_{IOUT} = 1k$                                                                                                               |   |          | 180        |                          | kHz                     |

| t <sub>r</sub>                     | Rise Time                                                      |                                                                                                                                                    |   |          | 2          |                          | μs                      |

# **ELECTRICAL CHARACTERISTICS**

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. In addition to the Absolute Maximum Ratings, the output current and supply current must be limited to insure that the power dissipation in the LT6110 does not allow the die temperature to exceed 150°C. See the Applications Information section Power Dissipation for further information.

Note 2: R<sub>SENSE</sub> resistance and maximum R<sub>SENSE</sub> currents are guaranteed by characterization and process controls.

Note 3: The LT6110I is guaranteed to meet specified performance from -40°C to 85°C. The LT6110H is guaranteed to meet specified performance from -40°C to 125°C.

Note 4: Specified error is for the LT6110 output current mirror and does not include errors due to V<sub>OS</sub> or resistor tolerances. Since most systems will not have 100% correction, the total system error can be compensated to less than the specified error with proper design. See the Applications Information section for details.

Note 5: Measurement errors limit automatic testing accuracy. These measurements are guaranteed by design correlation, characterization and testing to wider limits.

**Note 6:** The  $0^{\circ}C \leq T_A \leq 85^{\circ}C$  temperature range is guaranteed by characterization and correlation to testing at-40°C, 25°C and 85°C.

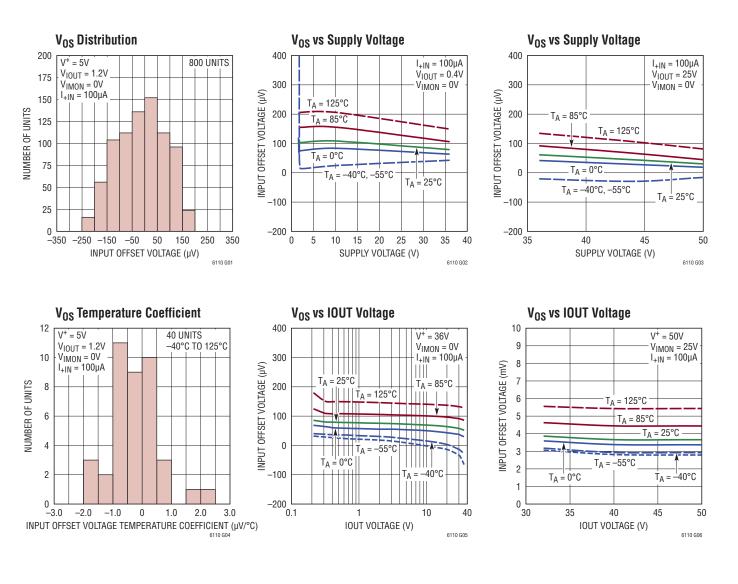

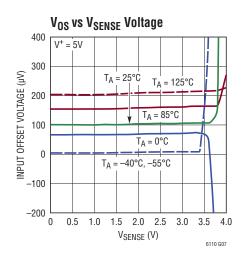

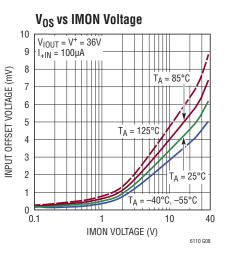

### TYPICAL PERFORMANCE CHARACTERISTICS

Downloaded from Arrow.com.

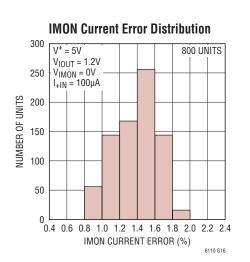

IOUT Current Error Distribution

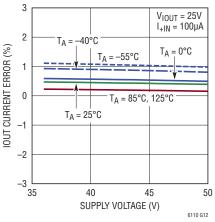

IOUT Current Error vs Supply Voltage

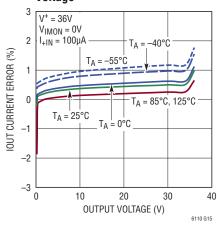

**IOUT Current Error vs Output**

Τд =

-40°C

T<sub>A</sub> = 0°C

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

OUTPUT VOLTAGE (V)

$T_A = -55^{\circ}C$

T<sub>A</sub> = 85°C, 125°C

6110 G14

Voltage

$V^{+} = 5V$

V<sub>IMON</sub> = 0V

I<sub>+IN</sub> = 100μA

$T_A = 25^{\circ}C$

3

2

1

0

-1

-2

-3

**OUT CURRENT ERROR** (%)

IOUT Current Error vs Supply Voltage

IOUT Current Error vs Output Voltage

5

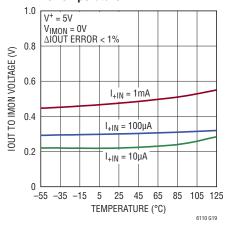

Minimum IOUT to IMON Voltage vs Temperature

IMON Current Error vs +IN Current 5  $V^{+} = 5V$  $V_{0UT} = 1.2V$ 4 -55°C TIII -|+|+ IMON CURRENT ERROR (%) 3 -40°C  $T_A =$ = 0°C 2 1 T<sub>A</sub> = 125°C 0 = 25°C ΤA T<sub>A</sub> = 85°C -1 -2 \_3 └─ 0.001 0.01 0.1 2 1 +IN CURRENT (mA) 6110 G22

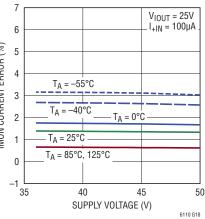

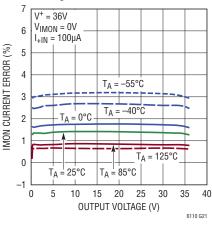

**IMON Current Error vs Output**

Voltage

7

6

5

MON CURRENT ERROR (%)

IMON CURRENT ERROR (%) 1 6110 G17

$V^+ = 5V$

$I_{+IN} = 100 \mu A$

**IMON Current Error vs Output** Voltage

4 T<sub>A</sub> = -55°C 3 -40°C T<sub>A</sub> =  $T_A = 0^{\circ}C$ 2 Å 1 T<sub>A</sub> = 125°C 0 T<sub>A</sub> = 85°C T<sub>A</sub> = 25°C -1 0  $0.5 \ 1.0 \ 1.5 \ 2.0 \ 2.5 \ 3.0 \ 3.5 \ 4.0 \ 4.5 \ 5.0$ OUTPUT VOLTAGE (V) 6110 G20

Supply Current vs Supply Voltage

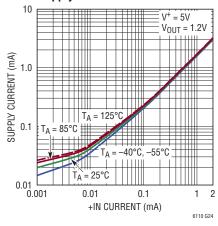

Supply Current vs +IN Current

**Frequency Response**

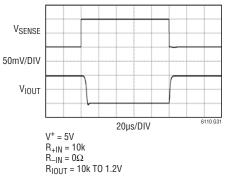

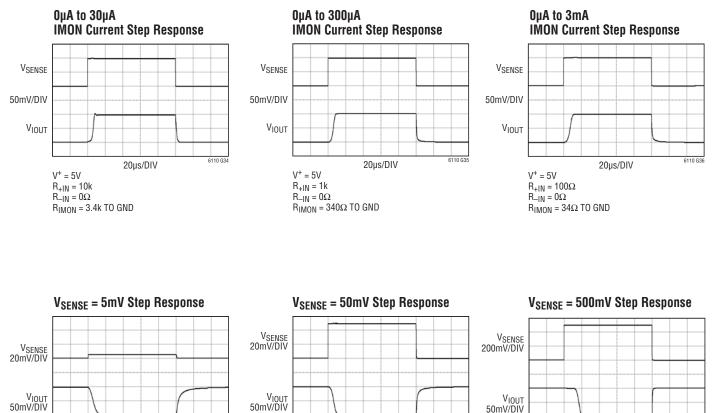

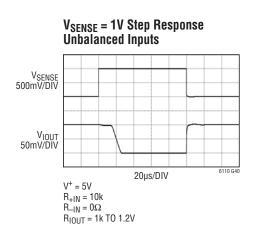

0µA to 100µA **IOUT Current Step Response**

#### OµA to 1mA **IOUT Current Step Response**

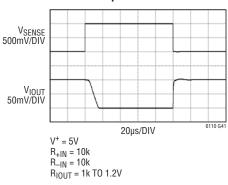

#### V<sub>SENSE</sub> = 1V Step Response Balanced Inputs

### PIN FUNCTIONS (TSOT-23/DFN)

NC (Pin 1/Pin 8): Not Internally Connected.

**IOUT (Pin 2/Pin 7):** Sinking Current Output. IOUT will sink a current that is equal to  $V_{SENSE}/R_{IN.}$   $V_{SENSE}$  is the voltage developed across the sense resisor.

**IMON (Pin 3/Pin 6):** Sourcing Current Output. IMON will source a current that is equal to  $3 \cdot V_{SENSE}/R_{IN}$ .

V<sup>-</sup> (Pin 4/Pin 5): Negative Power Supply. Normally connected to ground.

**–IN (Pin 5/Pin 4):** Negative Input to the Internal Sense Amplifier. Must be tied to system load side of the sense resistor, either directly or through a resistor.

**RS (Pin 6/Pin 3):** Internal Sense Resistor. Connect to the load to use. Leave open when using an external sense resistor.

**V<sup>+</sup> (Pin 7/Pin 2):** Positive Power Supply. Connect to the more positive side of the sense resistor. A minimum capacitance of  $0.1\mu$ F is required from V<sup>+</sup> to V<sup>-</sup>.

**+IN (Pin 8/Pin 1):** Positive Input to the Internal Sense Amplifier. The internal sense amplifier will drive +IN to the same potential as -IN. A resistor,  $R_{+IN}$ , tied from V<sup>+</sup> to +IN sets the IOUT and IMON output currents as defined in the the IOUT and IMON pin functions description.

**Exposed Pad (Pin 9, DFN Only):** V<sup>-</sup>. Must be soldered to the PCB.

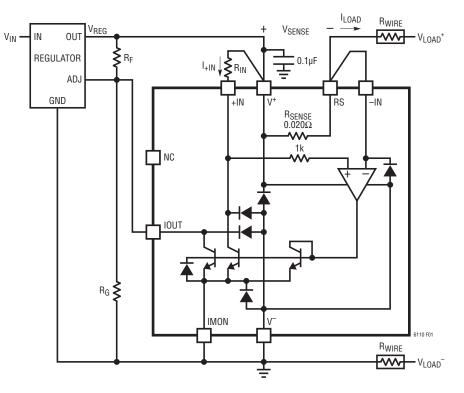

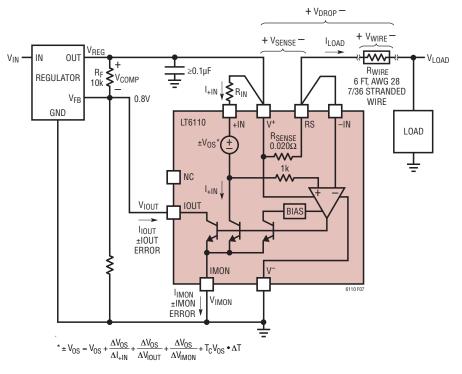

### **BLOCK DIAGRAM**

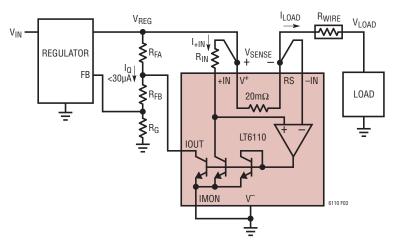

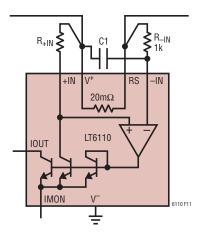

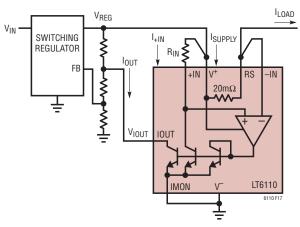

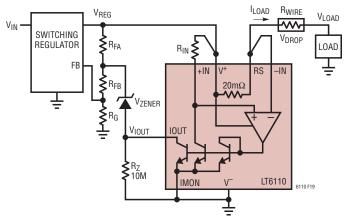

Figure 1. Block Diagram and Typical Connection

### INTRODUCTION

The LT6110 provides a simple and effective solution to a common problem in power distribution. When a load draws current through a long or thin wire, wire resistance causes an IR drop that reduces the voltage delivered to the load. A regulator IC cannot detect this drop without a Kelvin sense at the load, which requires a multi-conductor wire that is not supported in some applications.

The LT6110 detects the load current and sets a proportional current at an output that can be used to control the output voltage of an adjustable regulator to compensate for the drop in the wire.

The accuracy and wide output current range of the LT6110 allow it to compensate for either small or large voltage drops to a high degree of precision. The LT6110 can sense the load current with its internal sense resistor or an external sense resistor can be used to improve accuracy and handle currents greater than 3A. Resistor-programmable gain gives substantial flexibility to the compensation circuit. A signal bandwidth of 180kHz enables fast response time to load changes and provides good loop characteristics so that the power supply circuit remains stable.

The LT6110 requires that the resistance of the wire be known. However, that resistance does not have to be very accurate for the LT6110 to provide good compensation since the regulation at the load is the product of the error due to the wire resistance and the error in the LT6110 compensation circuit.

For example, a 5V regulator circuit has 10% regulation at the load due to a wire resistance drop of 0.5V. Even if the wire resistance doubled, causing an error in the LT6110 compensation circuit of 50%, the regulation at the load is still reduced to  $10\% \cdot 50\% = 5\%$ .

For systems that are better controlled, the load regulation can be improved to far exceed that possible without the LT6110. As an example, for a known wire resistance, and with an external 1% sense resistor, the same 10% load regulation in the previous example can be reduced to less than 0.5%. The LT6110 has two output pins, IOUT and IMON. Either pin may be used to provide a current that is proportional to the load current. The IOUT pin provides a sinking current to compensate regulators with a ground referred voltagereference, such as the LT3980. The IMON pin provides a sourcing current to compensate regulators with an output referred reference like the LT1083 and current-referenced regulators like the LT3080. As an added feature, the output current from either pin can be converted to a voltage via a simple resistor, creating a voltage that is also proportional to load current. This voltage may be used to measure or monitor the load current. Either or both pins may be used for regulator control, and either or both pins may be used for monitoring, allowing substantial flexibility in system design.

#### **THEORY OF OPERATION**

The outputs of the LT6110 are proportional to a sense voltage,  $V_{SENSE}$ , developed across an internal or external sense resistor,  $R_{SENSE}$  (see Figure 1).

A sense amplifier loop forces +IN to the same voltage as -IN. Connecting an external resistor,  $R_{IN}$ , between V<sup>+</sup> and +IN forces a voltage across  $R_{IN}$  equal to  $V_{SENSE}$ , creating a current into +IN,  $I_{+IN}$ , equal to  $V_{SENSE}/R_{IN}$ . This current is precisely mirrored to IOUT. The emitter currents of the three transistors in the mirror are combined to form the IMON output current. Ideally, the IOUT sink current is equal to  $I_{+IN}$  and the IMON source current is equal to three times  $I_{+IN}$ .

### $V^+$ and $V^-$

The LT6110 is designed to operate with a supply voltage  $(V^+ \text{ to } V^-)$  up to 50V. However, when using a supply voltage greater than 36V, additional care must be taken not to exceed the absolute maximum ratings. The V<sup>+</sup> to IOUT voltage must be kept less than 36V to avoid the breakdown of internal transistors.

The V<sup>+</sup> pin needs to be bypassed with at least a  $0.1 \mu F$  capacitor placed close to the pin.

#### +IN and -IN

The +IN and –IN inputs can have a maximum differential voltage equal to the supply voltage. This protects the LT6110 if the –IN pin (the remote load side) is accidentally shorted to ground. In this case, the IOUT current must be limited to less than 2mA (see the Limiting the Regulator Boost Voltage section).

The +IN to IOUT voltage must be kept below 36V to avoid the breakdown of internal transistors.

#### IOUT and IMON

The IOUT to IMON outputs can have a maximum differential voltage of 36V for IOUT above IMON and -0.6V for IOUT below IMON. A 36V Zener diode can be connected from IOUT to IMON to prevent damage to the output NPN transistor in the event of a fault condition. In this case, a low leakage Zener diode should be used to reduce error in the IOUT current.

### **RS (Internal R<sub>SENSE</sub>)**

The internal sense resistor can reliably carry a continuous current up to 3A and transient currents of 5A for up to 0.1 seconds. For currents greater than this, an external sense resistor should be used. The internal sense resistor has a temperature coefficient similar to copper.

#### **DESIGN PROCEDURE**

The design of an LT6110 compensation circuit is a simple 3-step process. To start, the following parameters must be known:

R<sub>WIRE</sub>, total wire resistance to the load

R<sub>SENSE</sub>, resistor used to sense the load current

R<sub>F</sub>, feedback resistor of the regulator

ILOADMAX, maximum load current

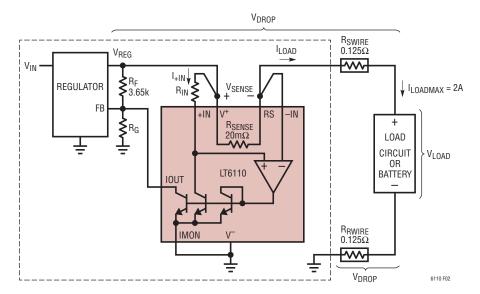

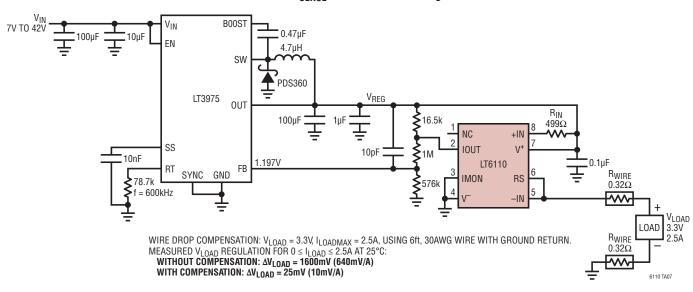

The circuit in Figure 2 shows an adjustable voltage regulator with an LT6110 compensation circuit. The regulator has an internal ground referred voltage reference to set its output voltage. There are two wires to the load, one source ( $R_{SWIRE}$ ) and one return ( $R_{RWIRE}$ ). Since it is the most common configuration it will be used for the following design example. Current referenced regulators and regulators with an output referred reference are covered in later sections.

**Step 1:** Determine the drop in voltage at the load due to the wire resistance and sense resistor at the maximum load current.

$V_{DROP} = (R_{SWIRE} + R_{RWIRE} + R_{SENSE}) \bullet I_{LOADMAX}$  $V_{DROP} = (0.125\Omega + 0.125\Omega + 0.02\Omega) \bullet 2A = 0.54V$

**Step 2:** Determine the resistor on the +IN pin,  $R_{IN}$ , required to cancel  $V_{DROP}$ .

The regulator output voltage will increase as current is pulled from the IOUT pin through the feedback resistor,  $R_F$ , creating a compensation voltage.

$V_{COMP} = I_{IOUT} \bullet R_F$

To cancel the voltage drop at the load, set  $V_{\text{COMP}}$  equal to  $V_{\text{DROP}}.$

$V_{COMP} = I_{IOUT} \bullet R_F = V_{DROP}$

Since the IOUT current is equal to the current going into the +IN pin and the current in the +IN pin is equal to the sense voltage divided by  $R_{IN}$ ,  $R_{IN}$  can be determined by the following equations:

$$I_{\rm IOUT} = I_{\rm +IN} = \frac{V_{\rm SENSE}}{R_{\rm IN}}$$

where  $V_{SENSE} = I_{LOADMAX} \bullet R_{SENSE}$

Combining the above equations,

$$R_{IN} = (I_{LOADMAX} \bullet R_{SENSE}) \bullet \frac{R_F}{V_{DROP}}$$

$$R_{\rm IN} = (2A \bullet 0.02\Omega) \bullet \frac{3.65k}{0.54V} = 270\Omega$$

**Step 3:** The final step is to consider the errors in the compensation circuit to determine if the resulting voltage error at the load meets the desired performance.

For example, the internal  $R_{SENSE}$  of the LT6110 has a typical tolerance of ±7.5%. If the other errors in the compensation circuit such as  $V_{OS}$ , IOUT current error and the resistor tolerances of  $R_F$  and  $R_{IN}$  add an additional ±2.5% error, then the total error in the compensation circuit would be ±10% resulting in a voltage error at the load of the following:

$V_{LOADERROR} = V_{COMP} \bullet Compensation Error$

$V_{LOADERROR} = 0.54V \bullet (\pm 10\%) = \pm 0.054V$

A 10× improvement.

If this is not adequate for the given application, steps can be taken to reduce the sources of error, such as using an external sense resistor with a tighter tolerance. See the section on External Current Sense Resistors for more information.

In most cases, the internal sense resistor, wire resistance tolerances and temperature mismatch of the  $R_{SENSE}$  and  $R_{WIRE}$  resistances will contribute the largest portion of the overall compensation circuit error. See the sections on Error Sources, Copper Wire Information and Temperature Errors for a comprehensive discussion.

### ADDITIONAL DESIGN CONSIDERATIONS

### **IOUT Current**

The recommended range of IOUT current is  $30\mu A \le I_{IOUT} \le 300\mu A$  for the best precision. For performance outside of this range, see the Typical Performance Curves to determine typical errors.

If the IOUT current is less than  $30\mu A$ , the feedback resistor may need to be adjusted to reduce the error in the compensation circuit.

In the previous example,

$$I_{IOUT} = \frac{V_{SENSE}}{R_{IN}} = \frac{0.04}{270} = 148 \mu A$$

Since this is within the recommended range no further adjustment is needed.

See the section on Compensating a Low Quiescent Current Design for IOUT current less than  $30\mu A$ .

### Load Regulation

Load regulation is often specified as an error in output voltage at a given load current, as in the previous example, but it is also specified as a percentage of the regulator output voltage. If the output voltage of the regulator circuit in Figure 2 is 5V, the resulting compensated load regulation, in percent, would be the following:

LoadReg<sub>COMP</sub> (%) =

$$\frac{V_{LOADERROR}}{V_{REG}} \bullet 100$$

LoadReg<sub>COMP</sub> (%) =  $\frac{\pm 0.054V}{5V} \bullet 100 = \pm 1.1\%$

Without the compensation circuit (no  $\mathsf{R}_{\text{SENSE}}$ ) the load regulation in percent would be,

LoadReg<sub>UNCOMP</sub> (%) =

$$\frac{-0.5V}{5V} \cdot 100 = -10\%$$

The regulator's output will also change due to its own load regulation effects (per the regulator's specification). In general, this change in voltage is small compared to the wire-drop, and can be ignored. If it is considered to be a significant source of error, it can be included as part of the wire-drop compensation. To include the regulator's load regulation effect, simply add the voltage drop due to the regulator's load regulation at I<sub>LOADMAX</sub> to V<sub>DROP</sub>, when calculating the compensation circuit parameters.

#### PCB Trace Resistance

Printed circuit trace resistance between the output of the regulator and the load will cause additional voltage drops. As with the regulator's load regulation effects, these drops can be compensated for by adding them to  $V_{DROP}$  when calculating the compensation circuit parameters. This also allows the use of narrower traces to deliver power to the load and still retain good load regulation. See the PCB Copper Resistor section for more information on how to determine trace resistance.

#### Kelvin Sense Connection to R<sub>SENSE</sub>

To reduce  $R_{SENSE}$  error due to trace resistance, the –IN pin and  $R_{IN}$  resistor should be connected as close to  $R_{SENSE}$  as possible, as reflected in Figure 2.

#### **Compensating a Low Quiescent Current Design**

Switching regulator circuits are used for high power efficiency. Many are required to maintain high efficiency at light or no load conditions. In these cases the quiescent operating current is minimized by using larger valued resistors to program the output voltage so very little current is wasted in the feedback network.

A large value for resistor  $R_F$  could require too low of a compensating current (<30µA) from IOUT of the LT6110. In this situation the feedback resistor,  $R_F$ , can be split into two resistor values. A small value resistor to conduct  $I_{IOUT}$  from the LT6110 and compensate the output voltage when the load current is high, and a second, larger valued resistor, to keep the no-load quiescent current drain low. With this arrangement, as shown in Figure 3,  $I_{IOUT}$  can be designed for 100µA to preserve  $V_{DROP}$  compensation accuracy. At no load the quiescent current drawn through the feedback resistors,  $I_Q$ , can be kept very low.

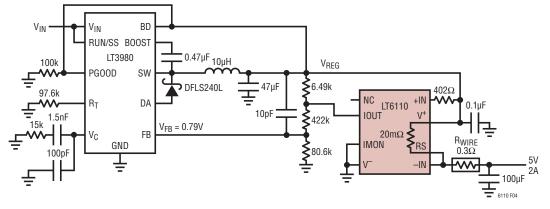

Figure 3. Low Quiescent Current Wire Compensation Using Three Regulator Resistors

In Figure 3  $R_F$  is split into  $R_{FA}$  and  $R_{FB}$ .  $V_{REG}$  is the no-load quiescent output voltage of the regulator. The design of these two feedback resistors follows:

$$R_{FA} = \frac{V_{DROP}}{I_{IOUT}}$$

$I_{IOUT}$  can be sized to be 100 $\mu A$  at full load current and only this resistor creates the  $V_{DROP}$  compensation voltage.

$$\mathsf{R}_{\mathsf{FB}} = \frac{\mathsf{V}_{\mathsf{REG}} - \mathsf{V}_{\mathsf{FB}}}{\mathsf{I}_{\mathsf{Q}}} - \mathsf{R}_{\mathsf{FA}}$$

$\mathsf{I}_{\mathsf{Q}}$  is the no-load quiescent current flowing through the resistor string.

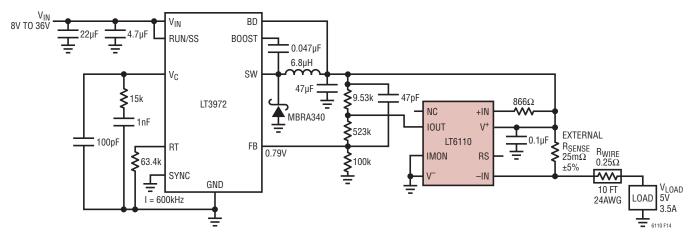

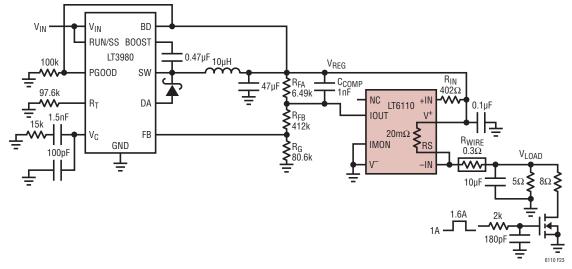

Figure 4 is a circuit using the LT6110 and a three resistor voltage setting technique to compensate the voltage loss due to a 2A load connected through 6 feet of stranded copper wire ( $300m\Omega$  of wire resistance). The LT3980 is a 2A buck switching regulator programmed for 5V out with only 10µA of current, I<sub>Q</sub>, through the feedback resistor string when there is no load current. At the full 2A load the LT6110 uses the internal  $20m\Omega$  sense resistor to produce 100µA at IOUT to compensate for the 640mV drop.

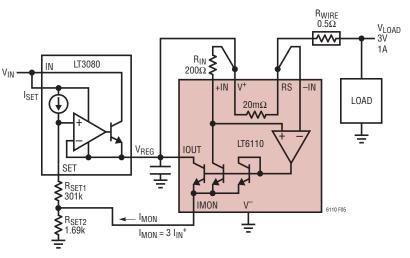

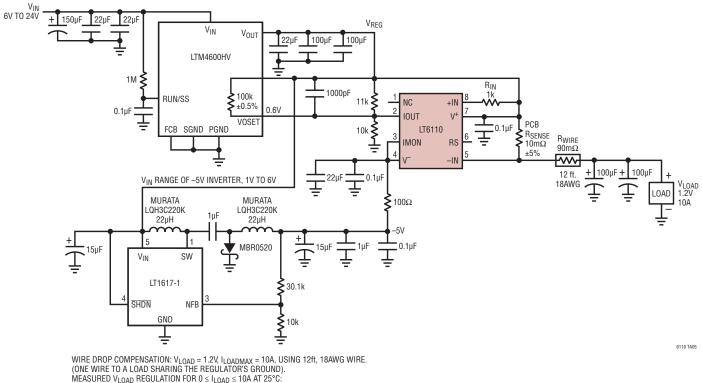

#### Compensating a Current Referenced Regulator Power Source

Figure 5 shows a cable drop compensation circuit using a current referenced regulator, the LT3080. A precision  $10\mu$ A set current, I<sub>SET</sub>, is sourced through two series connected resistors to program the output voltage for the remote load. To compensate for the load connecting cable drop requires sourcing an additional current into this resistor pair to increase the output voltage. The LT6110 provides a sourced current at the IMON pin which is directly proportional to the current flowing to the load. This current is three times the normal IOUT current. The following equations are used to design this circuit:

$$V_{REG} = I_{SET} \bullet (R_{SET1} + R_{SET2})$$

$$V_{SENSE} = I_{LOAD} \bullet R_{SENSE}$$

$$I_{+IN} = \frac{V_{SENSE}}{R_{IN}}$$

Figure 4. LT3980 Buck Regulator with LT6110 Cable Drop Compensation Circuit

Figure 5. Wire Loss Compensation Using a Current Referenced LDO

To compensate for V<sub>DROP</sub> at I<sub>LOAD(MAX)</sub> set:

$$R_{SET2} = \frac{V_{DROP}}{I_{IMON}}$$

and

$$R_{SET1} = \frac{V_{REG}}{I_{SET}} - R_{SET2}$$

As an example, to compensate this 3V regulator for a 500mV cable drop with a 1A load current set  $I_{+IN}$  for 100 $\mu A$  for best accuracy. Then:

$R_{SET1}$  = 301k and  $R_{SET2}$  = 1.69k using nearest 1% tolerance standard resistor values.

$$R_{\rm IN} = \frac{1A \bullet 20m\Omega}{100\mu A} = 200\Omega$$

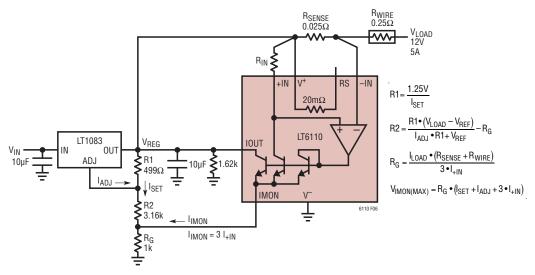

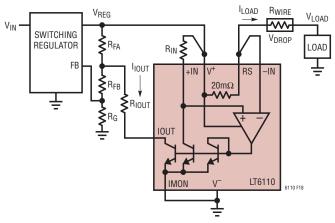

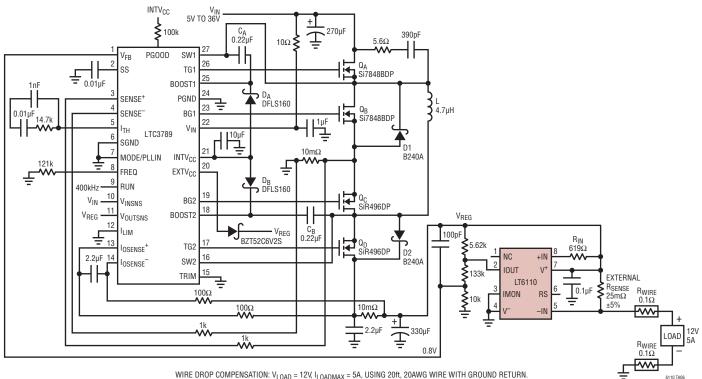

#### Compensating an Output Referred Adjustable Voltage Regulator

Many adjustable voltage regulators are biased from a floating voltage reference that sets a voltage between the output pin and an adjust pin. Three terminal fixed voltage regulators can also be made adjustable by biasing up the ground terminal. A feedback resistor string is used to program the output voltage. The amount of current through these resistors is scaled to a level to minimize error caused by any bias current at the adjust pin. As shown in Figure 6, an LT6110 can add cable drop compensation by using the current sourced from the IMON pin. To preserve accuracy the voltage at IMON should be kept within 5V of V<sup>-</sup>, or ground in this example. By using two resistors for the bottom resistor in the voltage regulator programming string, the cable drop compensation voltage can be added to a voltage near ground appearing at the IMON pin.

The following equations are used to design this circuit using an LT1083, 7A adjustable voltage regulator:

$V_{REF}$  = 1.25V between OUT and ADJ pins,  $I_{ADJ}$  = 75  $\mu A$  typ

$$I_{SET} = \frac{V_{REF}}{R1} \gg I_{ADJ}$$

$$V_{LOAD} (I_{LOAD} = 0) = (I_{SET} + I_{ADJ}) \bullet (R2 + R_G) + V_{REF}$$

$$V_{SENSE} = I_{LOAD} \bullet R_{SENSE}$$

$$I_{+IN} = \frac{V_{SENSE}}{R_{IN}}$$

$$I_{IMON} = 3 \bullet I_{+IN}$$

As an example, Figure 6 is a 12V regulator for a 5A remotely connected load with a wire resistance of  $250m\Omega$ . For the higher load current an external  $25m\Omega$  sense resistor is used. The cable drop voltage for such a high current application is significant:

$V_{DROP} = I_{LOAD(MAX)} \bullet (R_{SENSE} + R_{WIRE}) = 5A \bullet 275m\Omega$ = 1.375V

Figure 6. Wire Compensation Using a High Current Adjustable Regulator

To program the regulator output voltage and compensate for  $V_{DROP}$  at  $I_{LOAD(MAX)}$  the following procedure can be used:

Make  $I_{SET} >> I_{ADJ}$ , if  $I_{SET} = 33.3 \bullet I_{ADJ}$  then  $I_{SET} = 2.5$  mA

$$R1 = \frac{V_{REF}}{I_{SET}} = \frac{1.25V}{2.5mA} = 499\Omega$$

For 12V output with no-load current:

$$(R2 + R_G) = \frac{V_{LOAD} - V_{REF}}{I_{SET} + I_{ADJ}} = \frac{10.75V}{2.575mA} = 4.175k$$

Resistor  $R_G$  is used to develop the maximum load current compensation voltage. A smaller value for  $R_G$  minimizes the voltage programming error at no load but requires more current from the LT6110 IMON pin to compensate for cable drop loss. The IMON pin current is most accurate over a range from 30µA to 3mA.

$$R_{G} = \frac{V_{DROP}}{I_{IMON}}$$

For 1.375V of compensation, using a convenient value 1k resistor for  $R_G$  will require 1.375mA from the IMON pin which is near the mid range of accurate current levels.

With this selection for R<sub>G</sub> then:

R2 = 4.175k – 1k = 3.175k

use a 3.16k standard 1% tolerance value to set the no-load output voltage to 12V.

To program the LT6110 compensation current requires a selection for  $\ensuremath{\mathsf{R}_{\mathsf{IN}}}$ :

$$\mathsf{R}_{\mathsf{IN}} = \frac{\mathsf{V}_{\mathsf{SENSE}}}{\mathsf{I}_{\mathsf{+IN}}} = \frac{\mathsf{V}_{\mathsf{SENSE}}}{\frac{\mathsf{I}_{\mathsf{IMON}}}{3}}$$

$$V_{SENSE} = 5A \bullet 25m\Omega = 125mV$$

and

$$\frac{I_{\rm IMON}}{3} = \frac{1.375 \text{mA}}{3} = 460 \mu \text{A so}$$

$$R_{\rm IN} = \frac{125 \text{mV}}{460 \mu \text{A}} = 271 \Omega$$

use a 274  $\Omega$  standard value.

The IOUT pin can be connected to the 12V regulator output. The LT1083 requires a minimum output load current of 10mA so an additional 1.62k resistor (not required if  $I_{LOAD}$  is always greater than 10mA) is added to the output.

The voltage that appears at the IMON pin can impact the accuracy of the compensation circuit and should be noted. In this example the voltage will be a maximum at full load current and voltage compensation. This voltage is:

$V_{IMON(MAX)} = (I_{SET} + I_{ADJ} + I_{IMON}) \bullet R_G = (2.5mA + 75\mu A + 1.375mA) \bullet 1k = 3.95V.$

### ERROR SOURCES

The LT6110 output current allows for reliable compensation for small or large connection wiring voltage drops. The voltage regulation at the remote load can be improved dramatically using the LT6110. With properly designed cable drop compensation the load voltage variation will be reduced to only the error in the compensation voltage created. This error voltage is a combination of several circuit characteristics.

The first step in determining the error is to determine the amount of compensation voltage required. Figure 7 is an example circuit that indicates the various error terms to be considered. For this example a 5V regulator will provide 2A maximum to a remote load connected through 6 feet (~2 meters) of 28AWG (7/36) stranded hook-up wire. Using 28AWG provides the thinnest, low cost wire suitable for this application. Using wire resistance Table 4, the DC resistance of 6 ft of 28AWG (7/36) can be determined:  $R_{WIRE} = 6ft \cdot 63.3m\Omega/ft = 380m\Omega$ . At 2A full load current

this will create a  $V_{DROP}$  of 760mV. Without the LT6110 compensator the regulation of the 5V supply at the load would be 15%.

This example design will use the internal  $20m\Omega$  sense resistor of the LT6110 and will assume that the feedback resistor network in the voltage regulator cannot be modified or optimized for compensation. The R<sub>F</sub> used to develop the compensation voltage is fixed at 10k and the reference voltage at the feedback node where the compensator connects is 0.8V. From these parameters the basic compensation circuit can be easily designed:

$V_{SENSE}$  at full load is  $20m\Omega$  • 2A or 40mV

The compensation voltage, V<sub>COMP</sub>, required is:

V<sub>WIRE</sub> + V<sub>SENSE</sub>, 760mV + 40mV, or 800mV

To create this compensation voltage will require a current through feedback resistor R<sub>F</sub> of V<sub>COMP</sub>/R<sub>F</sub>, 800mV/10k for an I<sub>IOUT</sub> of 80 $\mu$ A. This is well within the most accurate range of current (30 $\mu$ Ato 300 $\mu$ A) flowing into the IOUT pin.

Figure 7. Cable Drop Compensation Error Sources

To create this current at full load requires an  $R_{IN}$  value of  $V_{SENSE}/I_{IOUT}$ ,  $40mV/80\mu$ A, or  $500\Omega$ . Using the nearest standard 1% tolerance value of  $499\Omega$  will be sufficient. Without considering any error terms other than this slight change in value for  $R_{IN}$  results in nearly perfect cable drop compensation. The theoretical load regulation would be improved from 15% to less than 0.01%.

The single largest source of compensation error comes from any change in the connecting wire resistance from the design assumptions. This could be caused by temperature, aging and possibly corrosion. In the compensator circuit, component tolerances and errors terms will combine to deviate from the near perfect designed amount of compensation. Figure 7 shows this simple example design and indicates the various error sources within the LT6110. All of the error terms can be determined from the Electrical Characteristics Table. The error terms for any compensator design include:

- R<sub>SENSE</sub> tolerance

- R<sub>IN</sub> tolerance

- R<sub>F</sub> tolerance

- $V_{\text{OS}},$  the offset voltage in  $\mu V$  of the internal current sense amplifier

- $\Delta V_{OS} / \Delta I_{+IN}$  is an error term caused by the finite gain of the current sense amplifier.

This is the change in the offset voltage as the sense voltage and resulting input current varies from 0 to the maximum value. It is a factor specified in mV/mA which is ohms and is accounted for as a small resistance in series with  $R_{IN}$ . The voltage across this small resistance is included in the total offset voltage term. The change in  $I_{+IN}$  current is relative to 100µA where the LT6110 is trimmed for accuracy.

- $\Delta V_{OS}/\Delta V_{IOUT}$  is a change in the offset voltage caused by a change in the voltage applied to the IOUT pin specified in mV/V. The change in V<sub>IOUT</sub> is relative to 1.2V DC where the LT6110 is trimmed for accuracy.

- $\Delta V_{OS} / \Delta V_{IMON}$  is a change in the offset voltage caused by a change in the voltage applied to the IMON pin specified in mV/V.

- IOUT current error is the accuracy of the internal current mirror. This is a percent deviation from I<sub>+IN</sub>.

- IMON current error is the accuracy of the total internal mirror current sourced to the IMON output. This is a percent deviation from 3 • I<sub>+IN</sub>.

- Temperature Related Errors (see Temperature Errors section)

Table 1 is an example of the stack-up of all error terms in the design of Figure 7. This table uses typical variances to be seen at 25°C. It is not a rigorous worst case analysis over all possible operating conditions, but instead serves to illustrate what to expect for load regulation improvement under nominal conditions.

In this example, including all typical error terms, the LT6110 still provides a factor of 10 improvement in voltage regulation at the remote load. To obtain the same level of load voltage stability without using the LT6110 would require reducing the amount of cable drop loss. The easiest way to do so would be to increase the wire gauge used to connect to the load. For a 76mV change in load voltage at 2A full load current would require a wire resistance of only  $38m\Omega$  and a 6 foot length 18AWG gauge wire is required. A larger wire gauge can be significantly more costly and is less flexible in routing to the load. These are two significant design compromises to be considered.

#### Table 1. Compensation Error Using Typical Variances Expected at 25°C.

| FIGURE 7 DESI<br>I <sub>+IN</sub> = 74.6µA | GN EXAMPLE. TOTAL         | V <sub>DROP</sub> TC   | ) COMPENSATE = 744mV,                                                                         | FOR MAXIMUM                                   | VCOMP  | FOR MINIMUM   | V <sub>COMP</sub> |

|--------------------------------------------|---------------------------|------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|--------|---------------|-------------------|

| TERM                                       | DESIGN VALUE/SPEC         | UNITS                  | COMMENT/CALCULATION                                                                           | TYPICAL ERROR                                 | VALUE  | TYPICAL ERROR | VALUE             |

| R <sub>SENSE</sub>                         | 20                        | mΩ                     | Internal Sense Resistor                                                                       | 7.50%                                         | 21.5   | -7.50%        | 18.5              |

| R <sub>IN</sub>                            | 499                       | Ω                      |                                                                                               | -0.5%                                         | 496.5  | 0.5%          | 501.5             |

| V <sub>0S</sub>                            | 0                         | μV                     |                                                                                               | -100                                          | -100   | 100           | 100               |

| $\Delta V_{OS} / \Delta I_{+IN}$           | 0                         | mV/mA                  | Relative to $I_{+IN} = 100\mu A$                                                              | -0.15                                         | -0.15  | 0.15          | 0.15              |

| $\Delta V_{OS} / \Delta V_{IOUT}$          | 0                         | mV/V                   | Relative to V <sub>IOUT</sub> = 1.2V                                                          | -0.005                                        | -0.005 | 0.005         | 0.005             |

| $\Delta V_{OS} / \Delta V_{IMON}$          | 0                         | mV/V                   | Relative to V <sub>IMON</sub> = 0V                                                            | -0.3                                          | -0.3   | 0.3           | 0.3               |

| Total V <sub>OS</sub>                      | $V_{0S} + \Delta V_{0S}/$ | ΔI <sub>+IN</sub> (100 | $\mu$ A - 80 $\mu$ A) + $\Delta$ V <sub>OS</sub> / $\Delta$ V <sub>IOUT</sub> (1.2V - 0.8V) + | $\Delta V_{OS} / \Delta V_{IMON} \bullet 0 V$ |        |               |                   |

|                                            |                           | μV                     |                                                                                               |                                               | -105   |               | 105               |

| I <sub>IOUT</sub> Error                    | 0                         | %                      | % IOUT Current Error Relative to I <sub>+IN</sub>                                             | 0.5                                           | 0.5    | -0.5          | -0.5              |

| IIMON Error                                | 0                         | %                      | % IMON Current Error Relative to $3 \bullet I_{+IN}$                                          | 1.5                                           | 1.5    | -1.5          | -1.5              |

| Summary of Terr                            | ns                        |                        |                                                                                               |                                               |        |               |                   |

| V <sub>SENSE</sub>                         | 40                        | mV                     | I <sub>LOAD(MAX)</sub> • R <sub>SENSE</sub>                                                   |                                               | 43     |               | 37                |

| I <sub>+IN</sub>                           | 80.2                      | μA                     | (V <sub>SENSE</sub> – Total V <sub>OS</sub> )/R <sub>IN</sub>                                 |                                               | 86.8   |               | 73.6              |

| I <sub>IOUT</sub>                          | 80.2                      | μA                     | $I_{+IN} \bullet (1 + I_{IOUT} Error)$                                                        |                                               | 87.2   |               | 73.2              |

| IIMON                                      | 240.6                     | μA                     | 3 • I <sub>+IN</sub> • (1 + I <sub>IMON</sub> Error)                                          |                                               | 264.4  |               | 219.6             |

| R <sub>F</sub>                             | 10                        | kΩ                     | Fixed Resistor Value in Power Source                                                          | 0.5%                                          | 10.05  | -0.5%         | 9.95              |

| V <sub>COMP</sub>                          | 802                       | mV                     | I <sub>IOUT</sub> • R <sub>F</sub>                                                            |                                               | 876    |               | 728               |

| V <sub>COMP</sub> Error                    | 0                         | %                      |                                                                                               |                                               | 9.2    |               | -9.2              |

| With Compensat                             | ion                       |                        | ·                                                                                             |                                               |        |               |                   |

| V <sub>LOAD_ERROR</sub>                    | 2                         | mV                     | V <sub>COMP</sub> – V <sub>DROP</sub>                                                         |                                               | 76     |               | -72               |

| Load Regulation                            | 0.03                      | %                      |                                                                                               |                                               | 1.52   |               | -1.44             |

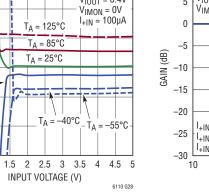

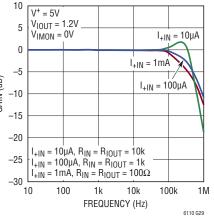

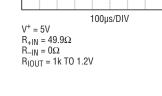

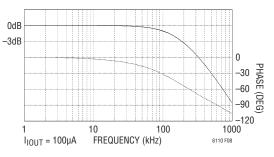

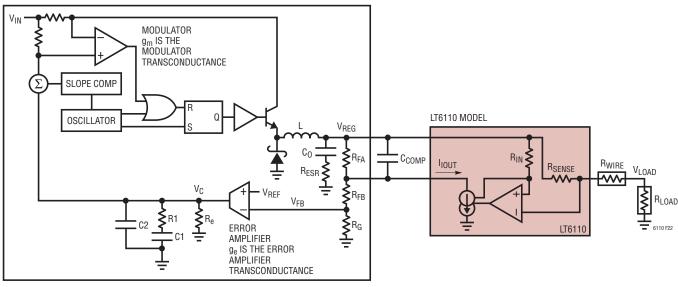

#### FREQUENCY RESPONSE AND TRANSIENTS

The LT6110 has a -3dB bandwidth of 180kHz. This smooth frequency response is shown in Figure 8. This defines the response time from the sensed input voltage to the compensation output currents. Power sources will typically have a large output capacitance making their loop response bandwidth much slower than the LT6110. The cable drop compensation loop is much faster than the power source so there should be little impact on loop stability in driving a remote load.

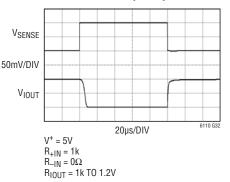

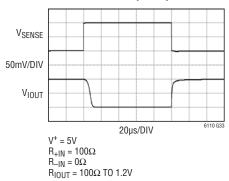

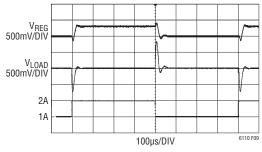

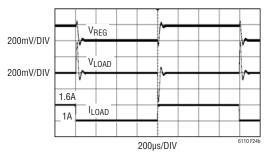

For fast or step change variations in load current some transients will be observed at the power source output and at the remote load due to the finite reaction time of the compensation loop. The amount of voltage transient seen will depend mostly on the size and quality of the supply bypass capacitors used at each end of the load connecting wire. An example of these transients is shown in Figure 9. Any ringing while settling out can be smoothed by additional filtering components in the control loop. A small feedback capacitor across the regulator feedback resistor,  $R_F$ , can provide effective smoothing of transients. Specific values to use depend on the particular application component values.

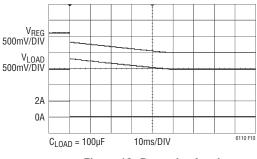

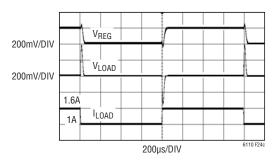

One important consideration for transients is a sudden open or removal of the load current from a high current condition. There is a risk of overvoltage at the load before the LT6110 can reduce the compensation voltage. A good solution to this potential issue is to bypass the remote load with a capacitance greater than the capacitance at the output of the regulator or power source. Figure 10 shows a load removal transient using a  $100\mu$ F load. Fortunately the amount of compensation in most applications should not be so large as to cause a serious overvoltage risk but should always be considered.

Figure 8. LT6110 Frequency Response

Figure 9. VLOAD Compensated

Figure 10. Removing Load

In addition to using a regulator capacitor to adjust the loop response, an RC pole in the LT6110 circuit can provide frequency compensation. Figure 11 shows an LT6110 with an input RC filter. Using the input RC filter introduces a second pole to the LT6110 one pole response (Figure 9). The LT6110 poles become a zero in the regulator's open-loop response that includes the LT6110 in its feedback path (providing the same function as the regulator's R<sub>F</sub> with a shunt capacitor).

Loop compensation with an LT6110 RC filter is not required if the regulator's loop is compensated with a zero in the feedback divider (refer to the Regulator Loop Stability section).

Figure 11. LT6110 Frequency Compensation

### **EXTERNAL CURRENT SENSE RESISTORS**

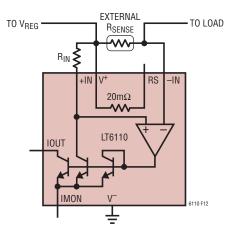

The LT6110 internal current sense resistor,  $R_{SENSE}$ , is provided for convenient use in many applications with a maximum load current less than 3A. For higher current or greater precision wire loss compensation an external sense resistor can be used. The external  $R_{SENSE}$  resistor can be a low valued current sense or shunt resistor, the DC resistance (DCR) of an inductor, or the resistance of a printed circuit board trace. Figure 12 shows an LT6110 circuit configuration using an external sense resistor. The internal resistor at the RS pin is left open circuited.

Figure 12. Using an External  $R_{\mbox{SENSE}}$  (Resistor, Inductor or PCB Trace)

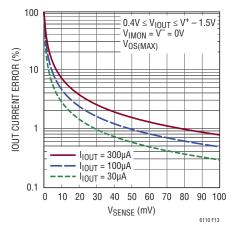

The value of the external R<sub>SENSE</sub> determines the V<sub>SENSE</sub> voltage. If I<sub>IOUT</sub> is 100 $\mu$ A then a V<sub>SENSE</sub> of 50mV is large enough to minimize the compensating IOUT current error due to V<sub>OS</sub> to less than 1% (see Figure 13).

Figure 13. V<sub>SENSE</sub>

#### **Precision Current Shunt Resistor**

A precision, very low V<sub>LOAD</sub> error, compensation circuit can be implemented with an LT6110 and a precision external R<sub>SENSE</sub>. A ±1% to ±5% tolerance or better R<sub>SENSE</sub> resistor significantly reduces I<sub>IOUT</sub> compensation current error due to part to part variations. In addition, the low temperature coefficient (TCR of typically ±100ppm/°C) of an external sense resistor greatly reduces the contribution of R<sub>SENSE</sub> to the total voltage drop loss at higher operating temperatures. Figure 14 shows a 5V, 3.5A buck regulator with an LT6110 using an external R<sub>SENSE</sub>. Table 2 is a list of typical current sense resistors.

| lable 2. Surface Mount R <sub>SENSE</sub> Resistors |                                                         |                      |                                                                                |          |              |  |

|-----------------------------------------------------|---------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|----------|--------------|--|

| PART NUMBER THICK FILM                              | VALUE RANGE                                             | TOLERANCE            | TCR                                                                            | POWER    | SIZE         |  |

| IRC LRC-LRF-2512                                    | $2m\Omega$ to $1\Omega$                                 | 1% to 5%             | 100ppm                                                                         | 2W       | 2512         |  |

| Stackpole Electronics CSR2512                       | 10m $\Omega$ to 1 $\Omega$                              | 1% to 5%             | 200ppm                                                                         | 2W       | 2512         |  |

| Vishay RCWE2512                                     | 33m $\Omega$ to 51 $\Omega$                             | 1% to 5%             | 200ppm                                                                         | 2W       | 2512         |  |

| Panasonic ERJM1W                                    | 1m $\Omega$ to 20m $\Omega$                             | 1% to 5%             | 100ppm                                                                         | 2W       | 2512         |  |

| Susumu PRL1632<br>Susumu PRL3264                    | $10m\Omega$ to $100m\Omega$ $10m\Omega$ to $100m\Omega$ | 1% to 2%<br>1% to 2% | 100ppm ( $20m\Omega$ to $51m\Omega$ )<br>100ppm ( $20m\Omega$ to $51m\Omega$ ) | 1W<br>2W | 1206<br>2512 |  |

#### Table 2. Surface Mount R<sub>SENSE</sub> Resistors

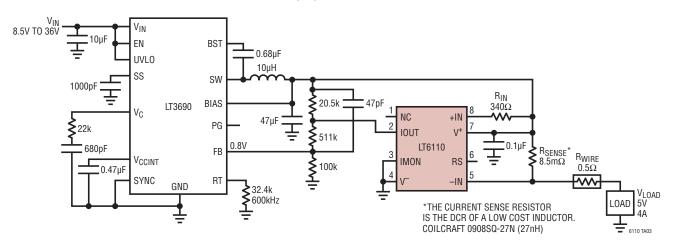

#### Copper Resistor Made from an R<sub>F</sub> Inductor

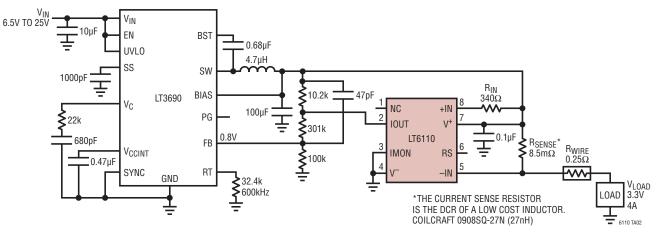

An inductor made of copper wire will have a small DC resistance, DCR or  $R_{COIL}$ , with a temperature coefficient that matches that of the copper wire connecting the remote load. Copper wire resistance has a positive temperature coefficient of approximately +3900ppm/°C. If the current sense resistor and the remote load are in the same operating environment and subject to an increase in temperature, the resistance increase in R<sub>SENSE</sub> will increase both V<sub>SENSE</sub> and the LT6110 compensation current to directly track and cancel the increase in wire voltage drop to the load (refer to the Temperature Errors section). Table 3 shows a list of small air core inductors suitable for use as external R<sub>SENSE</sub> resistors.

| Table 3. Coilcraft Air Core Inductors for External R <sub>SENSE</sub> |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

| 02.110E                  |                     |                                   |                         |  |  |  |

|--------------------------|---------------------|-----------------------------------|-------------------------|--|--|--|

| COILCRAFT PART<br>Number | INDUCTANCE<br>(nH)* | DCR NOMINAL (mΩ)<br>(±6% typical) | I <sub>RMS</sub><br>(A) |  |  |  |

| 0908SQ-27N               | 27                  | 8.5                               | 4.4                     |  |  |  |

| 2222SQ-221               | 221                 | 9.8                               | 5                       |  |  |  |

| 1010 US-141              | 146                 | 3.1                               | 14                      |  |  |  |

\*Inductance is not relevant for current sense.

### **PCB Copper Resistor**

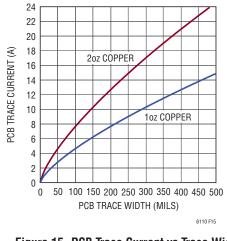

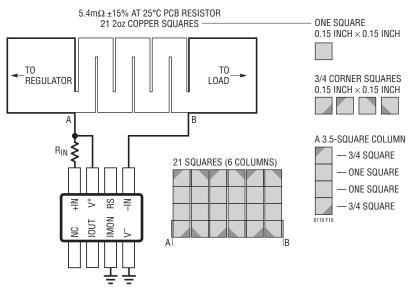

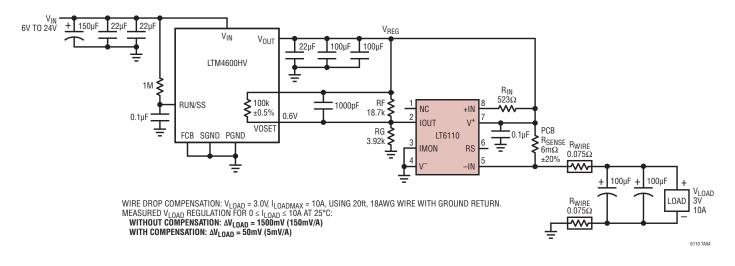

In a high load current application without a high precision load regulation specification, the cost of an external R<sub>SENSE</sub> resistor can be eliminated using the resistance of a printed circuit board, PCB, trace as a sense resistor. The resistance,  $R_{PCB}$ , is a function of copper resistivity ( $\rho$ ), PCB copper thickness (T), trace width (W) and trace length (L),  $R_{PCB} = \rho (L/(T \bullet W))$ . The typical manufacturing of PCB fabrication limits the trace resistance tolerance to  $\pm 15\%$ . A simplified R<sub>PCB</sub> calculation sets the length equal to the width (L/W = 1) and approximates  $0.5m\Omega$  and  $0.25m\Omega$ per square trace area for 1oz and 2oz copper respectively. The maximum current of a PCB trace depends on the trace cross sectional area, trace width (W) times copper thickness (T) and the amount of heating of the trace permitted. Figure 15 plots PCB trace current vs PCB trace width for 1oz (T = 1.4mils) and 2oz (T = 2.8mils) copper for less than 10°C temperature rise (this graph provides a conservative maximum trace current estimate based on the ANSI IPC2221 standard).

Figure 15. PCB Trace Current vs Trace Width (<10°C Temperature Rise)

Example: Design a 2oz copper PCB trace sense resistor to compensate for wire voltage drop for an  $I_{I,OAD(MAX)}$  of 10A.

A V<sub>SENSE</sub> of 60mV is large enough to minimize the compensating IOUT current error due to the input offset voltage of the LT6110.

$$R_{PCB} = \frac{V_{SENSE}}{I_{LOAD(MAX)}} = \frac{60mV}{10A} = 6m\Omega$$

Using Figure 15, the 2oz copper minimum trace width for 10A is 150mils. This sets the current handling capability of the trace.

The resistance of the trace resistor is set by the length of the trace. Each 150mil wide square of 2oz copper will have a resistance of  $0.25m\Omega$ . A total resistance of  $6m\Omega$  will require 24 squares ( $6m\Omega/0.25m\Omega/square$ ). The length of the PCB trace will then be  $24sq \times 150$  mils or 3.6 inches.

A serpentine layout can be used to reduce the footprint of  $R_{PCB}$ . Figure 16 shows a serpentine layout for a  $6m\Omega$  PCB sense resistor and the V<sub>SENSE</sub> connections to the LT6110. The corners of the serpentine resistor count as 3/4 of a square. In Figure 16, R<sub>PCB</sub> consists of six 3.5 square rectangular traces (two whole squares and two 3/4 squares). The  $R_{PCB}$  six rectangular traces equal 21 0.15 in  $\times$  0.15 in squares. Using a 2oz copper trace the resistance of the 21 squares is  $5.25m\Omega$  at  $25^{\circ}$ C (21 •  $0.25m\Omega$  per square). An additional very small trace resistance is due to the 0.015 in  $\times$  0.15 in trace that connects the rectangular

Figure 16. LT6110 and PCB Trace Resistor Layout

traces at the top and bottom corner squares. There are five connecting traces and their total resistance is  $0.125m\Omega$  ([0.015 inch/0.15 inch] •  $0.25m\Omega • 5$ ).

### Temperature Errors

In addition to the initial errors at 25°C the errors due to a temperature variation must be included. The ambient temperature variation of the LT6110 and the wire can have the following cases: The LT6110 and wire are at the same temperature, the LT6110 and wire are at much different temperatures or the temperature of the LT6110 circuit is known and the wire temperature can only be approximated. The design procedure targets a load voltage equal to  $V_{\text{REG(NOM)}}$  at maximum load current and cancels  $V_{\text{DROP}}$  by setting  $I_{\text{IOUT}} \cdot R_{\text{F}} = V_{\text{DROP}}$ . If, over the specified temperature range, { $I_{\text{IOUT}} \cdot R_{\text{F}} - V_{\text{DROP}}$ } is not zero volts, then there will be an error to the expected load voltage at maximum load current (for example, if  $V_{\text{LOAD}} = 5V$  at 25°C and at 75°C { $I_{\text{IOUT}} \cdot R_{\text{F}} - V_{\text{DROP}}$ } is 5mV then the  $V_{\text{LOAD}}$  error is 100 • (5mV/5V) = 0.1%).

Since  $I_{IOUT} = V_{SENSE}/R_{IN}$ , the temperature errors must include the errors due to  $R_{IN}$ ,  $R_{SENSE}$  and  $V_{OS}$ .

The error sources due to temperature of an LT6110 circuit are:

The IOUT current error vs temperature coefficient is -50ppm/°C

The V<sub>OS</sub> temperature coefficient is  $\pm 1\mu$ V/°C

The  $R_{IN}$  and  $R_F$  resistors temperature coefficient is  $\pm 100 ppm/^{\circ}C$

The internal  $R_{\mbox{SENSE}}$  resistor temperature coefficient is +3400ppm/°C

An additional temperature error is due to R<sub>WIRE</sub>. The copper wire temperature coefficient is +3900ppm/°C

The IOUT current,  $V_{OS}$ ,  $R_{IN}$  and  $R_F$  errors are small compared to the errors of the internal  $R_{SENSE}$  and  $R_{WIRE}$ . For a 50°C temperature rise the IOUT current,  $V_{OS}$ ,  $R_{IN}$  and  $R_F$  resistor error is 0.25%, 50µV and 0.5% respectively and the internal  $R_{SENSE}$  and  $R_{WIRE}$  error is 17% and 19.5% respectively.

Using the example of  $V_{LOAD} = 5V$ ,  $I_{LOAD} = 2A$ ,  $I_{IOUT} = 71.2\mu$ A,  $R_F = 10$ k,  $R_{IN} = 562\Omega$  and  $R_{WIRE} = 0.336\Omega$  the  $V_{LOAD}$  error due to the following three example cases is calculated:

**Case 1:** LT6110 and the wire are at 75°C and the V<sub>LOAD</sub> error is –0.36%. If the R<sub>SENSE</sub> temperature coefficient matches the wire's temperature coefficient of 3900ppm/°C then the V<sub>LOAD</sub> error is reduced. Using the copper wire resistance of an inductor as an R<sub>SENSE</sub> external the V<sub>LOAD</sub> error is reduced to –0.025%.

**Case 2:** The LT6110 is at 75°C, the wire is at 25°C and the  $V_{LOAD}$  error is 2.3%. The 2.3% error is mostly due to the internal  $R_{SENSE}$  temperature coefficient. Using an external ±100ppm/°C  $R_{SENSE}$  reduces the  $V_{LOAD}$  error to ±0.05%. In addition, using a thermistor across  $R_{IN}$  to increase the IOUT current as the temperature increases can reduce the temperature induced  $V_{LOAD}$  error.

**Case 3:** The LT6110 is at 25°C, the wire is at 75°C and the  $V_{LOAD}$  error is -2.6%. The error is due only to the copper wire resistance increase vs temperature. The Case 3 error can be reduced by designing for the maximum  $R_{WIRE}$  at a specified temperature. Copper wire specifications from a reliable manufacturer are required.

The maximum current per wire is a function of the wire temperature rise due to current, the maximum wire insulation temperature and the number of cable wires (refer to the Copper Wire Information section).

Table 4 is a random list of AWG wire resistance versus current based on lab measurements.

#### **Copper Wire Information**

The wire used in the power distribution of electronic systems is annealed (heated and cooled) copper wire and is specified for its resistance per unit length, weight per unit mass and current capacity. In the American Wire Gauge standard, AWG is the gauge number and corresponds to the diameter of a solid wire (as the gauge number increases the wire diameter decreases, the wire resistance increases and the current capacity decreases). Stranded copper wire is an insulated bundle of packed and twisted bare solid strands and its resistance, weight or cost depends on the type of coating (tin, silver or nickel) and stranding options (how the strands are grouped and twisted). The stranded wire's flexibility is useful for building and routing wire harness. The current capacity of copper wire is inversely proportional to its gauge number, number of wire conductors and operating temperature (increasing gauge, conductors and temperature, decreases current capacity). In addition the wire insulation temperature rating determines the maximum operating current (typical insulation ratings range from 80°C to 200°C).

Copper wire resistance increases directly with operating temperature. The temperature coefficient of copper  $\alpha$  is equal to 0.0039/°C at 20°C (a useful linear approximation from 0°C to 100°C). If R<sub>LOW</sub> is the resistance at a T<sub>LOW</sub> temperature and R<sub>HIGH</sub> is the resistance at a T<sub>HIGH</sub>

|                   | AWG 18<br>Strands/gauge<br>16/30 | AWG 20<br>Strands/gauge<br>7/28 | AWG 22<br>Strands/gauge<br>7/30 | AWG 24<br>Strands/gauge<br>19/36 | AWG 26<br>Strands/gauge<br>19/38 | AWG 28<br>Strands/gauge<br>7/36 | AWG 30<br>Strands/gauge<br>7/38 |

|-------------------|----------------------------------|---------------------------------|---------------------------------|----------------------------------|----------------------------------|---------------------------------|---------------------------------|

| Current<br>(AMPS) | R <sub>WIRE</sub><br>(mΩ/ft)     | R <sub>WIRE</sub><br>(mΩ/ft)    | R <sub>WIRE</sub><br>(mΩ/ft)    | R <sub>WIRE</sub><br>(mΩ/ft)     | R <sub>WIRE</sub><br>(mΩ/ft)     | R <sub>WIRE</sub><br>(mΩ/ft)    | R <sub>WIRE</sub><br>(mΩ/ft)    |

| 1                 | 6.53                             | 9.61                            | 15.42                           | 22.47                            | 37.97                            | 62.31                           | 102.36                          |

| 2                 | 6.54                             | 9.63                            | 15.51                           | 22.66                            | 38.41                            | 63.32                           | 109.14                          |

| 3                 | 6.56                             | 9.68                            | 15.66                           | 22.99                            | 39.08                            | 65.23                           |                                 |

| 4                 | 6.59                             | 9.73                            | 15.84                           | 23.38                            | 40.21                            |                                 |                                 |

| 5                 | 6.62                             | 9.82                            | 15.99                           | 23.78                            |                                  |                                 |                                 |

| 6                 | 6.65                             | 9.90                            | 16.32                           |                                  |                                  |                                 |                                 |

| 7                 | 6.71                             | 10.02                           |                                 |                                  |                                  |                                 |                                 |

| 8                 | 6.79                             | 10.15                           |                                 |                                  |                                  |                                 |                                 |

| 9                 | 6.83                             |                                 |                                 |                                  |                                  |                                 |                                 |

| 10                | 6.91                             |                                 |                                 |                                  |                                  |                                 |                                 |

#### Table 4. A Random List of Wire Resistance vs Current at 20°C

temperature then the wire's resistance vs temperature is:

$\mathsf{R}_{\mathsf{HIGH}} = \mathsf{R}_{\mathsf{LOW}} \bullet (\mathsf{1} + \alpha \bullet (\mathsf{T}_{\mathsf{HIGH}} - \mathsf{T}_{\mathsf{LOW}})).$

An approximation to the temperature rise in a wire due to current can be derived from the wire's resistance vs temperature equation using the wire's resistance increase vs safe operating current. If  $R_{LOW}$  is the wire resistance at a low current and  $R_{HIGH}$  is the wire resistance at a higher current and  $T_{RISE}$  is equal to  $T_{HIGH} - T_{LOW}$  then the temperature rise in a wire is:

$T_{RISE}$  (°C) = 256.4 • (R<sub>HIGH</sub>/R<sub>LOW</sub> - 1).

Table 4 is a list of measured copper wire resistance versus current at 20°C for an arbitrary group of 18AWG to 30AWG wires.

Example: Find the wire temperature rise for 3A flowing in a 28AWG wire. The 28AWG wire on Table 4 has 62.31m $\Omega$ /ft R<sub>LOW</sub> resistance at 1A and 65.23m $\Omega$ /ft R<sub>HIGH</sub> resistance at 3A.

$T_{RISE}$  for 3A is equal to 256.4 • (65.23/62.31 - 1) = 12°C.

An LT6110 wire drop compensation design requires reliable information of wire resistance and current capacity. Published copper wire tables are a convenient quick-start guide to copper wire information. However accurate copper wire data is obtained by actual measurements of samples of copper wire to be used from a reputable manufacturer. A statistically small sample of copper wire is sufficient for measurements (the average measured mass resistivity deviation of a large sample of copper wire is only ±0.26%).

The International Annealed Copper Standard of mass resistivity is:

$153.28 \bullet 10^{-6} (\Omega \text{-kg})/\text{m}^2$  in Metric and

$31.39 \cdot 10^{-6} (\Omega-lb)/ft^2$  in English units.

Mass resistivity is the product of Resistance/Length and Mass/Length and is useful for estimating the weight of copper wire required and its cost (the cost of copper wire depends on its weight and the price fluctuation of copper in the commodities market).

The weight of copper wire is:

153.28 • 10<sup>-6</sup>(Length in m<sup>2</sup>)/(Resistance in  $\Omega$ ) in kilograms or 31.39 • 10<sup>-6</sup>(Length in ft<sup>2</sup>)/(Resistance in  $\Omega$ ) in pounds.

Example: Find the weight of one hundred thousand feet of 18AWG wire and compare it to the weight of a 24AWG wire:

Table 4 shows 6.5mΩ/ft for 18AWG and 22.43mΩ/ft for 24AWG.

The weight of the 18AWG wire is:

$(31.39 \cdot 10^{-6}) \cdot [(100000)^2/(6.5 \cdot 10^{-3} \cdot 100000)] = 483 \text{ pounds.}$

The weight of the 24AWG wire is:

$(31.39 \cdot 10^{-6}) \cdot [(100000)^2 / (22.43 \cdot 10^{-3} \cdot 100000)]$ = 141 pounds.

The weight of the 18AWG is  $3.4 \times$  the weight of the 24AWG.

Using an LT6110 simplifies wire drop compensation and provides the option to specify the smallest size and lowest cost of copper wire.

The US Department of Commerce, National Bureau of Standards Handbook 100 is a comprehensive source of copper wire information.

### **Power Dissipation**

The LT6110 power dissipation is at a minimum for  $I_{+IN}$  100µA or less. If the  $I_{+IN}$  current is at its specified maximum of 1mA or greater then the maximum power dissipation and operating temperature must be considered. The LT6110 power dissipation is the sum of three components:

$V_{IOUT} \bullet I_{IOUT}$ ,

$V_{REG} \bullet (I_{+IN} + I_{SUPPLY})$  and

I<sub>LOAD</sub><sup>2</sup> • R<sub>SENSE</sub> (if the internal R<sub>SENSE</sub> is used)

Example of an extreme power dissipation case:

$V_{REG} = 50V, I_{+IN} = 1mA.$

$V_{IOUT} = 36V, I_{IOUT} = 1mA,$

$I_{SUPPLY} = 2.7 \text{mA} (I_{SUPPLY} \text{ is a function of } I_{+IN}. \text{See the } I_{SUPPLY} \text{ vs } I_{+IN} \text{ plot under Typical Performance Characteristics}).$

$I_{LOAD}$  = 2A and  $R_{SENSE}$  = 20m $\Omega$

Calculate LT6110 power dissipation:

Power =  $36 \cdot 0.001 + 50 \cdot (0.001 + 0.0027) + 2^2 \cdot 0.02$ Power = 0.301 Watts

Figure 17. LT6110 Power Dissipation

The maximum operating ambient temperature  $T_{AMAX}$  is equal to  $T_{JMAX}-\theta_{JA}\bullet$  Power.

$T_{JMAX}$  is 150°C and  $\theta_{JA}$  is 195°C/W for a TSOT-23 package and

$T_{JMAX}$  is 150°C and  $\theta_{JA}$  is 80.6°C/W for a DFN package.

$T_{AMAX} = 150$ °C – 0.301W • 195°C/W = 91°C for the TSOT-23 package and

$T_{AMAX}$  = 150°C - 0.301W  $\bullet$  80.6°C/W = 126°C for the DFN package.

### Limiting the Regulator Boost Voltage ( $V_{REGMAX}$ )

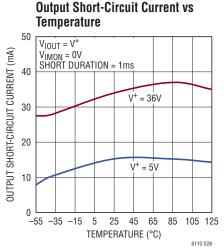

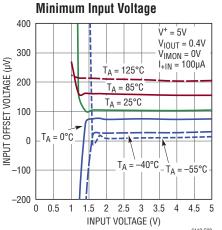

In some wire drop compensation applications it may be necessary to limit the maximum voltage at the regulator output to ensure the safe operation of all load circuitry. Adding a resistor,  $R_{IOUT}$ , in series with the output pin limits the maximum compensation current. This in turn limits the maximum voltage boosting at the regulator output,  $V_{REGMAX}$ . The increasing  $I_{IOUT}$  current through  $R_{IOUT}$  drops the voltage at the IOUT pin to a minimum level and limits the maximum IOUT current (refer to the Minimum IOUT to IMON Voltage vs Temperature graph under Typical Performance Characteristics). If the limited IOUT current is greater than 1mA, a 0.1µF capacitor should be placed from the IOUT pin to ground to ensure stable operation. The  $R_{IOUT}$  resistor limits the regulator's voltage to an arbitrary value higher than  $V_{LOAD} + R_{FA} \bullet I_{IOUT}$ .

### Design Procedure:

1. Select a V<sub>REGMAX</sub> voltage > V<sub>LOAD</sub> + R<sub>FA</sub> • I<sub>IOUT</sub>.

#### Figure 18. Limiting Regulator Voltage Boost ( $V_{REGMAX}$ )

2. Calculate R<sub>IOUT</sub>:

$$R_{IOUT} = \frac{\left(V_{LOAD} - \frac{R_{FA}}{R_{G}} \bullet V_{FB}\right) \bullet R_{FA}}{V_{REGMAX} - V_{LOAD}}$$

Example: Limit the output of a 5V regulator to less than 6V.

$V_{LOAD} = 5V$ ,  $I_{LOADMAX} = 2A$  and  $I_{IOUT} = 100\mu A$ .

$R_{FA}$  = 6.49k,  $R_{FB}$  = 422k and  $R_G$  = 80.6k,  $R_{IN}$  = 402 $\Omega,$   $V_{FB}$  = 0.79V (Figure 4).

Calculate R<sub>IOUT</sub>:

$$\mathsf{R}_{\mathsf{IOUT}} = \frac{\left(5 - \frac{6490}{80600} \bullet 0.79\right) \bullet 6490}{6 - 5}$$

$R_{IOUT}$  = 32k and 5.649V  $\leq V_{REGMAX} \leq 6V.$

### Limiting V<sub>IOUT</sub>

The absolute maximum voltage at the IOUT pin (V<sub>IOUT</sub>) is 36V. If V<sub>IOUT</sub> is greater than 36V then a Zener diode from the IOUT pin to the regulator resistors and a resistor from the IOUT pin to V<sup>-</sup> can limit the V<sub>IOUT</sub> voltage to  $\leq$ 36V. The Zener diode voltage, V<sub>ZENER</sub>, is typically specified as a nominal voltage with a minimum and a maximum. For limiting V<sub>IOUT</sub>, use the minimum Zener voltage rating, V<sub>ZENERMIN</sub>. V<sub>ZENERMIN</sub> is typically specified at a current of 2mA to 5mA and at the low LT6110 I<sub>IOUT</sub> currents ( $\leq$ 1mA), the actual V<sub>ZENERMIN</sub> can be up to 2V less than the minimum voltage listed in a diode data sheet. Therefore select a Zener diode with a minimum voltage at least 2V

Downloaded from Arrow.com.

Figure 19. Limiting the Voltage at the IOUT Pin (V\_{OUT} \leq 36V)

greater than the calculated V<sub>ZENERMIN</sub> voltage.

$$V_{ZENERMIN} \ge V_{REGMAX} - \begin{pmatrix} V_{IOUT} + I_{IOUT} \cdot R_{FA} + \\ \frac{R_{FA}}{R_G} \cdot V_{FB} \end{pmatrix}$$

$V_{\text{REGMAX}} = V_{\text{LOAD}} + I_{\text{LOADMAX}} \bullet (R_{\text{SENSE}} + R_{\text{WIRE}}).$ Example: Limit  $V_{\text{IOUT}}$  to 20V.

$V_{LOAD}$  = 48V and  $I_{LOADMAX}$  = 2A,  $R_{WIRE}$  = 1 $\Omega$ .

$\begin{array}{l} R_{SENSE} = 20m\Omega, \, R_{FA} = 20.5k, \, R_{FB} = 453k, \, R_{G} = 12.4k, \, R_{IN} \\ = 402\Omega, \, V_{FB} = 1.223V, \, I_{IOUT} = 100 \mu A. \end{array}$

Calculate  $V_{\text{REGMAX}} = 48 + 2(0.02 + 1) = 50.04V$ .

Calculate V<sub>ZENERMIN</sub>:

V<sub>ZENERMIN</sub> ≥ 50.04 -

$$\begin{pmatrix} 20 + (100 \cdot 10^{-6}) \cdot (20.5 \cdot 10^{3}) + (20.5 \cdot 10^{3})$$

$V_{ZENERMIN} = 26V.$

The minimum Zener diode voltage must be  $\geq$ 28V.

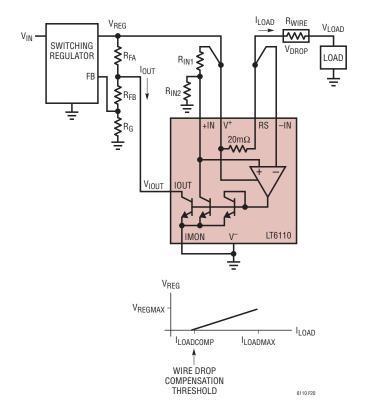

#### Setting the Wire Compensation Threshold

With light load currents, wire drop compensation may not be desirable. An additional resistor,  $R_{IN2},$  from the +IN pin to ground provides the option to set a load current

Figure 20. Setting the Wire Drop Compensation Threshold

threshold,  $I_{LOADCOMP}$ , for the start of wire drop compensation. When the load current is equal to  $I_{LOADCOMP}$  the maximum error in voltage at the load occurs. For  $I_{LOAD}$  greater than  $I_{LOADCOMP}$  the error in voltage at the load decreases to zero at  $I_{LOADMAX}$ .

Design Procedure:

- 1. Choose a threshold current.

- 2. Calculate  $\mathsf{R}_{\mathsf{IN1}}$  and  $\mathsf{R}_{\mathsf{IN2}}$ :

$$R_{IN1} = \frac{I_{LOADMAX} \bullet R_{SENSE}}{I_{IOUT}} - \frac{\frac{V_{LOAD} + I_{LOADMAX} \bullet R_{WIRE}}{I_{IOUT}}}{\frac{V_{LOAD}}{I_{LOADCOMP} \bullet R_{SENSE}} - 1}$$

$$R_{IN2} = \left(\frac{V_{LOAD}}{I_{LOADCOMP} \bullet R_{SENSE}} - 1\right) \bullet R_{IN1}$$

١/

Example: Design the start of wire drop compensation at 1A.  $V_{LOAD} = 5V$ ,  $I_{LOADMAX} = 3.5A$ ,  $R_{WIRE} = 0.25\Omega$ ,  $R_{SENSE} = 25m\Omega$  and  $I_{IOIIT} = 100\mu A$ .

6110fa

• D

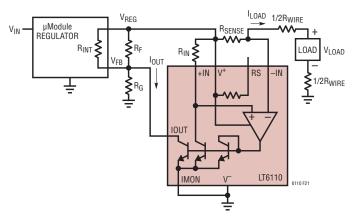

Figure 21. An LT6110 with a  $\mu Module$  Regulator

1.  $I_{LOADCOMP} = 1A$ .

2. Calculate  $R_{IN1}$  and  $R_{IN2}$ :  $R_{IN1}$  = 576  $\Omega$  and  $R_{IN2}$  = 115k.

At  $I_{LOAD} = 1AV_{LOAD} = 4.75V$  and at  $I_{LOAD} = 3.5AV_{LOAD} = 5V$ .

#### Wire Drop Compensation Using a µModule Regulator

Typically a  $\mu$ Module<sup>®</sup> regulator contains a resistor (R<sub>INT</sub>) from the regulator's output to the error amplifier's input. The  $\mu$ Module resistor is inaccessible and is in parallel to the external feedback resistor (R<sub>F</sub>) required for wire drop compensation with an LT6110 (the R<sub>INT</sub> value is listed in the  $\mu$ Module regulator data sheet).

Design Procedure:

- 1. Choose the compensation current  $I_{IOUT}$  (100µA typically).