### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                                        |             | Min.     | Max.     | Units |

|-------------------|-------------------------------------------------------------------|-------------|----------|----------|-------|

| Vs                | High side offset voltage                                          |             | -0.3     | 600      |       |

| V <sub>BS</sub>   | High side floating supply voltage                                 |             | -0.3     | 25       |       |

| Vcc               | Low side and logic fixed supply voltage                           |             | -0.3     | 25       |       |

| V <sub>IN</sub>   | Maximum input voltage between V <sub>IN+ and</sub> V <sub>S</sub> | 1           | -5       | 5        | V     |

| V <sub>PO</sub>   | Digital PWM output voltage                                        |             | COM -0.3 | VCC +0.3 |       |

| Voc               | Overcurrent output voltage                                        |             | COM -0.3 | VCC +0.3 |       |

| dV/dt             | Allowable offset voltage slew rate                                |             | _        | 50       | V/ns  |

| PD                | Package power dissipation @ T <sub>A</sub> ≤ +25°C                | 8 lead SOIC | _        | .625     | W     |

|                   |                                                                   | 8 lead PDIP | _        | 1.0      | , vv  |

| Rth <sub>JA</sub> | Thermal resistance, junction to ambient                           | 8 lead SOIC | _        | 200      |       |

|                   |                                                                   | 8 lead PDIP | _        | 125      | °C/W  |

| TJ                | Junction temperature                                              |             | _        | 150      |       |

| T <sub>S</sub>    | Storage temperature                                               |             | -55      | 150      | °C    |

| TL                | Lead temperature (soldering, 10 seconds)                          |             | _        | 300      |       |

Note 1: Capacitors are required between VB and Vs when bootstrap power is used. The external power supply, when used, is required between VB and Vs pins.

## **Recommended Operating Conditions**

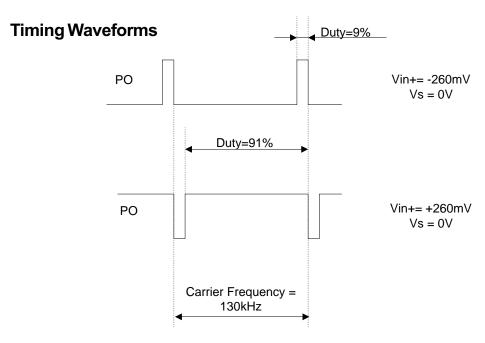

The output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions.

| Symbol          | Definition                                                | Min.                 | Max.               | Units |

|-----------------|-----------------------------------------------------------|----------------------|--------------------|-------|

| V <sub>B</sub>  | High side floating supply voltage                         | V <sub>S</sub> +13.0 | V <sub>S</sub> +20 |       |

| Vs              | High side floating supply offset voltage                  | 0.3                  | 600                |       |

| V <sub>PO</sub> | Digital PWM output voltage                                | СОМ                  | VCC                | V     |

| V <sub>OC</sub> | Overcurrent output voltage                                | СОМ                  | VCC                |       |

| V <sub>CC</sub> | Low side and logic fixed supply voltage                   | 9.5                  | 20                 |       |

| V <sub>IN</sub> | Input voltage between V <sub>IN+</sub> and V <sub>S</sub> | -260                 | +260               | mV    |

| T <sub>A</sub>  | Ambient temperature                                       | -40                  | 125                | °C    |

### **DC Electrical Characteristics**

$V_{CC} = V_{BS} = 15V$ , and  $T_A = 25^{\circ}$  unless otherwise specified.

| Symbol                      | Definition                                           | Min. | Тур. | Max. | Units  | Test Conditions                        |

|-----------------------------|------------------------------------------------------|------|------|------|--------|----------------------------------------|

| V <sub>IN</sub>             | Nominal input voltage range before saturation        | -260 | _    | 260  |        |                                        |

|                             | V <sub>IN+</sub> -V <sub>S</sub>                     |      |      |      |        |                                        |

| V <sub>OC+</sub>            | Overcurrent trip positive input voltage              | _    | 260  | _    | mV     |                                        |

| V <sub>OC</sub> -           | Overcurrent trip negative input voltage              | _    | -260 | _    |        |                                        |

| Vos                         | Input offset voltage                                 | -10  | 0    | 10   |        | V <sub>IN</sub> = 0V (Note 1)          |

| ΔVos/ΔTA                    | Input offset voltage temperature drift               | _    | 25   | _    | μV/°C  |                                        |

| G                           | Gain (duty cycle % per V <sub>IN</sub> )             | 155  | 160  | 165  | %/V    | max gain error=5%                      |

|                             |                                                      |      |      |      |        | (Note 2)                               |

| ΔG/ΔΤΑ                      | Gain temperature drift                               | _    | 20   | _    | ppm/°C |                                        |

| I <sub>LK</sub>             | Offset supply leakage current                        | _    | _    | 50   | μA     | V <sub>B</sub> = V <sub>S</sub> = 600V |

| I <sub>QBS</sub>            | Quiescent V <sub>BS</sub> supply current             | _    | 2    | _    | A      | V <sub>S</sub> = 0V                    |

| Iqcc                        | Quiescent V <sub>CC</sub> supply current             | _    | _    | 0.5  | mA     |                                        |

| LIN                         | Linearity (duty cycle deviation from ideal linearity | _    | 0.5  | 1    | %      |                                        |

|                             | curve)                                               |      |      |      |        |                                        |

| $\Delta V_{LIN}/\Delta T_A$ | Linearity temperature drift                          | _    | .005 | _    | %/°C   |                                        |

| lopo                        | Digital PWM output sink current                      | 20   | _    | _    |        | V <sub>O</sub> = 1V                    |

|                             |                                                      | 2    | _    | _    | ^      | V <sub>O</sub> = 0.1V                  |

| locc                        | OC output sink current                               | 10   | _    | _    | - mA   | V <sub>O</sub> = 1V                    |

|                             |                                                      | 1    | _    | _    |        | V <sub>O</sub> = 0.1V                  |

Note 1: ±10mV offset represents ±1.5% duty cycle fluctuation

Note 2: Gain = (full range of duty cycle in %) / (full input voltage range).

### **AC Electrical Characteristics**

$V_{CC} = V_{BS} = 15V$ , and  $T_A = 25^{\circ}$  unless otherwise specified.

| Symbol                  | Definition                             | Min. | Тур. | Max. | Units  | Test Conditions                 |  |

|-------------------------|----------------------------------------|------|------|------|--------|---------------------------------|--|

| Propagat                | tion delay characteristics             |      |      |      |        |                                 |  |

| fo                      | Carrier frequency output               | 100  | 130  | 180  | kHz    | figure 1                        |  |

| $\Delta$ f/ $\Delta$ TA | Temperature drift of carrier frequency | _    | 500  | _    | ppm/°C | V <sub>IN</sub> = 0 & 5V        |  |

| Dmin                    | Minimum duty                           | _    | 9    | _    | %      | V <sub>IN</sub> +=-260mV,       |  |

| Dmax                    | Maximum duty                           | _    | 91   | _    | %      | V <sub>IN</sub> +=+260mV        |  |

| BW                      | fo bandwidth                           | _    | 15   | _    | kHz    | V <sub>IN</sub> + = 100mVpk -pk |  |

|                         |                                        |      |      |      |        | sine wave, gain=-3dB            |  |

| PHS                     | Phase shift at 1kHz                    | _    | -10  | _    | 0      | V <sub>IN</sub> + =100mVpk-pk   |  |

|                         |                                        |      |      |      |        | sine wave                       |  |

| tdoc                    | Propagation delay time of OC           | 1    | 2    | _    | μsec   |                                 |  |

| twoc                    | Low true pulse width of OC             | _    | 1.5  | _    | μσου   |                                 |  |

Figure 1 Output waveform

## **Application Hint:**

Temperature drift of the output carrier frequency can be cancelled by measuring both a PWM period and the on-time of PWM (Duty) at the same time. Since both periods vary in the same direction, computing the ratio between these values at each PWM period gives consistent measurement of the current feedback over the temperature drift.

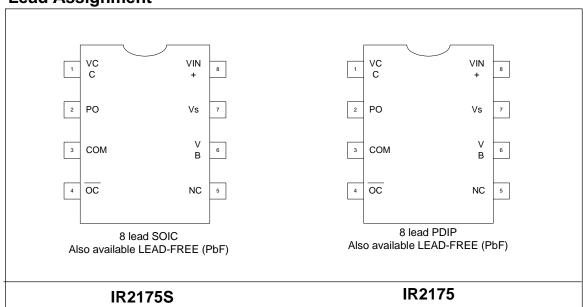

### **Lead Definitions**

| Symbol           | Description                         |

|------------------|-------------------------------------|

| Vcc              | Low side and logic supply voltage   |

| COM              | Low side logic ground               |

| V <sub>IN+</sub> | Positive sense input                |

| VB               | High side supply                    |

| Vs               | High side return                    |

| РО               | Digital PWM output                  |

| <u>oc</u>        | Overcurrent output (negative logic) |

| N.C.             | No connection                       |

# **Lead Assignment**

# IR2175(S) & (PbF)

# International TOR Rectifier

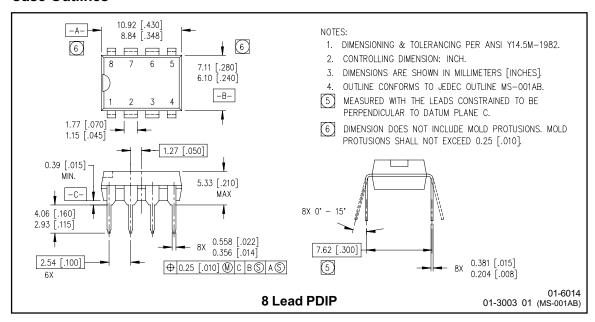

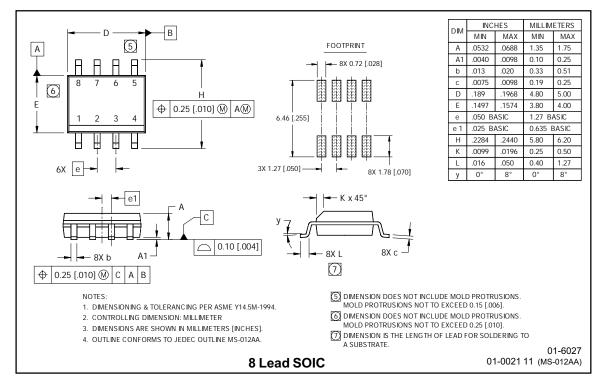

#### **Case Outlines**

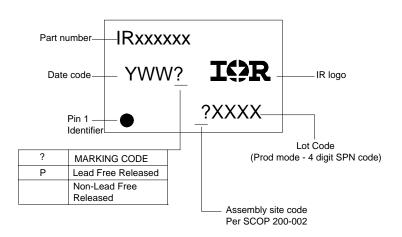

### LEADFREE PART MARKING INFORMATION

### **ORDER INFORMATION**

### **Basic Part (Non-Lead Free)**

8-Lead PDIP IR2175 order IR2175 8-Lead SOIC IR2175S order IR2175S

#### **Leadfree Part**

8-Lead PDIP IR2175 order IR2175PbF 8-Lead SOIC IR2175S order IR2175SPbF

# International TOR Rectifier

Thisproduct has been designed and qualified for the industrial market.

Qualification Standards can be found on IR's Web Site http://www.irf.com

Data and specifications subject to change without notice.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

9/6/2004