#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                         |                       | Min.                  | Max.                  | Units |  |  |  |

|---------------------|----------------------------------------------------|-----------------------|-----------------------|-----------------------|-------|--|--|--|

| V <sub>B</sub>      | High side floating absolute voltage                | -0.3                  | 625                   |                       |       |  |  |  |

| Vs                  | High side floating supply offset voltage           | V <sub>B</sub> - 25   | V <sub>B</sub> + 0.3  |                       |       |  |  |  |

| V <sub>HO</sub>     | High side floating output voltage                  | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3  |                       |       |  |  |  |

| V <sub>CC</sub>     | Low side and logic fixed supply voltage            | -0.3                  | 25                    | .,                    |       |  |  |  |

| V <sub>LO</sub>     | Low side output voltage                            | -0.3                  | V <sub>CC</sub> + 0.3 | - V                   |       |  |  |  |

| DT                  | Programmable dead-time pin voltage (IR21           | V <sub>SS</sub> - 0.3 | V <sub>CC</sub> + 0.3 |                       |       |  |  |  |

| V <sub>IN</sub>     | Logic input voltage (IN & SD)                      | V <sub>SS</sub> - 0.3 | V <sub>CC</sub> + 0.3 |                       |       |  |  |  |

| V <sub>SS</sub>     | Logic ground (IR21094/IR21894 only)                |                       | V <sub>CC</sub> - 25  | V <sub>CC</sub> + 0.3 |       |  |  |  |

| dV <sub>S</sub> /dt | Allowable offset supply voltage transient          |                       | _                     | 50                    | V/ns  |  |  |  |

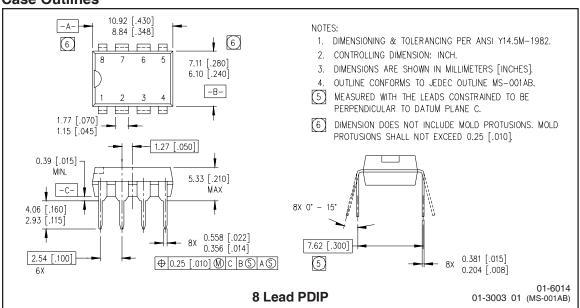

| PD                  | Package power dissipation @ T <sub>A</sub> ≤ +25°C | (8 Lead PDIP)         | _                     | 1.0                   |       |  |  |  |

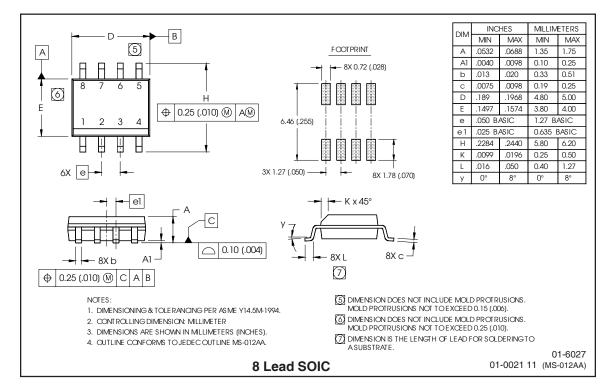

|                     |                                                    | (8 Lead SOIC)         | _                     | 0.625                 | w     |  |  |  |

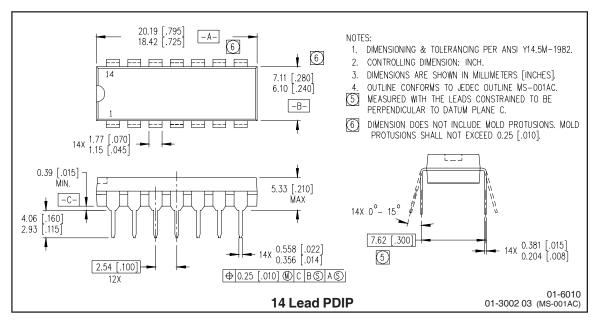

|                     |                                                    | (14 lead PDIP)        | _                     | 1.6                   |       |  |  |  |

|                     |                                                    | (14 lead SOIC)        | _                     | 1.0                   |       |  |  |  |

| RthJA               | Thermal resistance, junction to ambient            | (8 Lead PDIP)         | _                     | 125                   |       |  |  |  |

|                     |                                                    | (8 Lead SOIC)         | _                     | 200                   | °C/W  |  |  |  |

|                     |                                                    | (14 lead PDIP)        | _                     | 75                    |       |  |  |  |

|                     |                                                    | (14 lead SOIC)        | _                     | 120                   | Ī     |  |  |  |

| TJ                  | Junction temperature                               |                       | _                     | 150                   |       |  |  |  |

| T <sub>S</sub>      | Storage temperature                                |                       | -50                   | 150                   | °C    |  |  |  |

| TL                  | Lead temperature (soldering, 10 seconds)           |                       | _                     | 300                   |       |  |  |  |

#### **Recommended Operating Conditions**

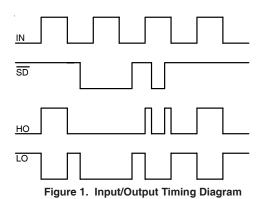

The input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions. The V<sub>S</sub> and V<sub>SS</sub> offset rating are tested with all supplies biased at 15V differential.

| Symbol          | Definition                                        | Min.                | Max.                | Units |

|-----------------|---------------------------------------------------|---------------------|---------------------|-------|

| VB              | High side floating supply absolute voltage        | V <sub>S</sub> + 10 | V <sub>S</sub> + 20 |       |

| Vs              | High side floating supply offset voltage          | Note 1              | 600                 |       |

| V <sub>HO</sub> | High side floating output voltage                 | Vs                  | V <sub>B</sub>      |       |

| Vcc             | Low side and logic fixed supply voltage           | 10                  | 20                  |       |

| V <sub>LO</sub> | Low side output voltage                           | 0                   | V <sub>CC</sub>     | V     |

| V <sub>IN</sub> | Logic input voltage (IN & SD)                     | V <sub>SS</sub>     | V <sub>CC</sub>     |       |

| DT              | Programmable dead-time pin voltage (IR21094 only) | V <sub>SS</sub>     | V <sub>CC</sub>     |       |

| Vss             | Logic ground (IR21094 only)                       | -5                  | 5                   |       |

| T <sub>A</sub>  | Ambient temperature                               | -40                 | 125                 | °C    |

Note 1: Logic operational for  $V_S$  of -5 to +600V. Logic state held for  $V_S$  of -5V to -V<sub>BS</sub>. (Please refer to the Design Tip DT97-3 for more details).

### **Dynamic Electrical Characteristics**

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>) = 15V,  $V_{SS}$  = COM,  $C_L$  = 1000 pF,  $T_A$  = 25°C, DT = VSS unless otherwise specified.

| Symbol         | Definition                                     | Min. | Тур. | Max. | Units | <b>Test Conditions</b>      |

|----------------|------------------------------------------------|------|------|------|-------|-----------------------------|

| ton            | Turn-on propagation delay                      | _    | 750  | 950  |       | V <sub>S</sub> = 0V         |

| toff           | Turn-off propagation delay                     | _    | 200  | 280  |       | V <sub>S</sub> = 0V or 600V |

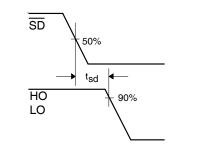

| tsd            | Shut-down propagation delay                    | _    | 200  | 280  |       |                             |

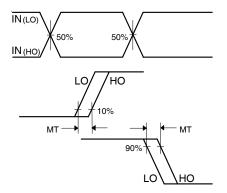

| MT             | Delay matching, HS & LS turn-on/off            | _    | 0    | 70   | nsec  |                             |

| t <sub>r</sub> | Turn-on rise time                              | _    | 150  | 220  |       | V <sub>S</sub> = 0V         |

| tf             | Turn-off fall time                             | _    | 50   | 80   |       | V <sub>S</sub> = 0V         |

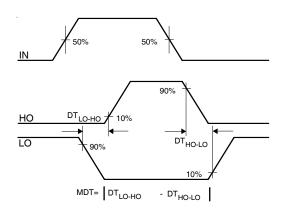

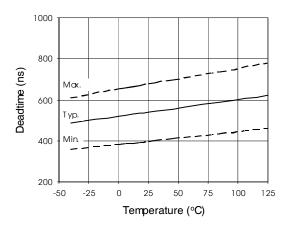

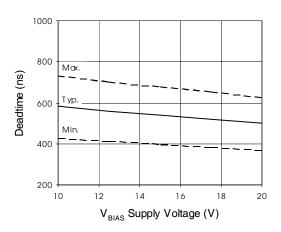

| DT             | Deadtime: LO turn-off to HO turn-on(DTLO-HO) & | 400  | 540  | 680  |       | RDT= 0                      |

|                | HO turn-off to LO turn-on (DTHO-LO)            | 4    | 5    | 6    | usec  | RDT = 200k (IR21094)        |

| MDT            | Deadtime matching = DTLO - HO - DTHO-LO        | _    | 0    | 60   | nsec  | RDT=0                       |

|                |                                                | _    | 0    | 600  | 1.300 | RDT = 200k (IR21094)        |

International

TOR Rectifier

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V,  $V_{SS}$  = COM, DT=  $V_{SS}$  and  $T_A$  = 25°C unless otherwise specified. The  $\overline{V_{IL}}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$ /COM and are applicable to the respective input leads: IN and  $\overline{SD}$ . The  $V_O$ ,  $I_O$  and Ron parameters are referenced to COM and are applicable to the respective output leads: HO and LO.

| Symbol               | Definition                                                                                           | Min. | Тур. | Max. | Units | <b>Test Conditions</b>         |

|----------------------|------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------------------------|

| V <sub>IH</sub>      | Logic "1" input voltage for HO & logic "0" for LO                                                    | 2.9  | _    | _    |       | V <sub>CC</sub> = 10V to 20V   |

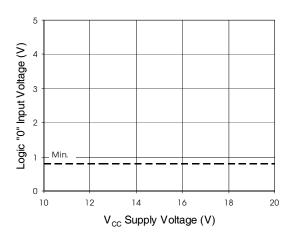

| V <sub>IL</sub>      | Logic "0" input voltage for HO & logic "1" for LO                                                    | _    | _    | 0.8  |       | V <sub>CC</sub> = 10V to 20V   |

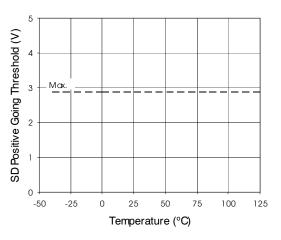

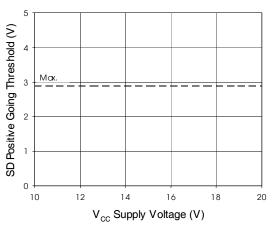

| V <sub>SD,TH+</sub>  | SD input positive going threshold                                                                    | 2.9  | _    | _    | .,    | V <sub>CC</sub> = 10V to 20V   |

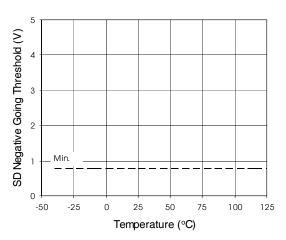

| V <sub>SD,TH</sub> - | SD input negative going threshold                                                                    | _    | _    | 0.8  | V     | V <sub>CC</sub> = 10V to 20V   |

| V <sub>OH</sub>      | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub>                                        | _    | 0.8  | 1.4  |       | I <sub>O</sub> = 20 mA         |

| V <sub>OL</sub>      | Low level output voltage, VO                                                                         | _    | 0.3  | 0.6  |       | I <sub>O</sub> = 20 mA         |

| I <sub>LK</sub>      | Offset supply leakage current                                                                        | _    | _    | 50   |       | $V_{B} = V_{S} = 600V$         |

| I <sub>QBS</sub>     | Quiescent V <sub>BS</sub> supply current                                                             | 20   | 75   | 130  | μA    | V <sub>IN</sub> = 0V or 5V     |

| IQCC                 | Quiescent V <sub>CC</sub> supply current                                                             | 0.4  | 1.0  | 1.6  | mA    | V <sub>IN</sub> = 0V or 5V     |

|                      |                                                                                                      |      |      |      |       | RDT = 0                        |

| I <sub>IN+</sub>     | Logic "1" input bias current                                                                         | _    | 5    | 20   | _     | $IN = 5V, \overline{SD} = 0V$  |

| I <sub>IN</sub> -    | Logic "0" input bias current                                                                         | _    | _    | 2    | μA    | IN = 0V, SD = 5V               |

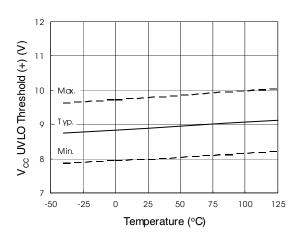

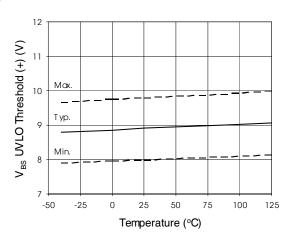

| V <sub>CCUV+</sub>   | $V_{\mbox{\footnotesize{CC}}}$ and $V_{\mbox{\footnotesize{BS}}}$ supply undervoltage positive going | 8.0  | 8.9  | 9.8  |       |                                |

| V <sub>BSUV+</sub>   | threshold                                                                                            |      |      |      |       |                                |

| V <sub>CCUV</sub> -  | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage negative going                               | 7.4  | 8.2  | 9.0  |       |                                |

| V <sub>BSUV</sub> -  | threshold                                                                                            |      |      |      | V     |                                |

| VCCUVH               | Hysteresis                                                                                           | 0.3  | 0.7  | _    |       |                                |

| V <sub>BSUVH</sub>   |                                                                                                      |      |      |      |       |                                |

| I <sub>O+</sub>      | Output high short circuit pulsed vurrent                                                             | 120  | 200  | _    | A     | $V_O = 0V$ , $PW \le 10 \mu s$ |

| I <sub>O-</sub>      | Output low short circuit pulsed current                                                              | 250  | 350  | _    | mA    | $V_O = 15V,PW \le 10 \mu s$    |

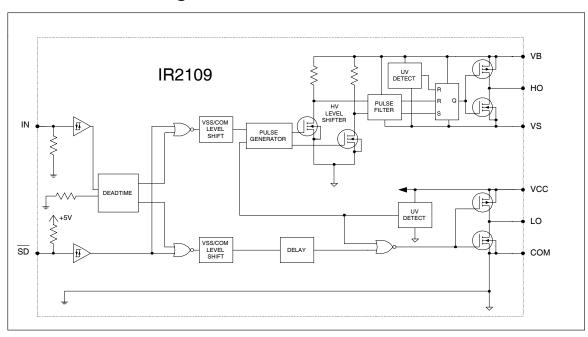

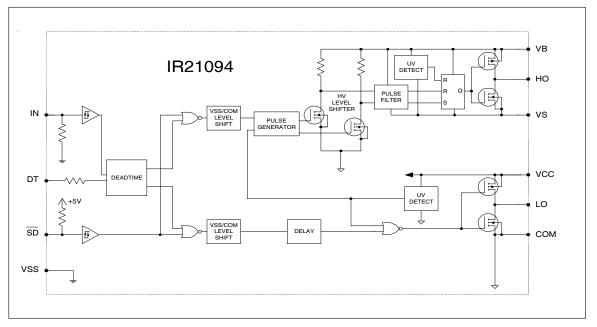

### **Functional Block Diagrams**

International

TOR Rectifier

### **Lead Definitions**

| Symbol          | Description                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------|

| IN              | Logic input for high and low side gate driver outputs (HO and LO), in phase with HO (referenced to COM |

|                 | for IR2109 and VSS for IR21094)                                                                        |

| SD              | Logic input for shutdown (referenced to COM for IR2109 and VSS for IR21094)                            |

| DT              | Programmable dead-time lead, referenced to VSS. (IR21094 only)                                         |

| VSS             | Logic Ground (21094 only)                                                                              |

| V <sub>B</sub>  | High side floating supply                                                                              |

| НО              | High side gate drive output                                                                            |

| Vs              | High side floating supply return                                                                       |

| V <sub>CC</sub> | Low side and logic fixed supply                                                                        |

| LO              | Low side gate drive output                                                                             |

| СОМ             | Low side return                                                                                        |

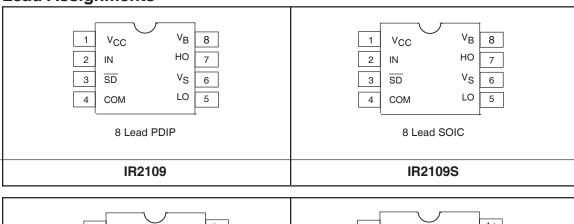

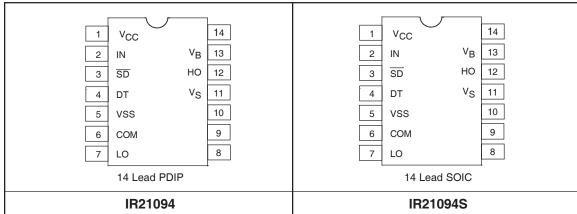

### **Lead Assignments**

IN(LO)

50%

50%

ton

ton

ton

toff

4

90%

90%

10%

Figure 2. Switching Time Waveform Definitions

Figure 3. Shutdown Waveform Definitions

Figure 4. Deadtime Waveform Definitions

Figure 5. Delay Matching Waveform Definitions

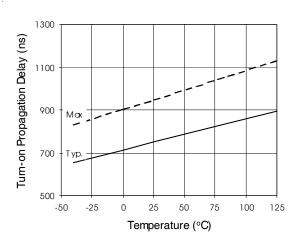

Figure 6A. Turn-on Propagation Delay vs. Temperature

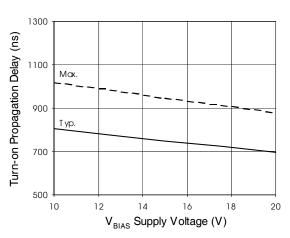

Figure 6B. Turn-on Propagation Delay vs. Supply Voltage

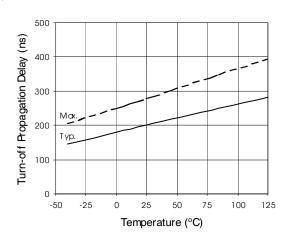

Figure 7A. Turn-off Propagation Delay vs. Temperature

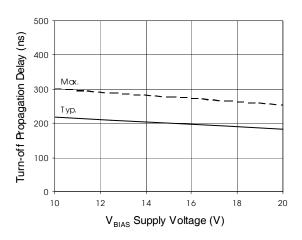

Figure 7B. Turn-off Propagation Delay vs. Supply Voltage

# International TOR Rectifier

## IR2109(4) (s) & (PbF)

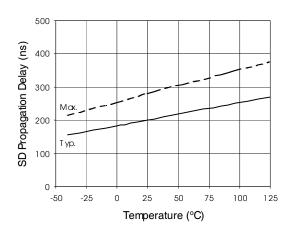

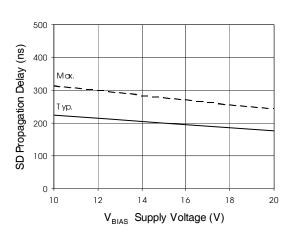

Figure 8A. SD Propagation Delay vs. Temperature

Figure 8B. SD Propagation Delay vs. Supply Voltage

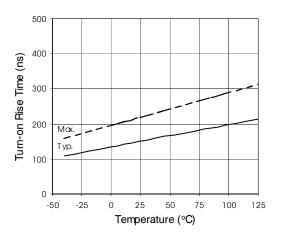

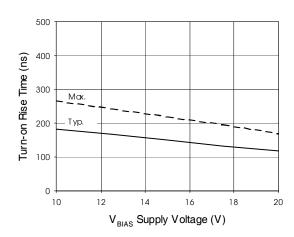

Figure 9A. Turn-on Rise Time vs. Temperature

Figure 9B. Turn-on Rise Time vs. Supply Voltage

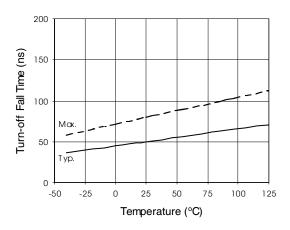

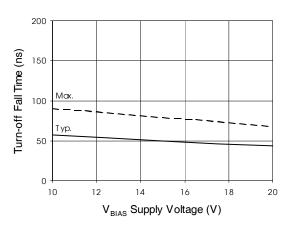

Figure 10A. Turn-off Fall Time vs. Temperature

Figure 10B. Turn-off Fall Time vs. Supply Voltage

Figure 11A. Deadtime vs. Temperature

Figure 11B. Deadtime vs. Supply Voltage

# International Rectifier

## IR2109(4) (s) & (PbF)

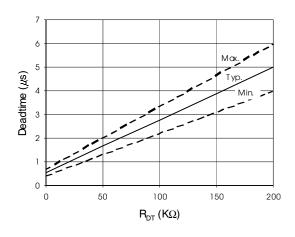

Figure 11C. Deadtime vs. R<sub>DT</sub> (IR21094 only)

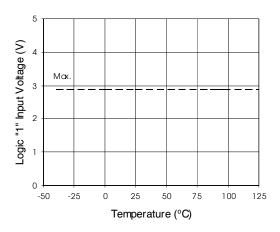

Figure 12A. Logic "1" Input Voltage vs. Temperature

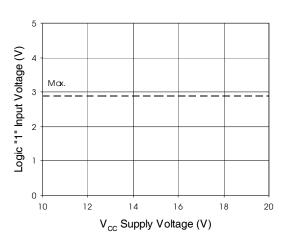

Figure 12B. Logic "1" Input Voltage vs. Supply Voltage

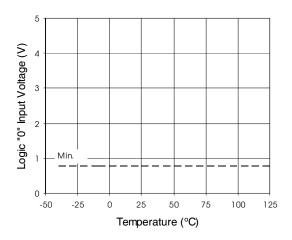

Figure 13A. Logic "0" Input Voltage vs. Temperature

Figure 13B. Logic "0" Input Current vs. Supply Voltage

Figure 14A. SD Positive Going Threshold vs. Temperature

Figure 14B. SD Positive Going Threshold vs. Supply Voltage

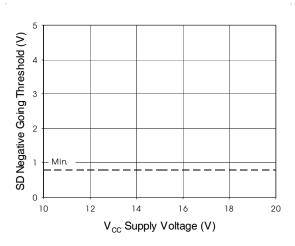

Figure 15A. SD Negative Going Threshold vs. Temperature

Figure 15B. SD Negative Going Threshold vs. Supply Voltage

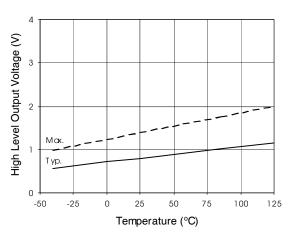

Figure 16A. High Level Output Voltage vs. Temperature

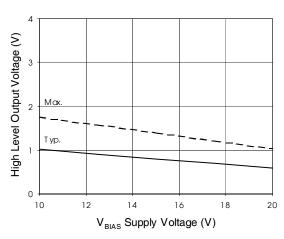

Figure 16B. High Level Output Voltage vs. Supply Voltage

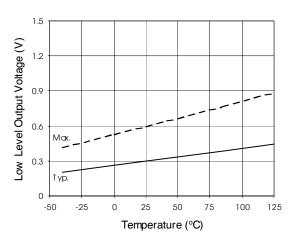

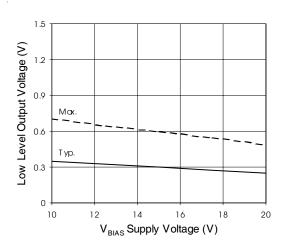

Figure 17A. Low Level Output Voltage vs. Temperature

Figure 17B. Low Level Output Voltage vs. Supply Voltage

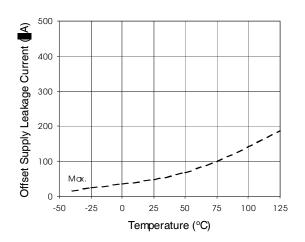

Figure 18A. Offset Supply Leakage Current vs. Temperature

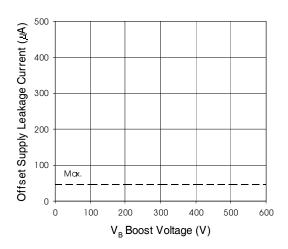

igure 18B. Offset Supply Leakage Current vs. Boost Voltage

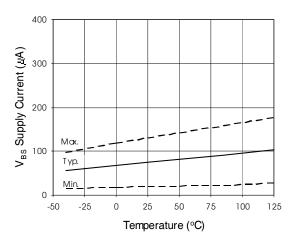

Figure 19A. VBS Supply Current vs. Temperature

# International TOR Rectifier

## IR2109(4) (s) & (PbF)

Figure 19B. VBS Supply Current vs. Supply Voltage

3.0

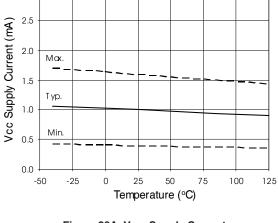

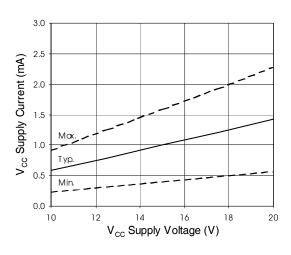

Figure 20A. V<sub>CC</sub> Supply Current vs. Temperature

Figure 20B. V<sub>CC</sub> Supply Current vs. V<sub>CC</sub> Supply Voltage

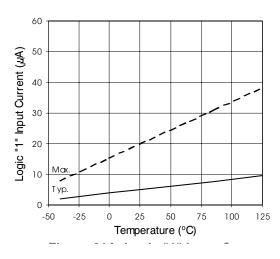

Figure 21A. Logic "1" Input Current vs. Temperature

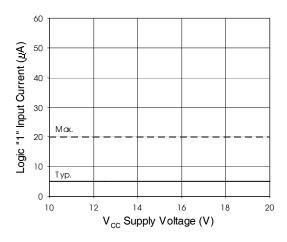

Figure 21B. Logic "1" Input Current vs. Supply Voltage

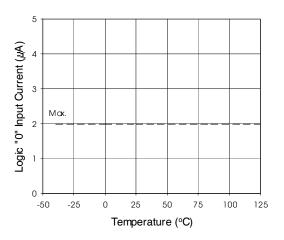

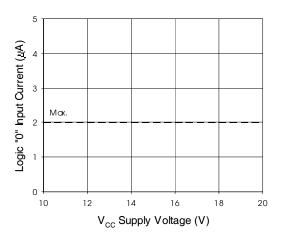

Figure 22A. Logic "0" Input Current vs. Temperature

Figure 22B. Logic "0" Input Currentt vs. Supply Voltage

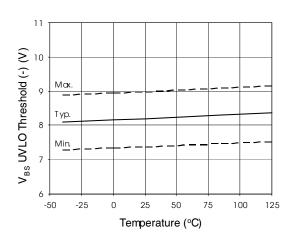

Figure 23. VCC Undervoltage Threshold (+) vs. Temperature

# International TOR Rectifier

## IR2109(4) (s) & (PbF)

Figure 24. VCC Undervoltage Threshold (-) vs. Temperature

Figure 25. VBS Undervoltage Threshold (+) vs. Temperature

Figure 26. VBS Undervoltage Threshold (-) vs. Temperature

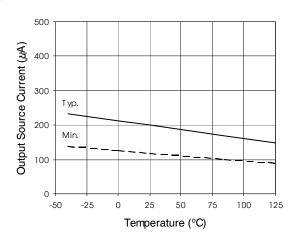

Figure 27A. Output Source Current vs. Temperature

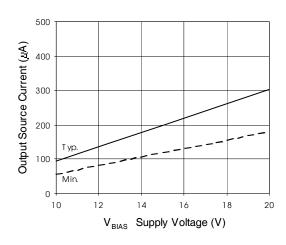

Figure 27B. Output Source Current vs. Supply Voltage

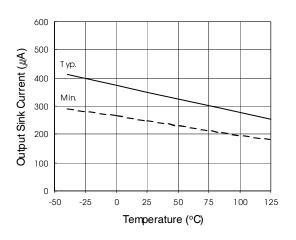

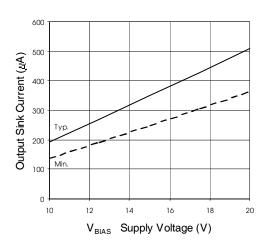

Figure 28A. Output Sink Current vs. Temperature

Figure 28B. Output Sink Currentt vs. Supply Voltage

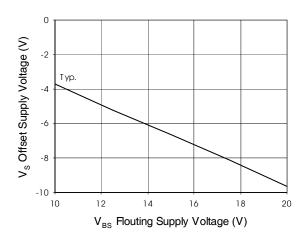

Figure 29. Maximum VS Negative Offset vs. Supply Voltage

# International Rectifier

### IR2109(4) (s) & (PbF)

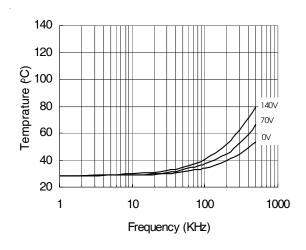

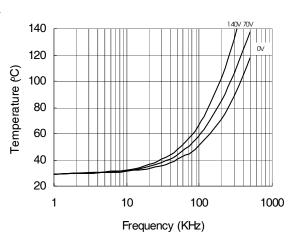

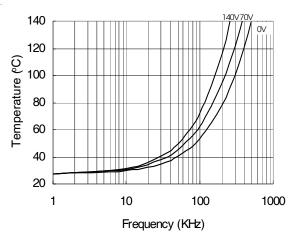

140 120 100 80 60 40 20 1 10 100 1000 Frequency (KHz)

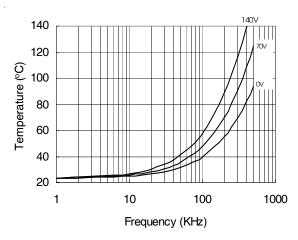

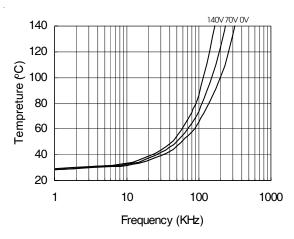

Figure 30. IR2109 vs Frequency (IRFBC20)  $R_{\mbox{\scriptsize qate}} = 33\Omega, \ \mbox{\scriptsize VCC} = 15\mbox{\scriptsize V}$

Figure 31. IR2109 vs Frequency (IRFBC30)  $R_{\mbox{gate}} = 22\Omega, \ \mbox{VCC} = 15 \mbox{V}$

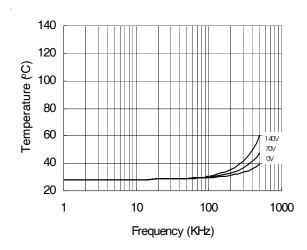

Figure 32. IR2109 vs Frequency (IRFBC40)  $R_{\mbox{gate}} = 15\Omega, \ \mbox{VCC} = 15\mbox{V}$

Figure 33. IR2109 vs Frequency (IRFPE50)  $R_{\mbox{\scriptsize qate}} = 10\Omega, \ \mbox{\scriptsize VCC} = 15\mbox{\scriptsize V}$

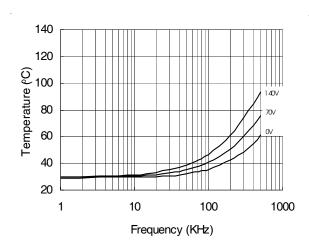

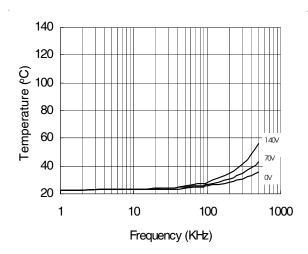

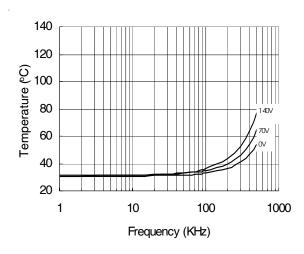

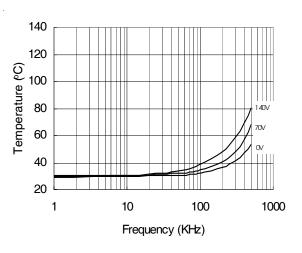

Figure 34. IR21094 vs. Frequency (IRFBC20),  ${\rm R_{\rm qate}}{=}33\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

Figure 35. IR21094 vs. Frequency (IRFBC30),  ${\rm R_{gate}}{=}22\Omega,\,{\rm V_{CC}}{=}15{\rm V}$

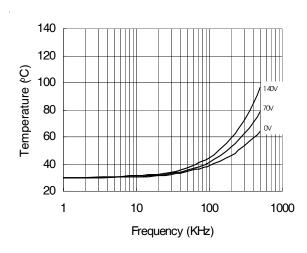

Figure 36. IR21094 vs. Frequency (IRFBC40),  ${\rm R_{\rm qate}}{=}15\Omega, {\rm V_{\rm CC}}{=}15{\rm V}$

Figure 37. IR21094 vs. Frequency (IRFPE50),  ${\rm R_{\rm nate}}{=}10\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

# International Rectifier

### IR2109(4) (s) & (PbF)

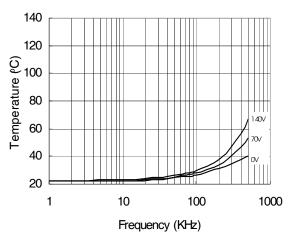

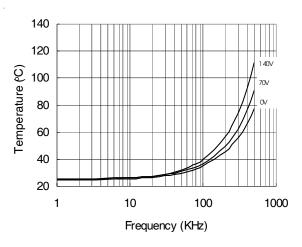

Figure 38. IR2109S vs. Frequency (IRFBC20),  ${\rm R_{\rm qate}} {=} 33\Omega, \, {\rm V_{CC}} {=} 15 {\rm V}$

Figure 39. IR2109S vs. Frequency (IRFBC30),  ${\rm R_{\rm gate}}{=}22\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

Figure 40. IR2109S vs. Frequency (IRFBC40),  ${\rm R_{\rm gate}}{=}15\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

Figure 41. IR2109S vs. Frequency (IRFPE50),  $R_{\text{oate}}$ =10 $\Omega$ ,  $V_{\text{cc}}$ =15V

# International TOR Rectifier

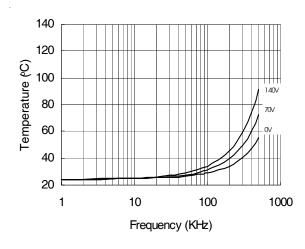

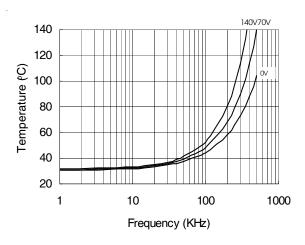

Figure 42. IR21094S vs. Frequency (IRFBC20),  ${\rm R_{gate}}{=}33\Omega,\,{\rm V_{CC}}{=}15{\rm V}$

Figure 43. IR21094S vs. Frequency (IRFBC30),  ${\rm R_{\rm qate}}{=}22\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

Figure 44. IR21094S vs. Frequency (IRFBC40),  ${\rm R_{\rm oate}}{=}15\Omega,\,{\rm V_{\rm cc}}{=}15{\rm V}$

Figure 45. IR21094S vs. Frequency (IRFPE50),  ${\rm R_{\rm qate}}{=}10\Omega,\,{\rm V_{\rm CC}}{=}15{\rm V}$

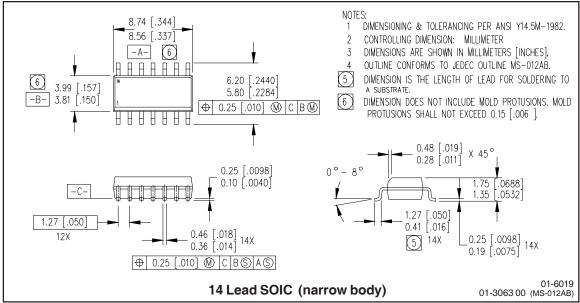

#### **Case Outlines**

Data and specifications subject to change without notice. 7/11/2003

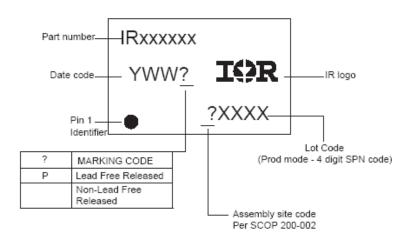

#### LEADFREE PART MARKING INFORMATION

#### **Basic Part (Non-Lead Free)**

#### **Lead-Free Part**

| 8-Lead PDIP IF  | R2109   | order | IR2109   |

|-----------------|---------|-------|----------|

| 8-Lead SOIC IF  | R2109S  | order | IR2109S  |

| 14-Lead PDIP IF | R21094  | order | IR21094  |

| 14-Lead SOIC IF | R21094S | order | IR21094S |

8-Lead PDIP IR2109 order IR2109PbF 8-Lead SOIC IR2109S order IR2109SPbF 14-Lead PDIP IR21094 order IR21094PbF 14-Lead SOIC IR21094S order IR21094SPbF

This product has been designed and qualified for the Industrial market.

Qualification Standards can be found on IR's Website.

Data and specifications subject to change without notice.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information.09/08/04