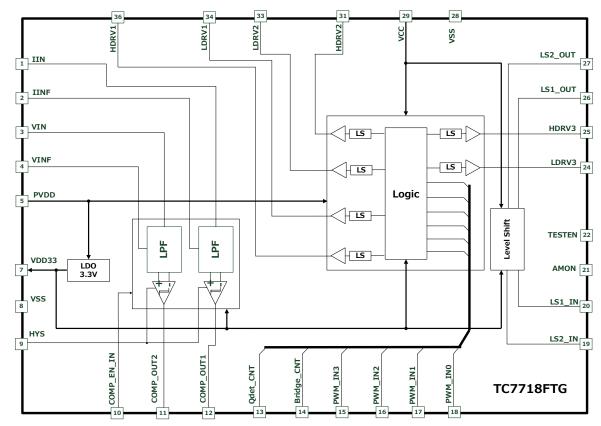

### 4. Block diagram

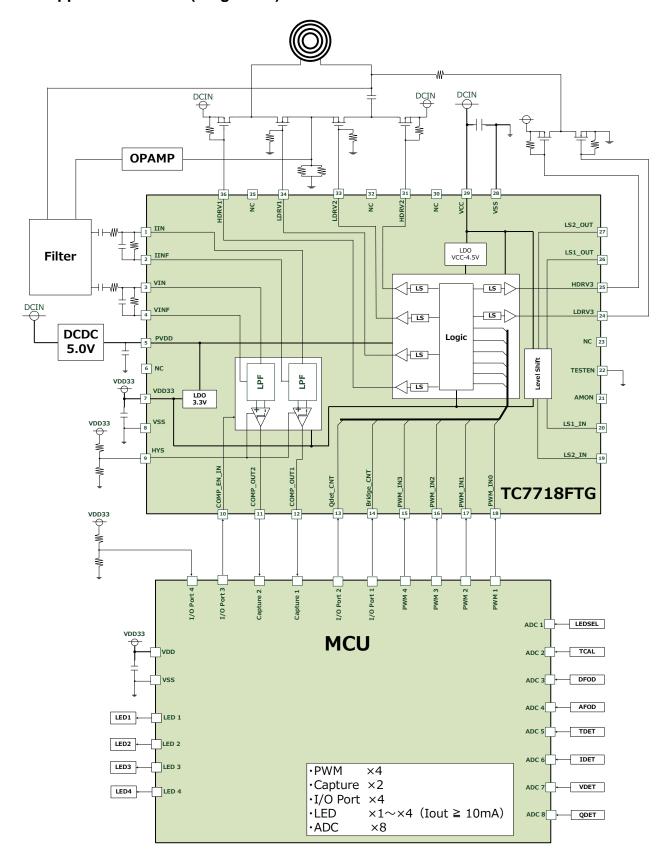

Figure 1 Internal block diagram

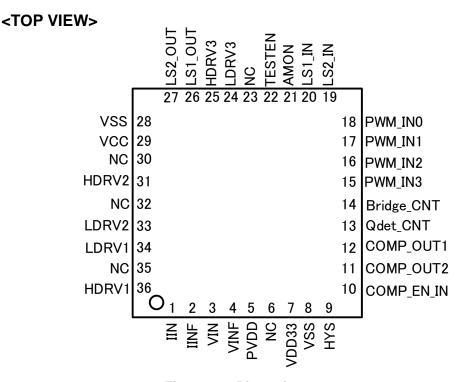

# 5. Pin assignment

Figure 2 Pin assignment

2

### 6. Pin function

Table 1 Pin function

| Pin<br>number | Pin symbol | I/O | Description                                   | Comment                          |

|---------------|------------|-----|-----------------------------------------------|----------------------------------|

| 1             | IIN        | I   | Capture input (Current channel)               |                                  |

| 2             | IINF       | I   | Internal OPAMP feedback                       | (Note 1)                         |

| 3             | VIN        | I   | Capture input (Voltage channel)               |                                  |

| 4             | VINF       | I   | Internal OPAMP feedback                       | (Note 1)                         |

| 5             | PVDD       | -   | Power supply pin                              |                                  |

| 6             | NC         | -   | Non connection                                | (Note 2)                         |

| 7             | VDD33      | -   | Power supply pin                              |                                  |

| 8             | VSS        | -   | GND pin                                       | (Note 3)                         |

| 9             | HYS        | I   | Hysteresis adjustment for internal comparator | (Note 4)                         |

| 10            | COMP_EN_IN | I   | Output enable for capture signal              |                                  |

| 11            | COMP_OUT2  | 0   | Comparator output 2 (VIN)                     |                                  |

| 12            | COMP_OUT1  | 0   | Comparator output 1 (VIN)                     |                                  |

| 13            | Qdet_CNT   | I   | Brake mode control                            |                                  |

| 14            | Bridge_CNT | I   | Full-bridge/Half-bridge shift                 |                                  |

| 15            | PWM_IN3    | I   | PWM input 3                                   |                                  |

| 16            | PWM_IN2    | I   | PWM input 2                                   |                                  |

| 17            | PWM_IN1    | I   | PWM input 1                                   |                                  |

| 18            | PWM_IN0    | I   | PWM input 0                                   |                                  |

| 19            | LS2_IN     | I   | Level shifter input 2                         |                                  |

| 20            | LS1_IN     | I   | Level shifter input 1                         |                                  |

| 21            | AMON       | 0   | Monitor pin                                   |                                  |

| 22            | TESTEN     | I   | Test pin                                      | (Note 3)                         |

| 23            | NC         | -   | Non connection                                | (Note 2)                         |

| 24            | LDRV3      | 0   | Low gate driving force 3                      | Tx coil for measuring Q (Note 5) |

| 25            | HDRV3      | 0   | High gate driving force 3                     | Tx coil for measuring Q (Note 5) |

| 26            | LS1_OUT    | 0   | Level shifter output 1                        |                                  |

| 27            | LS2_OUT    | 0   | Level shifter output 2                        |                                  |

| 28            | VSS        | -   | GND pin                                       | (Note 3)                         |

| 29            | VCC        | -   | Drive power supply                            |                                  |

| 30            | NC         | -   | Non connection                                | (Note 2)                         |

| 31            | HDRV2      | 0   | High gate driving force 2                     | Tx coil for operation (Note 5)   |

| 32            | NC         | -   | Non connection                                | (Note 2)                         |

| 33            | LDRV2      | 0   | Low gate driving force 2                      | Tx coil for operation (Note 5)   |

| 34            | LDRV1      | 0   | Low gate driving force 1                      | Tx coil for operation (Note 5)   |

| 35            | NC         | -   | Non connection                                | (Note 2)                         |

| 36            | HDRV1      | 0   | High gate driving force 1                     | Tx coil for operation (Note 5)   |

<sup>(</sup>Note 1) Please connect specified resistance and capacitor between IIN and IINF, VIN and VINF.

<sup>(</sup>Note 2) Please make it to open.

<sup>(</sup>Note 3) Please connect to common ground (GND)

<sup>(</sup>Note 4) Please supply the divided voltage which is divided from the power supplied from VDD33 by the resistance.

<sup>(</sup>Note 5) Please connect the pull-down resistance of  $100k\Omega$  between the gate pin and the source pin of Nch-MOSFET and Pch-MOSFET

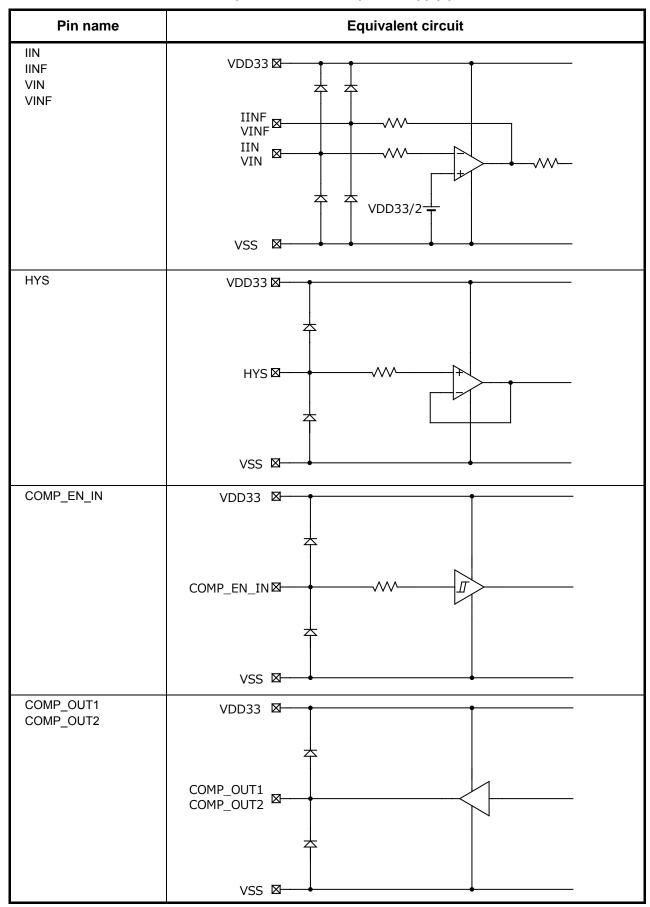

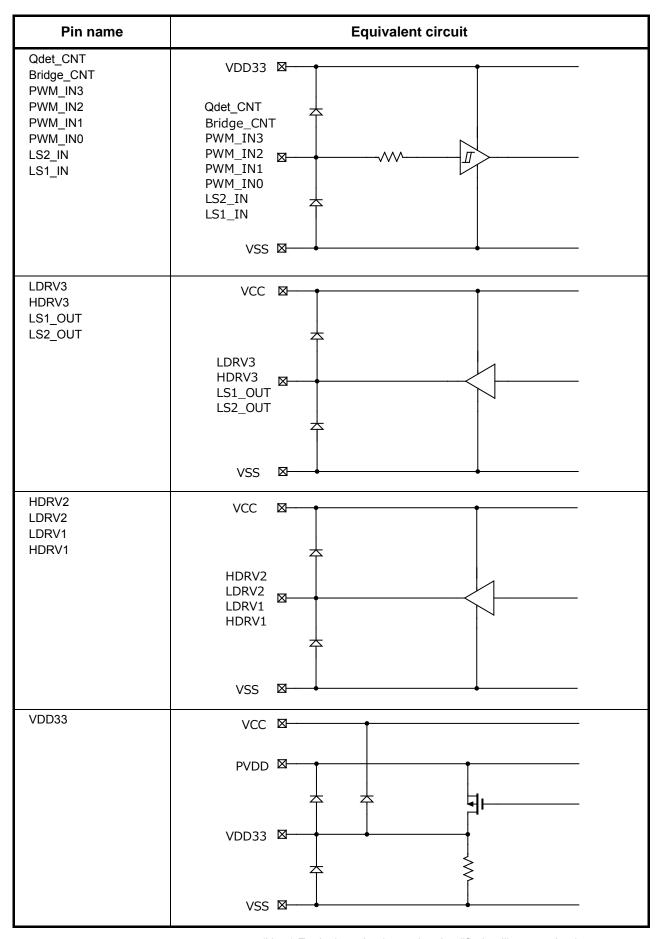

# 7. Equivalent circuit for input/output pins and power supply pins

Table 2 Equivalent circuit for power supply pins

5

(Note) Equivalent circuit may be simplified to illustrate circuits.

#### 8. Function and operation description

#### 8.1 General outline of wireless power system

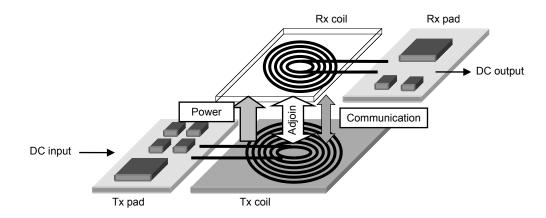

Qi compliant wireless power system consists of the first side (Tx) which transmits power and the second side (Rx) which receives power. Power is transmitted by adjoining coils included in Tx and Rx and by sharing and combining flux. Rx controls the power by monitoring receiving power and sending feedback signal to Tx. Tx controls the power by controlling transmitting power with feedback signal which is received from Rx. Configuration example of wireless power system is shown in Figure 3

Communication signal from Rx to Tx is transmitted (modulated) by ASK modulation. The communication rate and its packet in this communication are defined by Qi compliant. Communication rate is 2 kbps. Packets are ID, identification signal, error information, receive power, and stop signal. TX stops its operation in normal mode. It is powered on intermittently and confirms the existence of Rx on the Tx pad. When Tx recognizes Rx and succeeds the identification, transmit operation starts. Tx continues transmit operation until Tx cannot recognize the existence of Rx or receives transmit stop signal from Rx.

Qi Medium power v1.2 system adjusts the parameter to transmit the electrical power by interactive communication. And the electrical power of 15W (max) can be transmitted. The communication from TX to RX is performed by FSK modulation method. As for details of Qi system, please refer to the HP of WPC.

Figure 3 General outline of wireless power system

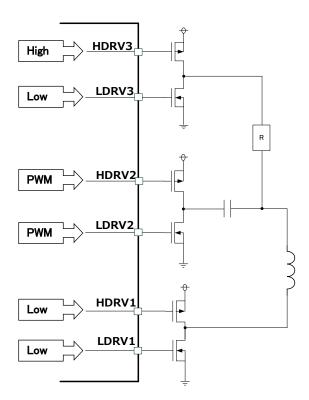

#### 8.2 Pre driver

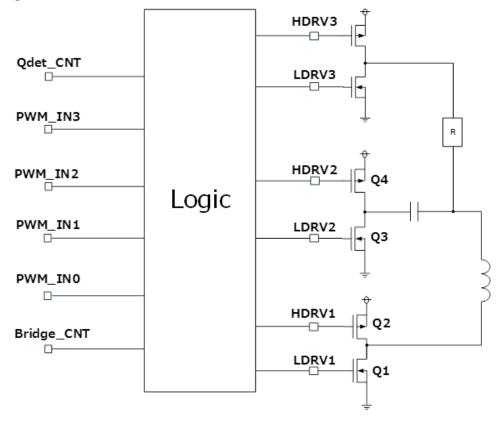

The TC7718FTG controls the external FET that drives the coil of transmission side by the signal from MCU (PWM\_IN [0:3], Bridge\_CNT, and Qdet\_CNT) as shown in below truth table.

The signal of Bridge\_CNT switches Half and Full. The signal of Qdet\_CNT configures the Break mode in measuring Q value of the transmission coil. When improper configuration, which causes shorting the external FET, is inputted to PWM\_IN [0:3], penetration protection function operates to fix the corresponded pin in the HDRV [1:3] at high level.

To control the Phase shift, four or more independent output pins of PWM signal are required for MCU.

|                          | Q det<br>CNT | Bridge<br>CNT | PWM<br>_IN0 | PWM<br>_IN1 | PWM<br>_IN2 | PWM<br>_IN3 | HDRV<br>1               | LDRV<br>1   | HDRV<br>2               | LDRV<br>2   | HDRV<br>3               | LDRV<br>3   |

|--------------------------|--------------|---------------|-------------|-------------|-------------|-------------|-------------------------|-------------|-------------------------|-------------|-------------------------|-------------|

| Q det ON<br>Full Bridge  | 0            | 0             | х           | x           | PWM<br>_IN2 | PWM<br>_IN3 | н                       | н           | н                       | н           | inverted<br>PWM<br>IN_3 | PWM<br>IN_2 |

| Q det ON<br>Half Bridge  | 0            | 1             | х           | х           | PWM<br>_IN2 | PWM<br>_IN3 | н                       | н           | н                       | н           | inverted<br>PWM<br>IN_3 | PWM<br>IN_2 |

| Q det OFF<br>Full Bridge | 1            | 0             | PWM<br>_INO | PWM<br>_IN1 | PWM<br>_IN2 | PWM<br>_IN3 | inverted<br>PWM<br>_IN1 | PWM<br>_INO | inverted<br>PWM<br>_IN3 | PWM<br>_IN2 | н                       | L           |

| Q det OFF<br>Half Bridge | 1            | 1             | х           | х           | PWM<br>_IN2 | PWM<br>_IN3 | L                       | L           | inverted<br>PWM<br>_IN3 | PWM<br>_IN2 | н                       | L           |

[X]: Don't care

Both drivers of HDRV and LDRV are operated by VCC and VSS.

#### 8.2.1 Configuration

Figure 4 Equivalent circuit of pre driver

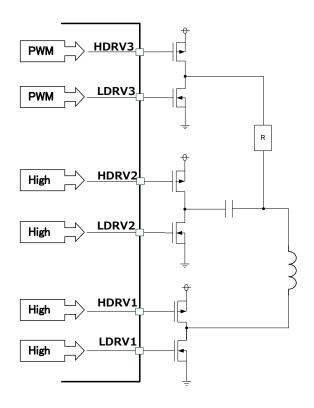

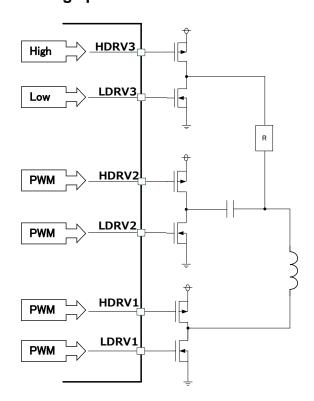

### <Q-value measurement>

# <Full Bridge power transmission>

## <Half Bridge power transmission>

Figure 5 Driver control

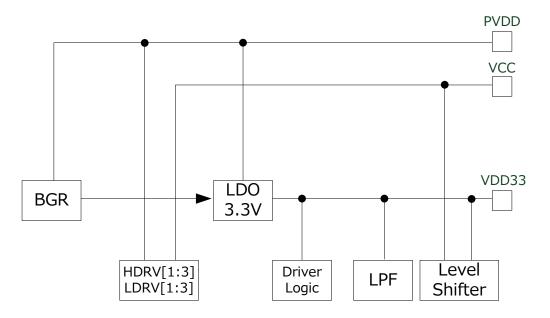

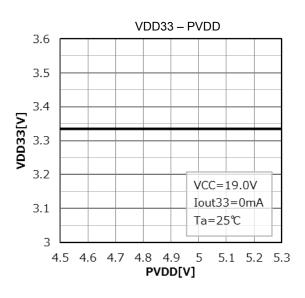

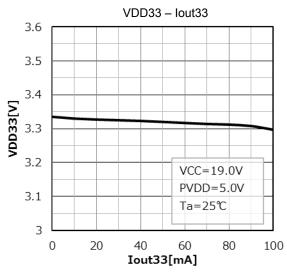

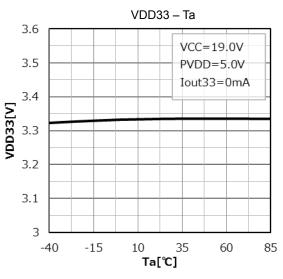

#### 8.3 LDO

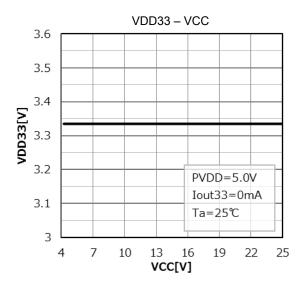

The TC7718FTG has LDO (VDD33) for the power supply to the internal logic block and the external MCU block.

#### 8.3.1 VDD33

VDD33 is 3.3V-voltage source for the internal logic block and the external MCU block.

(Note) Connect the capacitor of  $1\mu F$  (COUT) between VDD33 and GND.

Figure 6 Power configuration

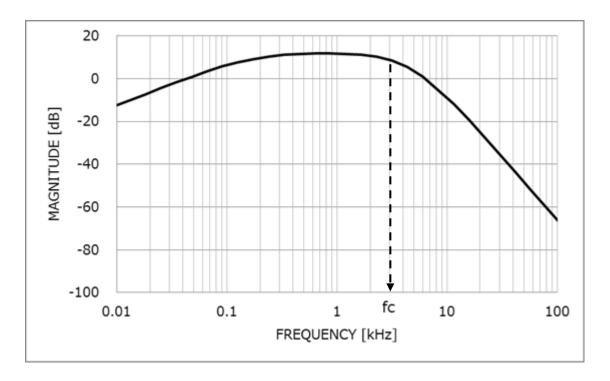

#### 8.4 Filter

The TC7718FTG can take the communication signal form the coil of receiving side by the built-in LPF and the comparator. And it converts this signal to the logic signal and output it to the MCU. All internal circuits connected to VIN pin and IIN pin have same constructions. When COMP\_EN\_IN pin inputs high level, the logic signal is outputted to the MCU. And when COMP\_EN\_IN pin inputs low level, the logic signal stops outputting.

#### 8.4.1 Filter characteristic

Figure 7 shows the filter characteristic of LPF with the peripheral circuits of table 3.

Symbol Value Unit No Ri 20  $\mathsf{k}\Omega$ Rf 20  $\mathsf{k}\Omega$ Ci 47 nF Cf 1200 рF

Table 3 Peripheral circuit value of Low Pass Filter

Figure 7 Filter characteristic

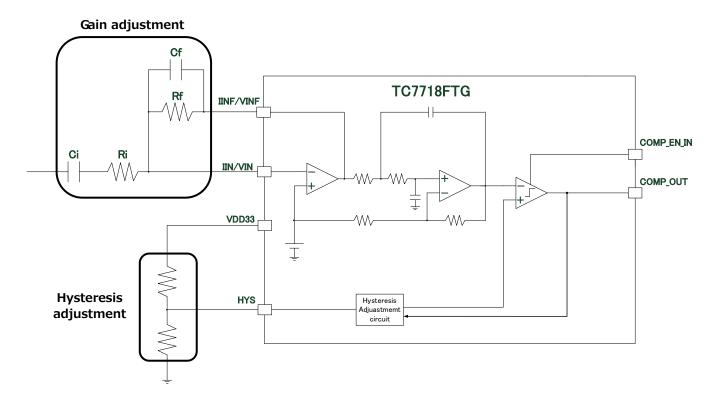

#### 8.4.2 Configuration

The gain of the internal OPAMP and the hysteresis of the comparator can be adjusted by the external circuit.

Figure 8 Filter adjustment circuit

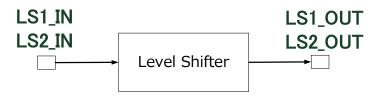

#### 8.5 Level shifter

The TC7718FTG incorporates the level shifter that converts the signal level from the MCU to the level which can be control the SW. It controls the SW that switches two or more coils. The signal is only the single way from the MCU to the SW. Logic is not inverted between input and output. (When H is input, H is output, and when L is input, L is output.)

Figure 9 Level shifter

11

2018-04-24

# 9. Absolute maximum ratings (Ta= 25°C)

Table 4 Absolute maximum ratings

| Characteristics             | Symbol              | Rating            | Unit |

|-----------------------------|---------------------|-------------------|------|

| Supply voltage              | PVDD                | -0.3 to 5.5       | V    |

| Supply voltage              | VCC                 | -0.3 to 28        | V    |

| Input voltage (Note 1)      | VIN                 | -0.3 to VDD33+0.5 | V    |

| Output voltage 1 (Note 2)   | V <sub>OUT1</sub>   | -0.3 to VCC+0.5   | V    |

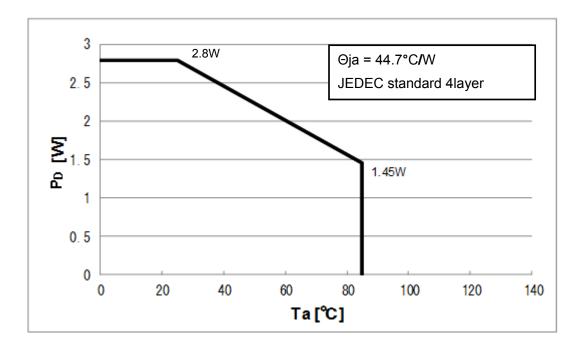

| Power consumption (Ta=25°C) | P <sub>D</sub>      | 2.8               | W    |

| Soldering temperature (10s) | T <sub>SOLDER</sub> | 260               | °C   |

| Storage temperature         | T <sub>stg</sub>    | -40 to 150        | °C   |

| Operating temperature       | T <sub>opr</sub>    | -40 to 85         | °C   |

(Note) The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings. Exceeding the rating (s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion. Please use the IC within the specified operating ranges.

(Note 1) All input pins

(Note 2) Apply to HDRV [3:1], LDRV [3:1], LS1\_OUT, and LS2\_OUT

### 9.1 Operating Conditions

Table 5 Operating Conditions (Ta = 25°C)

| Characteristics        | Symbol | Min | Тур. | Max  | Unit |

|------------------------|--------|-----|------|------|------|

| VCC Operating voltage  | VCC    | 4.5 | -    | 25.0 | V    |

| PVDD Operating voltage | PVDD   | 4.5 | -    | 5.3  | V    |

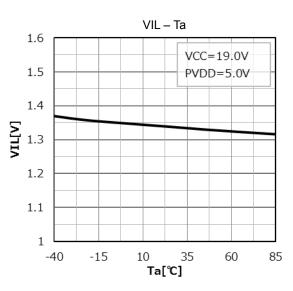

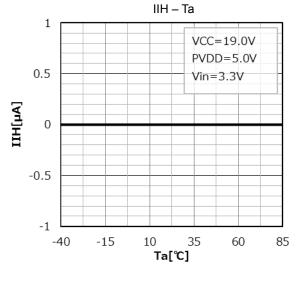

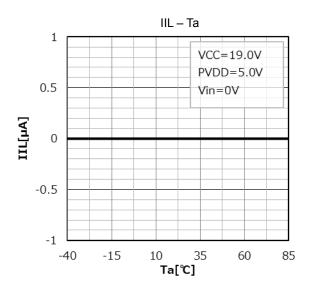

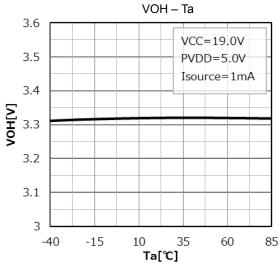

### 10. Electrical characteristics

#### 10.1 DC electrical characteristics

**Table 6 DC electrical characteristics**

(Unless otherwise specified, VCC = 19.0V, PVDD = 5.0V, COUT =  $1.0\mu F$ , Ta =  $25^{\circ}C$ )

|                                      |          | ,                                | •           |      |            |      |  |  |  |  |

|--------------------------------------|----------|----------------------------------|-------------|------|------------|------|--|--|--|--|

| Characteristics                      | Symbol   | Test condition                   | Min         | Тур. | Max        | Unit |  |  |  |  |

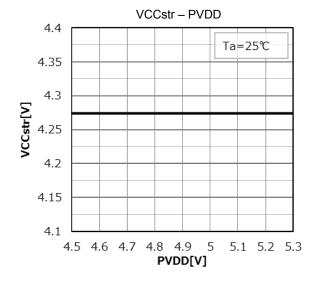

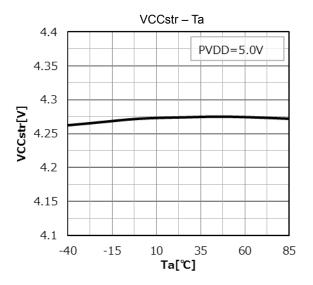

| VCC starting voltage (UVLO release)  | VCCstr   | -                                | 4.1         | 4.3  | 4.5        | V    |  |  |  |  |

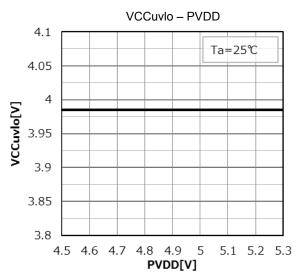

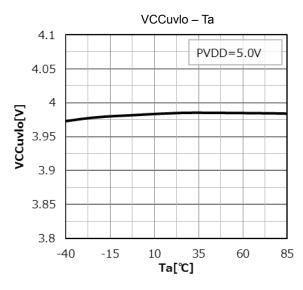

| VCC_UVLO operating voltage           | VCCuvlo  | -                                | 3.8         | 4.0  | 4.2        | ٧    |  |  |  |  |

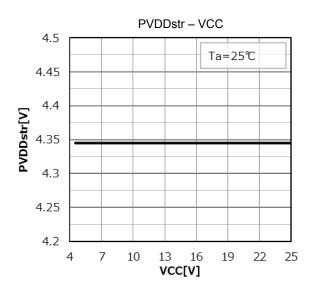

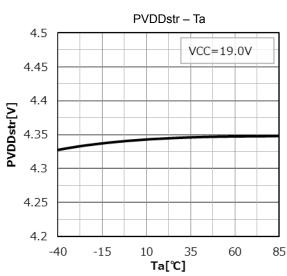

| PVDD starting voltage (UVLO release) | PVDDstr  | -                                | 4.1         | 4.3  | 4.5        | ٧    |  |  |  |  |

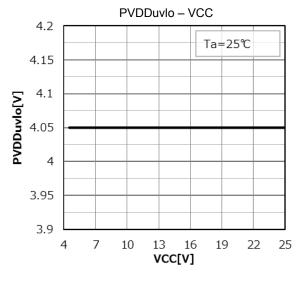

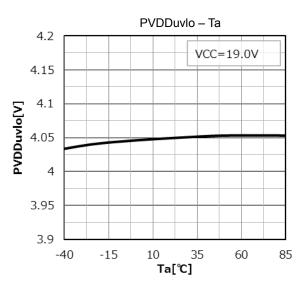

| PVDD_UVLO operating voltage          | PVDDuvlo | -                                | 3.8         | 4.0  | 4.2        | ٧    |  |  |  |  |

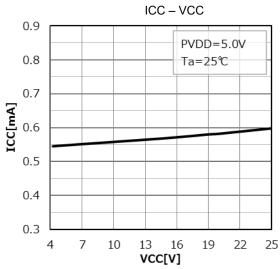

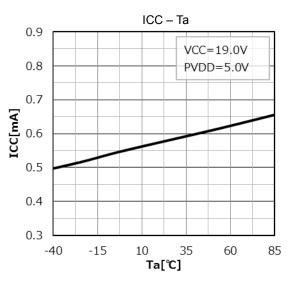

| VCC consumption current              | ICC      | Output pin: Open                 | -           | 0.6  | 1.2        | mA   |  |  |  |  |

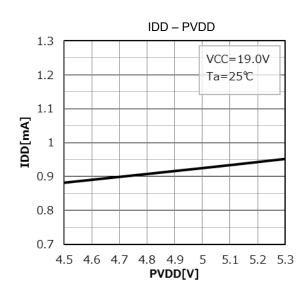

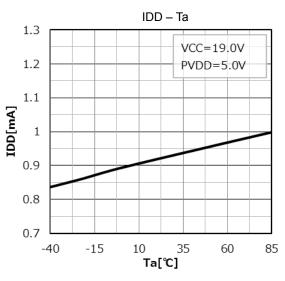

| PVDD consumption current             | IDD      | Output pin: Open                 | -           | 1.0  | 1.5        | mA   |  |  |  |  |

| LDO                                  |          |                                  |             |      |            |      |  |  |  |  |

| Output voltage                       | VDD33    | lout33 = 0mA                     | 3.0         | -    | 3.6        | V    |  |  |  |  |

| Output current                       | lout33   | Vdrop = 165mV                    | 60          | -    | -          | mA   |  |  |  |  |

| Load regulation                      | Load33   | PVDD = 5V<br>lout33 = 0mA → 60mA | -           | -    | 165        | mV   |  |  |  |  |

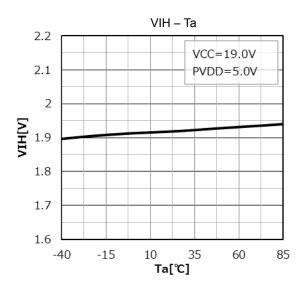

| Input / Output pin characteristic    | s        |                                  |             |      |            |      |  |  |  |  |

| High-level input voltage *1          | VIH      | -                                | VDD33*0.75  | -    | VDD33      | V    |  |  |  |  |

| Low-level input voltage *1           | VIL      | -                                | 0           | -    | VDD33*0.25 | ٧    |  |  |  |  |

| High-level input current *1          | IIH      | Vin = 3.3V                       | -1.0        | -    | -          | μΑ   |  |  |  |  |

| Low-level input current *1           | IIL      | Vin = 0V                         | -           | -    | 1          | μΑ   |  |  |  |  |

| High-level output voltage *2         | VOH      | Isource = 1mA                    | VDD33 - 0.5 | -    | -          | >    |  |  |  |  |

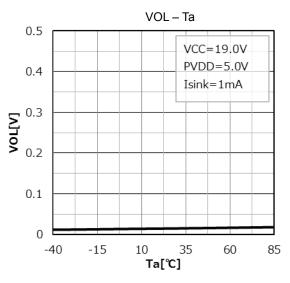

| Low-level output voltage *2          | VOL      | Isink = 1mA                      | -           |      | 0.5        | ٧    |  |  |  |  |

| Predriver                            |          |                                  |             |      |            |      |  |  |  |  |

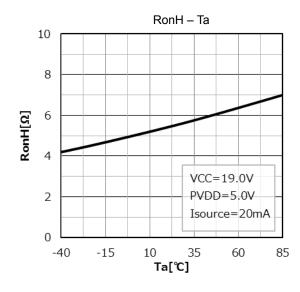

| High side MOS Ron                    | RonH     | Isource = 20mA                   | -           | 5.0  | 10.0       | Ω    |  |  |  |  |

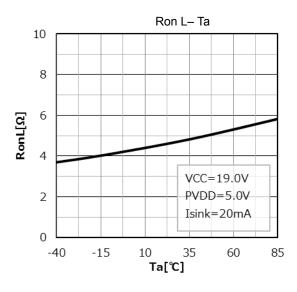

| Low side MOS Ron                     | RonL     | Isink = 20mA                     | -           | 5.0  | 10.0       | Ω    |  |  |  |  |

| Level shifter                        |          |                                  |             |      |            |      |  |  |  |  |

| High-level output voltage *3         | VOH_LS   | Isource = 20mA                   | VCC - 0.2   | -    | -          | V    |  |  |  |  |

| Low-level output voltage *3          | VOL_LS   | Isink = 20mA                     | -           | -    | 0.2        | V    |  |  |  |  |

|                                      | _        |                                  |             |      |            |      |  |  |  |  |

<sup>\*1</sup> Apply to COMP\_EN\_IN, Qdet\_CNT, Bridge\_CNT, PWM\_IN0, PWM\_IN1, PWM\_IN2, PWM\_IN3, LS1\_IN, LS2\_IN,

<sup>\*2</sup> Apply to COMP\_OUT1 and COMP\_OUT2 \*3 Apply to LS1\_OUT and LS2\_OUT

### **10.2** Electrostatic Discharge (ESD)

Note: Caution about the electrostatic discharge (ESD) sensitivity of this product. For ESD test data of this product, please contact our sales representative.

# 11. Application circuit (Single coil)

Figure 10 Application circuit (Single coil)

### 12. Thermal Estimation

This figure is allowable power dissipation graph of the TC7718FTG.

Figure 11 Thermal Estimation

You have to design PCB layout so that power loss does not go beyond this Pd-Ta line in this graph.

This graph is based on JEDEC standard 4 layers PCB. Thermal resistance strongly depends on the size of PCB, the pattern layout, and the number of layer of PCB.

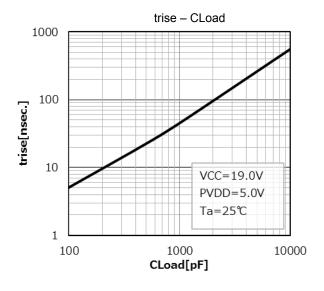

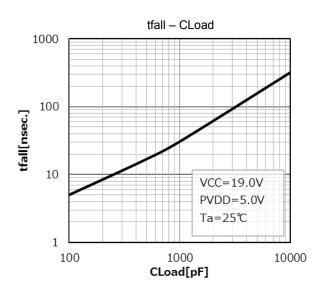

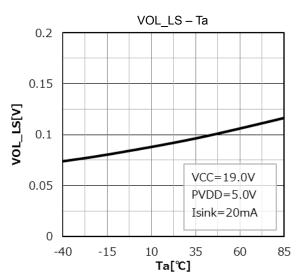

# 13. Application Curves (Reference data)

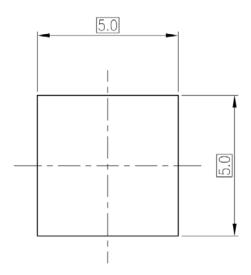

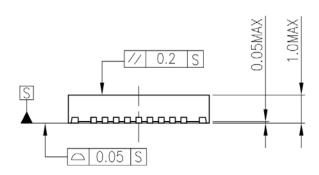

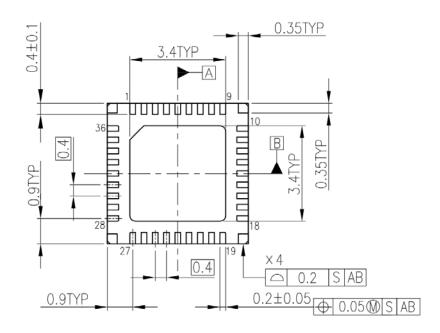

# 14. Package dimensions

P-VQFN36-0505-0.40-001

Unit: mm

Weight: 67.6mg (typ.)

Figure 12 Package dimensions

#### RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF

SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES

OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION

AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS

RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of

Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled

substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR

LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

### TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION