# **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings\***

| Supply Voltage (V <sub>DD</sub> )+6V                  |  |

|-------------------------------------------------------|--|

| Voltage on any Pin (GND – 0.3V) to $(V_{DD} + 0.3V)$  |  |

| Current on any Pin±50mA                               |  |

| Package Thermal Resistance ( $\theta_{JA})$ 330°C C/W |  |

| Operating Temperature (T <sub>A</sub> ) See Below     |  |

| Storage Temperature (T_{STG})65°C to +150°C           |  |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **TC1320 ELECTRICAL SPECIFICATIONS**

| Electrical Ch           | naracteristics: $V_{DD}$ = 2.7V to 5.5V, -40°C $\leq$ | T <sub>A</sub> ≤ +85 | °C, V <sub>REF</sub> = | 1.2V unless o         | otherwise | noted.                                                                                  |

|-------------------------|-------------------------------------------------------|----------------------|------------------------|-----------------------|-----------|-----------------------------------------------------------------------------------------|

| Symbol                  | Parameter                                             | Min                  | Тур                    | Max                   | Unit      | Test Conditions                                                                         |

| Power Supp              | ly                                                    |                      |                        |                       |           |                                                                                         |

| V <sub>DD</sub>         | Supply Voltage                                        | 2.7                  | 350                    | 500                   | μA        |                                                                                         |

| I <sub>DD</sub>         | Operating Current                                     | —                    | 0.35                   | 0.5                   | mA        | V <sub>DD</sub> = 5.5V, V <sub>REF</sub> = 1.2V<br>Serial Port Inactive <b>(Note 1)</b> |

| I <sub>DD-STANDBY</sub> | STANDBY Standby Supply Current                        |                      | 0.1                    | 1                     | μΑ        | V <sub>DD</sub> = 3.3V<br>Serial Port Inactive <b>(Note 1)</b>                          |

| Static Perfor           | mance - Analog Section                                |                      |                        |                       |           |                                                                                         |

|                         | Resolution                                            | _                    | —                      | 8                     | Bits      |                                                                                         |

| INL                     | Integral Non-Linearity at FS, $T_A = +25^{\circ}C$    | _                    | _                      | ±2                    | LSB       | (Note 2)                                                                                |

| FSE                     | Full Scale Error                                      | _                    | _                      | ±3                    | %FS       |                                                                                         |

| DNL                     | Differential Non-Linearity, $T_A = +25^{\circ}C$      | _                    | _                      | ±0.8                  | LSB       | All Codes (Note 2)                                                                      |

| V <sub>OS</sub>         | Offset Error at V <sub>OUT</sub>                      | _                    | ±0.3                   | ±8                    | mV        | (Note 2)                                                                                |

| TCV <sub>OS</sub>       | Offset Error Tempco at V <sub>OUT</sub>               | _                    | 10                     | _                     | μv/°C     |                                                                                         |

| PSRR                    | Power Supply Rejection Ratio                          | _                    | 80                     | —                     | dB        | V <sub>DD</sub> at DC                                                                   |

| V <sub>REF</sub>        | Voltage Reference Range                               | 0                    | _                      | V <sub>DD</sub> – 1.2 | V         |                                                                                         |

| I <sub>REF</sub>        | Reference Input Leakage Current                       | _                    | _                      | ±1.0                  | μA        |                                                                                         |

| V <sub>SW</sub>         | Voltage Swing                                         | 0                    | _                      | V <sub>REF</sub>      | V         | $V_{REF} \le (V_{DD} - 1.2V)$                                                           |

| R <sub>OUT</sub>        | Output Resistance @ V <sub>OUT</sub>                  | _                    | 5                      | _                     | Ω         | R <sub>OUT</sub> (Ω)                                                                    |

| I <sub>OUT</sub>        | Output Current (Source or Sink)                       | _                    | 2                      | _                     | mA        |                                                                                         |

| I <sub>SC</sub>         | Output Short-Circuit Current                          | _                    | 30                     | 50                    | mA        | Source                                                                                  |

|                         | V <sub>DD</sub> = 5.5V                                | _                    | 20                     | 50                    | mA        | Sink                                                                                    |

| Dynamic Pe              | rformance                                             |                      |                        |                       |           |                                                                                         |

| SR                      | Voltage Output Slew Rate                              | _                    | 0.8                    | —                     | V/µs      |                                                                                         |

| t <sub>SETTLE</sub>     | Output Voltage Full Scale Settling Time               | _                    | 10                     | _                     | μsec      |                                                                                         |

| t <sub>WU</sub>         | Wake-up Time                                          | _                    | 20                     | —                     | μS        |                                                                                         |

|                         | Digital Feed Through and Crosstalk                    | _                    | 5                      | —                     | nV-s      | SDA = V <sub>DD</sub> , SCL = 100kHz                                                    |

| Serial Port I           | nterface                                              |                      |                        |                       |           |                                                                                         |

| V <sub>IH</sub>         | Logic Input High                                      | 2.4                  | _                      | V <sub>DD</sub>       | V         |                                                                                         |

| V <sub>IL</sub>         | Logic Input Low                                       | _                    |                        | 0.6                   | _         |                                                                                         |

| V <sub>OL</sub>         | SDA Output Low                                        | _                    |                        | 0.4<br>0.6            | V<br>V    | $I_{OL} = 3mA$ (Sinking Current)<br>$I_{OL} = 6mA$                                      |

| C <sub>IN</sub>         | Input Capacitance SDA, SCL                            | _                    | 5                      | 0.4                   | pF        |                                                                                         |

| I <sub>LEAK</sub>       | I/O Leakage                                           | _                    | _                      | ±1.0                  | μA        |                                                                                         |

Note 1: SDA and SCL must be connected to  $V_{DD}$  or GND.

2: Measured at  $V_{OUT} \ge 50$  mV referred to GND to avoid output buffer clipping.

© 2002-2012 Microchip Technology Inc.

# TC1320 ELECTRICAL SPECIFICATIONS (CONTINUED)

| <b>Electrical Characteristics:</b> $V_{DD}$ = 2.7V to 5.5V, -40°C $\leq$ T <sub>A</sub> $\leq$ +85°C, V <sub>REF</sub> = 1.2V unless otherwise noted. |                                       |                       |     |      |                 |                                                         |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|-----|------|-----------------|---------------------------------------------------------|--|--|--|

| Symbol                                                                                                                                                | Parameter                             | Parameter Min Typ Max |     | Unit | Test Conditions |                                                         |  |  |  |

| Serial Port A                                                                                                                                         | AC Timing                             |                       |     |      |                 |                                                         |  |  |  |

| f <sub>SMB</sub>                                                                                                                                      | SMBus Clock Frequency                 | 10                    | —   | 100  | kHz             |                                                         |  |  |  |

| t <sub>IDLE</sub>                                                                                                                                     | Bus Free Time Prior to New Transition | 4.7                   | —   | —    | μsec            |                                                         |  |  |  |

| t <sub>H(START)</sub>                                                                                                                                 | START Condition Hold Time             | 4.0                   | _   | _    | μsec            |                                                         |  |  |  |

| t <sub>SU(START)</sub>                                                                                                                                | START Condition Setup Time            | 4.7                   | _   | _    | μsec            | 90% SCL to 10% SDA<br>(for Repeated START<br>Condition) |  |  |  |

| t <sub>SU(STOP)</sub>                                                                                                                                 | STOP Condition Setup Time             | 4.0                   | —   | _    | μsec            |                                                         |  |  |  |

| t <sub>H-DATA</sub>                                                                                                                                   | Data In Hold Time                     | 100                   | —   | —    | nsec            |                                                         |  |  |  |

| t <sub>SU-DATA</sub>                                                                                                                                  | Data In Setup Time                    | 100                   | _   | _    | nsec            |                                                         |  |  |  |

| t <sub>LOW</sub>                                                                                                                                      | Low Clock Period                      | 4.7                   | —   | —    | μsec            | 10% to 10%                                              |  |  |  |

| t <sub>HIGH</sub>                                                                                                                                     | High Clock Period                     | 4                     | —   | _    | μsec            | 90% to 90%                                              |  |  |  |

| t <sub>F</sub>                                                                                                                                        | SMBus Fall Time                       | _                     | —   | 300  | nsec            | 90% to 10%                                              |  |  |  |

| t <sub>R</sub>                                                                                                                                        | SMBus Rise Time                       | _                     | —   | 1000 | nsec            | 10% to 90%                                              |  |  |  |

| t <sub>POR</sub>                                                                                                                                      | Power-on Reset Delay                  | _                     | 500 | —    | μsec            | $V_{DD} \ge V_{POR}$ (Rising Edge)                      |  |  |  |

Note1:SDA and SCL must be connected to  $V_{DD}$  or GND.2:Measured at  $V_{OUT} \ge 50 mV$  referred to GND to avoid output buffer clipping.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

| Pin Number | Symbol           | Туре           | Description                                                                                                                                                                                                                                 |

|------------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>REF</sub> | Input          | Input. Voltage Reference Input can range from 0V to 1.2V below V <sub>DD</sub> .                                                                                                                                                            |

| 2          | SDA              | Bi-Directional | Bi-directional. Serial data is transferred on the SMBus in both directions using this pin.                                                                                                                                                  |

| 3          | SCL              | Input          | Input. SMBus serial clock. Clocks data into and out of the TC1320.                                                                                                                                                                          |

| 4          | GND              | Power          | Ground.                                                                                                                                                                                                                                     |

| 5          | V <sub>OUT</sub> | Output         | Output. Buffered DAC output voltage. This voltage is a function of the reference voltage and the contents of the DATA register.                                                                                                             |

| 6          | NC               | None           | No connection.                                                                                                                                                                                                                              |

| 7          | DAC-OUT          | Output         | Output. Unbuffered DAC output voltage. This voltage is a function of the reference voltage and the contents of the DATA register. This output is unbuffered and care must be taken that the pin is connected only to a high-impedance node. |

| 8          | V <sub>DD</sub>  | Power          | Positive power supply input. See electrical specifications.                                                                                                                                                                                 |

$<sup>\</sup>ensuremath{\textcircled{}^{\circ}}$  2002-2012 Microchip Technology Inc.

# 3.0 DETAILED DESCRIPTION

The TC1320 is a monolithic 8-bit digital-to-analog converter, that is designed to operate from a single supply that can range from 2.7V to 5.5V. The DAC consists of a data register (DATA), a configuration register (CONF), and a current output amplifier. The TC1320 uses an external reference, which also determines the maximum output voltage.

The TC1320 uses a current steering DAC, based on an array of matched current sources. This current, along a precision resistor, converts the contents of the Data Register and  $V_{REF}$  into an output voltage,  $V_{OUT}$  given by:

$V_{OUT} = V_{REF} (DATA/256)$

#### 3.1 Reference Input

The reference pin, V<sub>REF</sub>, is a buffered high-impedance input and because of this, the load regulation of the reference source needs only to be able to tolerate leakage levels of current (less than 1µA). V<sub>REF</sub> accepts a voltage range from 0 to (V<sub>DD</sub> – 1.2V). Input capacitance is typically 10pF.

#### 3.2 Output Amplifier

The TC1320 DAC output is buffered with an internal unity gain rail-to-rail input/output amplifier, with a typical slew rate of  $0.8V/\mu$ sec. Maximum full scale transition settling time is  $10\mu$ sec to within ±1/2LSB when loaded with  $1k\Omega$  in parallel with 100pF.

#### 3.3 Standby Mode

The TC1320 allows the host to put it into a Low Power ( $I_{DD} = 0.5\mu A$ , typical) Standby mode. In this mode, the D/A conversion is halted. The SMBus port operates normally. Standby mode is enabled by setting the SHDN bit in the CONFIG register. The table below summarizes this operation.

| TABLE 3-1: | STANDBY MODE OPERATION |

|------------|------------------------|

|------------|------------------------|

| SHDN Bit | Operating Mode |

|----------|----------------|

| 0        | Normal         |

| 1        | Standby        |

#### 3.4 SMBus Slave Address

The TC1320 is internally programmed to have a default SMBus address value of 1001 000b. Seven other addresses are available by custom order (contact factory). See Figure 3-1 for locating address bits in SMBus protocol.

# FIGURE 3-1: SMBus PROTOCOLS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S A                     | ddress | s   | R/W         | ACI                         | к      | Command |             | ACK       | D                                                                 | ata       | ACK        | Р |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|-----|-------------|-----------------------------|--------|---------|-------------|-----------|-------------------------------------------------------------------|-----------|------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                       | '-Bits |     | 0           |                             |        | 8       | 8-Bits      |           | 8-                                                                | Bits      |            |   |

| Por                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Slave A<br>ad 1-Byte Fo |        |     |             | which register you are into |        |         |             |           | ata Byte: data goes<br>to the register set<br>y the command byte. |           |            |   |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Address                 | R/W    | ACK | Comma       | nd                          | ACK    | s       | Address     | R/W       | ACK                                                               | Data      | NACK       | Р |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-Bits                  | 0      | AUK | 8-Bits      |                             | AUK    | 3       | 7-Bits      | 1         | AUK                                                               | 8-Bits    |            |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         | -      |     | 0 Dita      | <b>,</b>                    |        |         | 7-Dit3      | '         |                                                                   | 0 Dito    |            |   |

| Slave Address Command Byte: selects<br>which register you are<br>reading from. Slave Address: repeated<br>due to change in data<br>flow direction. Data Byte: reads from<br>the register set by the<br>command byte.   Receive 1-Byte Format Command Byte: selects<br>which register you are<br>reading from. Slave Address: repeated<br>due to change in data<br>flow direction. Data Byte: reads from<br>the register set by the<br>command byte. |                         |        |     |             |                             |        |         |             |           |                                                                   |           |            |   |

| Rec                                                                                                                                                                                                                                                                                                                                                                                                                                                 | eive 1-Byte             | Forma  |     | 0           | ster yo                     |        |         | due to chan | ge in dat |                                                                   | the regis | ster set b |   |

| Rec<br>S                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                       | Forma  | t   | reading fro | ster yo                     | ou are |         | due to chan | ge in dat |                                                                   | the regis | ster set b |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                       |        | t   | reading fro | ster yo<br>om.              | ou are |         | due to chan | ge in dat |                                                                   | the regis | ster set b |   |

DS21386C-page 6

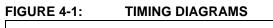

# 4.0 SERIAL PORT OPERATION

The Serial Clock input (SCL) and bi-directional data port (SDA) form a 2-wire bi-directional serial port for programming and interrogating the TC1320. The following conventions are used in this bus architecture:

#### TABLE 4-1: TC1320 SERIAL BUS CONVENTIONS

| Term        | Explanation                                                                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter | The device sending data to the bus.                                                                                                                                                                                                  |

| Receiver    | The device receiving data from the bus.                                                                                                                                                                                              |

| Master      | The device which controls the bus: initiating transfers (START), generating the clock, and terminating transfers (STOP).                                                                                                             |

| Slave       | The device addressed by the master.                                                                                                                                                                                                  |

| START       | A unique condition signaling the beginning of<br>a transfer indicated by SDA falling<br>(High - Low) while SCL is high.                                                                                                              |

| STOP        | A unique condition signaling the end of a transfer indicated by SDA rising (Low - High) while SCL is high.                                                                                                                           |

| ACK         | A Receiver Acknowledges the receipt of each<br>byte with this unique condition. The Receiver<br>drives SDA low during SCL high of the ACK<br>clock pulse. The Master provides the clock<br>pulse for the ACK cycle.                  |

| Busy        | Communication is not possible because the bus is in use.                                                                                                                                                                             |

| Not Busy    | When the bus is IDLE, both SDA and SCL will remain high.                                                                                                                                                                             |

| Data Valid  | The state of SDA must remain stable during<br>the High period of SCL in order for a data bit<br>to be considered valid. SDA only changes<br>state while SCL is low during normal data<br>transfers. (See START and STOP conditions.) |

All transfers take place under control of a host, usually a CPU or microcontroller, acting as the Master, which provides the clock signal for all transfers. The TC1320 *always* operates as a Slave. The serial protocol is illustrated in Figure 3-1. All data transfers have two phases; all bytes are transferred MSB first. Accesses are initiated by a START condition (START), followed by a device address byte and one or more data bytes. The device address byte includes a Read/Write selection bit. Each access must be terminated by a STOP Condition (STOP). A convention called *Acknowledge* (ACK) confirms receipt of each byte. Note that SDA can change only during periods when SCL is LOW (SDA changes while SCL is HIGH is reserved for START and STOP Conditions).

# 4.1 START Condition (START)

The TC1320 continuously monitors the SDA and SCL lines for a START condition (a HIGH to LOW transition of SDA while SCL is HIGH), and will not respond until this condition is met.

# 4.2 Address Byte

Immediately following the START Condition, the host must transmit the address byte to the TC1320. The 7-bit SMBus address for the TC1320 is 1001000. The 7-bit address transmitted in the serial bit stream must match for the TC1320 to respond with an Acknowledge (indicating the TC1320 is on the bus and ready to accept data). The eighth bit in the Address Byte is a Read/Write bit. This bit is a 1 for a read operation, or 0 for a write operation. During the first phase of any transfer, this bit will be set = 0 to indicate that the command byte is being written.

# 4.3 Acknowledge (ACK)

Acknowledge (ACK) provides a positive handshake between the host and the TC1320. The host releases SDA after transmitting eight bits, then generates a ninth clock cycle to allow the TC1320 to pull the SDA line LOW to Acknowledge that it successfully received the previous eight bits of data or address.

# 4.4 Data Byte

After a successful ACK of the address byte, the host must transmit the data byte to be written, or clock out the data to be read. (See the appropriate timing diagrams.) ACK will be generated after a successful write of a data byte into the TC1320.

# 4.5 STOP Condition (STOP)

Communications must be terminated by a STOP condition (a LOW to HIGH transition of SDA while SCL is HIGH). The STOP Condition must be communicated by the transmitter to the TC1320. Refer to Figure 4-1, Timing Diagrams for serial bus timing.

<sup>© 2002-2012</sup> Microchip Technology Inc.

### 4.6 Register Set and Programmer's Model

#### TABLE 4-2: TC1320 COMMAND SET (SMBus READ\_BYTE AND WRITE\_BYTE)

| Command Byte Description |      |                                   |  |  |  |  |  |  |  |

|--------------------------|------|-----------------------------------|--|--|--|--|--|--|--|

| Command                  | Code | Function                          |  |  |  |  |  |  |  |

| RWD                      | 00h  | Read/Write Data (DATA)            |  |  |  |  |  |  |  |

| RWCR                     | 01h  | Read/Write Configuration (CONFIG) |  |  |  |  |  |  |  |

# TABLE 4-3:CONFIGURATION REGISTER<br/>(CONFIG), 8-BIT, READ/WRITE

|       | Configuration Register (CONFIG) |      |                                               |        |                |                |                 |  |  |  |  |

|-------|---------------------------------|------|-----------------------------------------------|--------|----------------|----------------|-----------------|--|--|--|--|

| D[7]  | D[6]                            | D[5] | D[4]                                          | D[3]   | D[2]           | D[1]           | D[0]            |  |  |  |  |

|       | Reserved                        |      |                                               |        |                |                |                 |  |  |  |  |

| В     | Bit POR Function 1              |      |                                               |        |                |                | ration          |  |  |  |  |

| D[    | 0]                              | 0    | Standby                                       | Switch | Read/<br>Write | 1 = S<br>0 = N | tandby<br>ormal |  |  |  |  |

| D[7]- | D[1]                            | 0    | Reserved;<br>Always returns<br>Zero when Read |        | N/A            | Ν              | I/A             |  |  |  |  |

# TABLE 4-4:DATA REGISTER (DATA),<br/>8-BIT, READ/WRITE

|                                         | Data Register (DATA) |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|----------------------|--|--|--|--|--|--|--|--|--|--|

| D[7] D[6] D[5] D[4] D[3] D[2] D[1] D[0] |                      |  |  |  |  |  |  |  |  |  |  |

| MSB                                     |                      |  |  |  |  |  |  |  |  |  |  |

The DAC output voltage is a function of reference voltage and the binary value of the contents of the Data register. The transfer function is given by the expression:

#### **EQUATION 4-1:**

| $V_{OUT} = V_{REF} x \left[ \frac{DATA}{256} \right]$ |

|-------------------------------------------------------|

|-------------------------------------------------------|

# 4.7 Register Set Summary

The TC1320's register set is summarized in Table 4-5 below. All registers are 8-bits wide.

#### TABLE 4-5: TC1320 REGISTER SET SUMMARY

| Name   | Description     | POR State   | Read | Write |

|--------|-----------------|-------------|------|-------|

| Data   | Data Register   | 0000 0000b  | Х    | Х     |

| Config | CONFIG Register | d0000 0000b | Х    | Х     |

<sup>© 2002-2012</sup> Microchip Technology Inc.

# 5.0 PACKAGING INFORMATION

# 5.1 Package Marking Information

Package marking data not available at this time.

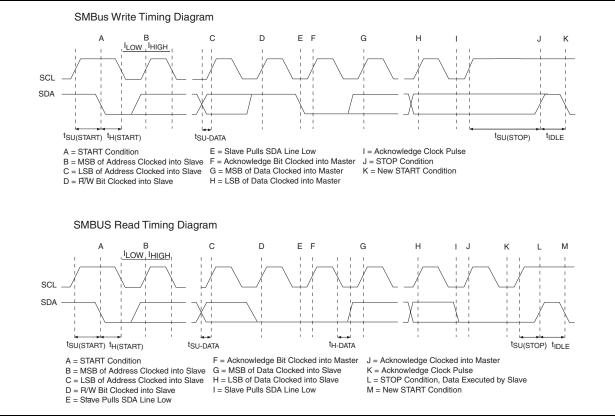

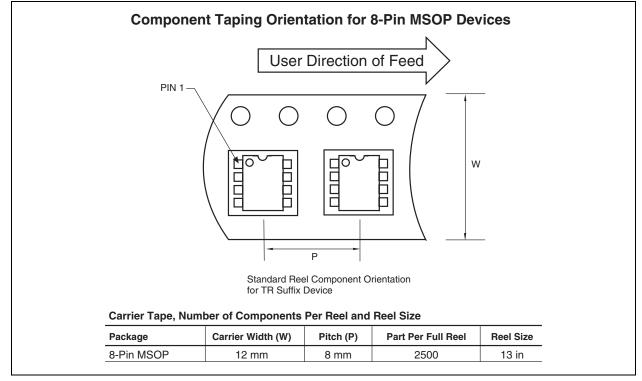

#### 5.2 Taping Forms

DS21386C-page 10

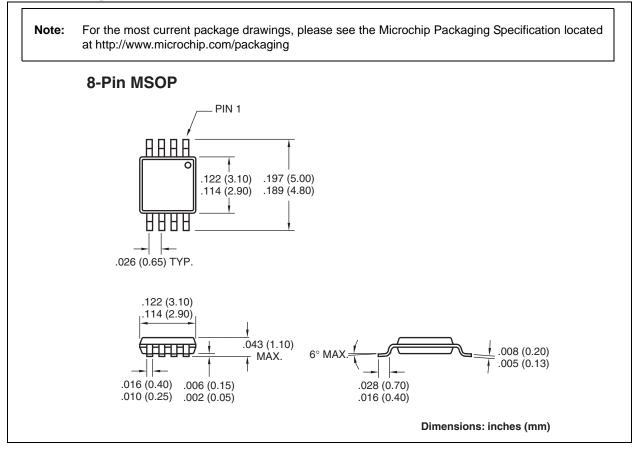

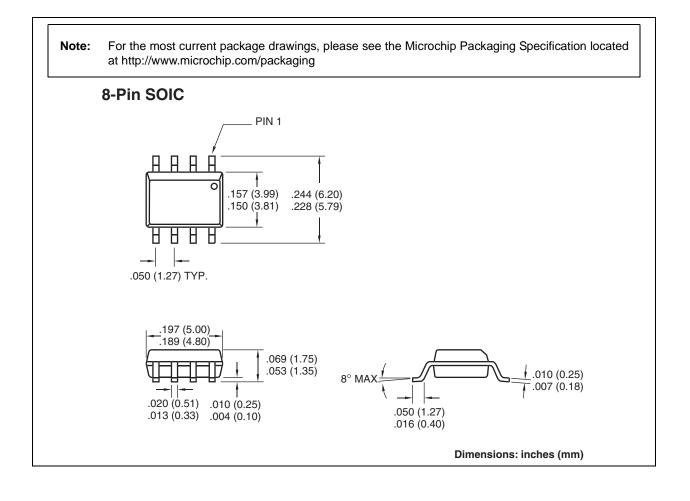

## 5.3 Package Dimensions

<sup>© 2002-2012</sup> Microchip Technology Inc.

# 6.0 **REVISION HISTORY**

# **Revision C (November 2012)**

Added a note to each package outline drawing.

<sup>© 2002-2012</sup> Microchip Technology Inc.

# SALES AND SUPPORT

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2002-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Rinted on recycled paper.

ISBN: 9781620767849

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

© 2002-2012 Microchip Technology Inc.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

**France - Paris** Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820