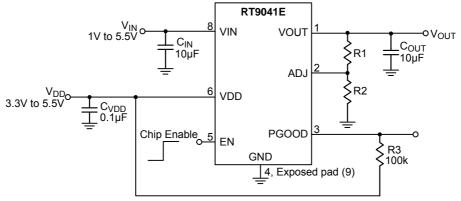

## **Typical Application Circuit**

### **Function Pin Description**

| Pin No.            | Pin Name | Pin Function                                                                                                                                                                               |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | VOUT     | Output Voltage.                                                                                                                                                                            |

| 2                  | ADJ      | Output Voltage Adjust Pin. Set the output voltage by the internal feedback resistors when ADJ is ground. If external feedback resistors is used, $V_{OUT} = V_{REF} \times (R1 + R2)/R2$ . |

| 3                  | PGOOD    | Power Good Open Drain Output.                                                                                                                                                              |

| 4, 9 (Exposed pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                |

| 5                  | EN       | Chip Enable (Active-High).                                                                                                                                                                 |

| 6                  | VDD      | Supply Voltage of Control Circuitry.                                                                                                                                                       |

| 7                  | NC       | No Internal Connection.                                                                                                                                                                    |

| 8                  | VIN      | Supply Input Voltage.                                                                                                                                                                      |

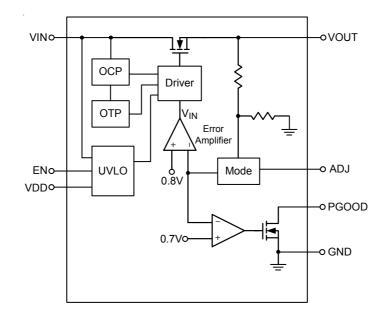

## **Function Block Diagram**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com DS9041E-03 November 2014

2

## RICHTEK

## Absolute Maximum Ratings (Note 1)

| <ul> <li>Bias Supply Input Voltage, VDD</li> <li>Supply Input Voltage, VIN</li> </ul> |                |

|---------------------------------------------------------------------------------------|----------------|

| Other Input/Output Pins                                                               | 6V             |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                                        |                |

| WDFN-8L 2x2                                                                           | 0.833VW        |

| Package Thermal Resistance (Note 2)                                                   |                |

| WDFN-8L 2x2, θ <sub>JA</sub>                                                          | 120°C/W        |

| WDFN-8L 2x2, θ <sub>JC</sub>                                                          | 8.2°C/W        |

| Lead Temperature (Soldering, 10 sec.)                                                 | 260°C          |

| Junction Temperature                                                                  | 150°C          |

| Storage Temperature Range                                                             | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                           |                |

| HBM (Human Body Model)                                                                | 2kV            |

## Recommended Operating Conditions (Note 4)

| Bias Supply Input Voltage, VDD | 3V to 5.5V                        |

|--------------------------------|-----------------------------------|

| Supply Input Voltage, VIN      | 1V to 5.5V                        |

| Junction Temperature Range     | –40°C to 125°C                    |

| Ambient Temperature Range      | $-40^{\circ}$ C to $85^{\circ}$ C |

### **Electrical Characteristics**

(V<sub>IN</sub> = 1.8V,  $I_{LOAD}$  = 1mA,  $C_{OUT}$  = 10 $\mu$ F,  $T_A$  = 25°C unless otherwise specified)

| Parameter                        | Symbol                           | Test Conditions                                                                                      | Min   | Тур       | Max   | Unit |  |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------|-------|-----------|-------|------|--|

| Input                            |                                  |                                                                                                      |       |           |       |      |  |

| Adjustable Output Voltage Range  | Vout                             |                                                                                                      | 0.8   |           | 2.5   | V    |  |

| Bias Input Under Voltage Lockout | V <sub>UVLO</sub>                |                                                                                                      |       | 2.7       |       | V    |  |

| VIN Shutdown Current             | I <sub>SHDN</sub>                | 1V < V <sub>IN</sub> < 5.5V, V <sub>IN</sub> = V <sub>OUT</sub> + 0.6V                               |       | 1         | 5     | μA   |  |

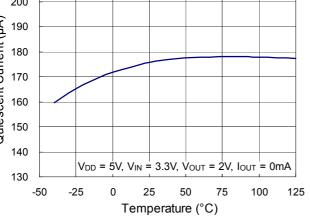

| Quiescent Current                | l <sub>Q</sub>                   | 3V < V <sub>DD</sub> < 5.5V                                                                          |       | 160       | 250   | μA   |  |

| VDD Shutdown Current             | I <sub>SHDN</sub>                | 3V < V <sub>DD</sub> < 5.5V                                                                          |       | 1         | 5     | μA   |  |

| Regulator Characteristics        |                                  |                                                                                                      |       |           |       |      |  |

| Line Regulation                  | $\Delta V_{OUT} / \Delta V_{IN}$ | I <sub>OUT</sub> = 10mA, 1.5V < V <sub>IN</sub> < 5.5V,<br>V <sub>IN</sub> = V <sub>OUT</sub> + 0.6V | -0.15 |           | 0.15  | %/V  |  |

| Load Regulation                  | $\Delta V_{OUT} / \Delta I_{IN}$ | $V_{IN} = V_{OUT} + 0.6V$ ,<br>$I_{LOAD} = 1mA \text{ to } 300mA$                                    |       | 0.2       | 1     | %    |  |

| Fixed Output Voltage Accuracy    | $\Delta V_{OUT}$                 | Short ADJ to GND, I <sub>OUT</sub> = 10mA                                                            | -2    |           | 2     | %    |  |

| Reference Voltage                | V <sub>REF</sub>                 | I <sub>OUT</sub> = 10mA                                                                              | 0.784 | 0.8       | 0.816 | V    |  |

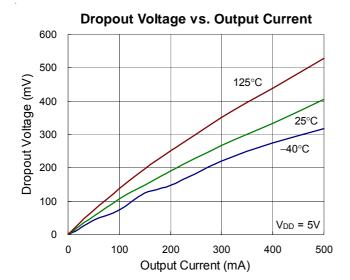

| Dropout Voltage                  | V <sub>DROP</sub>                | $I_{OUT} = 300 mA, \ V_{DD} - V_{OUT} \geq 2.1 V$                                                    |       | - 200 300 |       | m\/  |  |

| Diopout voltage                  |                                  | $I_{OUT}$ = 500mA, $V_{DD}-V_{OUT} \ge 2.1 V$                                                        |       | 300       | 500   | mV   |  |

| Current Limit                    | ILIM                             | R <sub>LOAD</sub> = 0                                                                                | 550   | 700       | 1400  | mA   |  |

| Thermal-Shutdown                 | T <sub>SD</sub>                  | 3V < V <sub>DD</sub> < 5.5V                                                                          |       | 160       |       | °C   |  |

| Thermal-Shutdown Hysteresis      | $\Delta T_{SD}$                  |                                                                                                      |       | 20        |       | °C   |  |

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9041E-03 November 2014

## **RT9041E**

| RICHTEK | R | CH | IT. | E | ~ |

|---------|---|----|-----|---|---|

|---------|---|----|-----|---|---|

| Parameter                            |            | Symbol | Test Conditions                           | Min | Тур | Max | Unit |  |

|--------------------------------------|------------|--------|-------------------------------------------|-----|-----|-----|------|--|

| ADJ                                  |            | •      |                                           |     |     |     |      |  |

| ADJ Pin Threshold                    | d          |        |                                           |     | 0.2 |     | V    |  |

| PGOOD Compara                        | ator       |        | -                                         |     |     |     |      |  |

| Comparator Thres                     | shold      |        | % of regulated output voltage             |     | 88  |     | %    |  |

| Comparator Hyste                     | eresis     | VHYST  | (Note 5)                                  |     | 10  |     | mV   |  |

| Logic and I/O                        |            |        | -                                         |     |     |     |      |  |

|                                      | Logic-High | VIH    |                                           | 1.6 |     |     | v    |  |

| EN Input Voltage                     | Logic-Low  | VIL    |                                           |     |     | 0.8 |      |  |

| EN Current                           |            | IEN    | V <sub>EN</sub> = 5V                      |     | 12  |     | μA   |  |

| PGOOD Output Low Voltage             |            |        | PGOOD sinking 1mA                         |     |     | 0.1 | V    |  |

| PGOOD Output High Leakage<br>Current |            |        | 0 < V <sub>PGOOD</sub> < V <sub>IN</sub>  | -1  |     | 1   | μA   |  |

| Dynamics                             |            |        |                                           |     |     |     |      |  |

| PGOOD Propagation Delay              |            | tpgood | Rising edge within 5% of regulation level |     |     | 5   | ms   |  |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guaranteed by Design.

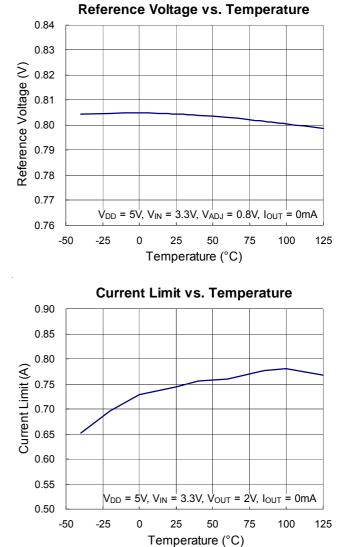

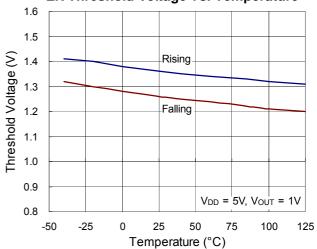

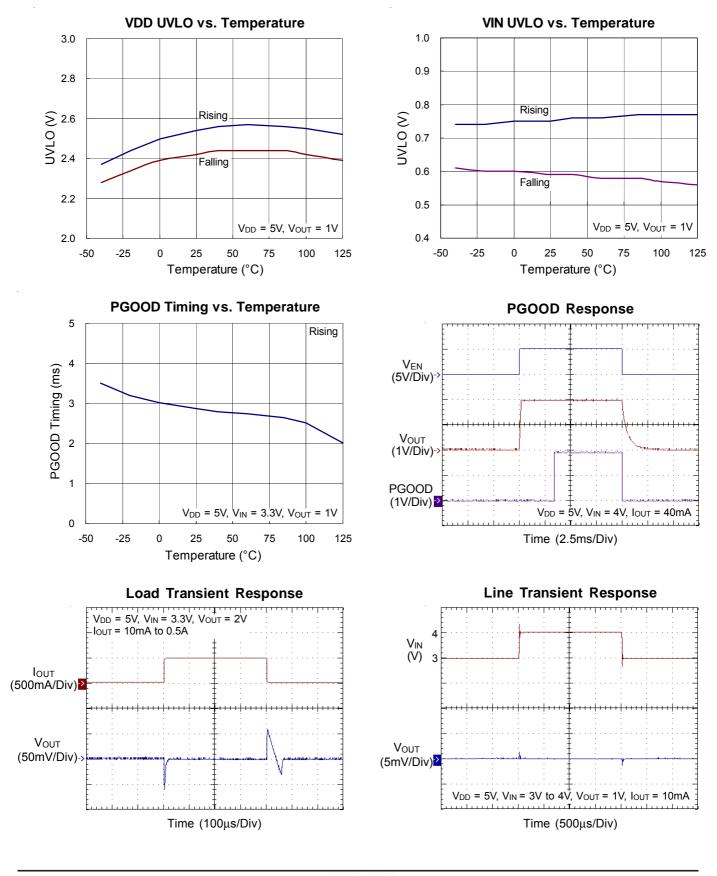

### **Typical Operating Characteristics**

**EN Threshold Voltage vs. Temperature**

RICHTEK is a registered trademark of Richtek Technology Corporation. Copyright ©2014 Richtek Technology Corporation. All rights reserved. DS9041E-03 November 2014

## **RT9041E**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com DS9041E-03 November 2014

6

## RICHTEK

## **RT9041E**

Copyright ©2014 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9041E-03 November 2014

### **Application Information**

The RT9041E is a low voltage, low dropout linear regulator with an external bias supply input, capable of supporting an input voltage range from 1V to 5.5V with a fixed output voltage from 1V to 2V in 0.1V increments.

#### Supply Voltage Setting

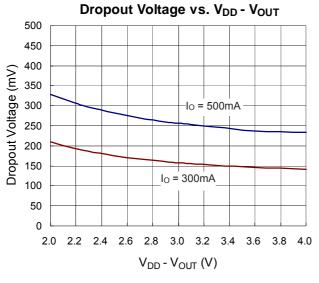

The bias supply voltage (V<sub>DD</sub>) operates from 3V to 5.5V. For better efficiency, it is suggested to operate V<sub>DD</sub> at 5V when the output voltage is higher than 1V. Figure 1 shows the curves of the recommended V<sub>DD</sub> – V<sub>OUT</sub> range vs. the dropout voltage (V<sub>IN</sub> – V<sub>OUT</sub>) values.

Figure 1. Dropout Voltage vs.  $V_{DD} - V_{OUT}$

#### **Output Voltage Setting**

The RT9041E output voltage is also adjustable from 0.8V to 2.5V via the external resistive voltage divider. The voltage divider resistors can have values up to  $800k\Omega$  because of the very high impedance and low bias current of the sense comparator. The output voltage is set according to the following equation :

$$V_{OUT} = V_{REF} x \left(1 + \frac{R1}{R2}\right)$$

where  $V_{\mathsf{REF}}$  is the reference voltage with a typical value of 0.8V.

#### Chip Enable Operation

The RT9041E goes into sleep mode when the EN pin is in a logic low condition. In this condition, the pass transistor, error amplifier, and band gap are all turned off, reducing the supply current to  $1\mu A$  (typ.). The EN pin can be directly tied to VIN to keep the part on.

#### **Current Limit**

The RT9041E contains an independent current limit circuitry, which monitors and controls the pass transistor's gate voltage, limiting the output current to 0.7A (typ.).

#### CIN and COUT Selection

Like any low dropout regulator, the external capacitors of the RT9041E must be carefully selected for regulator stability and performance. Using a capacitor of at least  $10\mu$ F is suitable. The input capacitor must be located at a distance of not more than 0.5 inch from the input pin of the IC. Any good quality ceramic capacitor can be used. However, a capacitor with larger value and lower ESR (Equivalent Series Resistance) is recommended since it will provide better PSRR and line transient response.

The RT9041E is designed specifically to work with low ESR ceramic output capacitor for space saving and performance consideration. Using a ceramic capacitor with value at least  $10\mu$ F and ESR larger than  $40m\Omega$  on the RT9041E output ensures stability. Nevertheless, the RT9041E can still work well with other types of output capacitors due to its wide range of stable ESR. Figure 2 shows the allowable ESR range as a function of load current for various output capacitance. Output capacitors with larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The output capacitor should be located at a distance of not more than 0.5 inch from the output pin of the RT9041E.

## RICHTEK

# Figure 2. Region of Stable $C_{OUT}$ ESR vs. the Load Current

#### **Thermal Considerations**

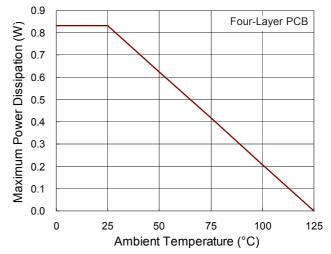

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-8L 2x2 packages, the thermal resistance,  $\theta_{JA}$ , is 120°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C – 25°C) / (120°C/W) = 0.833W for

WDFN-8L 2x2 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 3. Derating Curve of Maximum Power Dissipation

9

## RT9041E

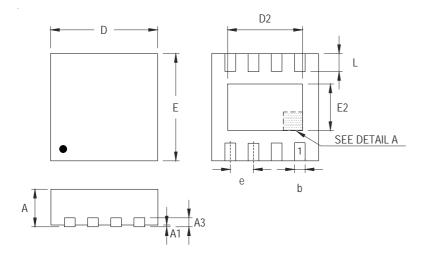

### **Outline Dimension**

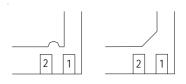

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Cumbal | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b      | 0.200      | 0.300          | 0.008                | 0.012 |  |

| D      | 1.950      | 2.050          | 0.077                | 0.081 |  |

| D2     | 1.000      | 1.250          | 0.039                | 0.049 |  |

| E      | 1.950      | 2.050          | 0.077                | 0.081 |  |

| E2     | 0.400      | 0.650          | 0.016                | 0.026 |  |

| е      | 0.500      |                | 0.0                  | )20   |  |

| L      | 0.300      | 0.400          | 0.012                | 0.016 |  |

W-Type 8L DFN 2x2 Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

www.richtek.com 10